# CCM PFC controller with high voltage startup

## Features

- Peak current mode CCM-operated

- 800 V high voltage startup with integrated input voltage sensing

- Active input filter capacitor discharge

- Proprietary multiplier "emulator" with minimum THD of line current in all operating conditions (CCM and DCM)

- Extremely few external components

- Protections: feedback loop failure, OVP, OCP, inductor saturation, brown-in, brownout (compliant to medical SMPS standards)

- Inductor current sense

- Disable and low consumption function

- In-rush current monitoring

- Soft-start for smooth startup

- 1.2% (@ Tj = 25 °C) internal reference voltage

- 65 kHz (A version) and 130 kHz (B version) switching frequency

- PGOOD\_OUT and adjustable PGOOD\_IN

- SSOP10 package

# Application

- PFC pre-regulators for:

- IEC61000-3-2 and JEIDA-MITI compliant SMPS in excess of 1 kW

- Desktop PC, server, web server, game console

- High power LED luminaries

- Industrial and medical SMPS according to IEC 60601-1-2

# Description

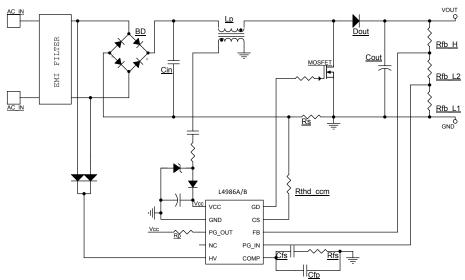

The L4986 is a peak current-mode PFC controller for boost converter with a proprietary multiplier "emulator" which in addition to the innovative THD optimizers guarantee very low Total Harmonic Distortion (THD) performance in all operating conditions. The device comes in a pin SO package and offers a high performance/ low-component count solution for CCM-operated boost PFC pre-regulators in EN61000-3-2 and JEIDA-MITI compliant applications, in a power range that spans from few hundred W to some kW.

The device, thanks to a proprietary off-time modulator, operates in quasi-fixed frequency in all operating conditions. Two options are available, 65 kHz for A and 130 kHz for B.

The 800 V high voltage start-up block includes also the circuitry to discharge the X-capacitors of the EMI filter to a safe level. This allows the unit to meet safety regulation (such as IEC 61010-1 or IEC 62368-1) without using the traditional discharge resistor in parallel to the X-capacitors.

| Product status link |

|---------------------|

| L4986               |

| L4986A              |

| L4986B              |

| L4986ATR            |

| L4986BTR            |

| Product summary |         |               |  |

|-----------------|---------|---------------|--|

| Order<br>codes  | Package | Packaging     |  |

| L4986A          |         | Tube          |  |

| L4986B          |         | Tube          |  |

| L4986ATR        | SSOP10  | Tape and reel |  |

| L4986BTR        | -       | Tape and reel |  |

51

The device features low consumption and disable functions allowing usage in applications supposed to comply even with the latest energy saving requirements issued by Energy Star, the Department of Energy (DoE) in the United States, the European Code of Conduct, the European Union's Ecodesign Directive, and other guidelines.

In addition to an overvoltage protection able to keep the output voltage under control during transient conditions, the IC is provided also with a protection against feedback loop failures or erroneous settings and boost inductor saturation. The brownout protection function allows to design medical equipment according to the latest regulations driven by IEC 60601-1-2 which requires the output regulation in case of mains dips lasting up to 500 msec. Soft-start limits the peak current.

The PG\_IN is an adjustable input comparator suitable for monitoring the PFC output voltage and accordingly driving a logic signal exiting from PG\_OUT pin. The totempole output stage, capable of 0.7 A source and 1.5 A sink current, is suitable for big MOSFET or IGBT drive.

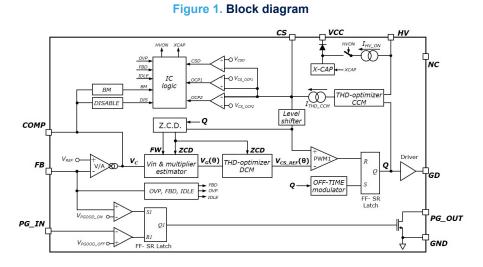

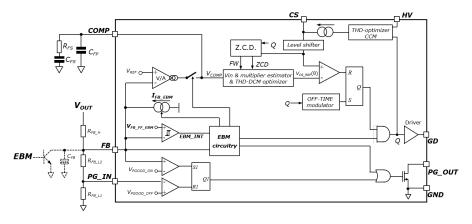

# 1 Block diagram and typical application

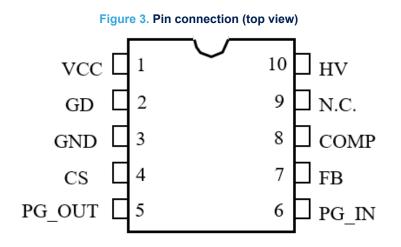

# 2 Pin connection and functions

| No. | Name   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VCC    | Supply voltage. The internal high voltage start-up generator charges an electrolytic capacitor connected between this pin and GND as long as the voltage on the pin is below the start-up threshold of the IC, after it is disabled and the chip turns on. A bypass capacitor to GND has to be place close to the pins to get a clean bias voltage.                                                                                                                                                                                                            |

| 2   | GD     | Gate driver output. The output stage is able to drive power MOSFETs and IGBTs; it is capable of 0.7 A source current and 1.5 A sink current (typical values).                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3   | GND    | IC ground. Current return for both the signal/bias part of the IC and the gate driver current. All of the ground connections of the bias components should be tied to a track going to this pin and kept separate from any pulsed current return.                                                                                                                                                                                                                                                                                                              |

|     |        | Current sense input. The inductor current is sensed through a resistor $R_S$ on the current return side. The resulting negative voltage is applied to this pin and compared to an internal sinusoidal-shaped reference to determine the turn-off instant of the external power switch. The pin is equipped with an internal current generator (sourced current during power switch on-time); it can be used, by simply adding a series resistor ( $R_{THD\_CCM}$ ) for improved THD in CCM operation.                                                          |

| 4   | CS     | If the voltage on the pin goes below $V_{CS\_OCP1}$ (-0.49 V typ.) the internal overcurrent comparator is triggered and terminates the conduction cycle of the external power switch before the normal PWM circuit does. In this way, the peak inductor current is limited at a maximum of 0.49/R <sub>S</sub> .                                                                                                                                                                                                                                               |

|     |        | A second overcurrent level set at $V_{CS\_OCP2}$ (-0.75 V typ.) detects abnormal current values (e.g. due to boost inductor saturation) and, on this occurrence, activates a safety procedure that immediately stops the converter activity until the current level reaches the zero-current threshold $V_{CS\_ZCD}$ (-10 mV typical value). It allows safe operations also during current surges occurring at power-up or after a mains dip or missing cycle; in fact it allows switching start/restart only when the overcurrent event is definitively over. |

|     |        | Power good output (open drain).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5   | PG_OUT | The pin is actively pulled to ground once the IC is turned on and the FB pin voltage exceeds the internal threshold $V_{PGOOD_ON}$ (2.375 V typ.).<br>If the PG_IN input is lower than the internal threshold $V_{PGOOD_OFF}$ (1.25 V typ.), the PG_OUT pin is set to high impedance.                                                                                                                                                                                                                                                                          |

| 6   | PG_IN  | Power good input.<br>The pin is used to set the off-threshold of PGOOD comparator and it is connected to the output voltage resistor divider.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 7   | FB     | Inverting input of the trans-conductance Error Amplifier (OTA).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| No. | Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |      | The information on the output voltage of the PFC regulator is fed into the pin through a resistor divider so that its voltage is proportional to the instantaneous value of the high voltage bus ( $V_{BULK}$ ). Under steady-state conditions the voltage on pin sits at the internal reference of the error amplifier ( $V_{REF}$ = 2.5 V). If the voltage exceeds the steady-state value by 7% ( $V_{FB} > V_{FB_S}$ ), e.g. due to an output voltage overshoot, the switching activity is stopped until $V_{FB} < V_{FB_R}$ (2.55 V typ.). If the voltage at FB pin is below $V_{FB_FF/EBM}$ (0.5 V typ.) either a failure of the output divider is assumed or the device is externally forced in burst-mode operation. In both cases the PFC controller is stopped with low consumption. See Section 5.7 Idle operation (external burst-mode function) and Section 5.10.6 Feedback failure detection for further details. |

| 8   | COMP | Output pin of the trans-conductance Error Amplifier (OTA). A compensation network is placed between this pin and GND to allow stability of the control loop and ensure high PF and THD. To avoid uncontrolled rise of the output voltage at light or zero load, when $V_{COMP} < V_{COMP_S}$ (1 V typ. Burst Mode condition) the gate driver pin (GD) is forced low and the switching activity is stopped. If the Burst Mode condition is triggered when GD is high, the system is allowed to complete the current ON-time and the system stoppage takes place after GD falling edge. The pin can be also used to disable the device by forcing $V_{COMP} < V_{COMP_DIS}$ (0.7 V typ.) by means of an external pull-down active network.                                                                                                                                                                                       |

| 9   | N.C. | High voltage spacer. This pin is not internally connected to isolate the high voltage section and ease compliance with safety regulations (creepage distance) on the PCB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |      | High voltage start-up generator input / AC voltage sensing input. The pin, able to withstand 800 V, has to be connected to the AC side of the input bridge via a pair of diodes (1N400x type) to sense the AC input voltage. If the voltage on the pin is higher than $V_{HV\_START}$ (29 V typ.), an internal pull-up circuit charges the capacitor connected between the pin VCC and GND. Initially the current is low for safety in case of a shorted VCC, and then it goes to the normal level as far as the VCC pin reaches the start-up threshold ( $V_{CC\_ON}$ ). The generator is re-enabled when the voltage on the VCC pin falls below the UVLO threshold ( $V_{CC\_OFF}$ ).                                                                                                                                                                                                                                        |

| 10  | HV   | The pin is used also to sense the AC voltage, which is used by the AC brownout, the input voltage feedforward and the THD-CCM optimizer functions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |      | An internal logic circuit detects that the unit has been detached from the power line; if this event occurs then, the HV pin sinks a current to discharge the X-capacitors of the EMI filter to a safe level. This allows the unit to meet safety regulations (such as IEC 61010-1 or IEC 62368-1) without using the traditional discharge resistor in parallel to the X-capacitor, thus saving the associated power losses and enabling ultra-low consumption in stand-by conditions. In case an AC brownout condition is detected the internal generator is alternatively turned on and off and, as a consequence, the voltage at VCC pin cycles between the start-up threshold and the UVLO threshold.                                                                                                                                                                                                                      |

# 3 Electrical data

57

# 3.1 Absolute maximum ratings

### Table 2. Absolute maximum ratings

| Symbol | Pin | Parameter                            | Value                | Unit |

|--------|-----|--------------------------------------|----------------------|------|

| VCC    | 1   | Supply voltage                       | -0.3 to 30           | V    |

| ICC    | 1   | Maximum supply current               | 0 to 25              | mA   |

| GD     | 2   | Gate driver                          | -0.3 to VCC          | V    |

| CS     | 4   | Current sense                        | -10 to 3.6           | V    |

| PG_OUT | 5   | PGOOD output                         | -0.3 to VCC          | V    |

| PG_IN  | 6   | PGOOD input (IPG_IN < 1 mA)          | -0.3 to self-limited | V    |

| FB     | 7   | Input feedback (IFB < 1mA)           | -0.3 to self-limited | V    |

| COMP   | 8   | OTA output                           | -0.3 to 6            | V    |

| HV     | 10  | Line voltage input (referred to GND) | -1 to 800            | V    |

## Table 3. Recommended operating conditions.

| Symbol | Pin | Parameter           | Min. | Max. | Unit | Remarks                                           |

|--------|-----|---------------------|------|------|------|---------------------------------------------------|

| VCC    | 1   | IC supply voltage   | -0.3 | 24.5 | V    | Internal clamp at 24.5 V min.                     |

| CS     | 4   | Current sense input | -10  | 3.3  | V    |                                                   |

| PG_OUT | 5   | Power good output   | -0.3 | VCC  | V    |                                                   |

| PG_IN  | 6   | Power good input    | -0.3 | 3.0  | V    | Internal clamp at 3 V min.                        |

| FB     | 7   | Feedback input      | -0.3 | 3.0  | V    | Internal clamp at 3 V min.                        |

| COMP   | 8   | OTA output          | -0.3 | 5.3  | V    | Values referred to an externally forced condition |

| HV     | 10  | High voltage input  | -1   | 600  | V    |                                                   |

# 3.2 Thermal data

### Table 4. Thermal data

| Symbol                | Parameter                               | Max. value | Unit |

|-----------------------|-----------------------------------------|------------|------|

| R <sub>th j-amb</sub> | Thermal resistance, junction-to-ambient | 120        | °C/W |

| P <sub>tot</sub>      | Power dissipation @Tamb = 50 °C         | 0.75       | W    |

| Tj                    | Junction temperature operating range    | -40 to 150 | °C   |

| T <sub>stg</sub>      | Storage temperature                     | -55 to 150 | °C   |

# 4 Electrical characteristics

$T_{j}$  = -25 to 125 °C,  $V_{CC}$  = 15 V,  $C_{GD}$  = 1 nF unless otherwise specified.

| Symbol                     | Parameter                                | Test Condition                                                                                    | Min. | Тур. | Max. | Unit |

|----------------------------|------------------------------------------|---------------------------------------------------------------------------------------------------|------|------|------|------|

| SUPPLY VOLTAGE             |                                          |                                                                                                   |      |      |      |      |

| V <sub>CC</sub>            | Operating range                          | After turn-on                                                                                     | 10   |      | 24.5 | V    |

| V <sub>CC_ON</sub>         | Turn-on threshold                        | Voltage rising <sup>(1)</sup>                                                                     | 13   | 14   | 15   | V    |

| V <sub>CC_OFF</sub>        | Turn-off threshold                       | Voltage falling <sup>(1)</sup>                                                                    | 8.5  | 9.0  | 9.5  | V    |

| V <sub>CC_HVSTUP_OVP</sub> | Turn-on threshold of HVSTUP in OVP state | Voltage falling <sup>(1)</sup>                                                                    | 10.8 | 11.5 | 12.2 | v    |

| Vz                         | V <sub>CC</sub> clamp voltage            | I <sub>VCC</sub> = 20 mA <sup>(2)</sup>                                                           | 24.5 | 26   | 27   | V    |

| SUPPLY CURRENT             |                                          |                                                                                                   |      |      |      |      |

| I <sub>START_UP</sub>      | Start-up current                         | Before turn-on, $V_{CC}$ = 14 V                                                                   |      | 400  | 550  | μA   |

|                            |                                          | V <sub>FB</sub> < V <sub>FB_FF/EBM</sub>                                                          |      | 0.6  | 0.8  | mA   |

| Ι <sub>Q</sub>             | Quiescent current                        | V <sub>FB</sub> = 2.5 V,<br>V <sub>COMP</sub> < V <sub>COMP</sub> _S                              |      | 0.65 | 0.85 | mA   |

|                            |                                          | V <sub>FB</sub> > V <sub>FB</sub> S                                                               |      | 0.65 | 0.85 | mA   |

|                            |                                          | L4986A, $T_{ON} = T_{ON MIN}^{(3)}$                                                               |      | 2.2  | 2.8  | mA   |

| Icc                        | Operating supply current                 | _                                                                                                 |      |      |      |      |

|                            |                                          | L4986A, HV*T <sub>ON</sub> = 1.3 ms <sup>(4)</sup>                                                |      | 3.8  | 4.7  | m/   |

|                            |                                          | L4986B, $T_{ON} = T_{ON} MIN^{(3)}$                                                               |      | 3.4  | 4.0  | m/   |

|                            |                                          | L4986B, HV*T <sub>ON</sub> = 0.65 ms <sup>(4)</sup>                                               |      | 4.6  | 5.5  | mA   |

| I <sub>DIS</sub>           | Quiescent in disable                     | V <sub>COMP</sub> < V <sub>COMP</sub> _DIS                                                        |      | 450  | 600  | μA   |

| HIGH-VOLTAGE STA           | RT-UP GENERATOR                          |                                                                                                   |      |      |      |      |

| V <sub>HV</sub>            | Breakdown voltage                        | I <sub>HV</sub> < 100 μA                                                                          | 800  |      |      | V    |

| V <sub>HV_START</sub>      | Start voltage                            | I <sub>VCC</sub> < 100 μA                                                                         | 22   | 29   | 40   | V    |

| V <sub>CC_SO</sub>         | VCC switchover threshold                 |                                                                                                   | 0.55 | 1    | 1.4  | V    |

|                            |                                          | $V_{HV}$ > 40 V, $V_{CC}$ < $V_{CC}$ _SO                                                          | 0.7  | 1    | 1.3  | m/   |

|                            | ON-state charge current                  | V <sub>HV</sub> > 40 V,                                                                           |      |      |      |      |

| I <sub>HV_ON</sub>         |                                          | $V_{CC} > V_{CC\_SO},$                                                                            | 5    | 7    | 10   | mA   |

|                            |                                          | V <sub>FB</sub> < V <sub>FB_HVSTUPOFF</sub>                                                       |      |      |      |      |

| V <sub>FB_HVSTUPOFF</sub>  | Generator shutdown threshold at FB pin   |                                                                                                   | 1.65 | 1.75 | 1.85 | v    |

| T <sub>TOUT</sub>          | Generator shutdown timeout               | After V <sub>CC</sub> exceeds V <sub>CC_ON</sub> &<br>V <sub>FB</sub> < V <sub>FB_HVSTUPOFF</sub> | 80   | 100  | 120  | ms   |

| I <sub>HV OFF</sub>        | OFF-state current consumption            | V <sub>HV</sub> = 400 V                                                                           |      | 20   | 25   | μA   |

|                            |                                          |                                                                                                   |      |      |      | P2.  |

| V <sub>HVPK BO</sub>       | Brownout threshold                       | V <sub>HV</sub> peak voltage falling <sup>(1)</sup>                                               | 94   | 100  | 106  | v    |

| V <sub>HVPK_BI</sub>       | Brown-in threshold                       | V <sub>HV</sub> peak voltage rising <sup>(1)</sup>                                                | 106  | 114  | 121  | V    |

| T <sub>DB_ACBO</sub>       | Brownout debounce time                   |                                                                                                   | 505  | 630  | 755  | ms   |

| - DB_ACBO                  |                                          |                                                                                                   | 505  | 030  | 100  | 1115 |

### Table 5. Electrical characteristics

| Symbol                 | Parameter                                           | Test Condition                                                        | Min.  | Тур.  | Max.  | Unit |

|------------------------|-----------------------------------------------------|-----------------------------------------------------------------------|-------|-------|-------|------|

|                        |                                                     | First time V <sub>CC</sub> > V <sub>CC_ON</sub>                       | 0.8   | 1     | 1.2   | ms   |

| T <sub>DB_ACBI</sub>   | Brown-in debounce time                              |                                                                       | 32    | 40    | 48    | ms   |

| -CAPACITOR DISC        | HARGE FUNCTION                                      |                                                                       |       |       |       |      |

| V <sub>HV_MIN</sub>    | Peak residual voltage                               | I <sub>HV_DIS</sub> > 5 mA                                            |       |       | 45    | V    |

| I <sub>HV_DIS</sub>    | Discharge current                                   | V <sub>HV</sub> = 45 V                                                | 5     |       |       | mA   |

| T <sub>DECT_XCAP</sub> | Detection time                                      |                                                                       | 51    | 64    | 77    | ms   |

| ERROR AMPLIFIER        |                                                     |                                                                       |       |       |       |      |

|                        |                                                     | T <sub>j</sub> = 25 °C                                                | 2.47  | 2.5   | 2.53  | V    |

| V <sub>REF</sub>       | Voltage feedback input threshold                    | 10 V < V <sub>CC</sub> < 24.5 V(1)                                    | 2.45  |       | 2.57  | V    |

| I <sub>FB</sub>        | Input bias current                                  | V <sub>FB</sub> = 0 to 3 V                                            | -0.1  | 0     | 0.1   | μA   |

| V <sub>FBCLAMP</sub>   | Internal clamp level                                | I <sub>FB</sub> = 1 mA                                                | 3.0   | 3.3   |       | V    |

| gm                     | Transconductance gain                               | V <sub>REF</sub> -150 mV < V <sub>FB</sub> < V <sub>REF</sub> +150 mV | 160   | 200   | 240   | μS   |

| R <sub>O</sub>         | Output impedance                                    |                                                                       | 5     |       |       | MΩ   |

|                        | Source current                                      | V <sub>COMP</sub> = 3 V, V <sub>FB</sub> = 1.9 V                      | 0.7   | 1     | 1.45  | mA   |

| ICOMP                  | Sink current                                        | V <sub>COMP</sub> = 3 V, V <sub>FB</sub> = 3.0 V                      | 0.7   | 1     | 1.45  | mA   |

|                        | Upper saturation voltage                            | I <sub>SOURCE</sub> = 0.2 mA                                          | 5.0   |       |       |      |

| V <sub>COMP</sub>      | Lower clamp voltage                                 | V <sub>FB</sub> = 3.0 V                                               | 0.8   |       | 0.9   | V    |

| DYNAMIC (D_OVP)        | and STATIC (S_OVP) OVERVOLTAGE                      | PROTECTIONS                                                           |       |       |       |      |

| ,                      | Burst mode threshold                                | Vellere felling(1)                                                    | 0.95  | 1.00  | 4.05  |      |

| V <sub>COMP_S</sub>    | S_OVP (Static OVP)                                  | Voltage falling <sup>(1)</sup>                                        |       |       | 1.05  | V    |

| V <sub>COMP_R</sub>    | Restart threshold                                   | Voltage rising <sup>(1)</sup>                                         | 1     | 1.05  | 1.1   | v    |

| COMP_R                 | after S_OVP                                         |                                                                       | -     | 1.00  | 1.1   | v    |

| V <sub>FB_S</sub>      | D_OVP disable threshold                             | 10 V < V <sub>CC</sub> < 24.5 V                                       | 2.595 | 2.675 | 2.755 | V    |

| V <sub>FB_R</sub>      | Restart threshold                                   | 10 V < V <sub>CC</sub> < 24.5 V                                       | 2.44  | 2.55  | 2.65  | v    |

|                        | after D_OVP                                         |                                                                       |       |       |       |      |

| DISABLE                |                                                     |                                                                       |       |       |       |      |

| V <sub>COMP_DIS</sub>  | Disable threshold                                   | Voltage falling <sup>(1)</sup>                                        | 0.65  | 0.7   | 0.75  | V    |

| V <sub>COMP</sub> _EN  | Enable threshold                                    | Voltage rising <sup>(1)</sup>                                         | 0.85  | 0.9   | 0.95  | V    |

| ICOMP_DIS              | Pull-up current at disable                          |                                                                       | 8     | 12    | 16    | μA   |

| CURRENT SENSING        | 3                                                   |                                                                       |       |       | 1     |      |

| I <sub>CS</sub>        | Leakage bias current                                | V <sub>CS</sub> = -0.5 V                                              |       | 15    | 21    | μA   |

|                        |                                                     | V <sub>CS</sub> = 0.235 V                                             | 7.5   | 10    | 14    | μA   |

| V <sub>CS_OFS</sub>    | CS level shifter offset                             | CS = 0 V                                                              | 3     | 10    | 17    | mV   |

| V <sub>CS_GAIN</sub>   | CS level shifter gain                               | C = -0.5 V                                                            | 0.94  | 0.98  | 1.02  | V/V  |

| V <sub>CS_OCP1</sub>   | 1 <sup>st</sup> level Overcurrent threshold         |                                                                       | -510  | -490  | -470  | mV   |

| T <sub>SS_OCP1</sub>   | 1 <sup>st</sup> level OCP threshold ramp<br>up time |                                                                       | 104   | 130   | 156   | ms   |

| T <sub>BLK</sub>       | Leading edge blocking                               | HV > 73 V rising                                                      | 120   | 150   | 180   | ns   |

| ' BLK                  | Leading edge blanking                               | HV < 45 V falling                                                     | 235   | 310   | 335   | ns   |

| td <sub>(H-L)</sub>    | Delay to output                                     |                                                                       |       |       | 110   | ns   |

| V <sub>CS_OCP2</sub>   | 2 <sup>nd</sup> level Overcurrent threshold         |                                                                       | -0.80 | -0.75 | -0.70 | V    |

| V <sub>CS_ZCD</sub>    | Zero current threshold                              |                                                                       | -15   | -10   | -5    | mV   |

| Symbol                 | Parameter                               | Test Condition                                              | Min.  | Тур.  | Max.  | Uni |

|------------------------|-----------------------------------------|-------------------------------------------------------------|-------|-------|-------|-----|

| CURRENT SENSE D        | ISCONNECTION                            |                                                             |       |       |       |     |

| V <sub>CSD</sub>       | Current Sense disconnection threshold   | Voltage rising                                              | 165   | 200   | 235   | mV  |

| T <sub>CSD_DB</sub>    | Disconnection<br>debounce time          |                                                             | 8     | 10    | 12    | μs  |

| EQUIVALENT MULTI       |                                         |                                                             |       |       |       |     |

|                        |                                         | V <sub>HVPK</sub> < 200 V <sup>(1)</sup>                    | 0.405 | 0.44  | 0.475 | V/V |

| K <sub>M</sub>         | Equivalent multiplier gain              | V <sub>HVPK</sub> > 235 V <sup>(1)</sup>                    | 0.092 | 0.10  | 0.108 | V/V |

| THD CCM-OPTIMIZE       | R                                       |                                                             |       |       |       |     |

| K <sub>CCM</sub>       |                                         |                                                             | 0.51  | 0.55  | 0.59  | н   |

|                        | E PROTECTION/EXTERNAL BURS              | T MODE (EBM)                                                |       |       |       |     |

|                        | Feedback failure protection             | Voltage falling <sup>(1)</sup>                              | 460   | 500   | 540   | mV  |

| $V_{FB}_{FF/EBM}$      | (on FB) / External burst mode threshold | Hysteresis                                                  |       | 50    |       | mV  |

| T <sub>FF/EBM_DB</sub> | FFP/EBM debounce time                   |                                                             | 1.25  | 1.8   | 2.35  | μs  |

|                        | FB current during EBM                   | VFB < VFB FF/EBM                                            | 70    | 100   | 135   | μA  |

| I <sub>FB_EBM</sub>    | FB current at exit EBM                  | V <sub>FB FF/EBM</sub> < V <sub>FB</sub> < V <sub>REF</sub> | 0.75  | 1     | 1.25  | mA  |

|                        | ENCY                                    |                                                             |       |       |       |     |

|                        | Switching frequency                     | T <sub>ON</sub> = 9μs, V <sub>HVPK</sub> < 200 V            |       |       |       |     |

|                        | (L4986A)                                | $T_{ON} = 3\mu s, V_{HVPK} > 235 V$                         | 60    | 65    | 71    | kH: |

| F <sub>SW</sub>        | Switching frequency                     | T <sub>ON</sub> = 4.5µs, V <sub>HVPK</sub> < 200 V          |       |       |       |     |

|                        | (L4986B)                                | T <sub>ON</sub> = 1.5µs, V <sub>HVPK</sub> > 235 V          | 120   | 130   | 142   | kH: |

| MAXIMUM ON-TIME        |                                         |                                                             |       |       |       |     |

|                        |                                         | L4986A                                                      | 32    | 40    | 50    | μs  |

| T <sub>ON_MAX</sub>    | Maximum on-time                         | L4986B                                                      | 16    | 20    | 26    | μs  |

| MINIMUM OFF-TIME       | · ·                                     | · · ·                                                       | '     |       |       |     |

| Toss                   | Minimum off-time                        | L4986A                                                      | 0.75  | 1.0   | 1.35  | μs  |

| T <sub>OFF_MIN</sub>   |                                         | L4986B                                                      | 0.35  | 0.5   | 0.75  | μs  |

| GATE DRIVER            |                                         |                                                             |       |       |       |     |

| V <sub>OL</sub>        | Output low voltage                      | I <sub>sink</sub> = 200 mA                                  |       |       | 0.7   | V   |

| ·OL                    | Supurion voltage                        | I <sub>sink</sub> = 5 mA                                    |       |       | 0.02  | V   |

|                        |                                         | 15V <vcc<24.5 i<sub="" v,="">source = 5mA</vcc<24.5>        | 11    | 12    | 13    | V   |

| V <sub>OH</sub>        | Output high voltage                     | V <sub>CC</sub> = 9 V,                                      | 7.85  |       |       | v   |

|                        |                                         | I <sub>source</sub> = 5 mA                                  | 7.00  |       |       | v   |

| I <sub>srcpk</sub>     | Peak source current                     |                                                             |       | -0.7  |       | Α   |

| I <sub>snkpk</sub>     | Peak sink current                       |                                                             |       | 1.5   |       | Α   |

| t <sub>f</sub>         | Voltage fall Time                       | V <sub>GD</sub> from 8 V to 1 V                             | 3     | 7     | 15    | ns  |

| tr                     | Voltage rise Time                       | V <sub>GD</sub> from 1 V to 8 V                             | 5     | 10    | 15    | ns  |

|                        | UVLO saturation                         | $V_{CC}$ = 0 V to $V_{CC_ON}$ , $I_{sink}$ = 1mA            |       |       | 1.1   | V   |

| POWER GOOD             | - 1                                     |                                                             |       | 1     |       |     |

| V <sub>PGOOD_ON</sub>  | Power good turn-on threshold            | Voltage falling <sup>(1)</sup>                              | 2.300 | 2.375 | 2.450 | V   |

| V <sub>PGOOD_OFF</sub> | Power good turn-off threshold           | Voltage falling <sup>(1)</sup>                              | 1.210 | 1.250 | 1.290 | V   |

| T <sub>PGOOD_DB</sub>  | Debounce time                           | Voltage rising on FB                                        | 40    | 50    | 60    | μs  |

| Symbol                | Parameter           | Test Condition                  | Min. | Тур. | Max. | Unit |

|-----------------------|---------------------|---------------------------------|------|------|------|------|

|                       |                     | Voltage falling on PG_IN        |      |      |      |      |

| VPGOOD_CLAMP          | Clamp voltage PG_IN | I <sub>PG_IN</sub> = 1 mA       | 3.0  | 3.3  |      | V    |

| I <sub>PG_IN</sub>    | Leakage             | V <sub>PG_IN</sub> > 200 mV     |      | 0.1  | 0.2  | μA   |

| V <sub>PG_OUT_L</sub> | PG_OUT low voltage  | I <sub>SINK</sub> = 3 mA        |      |      | 0.28 | V    |

| I <sub>PG_OUT</sub>   | Leakage             | $V_{PG_{OUT}} = V_{CC} - 0.2 V$ |      |      | 0.15 | μA   |

1. Parameters tracking each other.

2. The VCC pin is self-limited by an internal clamp when the device is in switching modality.

3. Equivalent to just before burst-mode condition.

4. Equivalent to full-load condition.

#### 5 Application information

#### 5.1 Theory of operation

The L4986A/B implements a conventional peak current mode control, based on fixed-off-time (FOT) control technique, with some proprietary circuitries that permit to ideally achieve the same performance of the more complex/expensive average current mode control.

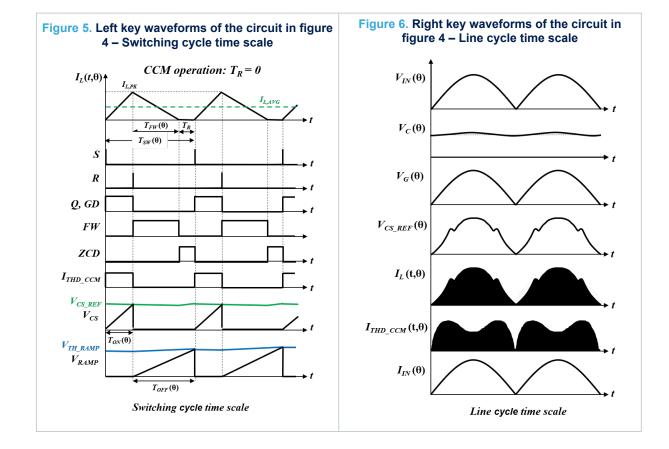

Referring to Figure 4. Control loop connections, the power switch on-time (T<sub>ON</sub>) is programmed by the output voltage control loop comparing the current sense signal V<sub>CS</sub> with the internal current reference V<sub>CS REF</sub> in order to keep the V<sub>OUT</sub> regulation; whereas the power switch off-time (T<sub>OFF</sub>) is programmed by the "OFF-TIME modulator" circuitry in order to keep quasi-fixed the switching frequency FSW in all operating conditions (see Section 5.2 OFF-time modulator for more details).

#### $V_{IN}(\theta) = V_{in,pk} \sin \theta$ $\vec{I_{IN}(\theta)}$ OUT м C<sub>IN</sub> $V_{AC}$ $I_L(\theta)$ Self-supply Ĩ ¥ VCC $\widetilde{\mathcal{C}}$ 1 -optin CCM Z.C.D. X-CAP F₩↓ ↓*ZCD* ↓ ZCD COM THD-optimize DCM Vin & multiplier GD <u>< ПП</u> Constant F<sub>SW</sub> GND (OFF TIME) Vauva ( $\theta$ )

#### Figure 4. Control loop connections

The trans-conductance Error Amplifier V/A compares a portion of the output voltage V<sub>OUT</sub>, brought at its inverting input externally available on pin FB via the resistor divider R<sub>3</sub>-R<sub>4</sub>, with an accurate internal reference V<sub>REF</sub> (2.5 V typ.) connected to the non-inverting input, and generates an error signal V<sub>C</sub> proportional to their difference. If the bandwidth of the error amplifier, essentially determined by the frequency compensation network connected between pin COMP and ground, is narrow enough - typically below 20 Hz - and a steady-state operation is assumed, the V<sub>C</sub> error signal available at pin COMP can be regarded as a DC level, at least as a first approximation. The V<sub>C</sub> voltage is then used by the "Vin & multiplier estimator" circuitry that, based also on the FW and ZCD signals (see Figure 5 and Figure 6 for more details), generates a voltage expressed by: **Equation 1**

$$V_G\left(\theta\right) = V_C \ K_1 \ \frac{V_{IN}(\theta)}{V_{OUT}}$$

where K<sub>1</sub> is the circuitry gain (constant term) and  $V_{IN}(\theta) = V_{in,pk} \sin \theta$  (with  $0 \le \theta \le \pi$ , as a result of the rectification operated by the input bridge) is the instantaneous line input voltage.

Equation 1 shows as the  $V_G(\theta)$  voltage is proportional to the  $V_{IN}(\theta)$  input voltage and to the  $V_C$  control voltage like in a standard current-mode PFC, but without using the standard multiplier block and without the AC line sensing.

The V<sub>G</sub>( $\theta$ ) voltage is then managed by the "THD-DCM optimizer" circuitry that acts as a simple gain (K<sub>2</sub>) in CCM operation whereas in DCM operation opportunely shapes the V<sub>G</sub>( $\theta$ ) voltage in order to achieve ideally sinusoidal

Considering the CCM operation, the  $V_{CS\_REF}(\theta)$  voltage is then expressed by:

#### Equation 2

input current.

where  $K_M = K_1 K_2$  is the equivalent multiplier gain (see Electrical characteristics table for details).

The internal current reference voltage  $V_{CS\_REF}(\theta)$  is then compared with the current sense  $V_{CS}(\theta)$  pin voltage (which is internally translated due to negative inductor current sensing) that is opportunely shaped by the "THD-CCM optimizer" in order to achieve sinusoidal input current in CCM operation.

In particular, referring to Figure 4 and Figure 5 during the power switch-on time the "THD-CCM optimizer" circuitry sources a current  $I_{THD\_CCM}(\theta)$  to the CS pin, generating a voltage across the external  $R_{THD\_CCM}$  resistor that is subtracted to the inductor current sense voltage  $R_S I_L(\theta)$ .

The resulting  $V_{CS}(\theta)$  voltage, at external power switch turn-off condition, is then:

#### **Equation 3**

$V_{CS}(\theta) = R_S I_{L,PK}(\theta) - R_{THD\_CCM} I_{THD\_CCM}(\theta) = V_{CS\_REF}(\theta)$

where the sourced  $I_{THD}$  <sub>CCM</sub>( $\theta$ ) current is:

$V_{CS\_REF}(\theta)^{CCM} = V_G(\theta) K_2 = \frac{K_M}{V_{OUT}} V_C V_{IN}(\theta)$

#### **Equation 4**

$I_{THD\_CCM}(\theta) = \frac{L_P}{2 K_{CCM}} \Delta I_L(\theta)$ L<sub>P</sub> is the inductor value,  $\Delta I_L(\theta)$  is the inductor current ripple, K<sub>CCM</sub> (0.55 typ.) is the circuitry gain.

(3)

(2)

5

(5)

(6)

(7)

(8)

(9)

(10)

(11)

Now considering that the input current  $I_{IN}(\theta)$  of the converter is the average value of the inductor current in a switching cycle results: **Equation 5**

$$I_{IN}(\theta)^{CCM} = I_{L,PK}(\theta) - \frac{\Delta I_L(\theta)}{2}$$

Selecting the THD-CCM optimizer resistor equal to: **Equation 6**

$I (0)^{DCM} - 1 I (0)^{TON}(\theta) + T_{FW}(\theta)$

$$R_{THD\_CCM} = K_{CCM} \frac{R_S}{L_P}$$

and replacing equations #2 and #4 in equation #3, after some calculations the inductor peak current results: **Equation 7**

$$I_{L,PK}(\theta) = \frac{1}{R_S} \frac{K_M}{V_{OUT}} V_C V_{IN}(\theta) + \frac{\Delta I_L(\theta)}{2}$$

Finally, replacing equation #7 in equation #5, the input current of the converter results: **Equation 8**

$$I_{IN}(\theta)^{CCM} = \frac{1}{R_S} \frac{K_M}{V_{OUT}} V_C V_{IN}(\theta)$$

which is sinusoidal and in phase with the  $V_{IN}(\theta)$  input voltage (ideally zero-THD and unity-PF). Considering the DCM operation ( $T_R>0$ ), through geometrical consideration, the input current  $I_{IN}(\theta)$  of the converter can be expressed by:

**Equation 9**

$$T_{IN}(\theta) = \frac{1}{2} T_{L,PK}(\theta) \frac{1}{T_{ON}(\theta) + T_{FW}(\theta) + T_{R}(\theta)}$$

Equation #9 shows that the term TR>0 introduces distortion if  $I_{L,PK}(\theta)$  has a sinusoidal shape like in a standard PFC. Referring to Figure 4, the sinusoidal voltage  $V_G(\theta) = V_C K_1 \frac{V_{IN}(\theta)}{V_{OUT}}$  is then opportunely shaped by the

'THD-DCM" optimizer block, which generates the current reference voltage expressed by: **Equation 10**

$$V_{CS\_REF}(\theta)^{DCM} = V_G(\theta) \frac{T_{ON}(\theta) + T_{FW}(\theta) + T_R(\theta)}{T_{ON}(\theta) + T_{FW}(\theta)}$$

Replacing equation #1 in equation #10, and considering that in DCM operation the peak of the inductor current is  $I_{L,PK}(\theta) = \Delta I_L(\theta)$ , after some calculations results:

Equation 11

$$I_{IN}(\theta)^{DCM} = \frac{1}{R_S} \frac{K_M}{V_{OUT}} V_C V_{IN}(\theta)$$

which is sinusoidal and in phase with the  $VI_N(\theta)$  input voltage (ideally zero-THD and unity-PF), and it has the same gain like in CCM operation.

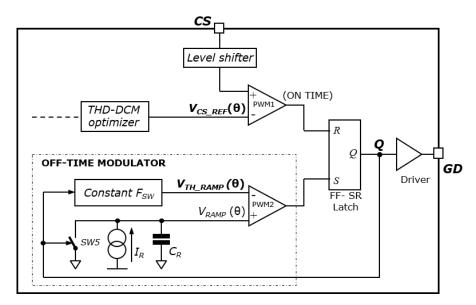

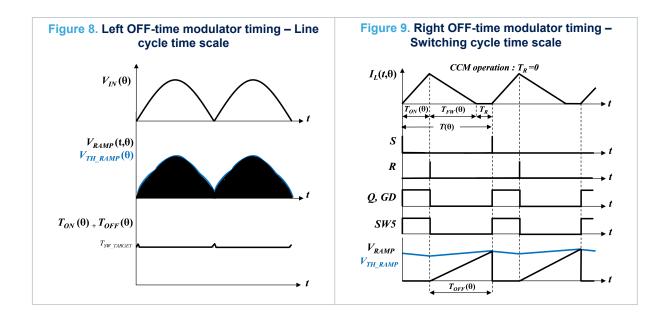

#### 5.2 OFF-time modulator

The device embeds a novel OFF-time modulator which is able to achieve quasi-fixed switching frequency in all operating conditions (CCM and DCM operation) and independent from the input/output voltage, the load conditions and the converter's parasitic as the existing modulators.

#### Figure 7. OFF-time modulator - details

Referring to Figure 7 , once the power switch ON-time is ended (Q signal goes low) the internal switch SW5 is open and the constant current generator  $I_R$  starts to charge linearly the capacitor  $C_R$ . The resulting voltage  $V_{RAMP}$  is compared with the voltage  $V_{TH\_RAMP}$ , which is generated by the "Constant  $F_{SW}$ " circuitry based on the Q signal duration ( $T_{ON}$ ). As soon as the ramp voltage  $V_{RAMP}$  reaches the  $V_{TH\_RAMP}$  voltage, the flip-flop is set and the external power switch is turned on (Q signal goes high).

In other words, the power switch off-time ( $T_{OFF}$ ) is modulated based on the on-time information ( $T_{ON}$ ) to keep cycle-by-cycle constant the resulting switching frequency ( $F_{SW}$ =1/ $T_{SW}$  TARGET):

T<sub>OFF</sub> = T<sub>SW\_TARGET</sub> - T<sub>ON</sub>.

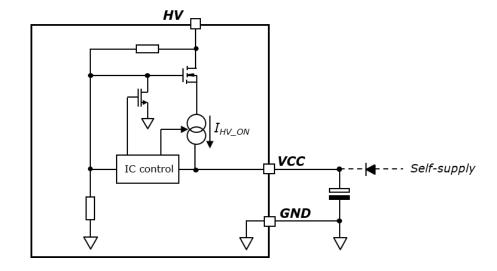

### 5.3 High voltage startup

The device embeds a High Voltage (HV) start-up circuitry, based on a high voltage N-channel FET as shown in Figure 10, in order to supply the IC during the initial start-up phase before the self-supply winding is operating.

#### Figure 10. Embedded high voltage start-up circuitry

As soon as the voltage on the HV pin is higher than  $V_{HV\_START}$  (29 V typ.), the HV start-up circuitry turns on and starts to source an  $I_{HV\_ON}$  current (7 mA typ.). This current, minus the device consumption  $I_{START\_UP}$  before startup (400 µA typ.), charges the external bypass capacitor connected between VCC pin and ground increasing its voltage almost linearly up to the device turn-on threshold  $V_{CC\_ON}$  (14 V typ.). To protect the HV-start-up circuitry from excessive power consumption, e.g. for a short-circuit on the VCC pin, the  $I_{HV\_ON}$  current sourced is 1 mA typical till the VCC pin voltage is lower than  $V_{CC\_SO}$  (1 V typ.).

Once the VCC pin voltage reaches  $V_{CC_ON}$  the device starts operating and to guarantee a reliable startup of the system, the HV current generator  $I_{HV_ON}$  is kept on till the output voltage reaches 70% typ. of the programmed value (FB pin higher than  $V_{FB_HVSTUP}$  threshold). To protect the HV-start-up circuitry from excessive power consumption, e.g. in case of an overcurrent request, the HV current generator is in any case automatically turned off after the  $T_{TOUT}$  timeout (100 ms typ.)

After the start-up phase, the system application should guarantee  $V_{CC} > V_{CC_OFF}$ . In fact, if the VCC pin voltage drops to  $V_{CC_OFF}$  the device shutdown and the HV-start-up is turned on to bring the VCC pin to a voltage  $V_{CC_ON}$  and restart the operations performing the soft-start.

## 5.4 Input line discharge (X-cap discharge function)

In order to guarantee the safety regulations such as IEC 61010-1/IEC 62368-1 without using the traditional discharge resistor in parallel to the X-capacitor, and thus saving also the associated power losses enabling ultra-low consumption in standby conditions, the device embeds an internal logic circuit that detects when the unit has been detached from the power line; if this event occurs then the high voltage start-up generator is turned on to discharge the X capacitors of the EMI filter to a safe level.

In particular, after a detection time  $T_{DECT\_XCAP}$  (64 ms typ.) from the AC mains disconnection, the X-cap discharge operation is triggered and the internal HV current generator is turned on: a discharge current  $I_{HV\_ON}$  (5 mA minimum) is drawn from the HV pin ensuring the X-cap discharge until the voltage on the HV pin falls below a safe level (45 V maximum,  $V_{HV\_MIN}$  parameter in Section 4 Electrical characteristics, Table 5), within the regulation maximum discharging time.

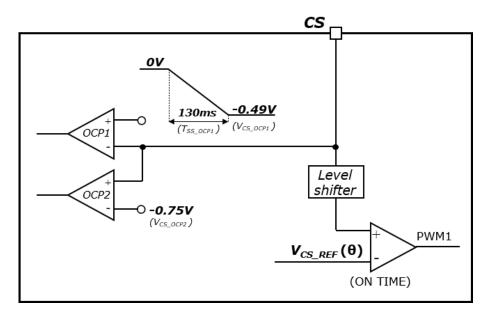

### 5.5 Soft-start

To limit the in-rush current of the converter at the startup, the device implements a soft startup increasing the peak of the inductor current from zero up to the required value programmed by the control loop to regulate the output voltage.

In particular, the device changes the reference threshold of the first overcurrent comparator (OCP1) from zero up to  $V_{CS\_OCP1}$  (-0.49 V typ.) in  $T_{SS\_OCP1}$  time (130 ms typ.), as shown in Figure 11.

#### Figure 11. Soft-start circuitry details

### 5.6 No load operation (burst-mode function)

To avoid uncontrolled rise of the output voltage at light or zero load, when  $V_{COMP} < V_{COMP}_S$  (1 V typ.) the device stops the switching activity and reduces its power consumption. As soon as the  $V_{COMP} > V_{COMP}_R$  (1.05 V typical and in tracking with the threshold  $V_{COMP}_S$ ) the device restarts the switching activity.

If the burst-mode condition is triggered when the gate driver GD is "high", the device completes the current ON-time and the system stoppage takes place after GD falling edge.

During the burst-mode operation, the system application should guarantee  $V_{CC} > V_{CC_OFF}$ . In fact, if the VCC pin voltage drops down to  $V_{CC_OFF}$ , the device shutdown and the HV-startup is turned on to bring the VCC pin to a voltage  $V_{CC_ON}$  and restart the operation performing the soft-start.

## 5.7 Idle operation (external burst-mode function)

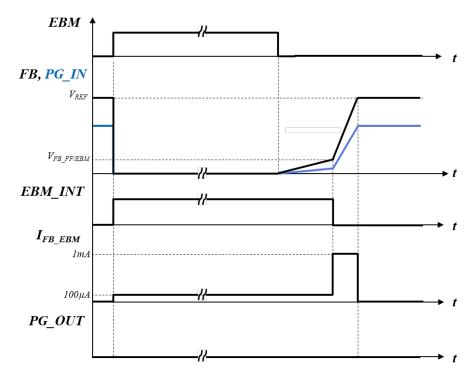

The FB pin can be used to implement an external burst-mode (EBM), forcing the pin lower than the internal threshold  $V_{FB\_FF/EBM}$  (500 mV typ.): the switching activity is stopped and the IC power consumption is reduced (Error Amplifier is also turned off and the COMP pin is forced to "high impedance"). The device restarts switching, without implementing the soft-start, as soon as the FB voltage exceeds the  $V_{FB\_FF/EBM}$  threshold by 50 mV typ. De-bounce time  $T_{FF/EBM\_DB}$  (1.8 µs typ.) is provided to avoid false triggering. Referring to Figure 12, it is worth noting that as soon as the device enters the EBM state (the internal signal EBM\_INT is high) a weak pull-up current  $I_{FB\_EBM}$  (100 µA typ.) is sourced from the FB pin in order to speed up the FB voltage rising edge when the external pull-down is released. In addition, once the FB voltage exceeds  $V_{FB\_FF/EBM} + 50$  mV the  $I_{FB\_EBM}$  current of 100 µA is increased to 1 mA till the FB pin voltage reaches the final target of 2.5 V (internal  $V_{REF}$ ). When using the EBM function, the suggested value of the FB filter capacitor  $C_{FB}$  is 3.3 nF.

### Figure 12. External Burst-Mode (EBM) function – circuit details

During the external burst-mode condition (FB <  $V_{FB\_FF/EBM}$ ), the system application should guarantee  $V_{CC}$  >  $V_{CC\_OFF}$  to minimize the power consumption. In fact, in case the VCC pin voltage approaches the device turn-off threshold the internal HV-start-up is turned on to bring  $V_{CC}$  voltage to the turn-on threshold  $V_{CC}$  on.

It is also worth noting that during this condition the PG\_OUT state is "frozen" to avoid false PGOOD deactivation (PG\_IN is proportional to FB pin that is forced low).

#### Figure 13. External Burst-Mode (EBM) function – timing

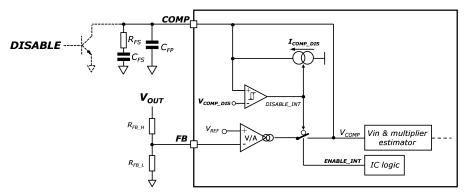

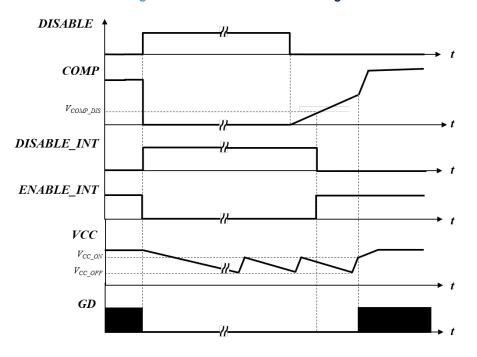

### 5.8 Disable operation (DISABLE function)

Forcing the COMP pin lower than the internal threshold  $V_{COMP_DIS}$  (0.7 V typ.), the device stops the operation and enters into low power consumption. The Error Amplifier is turned off and a weak internal pull-up current  $I_{COMP_DIS}$  (10 µA typ.) is activated. De-bounce time  $T_{COMP_DIS_DB}$  (50 µs typ.) is provided to avoid false triggering.

Referring to Figure 14, releasing the external pull-down the internal pull-up current ICOMP\_DIS charges the compensation network connected between COMP pin and ground and the COMP voltage starts to increase. As soon as the VCC pin voltage reaches the  $V_{CC_ON}$  turn-on threshold, the device checks the COMP pin: if the COMP pin is higher than the enable threshold  $V_{COMP_EN}$  (0.9 V typ.) the device restarts the operation implementing the soft-start, otherwise it waits for the next  $V_{CC_ON}$  crossing to check the COMP pin value.

Figure 14. DISABLE function – circuit details

During the disable condition, due to the absence of energy transferred from the auxiliary winding, the internal HV-startup is intermittently turned on to keep the device supplied between  $V_{CC}$  OFF and  $V_{CC}$  ON.

Figure 15. DISABLE function – timing

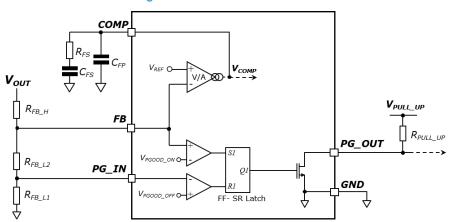

### 5.9 Power Good (PGOOD function)

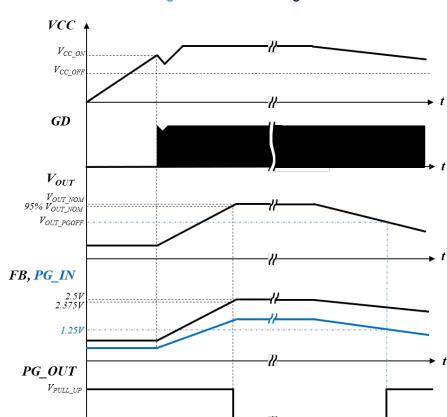

The PG\_IN is an adjustable input comparator suitable for monitoring the PFC output voltage and, accordingly, driving a logic signal exiting from PG\_OUT pin (open drain).

The PG\_OUT is actively pulled to ground once the IC is turned on and the FB pin voltage exceeds the internal threshold  $V_{PGOOD_ON}$  (2.375 V typ.). Then, as soon as the PG\_IN input voltage is lower than the internal threshold  $V_{PGOOD_OFF}$  (1.250 V typ.), the PG\_OUT pin is set to high impedance.

De-bounce time T<sub>PGOOD DB</sub> (50 µs typ.) is provided to avoid false activation / deactivation.

The PGOOD functionality is also linked to the operating status: PG\_OUT is set to high impedance if the device detects the CS disconnection.

Monitoring of the output voltage can be realized using the same resistors divider used to program the output voltage V<sub>OUT</sub>, as shown in Figure 16.

#### Figure 16. PGOOD connections

As soon as the VCC pin reaches the  $V_{CC_ON}$  turn-on threshold, the device starts up and the PG\_OUT pin is internally pulled-low as soon as the output voltage reaches 95% of the programmed voltage  $V_{OUT}$  (e.g.  $V_{PGOOD_ON} = 2.375$  V vs.  $V_{REF} = 2.500$  V target reference of the output voltage control loop).

Once the PG\_OUT pin is pulled low the device starts to monitor the PG\_IN pin voltage, which is proportional to the output voltage.

е

### Equation 12

$$V_{PG\_IN} = V_{OUT} \frac{R_{FB\_L1}}{R_{FB\_H} + R_{FB\_L}}$$

where  $R_{FB_H}$  and  $R_{FB_L} = R_{FB_{L1}} + R_{FB_{L2}}$  resistors are previously selected to program the desired nominal output voltage  $V_{OUT_NOM}$ .

As soon as the PG\_IN input voltage becomes lower than the internal threshold  $V_{PGOOD_OFF}$  (1.250 V typ.), the PG\_OUT is deactivated: the corresponding output voltage  $V_{OUT_PGOFF}$  can be then programmed selecting opportunely the  $R_{FB_L1}$  resistor:

#### **Equation 13**

$$R_{FB\_L1} = \frac{V_{PGOOD\_OFF}}{V_{OUT\_PGOFF}} \left( R_{FB\_H} + R_{FB\_L} \right)$$

(13)

(12)

#### Figure 17. PGOOD timing

## 5.10 Protections

A comprehensive set of protections is embedded to ensure a high level of reliability of the final application without adding extra components and/or circuitry.

### 5.10.1 AC brown-in (BI function)

At startup, as soon as the VCC pin voltage reaches the  $V_{CC_ON}$  turn-on threshold the device monitors the AC line input voltage through the HV pin and starts the operation if the input voltage is higher than the  $V_{HVPK_BI}$  brown-in threshold (around 81 Vac).

De-bounce time  $T_{DB\_ACBI}$  of 1 ms typ. is provided to avoid false triggering at the first startup. After that, the de-bounce time is increased to 40 ms.

#### 5.10.2 AC brownout (BO function)

During the normal operation, in order to protect the PFC pre-regulator from excessive RMS current, if the AC line voltage falls below the  $V_{HVPK\_BO}$  brownout threshold (around 71 Vac) for at least 630 ms typ. (see  $T_{DB\_ACBO}$  parameter in Table 5. Electrical characteristics), the switching activity is stopped.

A recycle of  $V_{CC}$  between the turn-off threshold ( $V_{CC_OFF}$ ) and the turn-on threshold ( $V_{CC_ON}$ ) is needed to restart the converter.

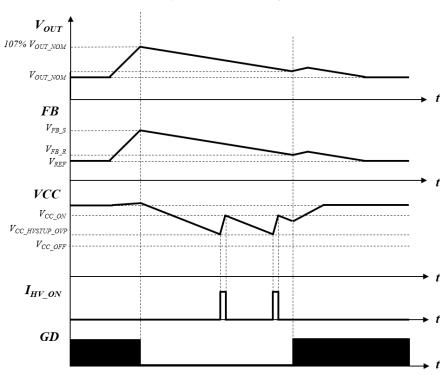

### 5.10.3 Output overvoltage (OVP function)

To limit an output voltage overshoot, e.g. due to a heavy load release or at startup with light-load, the device stops the switching activity as soon as the instantaneous output voltage  $V_{OUT}$  is higher than 7% typ. in respect to the programmed value.

In fact, the device detects an overvoltage condition monitoring the FB pin which is proportional to the instantaneous value of the output voltage VOUT and in steady-state conditions sits at the internal reference of the error amplifier ( $V_{REF}$  = 2.5 V).

As soon as the FB voltage exceeds the steady-state value by 7% (VFB > VFB\_S), the switching activity is stopped until it gets back close to it ( $V_{FB} < V_{FB_R}$ ).

De-bounce time  $T_{DOVP\ DB}$  (50 µs typ.) is provided to avoid false activation of the protection.

During the OVP condition, to avoid undesired IC shutdown, as soon as the VCC pin voltage falls below the  $V_{CC\_HVSTUP\_OVP}$  threshold (11.5 V typ.) the internal HV-startup is turned on to bring  $V_{CC}$  voltage to the turn-on threshold  $V_{CC\_ON}$ .

Figure 18. OVP timing

#### 5.10.4 Overcurrent (OCP1 function)

To limit the peak inductor current in case of extra request (e.g. heavy load changes), the device implements a cycle-by-cycle overcurrent protection. The device monitors the CS pin during the power switch on-time and as soon as the voltage on the CS pin goes below  $V_{CS\_OCP1}$  (-0.49 V typ.), the internal overcurrent comparator is triggered and terminates the conduction cycle of the power switch before the normal PWM circuit does. In this way, the peak inductor current is limited to a maximum of 0.49/RS.

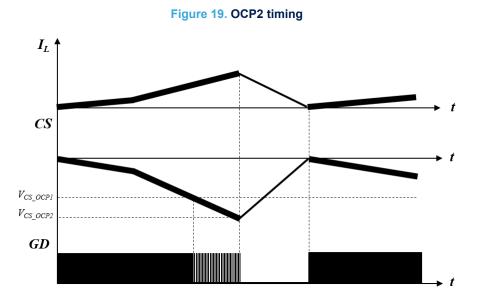

#### 5.10.5 Inductor saturation detection (OCP2 function)

A second overcurrent level set at  $V_{CS_OCP2}$  (-0.75 V typ.) detects abnormal current values (e.g. due to boost inductor saturation) and, on this occurrence for two consecutive switching cycles, activates a safety procedure that immediately stops the converter activity until the current level reaches the zero-current threshold (V<sub>CS\_ZCD</sub>).

The zero-current threshold monitor allows safe operations also during current surges occurring at power-up or after a mains dip or missing cycle; in fact it allows switching start/restart only when the overcurrent event is definitively over.

#### 5.10.6 Feedback failure detection

The device handles the possible disconnection of both output voltage feedback and input current monitoring. At startup, as soon as the VCC pin voltage reaches the  $V_{CC_ON}$  turn-on threshold, the device checks the FB and CS pins:

- if the FB pin voltage is lower than the internal V<sub>FB\_FF/EBM</sub> threshold (0.5 V typ.) a failure of the output divider resistor is assumed (e.g. R<sub>FB\_H</sub> resistor not mounted), then the device stops the switching activity and reduces its consumption.

- De-bounce time T<sub>FF/EBM\_DB</sub> (1.8µs typ.) is provided to avoid false triggering.

- if the CS pin voltage is higher than the internal V<sub>CSD</sub> threshold (200 mV typ.) a failure of the current sensing resistors is assumed (e.g. R<sub>THD\_CCM</sub> resistor not mounted and/or RS resistor burned), then the device stops the switching activity and reduces its consumption.

- De-bounce time T<sub>CSD\_DB</sub> (10 µs typ.) is provided to avoid false triggering and a recycle of V<sub>CC</sub> between the turn-off threshold (V<sub>CC\_OFF</sub>) and the turn-on threshold (V<sub>CC\_ON</sub>) is needed to restart the converter.

### 5.11 Line feedforward

To keep the maximum output power deliverable by the converter almost constant with respect to the AC input voltage, a two-level discrete voltage feedforward is integrated in the controller. Basically, the AC input voltage is monitored through the HV pin and internally compared with a fixed threshold to properly set the value of equivalent multiplier gain  $K_M$  (see Table 5. Electrical characteristics for details). The proper operation of the converter, with the right  $K_M$  multiplier gain, is guaranteed for an AC input voltage below 142 Vrms and above 166 Vrms.

# 6 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

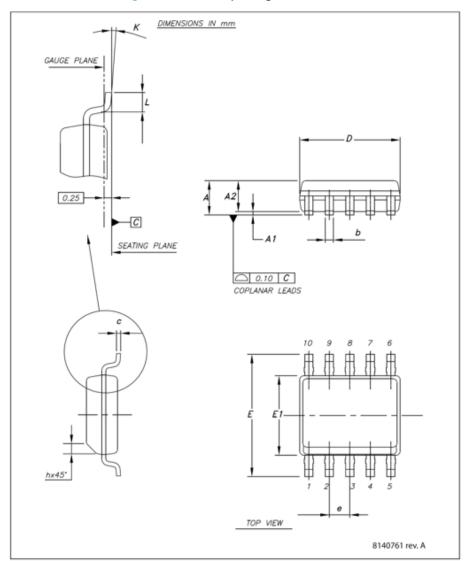

# 6.1 SSOP10 package information

#### Figure 20. SSOP10 package dimensions

### Table 6. SSO10 package mechanical data

| Symbol |      | Dimensions(mm) |      |

|--------|------|----------------|------|

| Symbol | Min. | Тур.           | Max. |

| А      | -    | -              | 1.75 |

| A1     | 0.10 | -              | 0.25 |

| Symbol | Dimensions(mm) |      |      |  |

|--------|----------------|------|------|--|

| Symbol | Min.           | Тур. | Max. |  |

| A2     | 1.25           | -    | -    |  |

| b      | 0.31           | -    | 0.51 |  |

| С      | 0.17           | -    | 0.25 |  |

| D      | 4.80           | 4.90 | 5    |  |

| E      | 5.80           | 6    | 6.20 |  |

| E1     | 3.80           | 3.90 | 4    |  |

| e      | -              | 1    | -    |  |

| h      | 0.25           | -    | 0.50 |  |

| L      | 0.40           | -    | 0.90 |  |

| К      | 0°             | -    | 8°   |  |

# 7 Ordering information

| Order code | Package | Package marking | Packaging     |

|------------|---------|-----------------|---------------|

| L4986A     | SSOP10  | L4986A          | Tube          |

| L4986B     | SSOP10  | L4986B          | Tube          |

| L4986ATR   | SSOP10  | L4986A          | Tape and reel |

| L4986BTR   | SSOP10  | L4986B          | Tape and reel |

### Table 7. Order codes

# **Revision history**

| Date        | Version | Changes                                     |

|-------------|---------|---------------------------------------------|

| 26-Jul-2021 | 1       | Initial release.                            |

| 11-Aug-2021 | 2       | Updated Table 5. Electrical characteristics |

### Table 8. Document revision history

# Contents

| 1   | Bloc   | k diagra                                        | am and typical application                    | 3  |

|-----|--------|-------------------------------------------------|-----------------------------------------------|----|

| 2   | Pin c  | connect                                         | tion and functions                            | 4  |

| 3   | Elec   | lectrical data                                  |                                               |    |

|     | 3.1    | Absolu                                          | ite maximum ratings                           | 6  |

|     | 3.2    | Therma                                          | al data                                       | 6  |

| 4   | Elect  | trical ch                                       | naracteristics                                | 7  |

| 5   | Appl   | ication                                         | information                                   | 11 |

|     | 5.1    | Theory                                          | of operation                                  |    |

|     | 5.2    | OFF-tir                                         | me modulator                                  |    |

|     | 5.3    | High vo                                         | oltage startup                                | 14 |

|     | 5.4    | Input line discharge (X-cap discharge function) |                                               |    |

|     | 5.5    | Soft-sta                                        | art                                           |    |

|     | 5.6    | No load                                         | d operation (burst-mode function)             |    |

|     | 5.7    | Idle operation (external burst-mode function)1  |                                               |    |

|     | 5.8    | Disable operation (DISABLE function)            |                                               |    |

|     | 5.9    | Power Good (PGOOD function)                     |                                               |    |

|     | 5.10   | Protections                                     |                                               |    |

|     |        | 5.10.1                                          | AC brown-in (BI function)                     |    |

|     |        | 5.10.2                                          | AC brownout (BO function)                     |    |

|     |        | 5.10.3                                          | Output overvoltage (OVP function)             |    |

|     |        | 5.10.4                                          | Overcurrent (OCP1 function).                  |    |

|     |        | 5.10.5                                          | Inductor saturation detection (OCP2 function) |    |

|     |        | 5.10.6                                          | Feedback failure detection                    |    |

|     | 5.11   | Line fe                                         | edforward                                     |    |

| 6   | Pack   | age inf                                         | ormation                                      |    |

|     | 6.1    | SSOP                                            | 10 package information                        |    |

| 7   | Orde   | ering inf                                       | formation                                     |    |

| Rev | vision | history                                         |                                               |    |

| Сог | ntents |                                                 |                                               |    |

| List of tables  |  |

|-----------------|--|

| List of figures |  |

# List of tables

| Table 1. | Pin description                  |

|----------|----------------------------------|

| Table 2. | Absolute maximum ratings         |

| Table 3. | Recommended operating conditions |

|          | Thermal data                     |

| Table 5. | Electrical characteristics       |

| Table 6. | SSO10 package mechanical data    |

| Table 7. | Order codes                      |

| Table 8. | Document revision history        |

# List of figures

| Figure 1.  | Block diagram                                                              | 3  |

|------------|----------------------------------------------------------------------------|----|

| Figure 2.  | Typical application.                                                       | 3  |

| Figure 3.  | Pin connection (top view).                                                 | 4  |

| Figure 4.  | Control loop connections                                                   | 11 |

| Figure 5.  | Left key waveforms of the circuit in figure 4 – Switching cycle time scale | 12 |

| Figure 6.  | Right key waveforms of the circuit in figure 4 – Line cycle time scale     | 12 |

| Figure 7.  | OFF-time modulator - details                                               | 14 |

| Figure 8.  | Left OFF-time modulator timing – Line cycle time scale                     | 14 |

| Figure 9.  | Right OFF-time modulator timing – Switching cycle time scale               | 14 |

| Figure 10. | Embedded high voltage start-up circuitry                                   | 15 |

| Figure 11. | Soft-start circuitry details                                               |    |

| Figure 12. | External Burst-Mode (EBM) function – circuit details                       | 17 |

| Figure 13. | External Burst-Mode (EBM) function – timing                                | 17 |

| Figure 14. | DISABLE function – circuit details                                         | 18 |

| Figure 15. | DISABLE function – timing                                                  | 18 |

| Figure 16. | PGOOD connections.                                                         | 19 |

| Figure 17. | PGOOD timing                                                               | 20 |

| Figure 18. | OVP timing                                                                 | 21 |

| Figure 19. | OCP2 timing                                                                | 22 |

| Figure 20. | SSOP10 package dimensions                                                  | 23 |

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2021 STMicroelectronics - All rights reserved