# **SMPS IC**

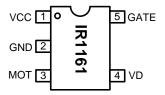

# SmartRectifier IR1161LPBF

# **SmartRectifier Control IC**

#### **Features**

- Secondary side synchronous rectification controller

- DCM, CrCM Flyback and resonant half-bridge topologies

- Direct sensing of MOSFET drain voltage up to 200V

- Max 500kHz switching frequency

- Anti-bounce logic and UVLO protection

- Micropower start-up & ultra-low quiescent current

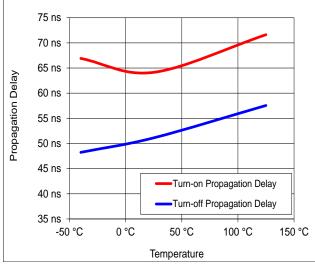

- 50ns turn-off propagation delay

- Programmable Minimum On Time

- Vcc Operating voltage range 4.75V to 18V

- Cycle by Cycle MOT Check Circuit

- Lead-free

- Compatible with 0.3W Standby, Energy Star, CECP, etc.

# **Applications**

· Charger, AC-DC adapters

# **Product Summary**

| Topology                          | Flyback,<br>Resonant Half-bridge |

|-----------------------------------|----------------------------------|

| VD                                | 200V                             |

| V <sub>CC</sub>                   | 4.75V ~ 18V                      |

| I <sub>0+</sub> & I <sub>0-</sub> | +1A & -2.5A                      |

| Turn on Propagation Delay         | 50ns (typical)                   |

| Turn off Propagation Delay        | 50ns (typical)                   |

# **Package Options**

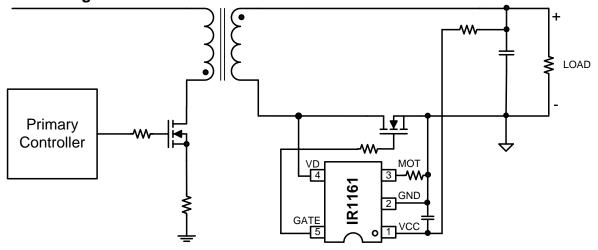

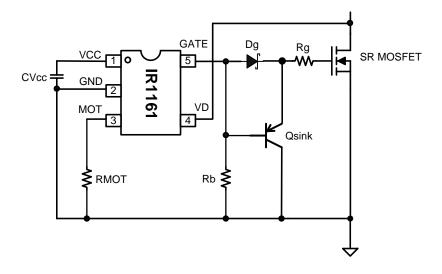

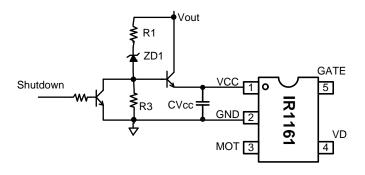

# **Application Diagram**

# **Ordering Information**

| Base Part Number     | Package Type    | Standard Pack |          | Complete Part Number |

|----------------------|-----------------|---------------|----------|----------------------|

| Daoo i ait italiiboi | r donago 1 y po | Form          | Quantity | Complete Full Humber |

| IR1161LPBF           | 5L-SOT-23       | Tape and Reel | 3000     | IR1161LTRPBF         |

2016-07-01

| Table of Contents                              | Page |

|------------------------------------------------|------|

| Ordering Information                           | 1    |

| Description                                    | 3    |

| Absolute Maximum Ratings                       | 4    |

| Electrical Characteristics                     | 5    |

| Functional Block Diagram                       | 7    |

| Input/Output Pin Equivalent Circuit Diagram    |      |

| Pin Definitions                                |      |

| Pin Assignments                                | 9    |

| Application Information and Additional Details |      |

| Package Details                                | 21   |

| Tape and Reel Details                          |      |

| Part Marking Information                       |      |

| Qualification Information                      | 25   |

## **Description**

The IR1161 is a synchronous rectification control IC designed to drive an N-Channel power MOSFET in a secondary output rectifier circuit. The MOSFET gate is switched on and off to bypass its body diode during the of the conduction period to minimize power dissipation, remaining off during the blocking period. The drain to source voltage is accurately sensed to determine the direction and magnitude of the current allowing the IR1161 to turn the MOSFET on and off at close to zero current.

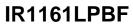

An integrated cycle-by-cycle minimum on time (MOT) protection circuit automatically detects a no load condition and turns off the gate driver output preventing negative current from flowing through the MOSFET.

Ruggedness and noise immunity are accomplished using an advanced blanking scheme and double-pulse suppression, which allows reliable operation in all operating modes.

# **Absolute Maximum Ratings**

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to GND, all currents are defined positive into any pin. The thermal resistance and power dissipation ratings are measured under board mounted and still air conditions.

| Symbol         | Definition                     | Min. | Max.                 | Units | Remarks                        |

|----------------|--------------------------------|------|----------------------|-------|--------------------------------|

| $V_{CC}$       | Supply Voltage                 | -0.3 | 20                   |       |                                |

| $V_D$          | Cont. Drain Sense Voltage      | -1   | 200                  |       |                                |

| $V_D$          | Pulse Drain Sense Voltage      | -3   | 200                  | V     |                                |

| $V_{MOT}$      | MOT Voltage                    | -0.3 | 3.5                  |       |                                |

| $V_{GATE}$     | Gate Voltage                   | -0.3 | V <sub>CC</sub> +0.3 |       | V <sub>CC</sub> =18V, Gate off |

| TJ             | Operating Junction Temperature | -40  | 150                  | °C    |                                |

| Ts             | Storage Temperature            | -55  | 150                  | C     |                                |

| $R_{	hetaJA}$  | Thermal Resistance             | _    | 212 <sup>†</sup>     | °C/W  |                                |

| P <sub>D</sub> | Package Power Dissipation      | _    | 590 <sup>†</sup>     | mW    | T <sub>AMB</sub> =25°C         |

# **Recommended Operating Conditions**

For proper operation the device should be used within the recommended conditions.

| Symbol   | Definition           | Min.             | Max. | Units |

|----------|----------------------|------------------|------|-------|

| $V_{CC}$ | Supply voltage       | 4.75             | 18   | V     |

| $V_{D}$  | Drain Sense Voltage  | -3 <sup>††</sup> | 200  | ]     |

| $T_J$    | Junction Temperature | -40              | 125  | °C    |

| Fsw      | Switching Frequency  | _                | 500  | kHz   |

††  $V_D$  -3V negative spike width  $\leq$ 100ns

# **Recommended Component Values**

| Symbol           | Component                                  | Min. | Max. | Units |

|------------------|--------------------------------------------|------|------|-------|

| R <sub>MOT</sub> | MOT pin resistor value                     | 5    | 100  | kΩ    |

| CV <sub>CC</sub> | V <sub>CC</sub> decoupling capacitor value | 1    | _    | μF    |

2016-07-01

# **Electrical Characteristics**

$V_{CC}$ =12V and  $T_A$ =25°C unless otherwise specified. The output voltage and current ( $V_O$  and  $I_O$ ) parameters are referenced to GND pin.

| Symbol                | Definition                                                     | Min. | Тур. | Max. | Units | Remarks                                            |

|-----------------------|----------------------------------------------------------------|------|------|------|-------|----------------------------------------------------|

| Supply Sec            | tion                                                           |      |      |      |       |                                                    |

| V <sub>CC</sub>       | Supply Voltage Operating Range                                 | 4.75 |      | 18   |       |                                                    |

| V <sub>CC ON</sub>    | V <sub>CC</sub> Turn On Threshold                              | 4.25 | 4.5  | 4.75 |       |                                                    |

| V <sub>CC UVLO</sub>  | V <sub>CC</sub> Turn Off Threshold<br>(Under Voltage Lock Out) | 4.15 | 4.4  | 4.65 | V     |                                                    |

| V <sub>CC HYST</sub>  | V <sub>CC</sub> Turn On/Off Hysteresis                         | _    | 0.1  |      |       |                                                    |

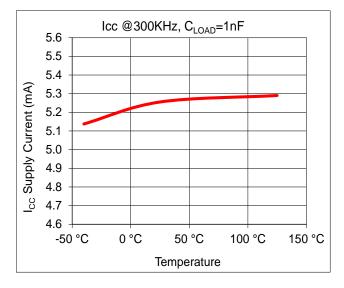

| I <sub>CC</sub>       | Operating Current                                              | _    | 5.0  | 8.0  | mA    | C <sub>LOAD</sub> =1nF,<br>f <sub>SW</sub> =300kHz |

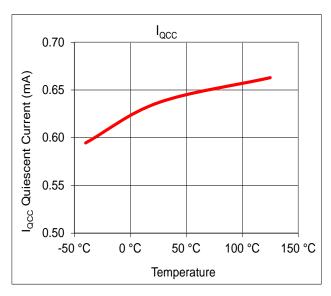

| $I_{QCC}$             | Quiescent Current                                              | _    | 0.65 | 1.1  |       | RMOT=50k                                           |

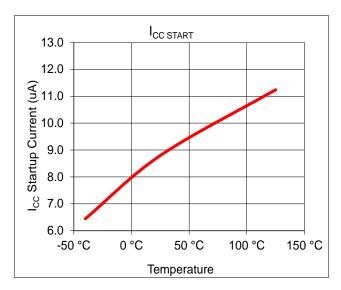

| I <sub>CC START</sub> | Start-up Current                                               |      | 10   | 50   | μA    | V <sub>CC</sub> = V <sub>CC ON</sub> - 0.1V        |

| Comparato             | r Section                                                      |      |      |      |       |                                                    |

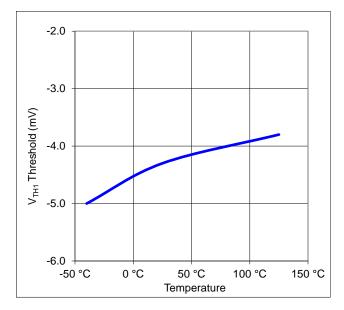

| $V_{TH1}$             | Turn-off Threshold                                             | -8   | -4   | 0    |       | V <sub>CC</sub> =5V to 15V                         |

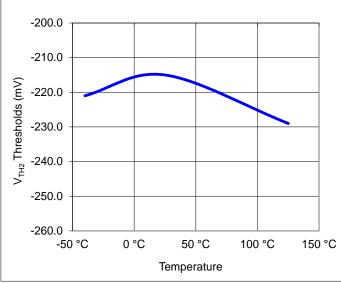

| $V_{TH2}$             | Turn-on Threshold                                              | -263 | -230 | -197 | mV    |                                                    |

| $V_{HYST}$            | Hysteresis                                                     | _    | 230  |      |       |                                                    |

| I <sub>IBIAS1</sub>   | Input Bias Current                                             | -10  | -7.5 | _    |       | V <sub>D</sub> =-50mV                              |

| I <sub>IBIAS2</sub>   | Input Bias Current                                             | _    | 7    | 30   | μA    | V <sub>D</sub> =200V                               |

| One-Shot S            | Section                                                        |      |      |      |       |                                                    |

| t <sub>BLANK</sub>    | Blanking Pulse Duration                                        | 8    | 13   | 24   | μs    |                                                    |

| $V_{TH3}$             | Reset Threshold                                                | 1.06 | 1.18 | 1.31 | V     |                                                    |

| t <sub>BRST</sub>     | Blanking Time of Reset                                         | _    | 400  | _    | ns    |                                                    |

| V <sub>HYST3</sub>    | Hysteresis                                                     | _    | 70   |      | mV    | GBD                                                |

| Minimum O             | n Time Section                                                 |      |      |      |       |                                                    |

|                       |                                                                | 80   | 100  | 120  | ns    | RMOT=5k                                            |

| $T_{ONmin}$           | Minimum On Time                                                | 400  | 500  | 600  | ns    | RMOT=24k                                           |

|                       |                                                                | 0.8  | 1    | 1.2  | μs    | RMOT=50k                                           |

# **Electrical Characteristics**

$V_{CC}$ =12V and  $T_A$ =25°C unless otherwise specified. The output voltage and current ( $V_O$  and  $I_O$ ) parameters are referenced to GND pin.

| Symbol                | ol Definition                |      | Тур. | Max.     | Units | Remarks                                                                             |

|-----------------------|------------------------------|------|------|----------|-------|-------------------------------------------------------------------------------------|

| Gate Driver Section   |                              |      |      |          |       |                                                                                     |

| $V_{GLO}$             | Gate Low Voltage             |      | 0.2  | 0.4      |       | I <sub>GATE</sub> =100mA,<br>V <sub>CC</sub> =12V                                   |

| V                     | Cata High Voltage            | 11.5 | 11.9 | $V_{CC}$ | V     | V <sub>CC</sub> =12V, I <sub>GATE</sub> =5mA                                        |

| $V_{GTH}$             | Gate High Voltage            | 4.5  | 4.9  | $V_{CC}$ |       | V <sub>CC</sub> =5V, I <sub>GATE</sub> =5mA                                         |

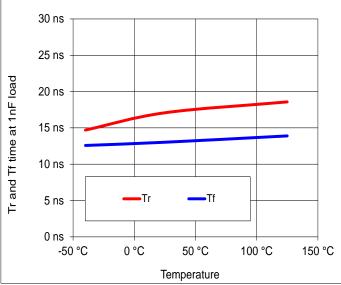

| t <sub>r</sub>        | Rise Time                    | _    | 20   |          |       | C <sub>LOAD</sub> =1nF, V <sub>CC</sub> =12V                                        |

| t <sub>f</sub>        | Fall Time                    | _    | 13   |          |       | C <sub>LOAD</sub> =1nF, V <sub>CC</sub> =12V                                        |

| t <sub>Don</sub>      | Turn on Propagation Delay    | _    | 60   | 90       | ns    | $V_{DS}$ to $V_{GATE} - V_{DS}$ goes down from 6V to -1V                            |

| t <sub>Doff</sub>     | Turn off Propagation Delay   | _    | 50   | 60       |       | V <sub>DS</sub> to V <sub>GATE</sub> – V <sub>DS</sub><br>goes up from<br>-1V to 6V |

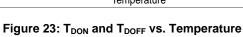

| $r_{\sf up}$          | Pull up Resistance           | _    | 9    |          |       | I <sub>GATE</sub> =100mA                                                            |

| r <sub>down</sub>     | Pull down Resistance         | _    | 2    |          | Ω     | I <sub>GATE</sub> =-100mA                                                           |

| I <sub>O source</sub> | Output Peak Current (source) | _    | 1    | _        | ۸     | GBD                                                                                 |

| I <sub>O sink</sub>   | Output Peak Current (sink)   | _    | 2.5  | _        | Α     | GBD                                                                                 |

GBD – parameter is guaranteed by design and is not tested.

# **Functional Block Diagram**

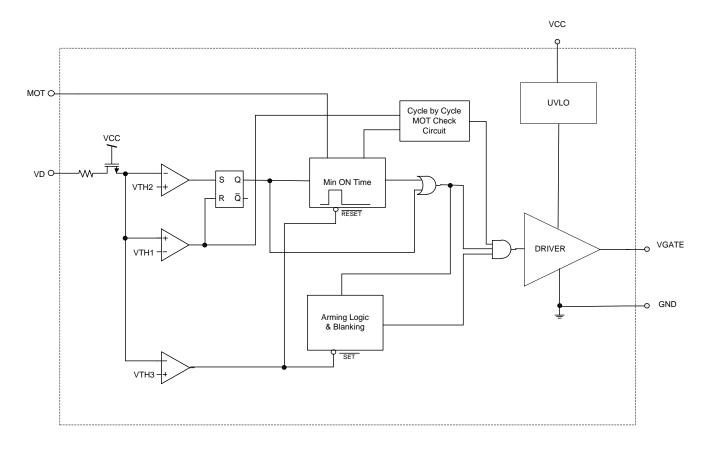

I/O Pin Equivalent Circuit Diagram

#### **Pin Definitions**

| PIN# | Symbol | Description                   |

|------|--------|-------------------------------|

| 1    | VCC    | Supply Voltage                |

| 2    | GND    | Ground                        |

| 3    | MOT    | Minimum On Time Program Input |

| 4    | VD     | FET Drain Sensing             |

| 5    | GATE   | Gate Drive Output             |

## **Pin Assignments**

## **Detailed Pin Description**

## **VCC: Power Supply**

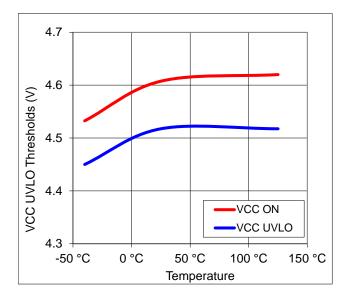

The supply voltage pin is monitored by the under voltage lockout circuit. It is possible to turn off the IC entering UVLO mode by pulling this pin below the minimum turn off threshold voltage for micro power consumption.

To avoid noise problems a bypass ceramic capacitor connected to Vcc and GND is needed, which should be placed as close as possible to the IC. A low value series resistor to Vcc may also be added if extra filtering is required. This pin is internally clamped to 20V.

#### **GND: Ground**

This is the IC ground reference connected to the SR MOSFET source.

#### **MOT: Minimum On Time**

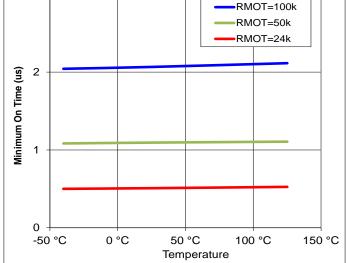

The MOT programming pin controls the amount of minimum on time. Once  $V_{TH2}$  is crossed for the first time, the gate signal will transition high and turn on the power MOSFET. Spurious ringing and oscillations can falsely trigger the input comparator to switch the output off. The MOT prevents this by blanking the input comparator to keep the SR MOSFET on for a minimum time. The MOT is typically programmed between 500ns and 2us by using an external resistor referenced to GND.

#### **VD: Drain Voltage Sense**

VD is the voltage sense pin for the SR MOSFET drain. This is a high voltage pin therefore particular care must be taken in properly routing the connection.

An additional RC filter can be placed at this input to improve noise immunity, however only small values (e.g. 100Ω + 100pF) may be used to avoid introducing significant delay to the control input.

#### **GATE: Gate Drive Output**

The gate drive output provides 1A source and 2.5A sink current capability. Although this output may be directly connected to the power MOSFET gate the use of a minimal gate resistor is recommended, especially when using multiple MOSFETs in parallel.

Care must be taken to keep the gate loop as short and as small as possible in order to minimize inductance and achieve optimal switching performance.

# **Application Information and Additional Details**

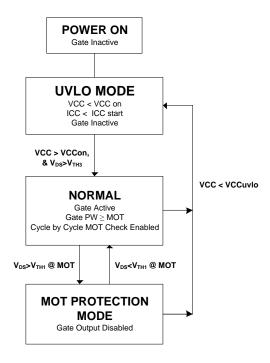

#### **State Diagram**

#### **UVLO Mode**

The IC remains in the under-voltage lockout condition until VCC exceeds the turn on threshold voltage,  $V_{CC\ ON}$ . During the time the IC remains in the UVLO state, the gate drive circuit is inactive and only a very small quiescent current  $I_{CC\ START}$  is consumed. UVLO mode is accessible from any other operating state whenever VCC <  $V_{CC\ UVLO}$ .

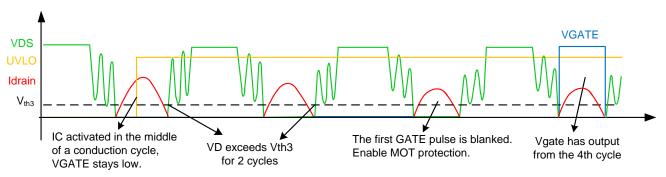

#### Normal Mode and Synchronized Enable Function

The IC enters into normal operating mode once the UVLO voltage has been exceeded. When the IC enters the Normal Mode, the GATE output remains disabled (stays low) for a start-up delay time in the range of 100us, then  $V_{DS}$  must transition above  $V_{TH3}$  two times to enable synchronous rectification. This ensures that the GATE output can never be enabled in the middle of a switching cycle. The first gate pulse after activation is blocked and the cycle by cycle MOT protection circuit is enabled. This logic avoids reverse currents through the SR MOSFET from occurring during startup. The gate will continuously drive the SR MOSFET after completing this startup sequence.

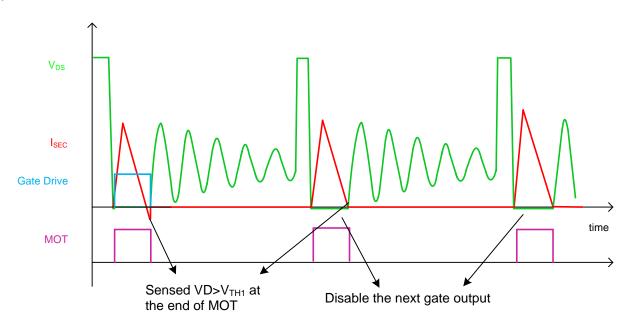

#### **MOT Protection Mode**

If the secondary current conduction time is shorter than the MOT (Minimum On Time), the following driver output pulse is disabled. This function can avoid reverse current from occurring when the system is switching at very low duty-cycles under very light or zero load conditions. System standby power consumption is reduced by disabling the GATE output. The cycle by cycle MOT check circuit is always activated under Normal Mode and MOT Protection Mode so that the IC will automatically resume normal operation only once the load increases to a level where the secondary current conduction time exceeds MOT.

# **General Description**

The direction of the rectified current in the SR MOSFET is sensed by the IR1161 through its high voltage drain sensing input VD, which monitors the drain to source voltage drop. Conduction occurs through the body diode when the MOSFET is switched off and when it is switched on, the R<sub>DSon</sub> acts as a shunt resistance. The GATE drive to the MOSFET is switched on only when current is flowing from source to drain. Internal blanking logic is used to prevent spurious transitions and guarantee correct operation under different load conditions.

The IR1161 is suitable for DCM or CrCM Flyback and Resonant Half-Bridge topologies.

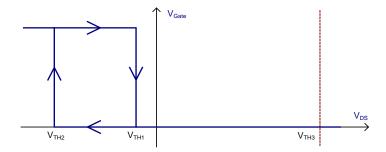

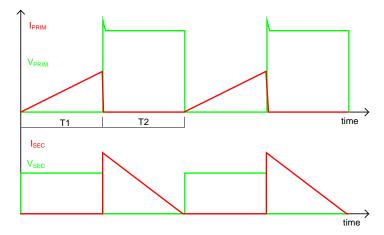

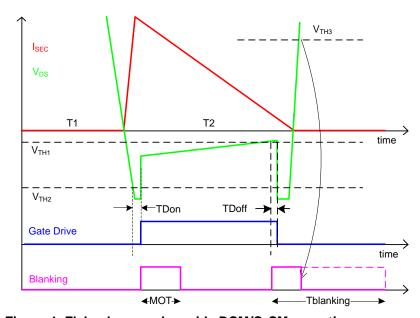

Figure 1: Input comparator thresholds

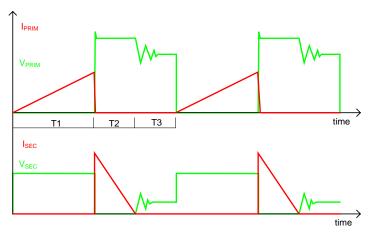

#### **Flyback Application**

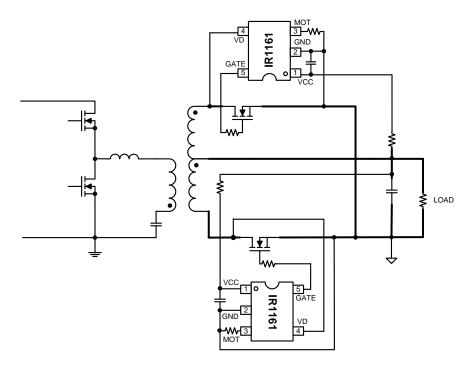

The typical application circuit of IR1161 in Flyback converter is shown on page 1.

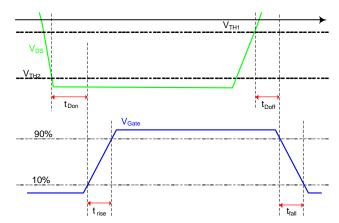

#### Turn-on phase

When the conduction phase of the SR MOSFET is initiated, current will start flowing through its body diode producing a negative  $V_{DS}$  voltage across it. The body diode has a much higher forward voltage drop than that created by the MOSFET on resistance and will therefore becoming more negative than the turn-on threshold  $V_{TH2}$ . At that point the IR1161 will drive the gate high, which will in turn cause  $V_{DS}$  to transition to a much smaller negative voltage. This voltage step is usually accompanied by some amount of ringing that could potentially trigger the IR1161 to turn off prematurely. To prevent this, a Minimum On Time (MOT) blanking period is maintains the SR MOSFET on for a minimum period of time, which is externally adjustable.

#### Turn-off phase

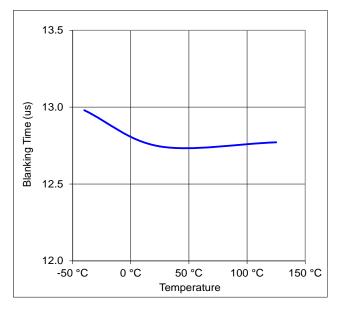

At the end of the conduction period the current reduces to zero, causing  $V_{DS}$  to cross the turn-off threshold  $V_{TH1}$ . The IR1161 will then turn the SR MOSFET gate off and current will start flowing again through the body diode causing a negative going  $V_{DS}$  voltage step. Depending on the amount of residual current,  $V_{DS}$  could potentially trigger the turn on threshold once again. For this reason  $V_{TH2}$  is blanked for a certain amount of time ( $T_{BLANK}$ ) after  $V_{TH1}$  has been triggered. The blanking time is internally set and is reset only by  $V_{DS}$  crossing the positive threshold  $V_{TH3}$  and remaining above this threshold for more than reset blanking time  $t_{BRST}$ . Once reset the IR1161 is ready for next conduction cycle.

Figure 2: Flyback Primary and secondary currents and voltages for DCM mode

Figure 3: Flyback Primary and secondary currents and voltages for CrCM mode

Figure 4: Flyback secondary side DCM/CrCM operation

2016-07-01

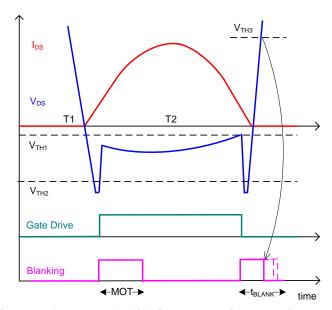

# **Resonant Half-Bridge Application**

The typical application circuit of IR1161 in LLC half-bridge is shown in Figure 5.

Figure 5: Resonant half-bridge application circuit

In the resonant half-bridge converter the turn-on phase and turn-off phase are similar to the Flyback except that the current shape is sinusoidal. The typical operating waveform is seen below in figure 6.

Figure 6: Resonant half-bridge operation waveform

# **Setting the MOT Time**

2016-07-01

The MOT time is set by an external resistor connected from the MOT pin to GND.

$$T_{MOT} = 2 \times 10^{-11} \times R_{MOT}$$

## **MOT Protection Mode**

The MOT protection function is designed to avoid reverse current occurring in the SR MOSFET. This could happen at light load if the MOT time is set longer that the actual conduction time. The IR1161 disables the gate drive output in MOT protection mode as described in the previous section and automatically resumes normal operation when the load increases to a level where the current conduction time is longer than MOT.

This function works in both Flyback and resonant half-bridge topologies. Figure 7 illustrates operation in a DCM Flyback converter.

**Figure 7: MOT Protection Mode**

#### **Synchronized Enable Function**

This function guarantees that the GATE drive always switches high at the beginning of a switching cycle. This is essential since mid-cycle switch on with the MOT function would force the MOSFET to remain on past the conduction period leading to reverse conduction.

This function works in both Flyback and resonant half-bridge topologies. Figure 8 is an example in resonant half-bridge converter.

Figure 8: Synchronized Enable Function (resonant half-bridge)

## **Driving a Logic Level MOSFET**

An external gate drive pull down circuit is recommended when driving a logic level MOSFET.

This is because during power up and power down the drain may be switching while the IR1161 remains in UVLO. SR MOSFET drain to gate capacitance causes voltage pulses to appear at the gate that could have sufficient amplitude to reach the turn on threshold because the IR1161 gate sink capability is limited when VCC < 2V.

The following circuit ensures that the gate voltage remains below 1V under all conditions:

Figure 9: Gate drive circuit for logic level SR MOSFET

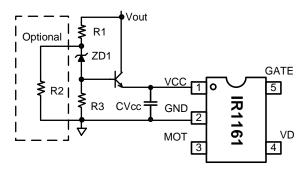

#### **Vcc Clamping Circuit**

The IR1161 can be directly biased by the converter output voltage  $V_{OUT}$  if this falls within the recommended range of Vcc although a low value series resistor may be required for optimal noise filtering. For higher system output voltages a clamping circuit is recommended to limit Vcc. This also lowers the gate drive voltage and reduces losses if  $V_{OUT}$  is above 15V.

Many clamping circuits are available from simple zener diode clamping to bipolar linear regulators. Figure 10 is one example; in this circuit the Vcc voltage will be clamped to a voltage of  $V_{OUT}$  -  $V_{ZD1}$  -  $V_{BE}$ . The circuit also provides turn-on delay to the IR1161, which will activate only when the output voltage exceeds  $V_{CCON} + V_{ZD1} + V_{BE}$ . R1 and R2 are optional for more precise control of the Vcc clamping voltage.

Figure 10: Vcc clamping circuit

#### **Shutdown Circuit**

The IR1161 can be disabled by pulling  $V_{\text{CC}}$  below the  $V_{\text{CC UVLO}}$  threshold.

Figure 11: IR1161 Enable/Disable circuit

# **General Timing Waveform**

Figure 12: Timing waveform

Figure 13: Undervoltage Lockout vs. Temperature

Figure 14: Icc Quiescent Current vs. Temperature

Figure 15: Icc Supply Current @1nF Load vs. Temperature

Figure 16: Icc Startup Current vs. Temperature

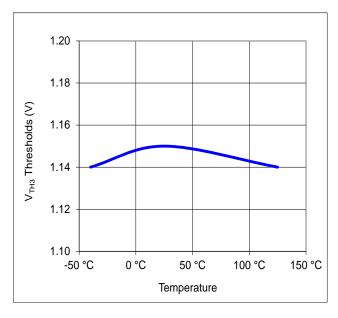

Figure 17: V<sub>TH1</sub> vs. Temperature

Figure 18: V<sub>TH2</sub> vs. Temperature

Figure 19: V<sub>TH3</sub> vs. Temperature

Figure 20: MOT Time vs. Temperature

3

Figure 21: Blanking Time vs. Temperature

Figure 22: Tr and Tf vs. Temperature

Figure 24: R<sub>UP</sub> and R<sub>DOWN</sub> vs. Temperature

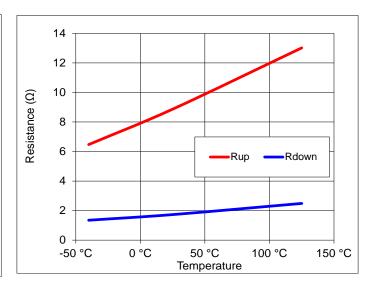

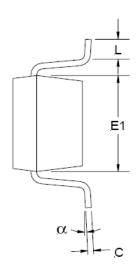

# Package Details: 5 Lead SOT23

| SYMBOL | MIN MAX  |      |  |  |  |

|--------|----------|------|--|--|--|

| Α      | 0.90     | 1.45 |  |  |  |

| A1     | 0.00     | 0.15 |  |  |  |

| A2     | 0.90     | 1.30 |  |  |  |

| В      | 0.25     | 0.50 |  |  |  |

| С      | 0.09     | 0.20 |  |  |  |

| D      | 2.80     | 3.00 |  |  |  |

| Е      | 2.60     | 3.00 |  |  |  |

| E1     | 1.50     | 1.75 |  |  |  |

| е      | 0.95     | REF  |  |  |  |

| e1     | 1.90 REF |      |  |  |  |

| L      | 0.35 0.5 |      |  |  |  |

| α      | 08       | 108  |  |  |  |

NOTE: ALL MEASUREMENTS ARE IN MILLIMETERS.

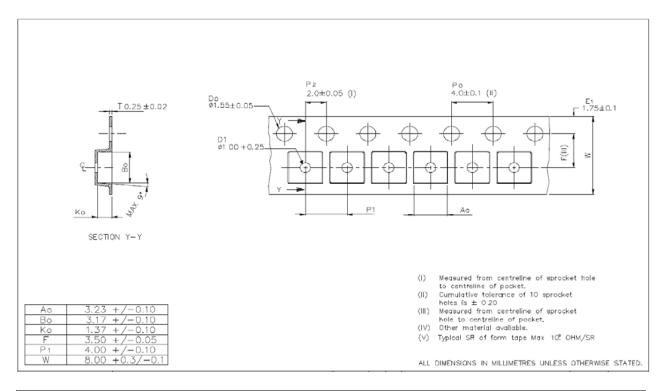

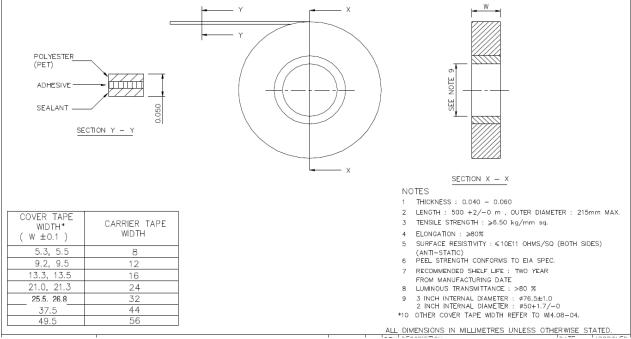

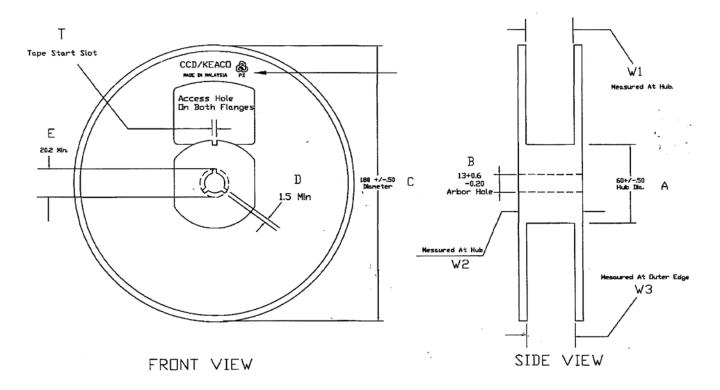

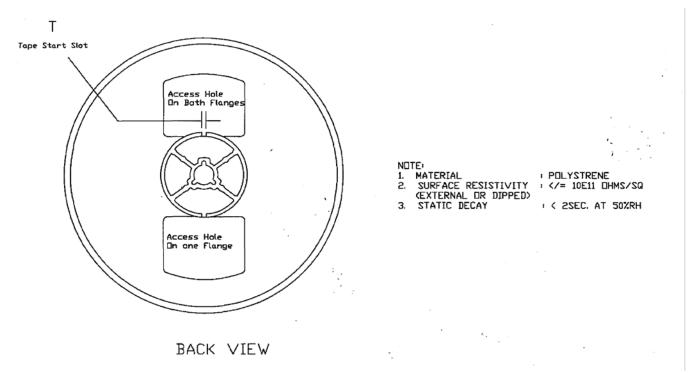

# Tape and Reel Details: 5 Lead SOT23

# Tape and Reel Details: 5 Lead SOT23

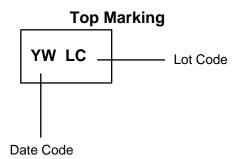

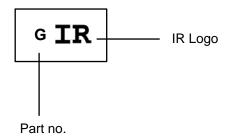

# Part Marking Information: 5 Lead SOT23

# **Bottom Marking**

# Qualification Information<sup>†</sup>

| Qualification Level        |                  | Industrial <sup>††</sup>                        |                                    |  |

|----------------------------|------------------|-------------------------------------------------|------------------------------------|--|

|                            |                  | Comments: This family of ICs has passed JEDEC's |                                    |  |

|                            |                  |                                                 | nfineon's Consumer qualification   |  |

|                            |                  | level is granted by extensi                     | on of the higher Industrial level. |  |

| Moisture Sensitivity Level |                  | SOT-23 5L                                       | MSL1 <sup>†††</sup>                |  |

|                            |                  | 301-23 5L                                       | (per IPC/JEDEC J-STD-020)          |  |

| Marking Market             |                  | Class A                                         |                                    |  |

| ESD                        | Machine Model    | (per JEDEC standard JESD22-A115)                |                                    |  |

| E3D                        | II D. I. M. I.I. | Class 1A                                        |                                    |  |

|                            | Human Body Model | (per EIA/JEDEC standard EIA/JESD22-A114)        |                                    |  |

| IC Latch-Up Test           |                  | Class I, Level A                                |                                    |  |

|                            |                  | (per JESD78)                                    |                                    |  |

| RoHS Compliant             |                  | Yes                                             |                                    |  |

- † Qualification standards can be found at Infineon's web site www.infineon.com

- †† Higher qualification ratings may be available should the user have such requirements. Please contact your Infineon sales representative for further information.

- ††† Higher MSL ratings may be available for the specific package types listed here. Please contact your Infineon sales representative for further information.

# **Revision History**

#### Major changes since the last revision

| Date         | Description of change                      |

|--------------|--------------------------------------------|

| June 1, 2015 | First release                              |

| May 24, 2016 | Changed MSL to level 1.                    |

| July 1, 2016 | Changed format template with Infineon logo |

Published by Infineon Technologies AG 81726 München, Germany © Infineon Technologies AG 2015 All Rights Reserved.

#### **IMPORTANT NOTICE**

The information given in this document shall in <u>no event</u> be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie"). With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (<a href="www.infineon.com">www.infineon.com</a>).

#### **WARNINGS**

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may <u>not</u> be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.

2016-07-01