### INPUT POWER MONITOR WITH DIGITAL INTERFACE

### DESCRIPTION

The IR3725 is a highly configurable power monitor IC that uses proprietary digital technology to measure a 12V rail current, its voltage, or its average power over a user specified time interval. Configuration and result reporting are managed through a serial digital interface. The current is measured as a voltage across a shunt resistance, an input inductor, or a copper trace resistance.

The real time voltage and current signals are multiplied, digitized, and averaged over a user selectable averaging interval providing TruePower<sup>™</sup> measurement of highly dynamic loads.

### FEATURES

- Accurate power, current, or voltage reporting

- 1.5 % maximum power error

- 1.0 % maximum current error

- Serial digital interface

- SMBus and I<sup>2</sup>C compatible

- Programmable averaging interval

- Flexible current sensing

- Resistive or Inductor DCR

- Applications

- Synchronous rectified buck converters

- Multiphase converters

- 12pin 3x4 DFN lead free

- RoHS Compliant

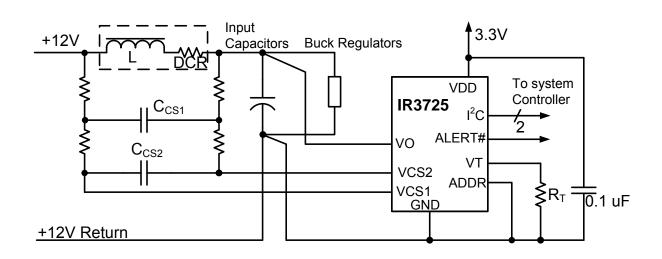

### **TYPICAL APPLICATION CIRCUIT**

### **ORDERING INFORMATION**

| Device       | Package                   | Order Quantity  |

|--------------|---------------------------|-----------------|

| IR3725MTRPBF | 12 lead DFN (4x3 mm body) | 3000 piece reel |

| IR3725MPBF   | 12 lead DFN (4x3 mm body) | Sample Quantity |

### ABSOLUTE MAXIMUM RATINGS

#### All voltages referenced to GND

| VDD:                              | 3.9V         |

|-----------------------------------|--------------|

| ALERT#:                           | 3.9V         |

| ALERT#                            | < VDD + 0.3V |

| VCS1, VCS2, VO                    | 25.0V        |

| All other Analog and Digital pins | 3.9V         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications are not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**ELECTRICAL SPECIFICATIONS** Unless otherwise specified, these specifications apply: VDD =  $3.3V \pm 5\%$ ,  $0^{\circ}C \le T_J \le 125^{\circ}C$ ,  $8V \le VO \le 23.5V$ , and operation in the typical application circuit. See notes following table.

| PARAMETER                                 | TEST CONDITION             | NOTE | MIN  | TYP  | MAX  | UNIT |

|-------------------------------------------|----------------------------|------|------|------|------|------|

| BIAS SUPPLY                               | -                          | _    | _    | _    |      | _    |

| VDD Turn-on Threshold, VDD <sub>UP</sub>  |                            |      |      |      | 3.1  | V    |

| VDD Turn-off Threshold, VDD <sub>DN</sub> |                            |      | 2.4  |      |      | V    |

| VDD UVLO Hysteresis                       |                            |      | 75   |      |      | mV   |

| VDD Operating Current                     | R <sub>T</sub> = 25.5 kΩ   |      |      | 700  | 1000 | μA   |

| VDD Shutdown Current                      | Config Reg enable bit d4=1 |      |      | 18   | 100  | μA   |

| VOLTAGE REFERENCE                         | -                          | _    | _    | _    | _    |      |

| V <sub>T</sub> Voltage                    | R <sub>T</sub> = 25.5 kΩ   |      | 1.40 | 1.50 | 1.60 | V    |

| Reference load, R <sub>T</sub>            |                            | 1    | 20   | 25.5 | 45.3 | kΩ   |

| VOLTAGE SENSOR                            | -                          | _    |      | -    | -    | -    |

| Voltage, full scale, V <sub>FS</sub>      |                            |      |      | 23.5 |      | V    |

| CURRENT SENSOR                            | -                          | -    | -    | -    | _    | _    |

| Voltage, Current Gain, V <sub>IG</sub>    | R <sub>T</sub> = 25.5 kΩ   |      |      | 1.48 |      | V    |

| DIGITIZER                                 | -                          | _    | _    | _    | _    |      |

| Internal Sampling frequency               | Driven from internal clock |      |      | 512  |      | kHz  |

| External Sampling frequency               | Driven from external clock |      | 922  | 1024 | 1126 | kHz  |

| POWER INFORMATION                         | -                          |      |      |      |      |      |

| Minimum Averaging Interval                | Config Reg [d3d0] = b'0000 | 1    | 0.85 | 1    | 1.15 | ms   |

| Maximum Averaging Interval                | Config Reg [d3d0] = b'1000 | 1    | 217  | 256  | 295  | ms   |

| PARAMETER                 | TEST CONDITION                                                                                             | NOTE        | MIN | TYP | MAX | UNIT |

|---------------------------|------------------------------------------------------------------------------------------------------------|-------------|-----|-----|-----|------|

| ACCURACY                  | _                                                                                                          |             | _   | _   | _   | _    |

| Power measurement error   | VO=12V, DCR voltage = 75 mV,<br>$R_T$ =25.5k $\Omega$ , RCS1=RCS2=1.5k $\Omega$                            | 1, 2        |     |     | 2   | %    |

|                           | T <sub>j</sub> = 0 - 85 °C                                                                                 | ·, <u>~</u> |     |     | 1.5 | 70   |

| Voltage measurement error | VO=12 V, DCR voltage = 75mV,<br>RT=25.5k $\Omega$ , RCS1=RCS2=1.5k $\Omega$                                | 1, 2        |     |     | 1.5 | %    |

|                           | Tj = 0 – 85 °C                                                                                             | ., _        |     |     | 1.3 | 70   |

| Current measurement error | VO=12V, DCR voltage = 75 mV,<br>R <sub>T</sub> =25.5k $\Omega$ , RCS1=RCS2=1.5k $\Omega$<br>Tj = 0 – 85 °C | 1, 2        |     |     | 1.6 | %    |

#### NOTES:

- 1. Guaranteed by design, not tested in production

- 2. Assumes no error contributed by external components

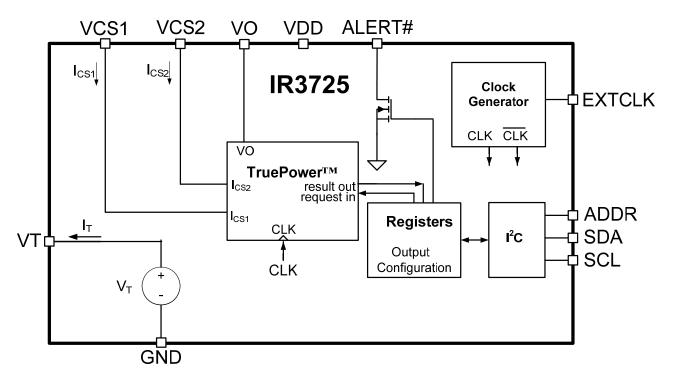

### **BLOCK DIAGRAM**

#### **PIN DESCRIPTION**

| NAME   | NUMBER | I/O LEVEL    | DESCRIPTION                                                    |

|--------|--------|--------------|----------------------------------------------------------------|

| VCS1   | 1      | Analog 12V   | Current sensing input 1                                        |

| VCS2   | 2      | Analog 12V   | Current sensing input 2                                        |

| VO     | 3      | Analog 12V   | Voltage sensing input                                          |

| VT     | 4      | Analog       | Thermistor sensing input                                       |

| GND    | 5      | 0V           | IC bias supply and signal ground                               |

| VDD    | 6      | 3.3V         | 3.3V bias supply                                               |

| EXTCLK | 7      | 3.3V Digital | Input for optional external clock                              |

| ADDR   | 8      | 3.3V Digital | Bus Address selection input                                    |

| SCL    | 9      | 3.3V Digital | Bus Clock; Input only                                          |

| SDA    | 10     | 3.3V Digital | Bus Data; Input / Open drain output                            |

| ALERT# | 11     | 3.3V Digital | Programmable output function; Open drain output clamped to VDD |

| NC     | 12     |              | Do not connect                                                 |

### **IC PIN FUNCTIONS**

#### **VDD PIN**

This pin provides operational bias current to circuits internal to the IR3725. Bypass it with a high quality ceramic capacitor to the GND pin.

#### **GND PIN**

This pin returns operational bias current to its source. It is also the reference to which the voltage VO is measured, and it sinks the reference current established by the external resistor  $R_T$ .

#### **VO PIN**

This pin is to be electrically connected to the location in the circuit where voltage for the power calculation is desired to be monitored. Power accuracy may be degraded if the voltage at this pin is below VO<sub>min</sub>.

#### VCS1 AND VCS2 PINS

The average current into these pins is used to calculate power. Current sources internal to the IR3725 will null the average voltage between this pin pair.

#### **VT FUNCTION**

A voltage internal to the IR3725 drives the VT pin while the pin current is monitored and used to set the amplitude of the switched current source IT. This pin should be connected to GND through a precision resistor network RT. This network may include provision for canceling the positive temperature coefficient of the inductor's DC resistance (DCR).

#### ALERT# FUNCTION

The ALERT# pin is a multi-use pin. During normal use it can be configured via the serial bus as an open drain ALERT# pin that will be driven logic low when new data is available in the output register. After the output register has been read via the serial bus the ALERT# will be released to its high resistance state. This pin can also be programmed to pull low when the output exceeds the programmable level.

#### ADDR PIN

The ADDR pin is an input that establishes the serial bus address. Valid addresses are selected by grounding, floating, or wiring to VDD the ADDR pin. Table 1, "User Selectable Addresses", provides a mapping of possible selections. Bypass this pin to GND with a high quality ceramic capacitor when floated.

#### Table 1 User selectable addresses

| ADDR pin configuration | Bus Address |

|------------------------|-------------|

| Low                    | b'1110 000  |

| Open                   | b'1110 010  |

| High                   | b'1110 110  |

#### EXTCLK

This pin is a Schmitt trigger input for an optional externally provided square wave clock. The duty ratio of this externally provided clock, if used, shall be between 40% and 60%. If no external clock is connected, the internal clock will be used. Connect this pin to GND if no external clock is used.

#### SCL

SCL is the serial bus clock and is capable of functioning with a rate as low as 10 kHz. It will continue to function as the rate is increased to 400 kHz. This device is considered a slave, and therefore uses the SCL as an input only.

#### SDA

SDA is monitored as data input during master to slave transactions, and is driven as data output during slave to master transactions as indicated in the Packet Protocol section to follow.

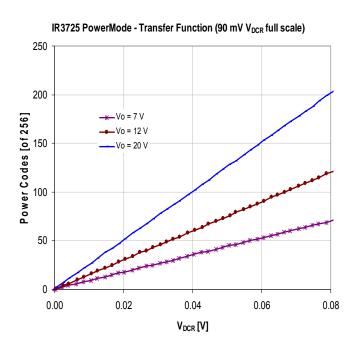

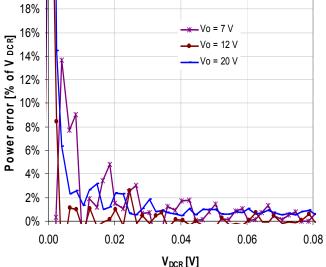

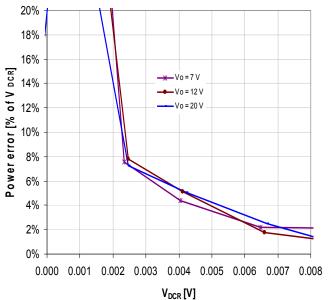

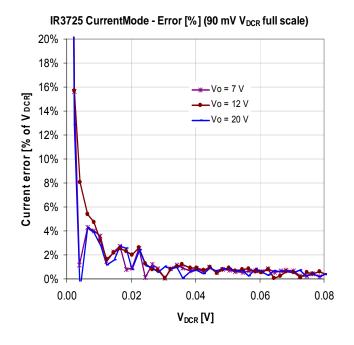

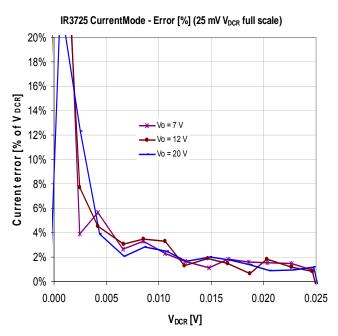

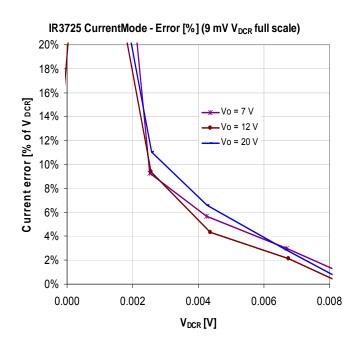

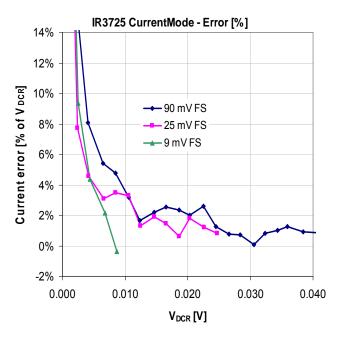

### **TYPICAL PERFORMANCE CHARACTERISTICS**

(One device tested using "Resistor Sensing Circuit", VDD = 3.3 V,  $C_{CS2}$  = 10 u F,  $R_T$  = 25.5 k  $\Omega$ , 90 mV full scale uses  $R_{CS1} = R_{CS2} = 1.5 \text{ k} \Omega$ , 25 mV full scale uses  $R_{CS1} = R_{CS2} = 432 \Omega$ , 9 mV full scale uses  $R_{CS1} = R_{CS2} = 150 \Omega$ . Each data point is average of eight samples.)

20% -Vo = 7 V -Vo = 12 V Vo = 20 V

IR3725 PowerMode - Error [%] (90 mV V<sub>DCR</sub> full scale)

IR3725 PowerMode - Error [%] (25 mV V<sub>DCR</sub> full scale) 20% 18% 16% Power error [% of V DCR] 14% Vo = 7 V Vo = 12 V 12% Vo = 20 V 10% 8% 6% 4% 2% 0% 0.000 0.005 0.010 0.015 0.020 0.025

V<sub>DCR</sub> [V]

IR3725 PowerMode - Error [%] (9 mV V<sub>DCR</sub> full scale)

Page 6 of 19 Downloaded from Arrow.com.

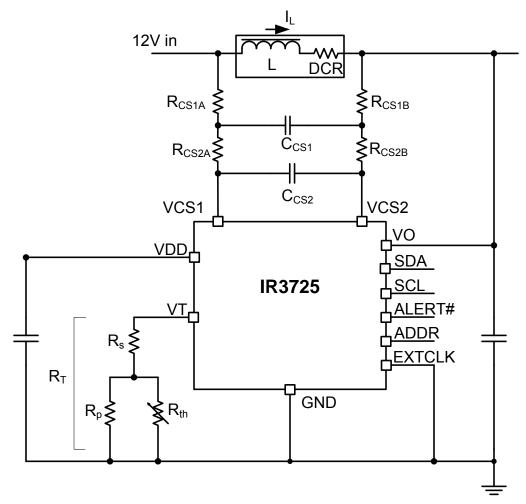

### FUNCTIONAL DESCRIPTION

Please refer to the Functional Description Diagram below. Power flow through the inductor is the product of output voltage VO times the inductor current I<sub>L</sub>. An average voltage V<sub>DCR</sub> will be developed across the inductor as a result of current flow I<sub>L</sub>. This voltage will result in a net current flow imbalance into the VCS pins that is equal to V<sub>DCR</sub> / (Rcs1 + Rcs2). A voltage nulling circuit inside the IC sinks enough current to equalize the voltages of Vcs1 and Vcs2. The current required to balance the voltages of these two nodes is reported as a fraction of the current V<sub>IG</sub> / R<sub>T</sub> using 256 as the denominator. Current will be reported as an integer number of counts in two's compliment binary format with a range of -256 to 256. Positive values will be reported when current flow is in the

direction of the current flow arrow in the diagram below.

The voltage is reported as a positive integer number of counts equal to (voltage \* 256) / V<sub>FS</sub>. V<sub>FS</sub> is defined in the ELECTRICAL SPECIFICATIONS. Power is reported as an integer number of counts in two's compliment binary format with a range of -256 to 256. Positive values will be reported when current flow is in the direction of the current flow arrow in the diagram below. Power expressed in counts will be (power \* 256) / (I<sub>FS</sub> \* V<sub>FS</sub>) where I<sub>FS</sub> equals V<sub>IG</sub>\*(Rcs1 + Rcs2) / (R<sub>T</sub>\*DCR). The full scale power P<sub>FS</sub> is the product of full-scale voltage and full scale current.

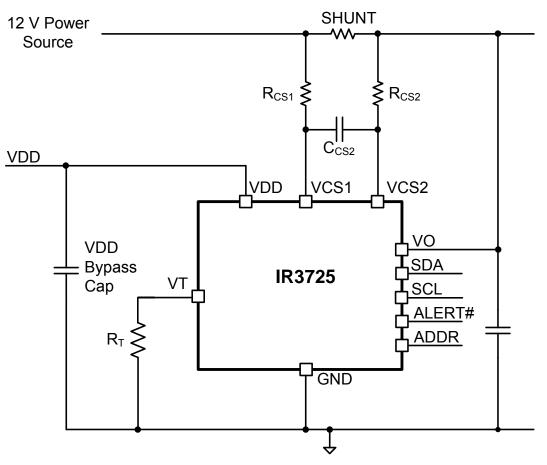

### **RESISTOR CURRENT SENSING APPLICATION**

The voltage on the shunt resistor of the circuit below is directly proportional to the current from the source. Shunts developing 5 mV to 75 mV at I<sub>FS</sub> have been used. Accuracy is enhanced at the higher voltage. Select R<sub>T</sub> to be a 25.5 k $\Omega$  1% or better initial tolerance resistor. Sinking current capability of VCS1 or VCS2 is V<sub>IG</sub> / R<sub>T</sub>.

Chose  $R_{CS1}$  and  $R_{CS2}$  such that this current through either of them develops the same voltage that is developed by the shunt at full scale current.

IFS \* RSHUNT =  $(V_{IG}/R_T)$  \* RCS

$C_{CS2}$  is the integrator capacitor and should have a ceramic dielectric with a value between 0.1  $\mu F$  and 10  $\mu F.$

Figure 2 Resistor Sensing Circuit

International

### INDUCTOR DCR CURRENT SENSING APPLICATION

Referring to the Functional Description Diagram, it can be seen that the shunt function can be accomplished by the DC resistance of the inductor that is already present. Omitting the resistive shunt reduces BOM cost and increases efficiency. In exchange for these two significant advantages two easily compensated design complications are introduced, a time constant and a temperature coefficient.

The inductor voltage sensed between the Rcs1 resistors is not simply proportional to the inductor current, but rather is expressed in the Laplace equation below.

$$V_{L} = I_{L} \cdot DCR \left(1 + s \frac{L}{DCR}\right)$$

This inductor time constant is canceled when

$$\frac{L}{DCR} = 2 \cdot \frac{R_{CS1} \cdot R_{CS2}}{R_{CS1} + R_{CS2}} \cdot C_{CS1} \, . \label{eq:CS1}$$

Let  $\frac{R_{CS1} \cdot R_{CS2}}{R_{CS1} + R_{CS2}} = R_{eq}.$

A second equation is used to set the full-scale inductor current.

$$I_{FS} = \frac{V_{IG}}{R_{T}} \cdot \frac{\left(R_{CS1} + R_{CS2}\right)}{DCR} \cdot Let$$

$R_{CS1} + R_{CS2} = R_{sum}$  and solve for Rsum.

Select a standard value C<sub>CS1</sub> that is larger than

$\frac{4 \cdot L}{\text{DCR} \cdot \text{R}_{\text{sum}}}$  . Solve for  $\text{R}_{\text{eq}}.$

We now know Req and Rsum, but we do not know the individual resistor values  $R_{CS1}$  or  $R_{CS2}$ . The next step is to solve for them simultaneously. By substituting  $R_{sum}$  into the  $R_{eq}$  equation the following can be written:

$$R_{eq} = \frac{R_{CS1} \cdot R_{CS2}}{R_{sum}}$$

, which can then be rearranged to

$$R_{CS1}^2 - R_{CS1} \cdot R_{sum} + R_{eq} \cdot R_{sum} = 0 \; . \label{eq:RCS1}$$

Note that this equation is of the form

$ax^2 + bx + c = 0$  where a=1, b=-Rsum, and c=Req•Rsum. The roots of this quadratic equation will be  $R_{CS1}$  and  $R_{CS2}$ . Use the higher value resistor as  $R_{CS1}$  in order to minimize ripple current in  $C_{CS1}$ .

$$R_{CS1} = R_{SUM} \cdot \frac{1 + \sqrt{1 - 4 \cdot \frac{R_{eq}}{R_{SUM}}}}{2}$$

$$R_{CS2} = R_{SUM} \cdot \frac{1 - \sqrt{1 - 4 \cdot \frac{R_{eq}}{R_{SUM}}}}{2}$$

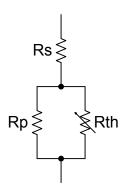

# THERMAL COMPENSATION FOR INDUCTOR DCR CURRENT SENSING

The positive temperature coefficient of the inductor DCR can be compensated if  $R_T$  varies inversely proportional to the DCR. DCR of a copper coil, as a function of temperature, is approximated by

$$DCR(T) = DCR(T_R) \cdot (1 + (T - T_R) \cdot TCR_{Cu}) \quad . \tag{1}$$

$T_R$  is some reference temperature, usually 25 °C, and TCR<sub>Cu</sub> is the resistive temperature coefficient of copper, usually assumed to be 0.39 %/°C near room temperature. Note that equation 1 is linearly increasing with temperature and has an offset of DCR( $T_R$ ) at the reference temperature. If  $R_T$  incorporates a negative temperature coefficient thermistor then temperature effects of DCR can be minimized. Consider a circuit of two resistors and a

thermistor as shown in the R<sub>T</sub> network below.

Figure 3 R<sub>T</sub> Network

If Rth is an NTC thermistor then the resistance of the network will decrease as temperature increases. Unfortunately, most thermistors exhibit far more variation with temperature than copper wire. One equation used to model thermistors is

$$R_{th}(T) = R_{th}(T_0) \cdot e^{\left(\beta \left(\frac{1}{T} - \frac{1}{T_0}\right)\right)}$$

(2)

where  $R_{th}(T)$  is the thermistor resistance at some temperature T,  $R_{th}(T_0)$  is the thermistor resistance at the reference temperature  $T_0$ , and  $\beta$  is the material constant provided by the thermistor manufacturer. Kelvin degrees are used in the exponential term of equation 2. If  $R_s$  is large and  $R_p$  is small, the curvature of the equivalent network resistance can be reduced from the curvature of the thermistor alone. Although the exponential equation 2 can never compensate linear equation 1 at all temperatures, a spreadsheet can be constructed to minimize error over the temperature interval of interest. The resistance  $R_T$  of the network shown as a function of temperature is

$$R_{T}(T) = R_{s} + \frac{1}{\frac{1}{R_{p}} + \frac{1}{R_{th}(T)}}$$

(3)

using  $R_{th}(T)$  from equation 2. Equation 4 may be written as a function of temperature using equations 1 and 3 as follows:

$$I_{FS}(T) = \frac{V_{IG}}{R_T(T)} \cdot \frac{\left(R_{CS1} + R_{CS2}\right)}{DCR(T)}.$$

(4)

With Rs and Rp as additional free variables, use a spreadsheet to solve equation 4 for the desired full scale current while minimizing the  $I_{FS}(T)$  variation over temperature.

### ERROR MANAGEMENT

Component value errors external to the IR3725 contribute to power and current measurement error. The power reported by the IR3725 is a function not only of actual power or current, but also of products and quotients of R<sub>T</sub>, R<sub>CS1</sub>, R<sub>CS2</sub>, DCR (or R<sub>SHUNT</sub>), as well as parameters internal to the IR3725. The tolerance of these components increases the total power or current error. Small signal resistors are typically available in 1% tolerance, but 0.1% parts are available. Shunts are also available at 1% or 0.1% tolerance. The DCR tolerance of inductors can be 5%, but 3% are available. Fortunately, it is not typical that worst-case errors would systematically stack in one direction. It is statistically likely that a high going value would be paired with a low going value to somewhat cancel the error. Because of this, tolerances can be added in guadrature (RSS). As an example, a 3% DCR used with a 1% R<sub>T</sub>, a 1% R<sub>CS</sub>, and 1.5% IR3725 contributes

$$\sqrt{(0.03)^2 + (0.01)^2 + (0.01)^2 + (0.015)^2} \approx 3.6\%$$

error to a typical system.

### LAYOUT GUIDELINES

The following guidelines will minimize noise and error. Refer to the Functional Description Diagram.

- 1. Bypass VDD to GND with a high quality ceramic capacitor.

- 2. Place Ccs2 close to IC pins Vcs1 and Vcs2. Route Vcs1 and Vcs2 to the current sensing element as a differential pair.

- 3. Sense the current sensing element at its terminals, Kelvin style. Current and power will be over reported if printed wire board resistance is included between the sense points.

- 4. If inductor DCR current sensing is used, place the compensating thermistor near the inductor. Route the thermistor leads back to the vicinity of the IC with differential routing. Void any vias going to ground along the path back until near the IC. Locate the thermistor network (not the thermistor) near the IC.

Quantization error occurs in digital systems because the full scale is partitioned into a finite number of intervals and the number of the interval containing the measured value is reported. It is not likely that the measured value would correspond exactly to the center of the interval. The error could be as large as half the width of the interval. With a binary word size of eight, full scale is partitioned into 255 intervals. Consider a measurement made near full scale. Any signal in this interval is less than  $\pm .2\%$  (one-half of 100% / 256) away from the interval's center, and would therefore never have more error than that due to quantization. On the other hand, consider a measurement at one-tenth full scale. One-half of an interval size at this level corresponds to 2% of the reported value! Relative quantization error increases as the measured value becomes small compared to the full-scale value.

Quantization error can be reduced by averaging a sequence of returned values.

- 5. VO should sense the voltage at the point of interest. Bypass VO to GND with a high quality ceramic capacitor near the IC.

- Use an isolated dedicated ground plane connected only to grounded components associated with the IC in the figure. Connect this dedicated ground plane at one location to the ground of the monitored voltage.

- 7. Do not connect pin 12 to any electrically active node.

### **CONFIGURATION REGISTER**

A configuration register is maintained via the serial bus MFR\_SPECIFIC\_00 command, code # D0h. The low order nibble (d3, d2, d1, d0) contains a binary number N from zero to eight. The averaging interval is  $2^{N}$  milliseconds. N defaults to zero on start up.

The next bit (d4) is to be used as a function shutdown bit. b'1 commands an energy saving shutdown mode, and power on default b'0 commands fully functioning mode.

d5 high enables the EXTCLK pin to receive the external clock signal, and default d5 low enables the internal clock.

The next two bits (d7, d6) program the output parameter. B'00 causes power to be measured and is the power on default state. B'01 causes voltage to be measured. B'10 causes current to be measured. B'11 is not defined and should not be used.

The next bit (d8) is used to configure the ALERT# pin. b'0 is the power on default, and commands ALERT# to be pulled low when new data is available. b'1 programs the ALERT# to pull low when the programmable threshold level is exceeded, whether it is power, voltage, or current.

Register bits (d15...d9) are the ALERT# threshold register. If the output register is larger than this register, and if (d8) is b'1, then the ALERT# pin will pull low. The two least significant bits of the output register are not represented in the ALERT# threshold register. d15...d9 defaults to zero on start up. The results of a configuration register change will be reflected in the OUTPUT REGISTER after previously requested operations have completed. Initialize the configuration register after start up.

| BIT # | CONFIGURATION REGISTER     |

|-------|----------------------------|

|       |                            |

| d0    | Averaging interval (LSB)   |

| d1    | Averaging interval         |

| d2    | Averaging interval         |

| d3    | Averaging interval (MSB)   |

| d4    | Shutdown                   |

| d5    | External clock             |

| d6    | OUTPUT config (LSB)        |

| d7    | OUTPUT config (MSB)        |

| d8    | ALERT# configuration       |

| d9    | ALERT# threshold (LSB + 2) |

| d10   | ALERT# threshold           |

| d11   | ALERT# threshold           |

| d12   | ALERT# threshold           |

| d13   | ALERT# threshold           |

| d14   | ALERT# threshold           |

| d15   | ALERT# threshold (MSB)     |

### **OUTPUT REGISTER**

The output register is loaded with a two's compliment factor of voltage, current, or power, depending on the last request loaded into the configuration register. Serial bus "Direct Data Format" is used. The value of the output register is to be multiplied by a scale factor that is derived below to yield power, voltage, or current in engineering units of watts, volts, or amps. Maximum power is the product of maximum voltage and maximum current.

The range of valid output register values is indicated in Table 2 below.

## Table 2 Output Register Range of ReturnedValues

| Parameter    | Returned value      | Returned  |

|--------------|---------------------|-----------|

|              | (twos compliment    | value     |

|              | binary)             | (decimal) |

| FS voltage   | 0100 0000 0000 0000 | 256       |

| Zero voltage | 0000 0000 0000 0000 | 0         |

| +FS current  | 0100 0000 0000 0000 | 256       |

| -FS current  | 1100 0000 0000 0000 | -256      |

| +FS power    | 0100 0000 0000 0000 | 256       |

| -FS power    | 1100 0000 0000 0000 | -256      |

A binary point is implicitly located to the left of the first six least significant figures, as in the example below.

#### SYYY YYYY YY.00 0000

The "S" above is the twos compliment sign bit, and the "Y's" are the twos compliment integers. Six zeros pad out the two byte response. These padding zeros could be considered a factor of the slope, which is allowed by the Direct Data Format. The output register multiplied by its scale factor  $K_x$  yields the requested quantity in engineering units, volts, amps, or watts.

The equations below convert digital counts to engineering units:

Voltage = counts \* V<sub>FS</sub> / 256

Current = counts \*  $V_{IG}$  \* ( $R_{CS1}$ + $R_{CS2}$ ) / ( $R_T$  \* DCR \* 256)

Power = counts \*  $V_{FS}$ \* $V_{IG}$ \*(Rcs1 + Rcs2) / (R<sub>T</sub>\*DCR\*256)

There is but one output register, and it holds the measurement type (voltage, current, or power) last requested by the configuration register. It is incumbent upon the user to establish correct configuration before requesting a read. READ\_VOUT, READ\_IOUT, and READ\_POUT are equivalent in that each returns the contents of the same output register.

| BIT#   | OUTPUT REGISTER            |

|--------|----------------------------|

| d15:d0 | Output variable, D0 is LSB |

#### RESERVED COMMAND CODES

Command codes D2h through D5h, D7h, and D8h are reserved for manufacturing use only and could lead to undesirable device behavior.

### PACKET PROTOCOL

- S = Start Condition

- W = Bus write (0)

- R = Bus read (1)

- A = Acknowledge, = 0 for ACK, =1 for NACK

- P = Stop Condition

- = master to slave

- = slave to master

#### **Bus Write CONFIGURATION Register**

| s | Slave Address | w | Α |   | С | om | mai | nd | Co | de |   | А |    | [  | Data | a By | yte | Lov | N  |    | А |     |     | Data | a Byte | e High | 1   |    |    | А | Р |

|---|---------------|---|---|---|---|----|-----|----|----|----|---|---|----|----|------|------|-----|-----|----|----|---|-----|-----|------|--------|--------|-----|----|----|---|---|

| S | see Table 1   | 0 | А | 1 | 1 | 0  | 1   | 0  | 0  | 0  | 0 | А | d7 | d6 | d5   | d4   | d3  | d2  | d1 | d0 | А | d15 | d14 | d13  | d12    | d11    | d10 | d9 | d8 | А | Р |

#### Bus Read CONFIGURATION Register

| S | Slave<br>Address | W | А | Command Code A S    | Slave<br>Address | R | A  | I     | Data | a By | te Lo | OW    |    | А |     |     | Da  | ata B | yte H | ligh |    |    | А | Ρ |

|---|------------------|---|---|---------------------|------------------|---|----|-------|------|------|-------|-------|----|---|-----|-----|-----|-------|-------|------|----|----|---|---|

| S | see<br>Table 1   | 0 | А | 1 1 0 1 0 0 0 0 A S | See<br>Table 1   | 1 | Ad | l7 d6 | d5   | d4   | d3 (  | d2 d1 | d0 | А | d15 | d14 | d13 | d12   | d11   | d10  | d9 | d8 | 1 | Ρ |

#### Bus READ\_VOUT (Output Register for Configuration register Data Byte Low = 01XXXXXX)

| S | Slave<br>Address | W | А | Command Code A    | Slave<br>Address | R | А   | C    | Data I | Byte | Low  |       | А |     |     | Da  | ata B | yte ⊦ | ligh |    |    | А | Ρ |

|---|------------------|---|---|-------------------|------------------|---|-----|------|--------|------|------|-------|---|-----|-----|-----|-------|-------|------|----|----|---|---|

| S | see<br>Table 1   | 0 | А | 1 0 0 0 1 0 1 1 A | See<br>Table 1   | 1 | A d | 7 d6 | d5 d4  | 4 d3 | d2 ( | d1 d0 | А | d15 | d14 | d13 | d12   | d11   | d10  | d9 | d8 | 1 | Ρ |

#### Bus READ\_IOUT (Output Register for Configuration register Data Byte Low = 10XXXXXX)

| S | Slave<br>Address | W | А | Command Code A S    | Slave<br>Address | R | А | Data Byte Low |    |    |    |       | A  |   | Data Byte High |     |     |     |     |     |    | А  | Ρ |   |

|---|------------------|---|---|---------------------|------------------|---|---|---------------|----|----|----|-------|----|---|----------------|-----|-----|-----|-----|-----|----|----|---|---|

| S | see<br>Table 1   | 0 | А | 1 0 0 0 1 1 0 0 A S | See<br>Table 1   | 1 | A | d7 d6         | d5 | d4 | d3 | d2 d1 | d0 | A | d15            | d14 | d13 | d12 | d11 | d10 | d9 | d8 | 1 | Ρ |

#### Bus READ\_POUT (Output Register for Configuration register Data Byte Low = 00XXXXXX)

| S | Slave<br>Address | w | А | Command Code  | A S   | Slave<br>Address | R | 4           | Data Byte Low |      |    |    |    |    | А | Data Byte High |     |     |     |     |     |    |    | А | Ρ |

|---|------------------|---|---|---------------|-------|------------------|---|-------------|---------------|------|----|----|----|----|---|----------------|-----|-----|-----|-----|-----|----|----|---|---|

| S | see<br>Table 1   | 0 | А | 1 0 0 1 0 1 1 | 0 A S | See<br>Table 1   | 1 | <b>A</b> d7 | d6 d          | 5 d4 | d3 | d2 | d1 | d0 | А | d15            | d14 | d13 | d12 | d11 | d10 | d9 | d8 | 1 | Ρ |

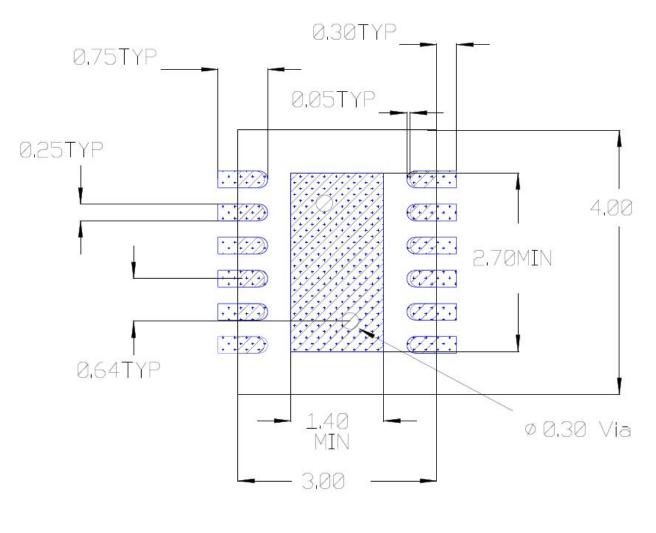

### PCB PAD AND COMPONENT PLACEMENT

The figure below shows a suggested pad and component placement.

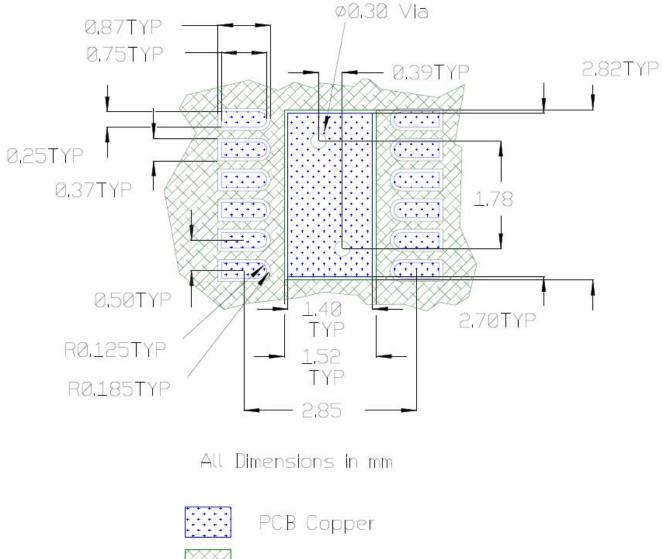

All Dimensions in mm

PCB Copper

Component

### SOLDER RESIST

The figure below shows a suggested solder resist placement.

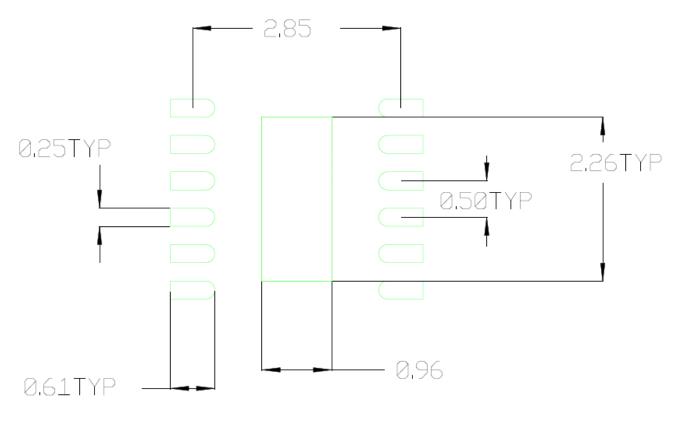

The figure below shows a suggested solder stencil design.

Stencil Aperture All Dimensions in mm

# International **IOR** Rectifier

L

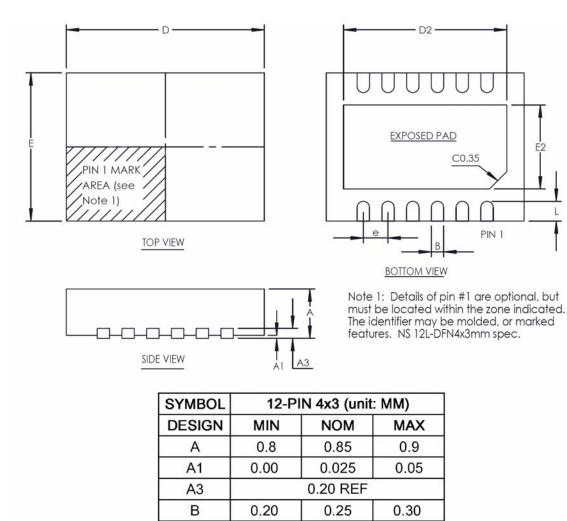

### **PACKAGE INFORMATION**

#### 4 X 3 MM 12L DFN LEAD FREE

3.90

3.20

2.90

1.60

0.30

4.00

3.30

3.00

1.70

0.5 TYP

0.40

4.10

3.40

3.10

1.80

0.50

D

D2

E

E2

e L

> Data and specifications subject to change without notice. This product has been designed and gualified for the Consumer market. Qualification Standards can be found on IR's Web site.

### International er

IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245, USA Tel: (310) 252-7105 TAC Fax: (310) 252-7903 Visit us at www.irf.com for sales contact information.