## BGM15LA12

Low-Band LNA Multiplexer Module

# **Data Sheet**

Revision 3.0 - 2015-07-24

# Power Management & Multimarket

Edition 2015-07-24

Published by Infineon Technologies AG 81726 Munich, Germany

©2015 Infineon Technologies AG All Rights Reserved.

#### **LEGAL DISCLAIMER**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office. Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

#### **Revision History**

Document No.: BGM15LA12\_v3.0.pdf

Revision History: Rev. v3.0

Previous Version: Preliminary, Revision v2.4 - 2014-08-21

|      | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                      |  |  |  |  |  |  |

|------|-----------------------------------------------------------|--|--|--|--|--|--|

| Page | Subjects (major changes since last revision)              |  |  |  |  |  |  |

| all  | "Preliminary" status removed                              |  |  |  |  |  |  |

| 19   | Package Outline Drawing: Minimum package height specified |  |  |  |  |  |  |

| 19   | Marking Specification added                               |  |  |  |  |  |  |

| 20   | Footprint Recommendation added                            |  |  |  |  |  |  |

|      |                                                           |  |  |  |  |  |  |

#### **Trademarks of Infineon Technologies AG**

$AURIX^{TM}, C166^{TM}, CanPAK^{TM}, CIPOS^{TM}, CIPURSE^{TM}, CoolGaN^{TM}, CoolMOS^{TM}, CoolSiC^{TM}, CORECONTROL^{TM}, CROSSAVE^{TM}, DAVE^{TM}, DI-POL^{TM}, DrBLADE^{TM}, EasyPIM^{TM}, EconoBRIDGE^{TM}, EconoDUAL^{TM}, EconoPACK^{TM}, EconoPIM^{TM}, EiceDRIVER^{TM}, eupec^{TM}, FCOS^{TM}, HITFET^{TM}, HybridPACK^{TM}, ISOFACE^{TM}, IsoPACK^{TM}, i-Wafer^{TM}, MIPAQ^{TM}, ModSTACK^{TM}, my-d^{TM}, NovalithIC^{TM}, OmniTune^{TM}, OPTIGA^{TM}, OptiMOS^{TM}, ORIGA^{TM}, POWERCODE^{TM}, PRIMARION^{TM}, PrimePACK^{TM}, PROFET^{TM}, PRO-SIL^{TM}, RASIC^{TM}, REAL3^{TM}, ReverSave^{TM}, SatRIC^{TM}, SIEGET^{TM}, SIPMOS^{TM}, SmartLEWIS^{TM}, SOLID FLASH^{TM}, SPOC^{TM}, TEMPFET^{TM}, thinQ!^{TM}, TRENCHSTOP^{TM}, TriCore^{TM}.$

#### **Other Trademarks**

Advance Design System<sup>TM</sup> (ADS) of Agilent Technologies, AMBA<sup>TM</sup>, ARM<sup>TM</sup>, MULTI-ICE<sup>TM</sup>, KEIL<sup>TM</sup>, PRIMECELL<sup>TM</sup>, REALVIEW<sup>TM</sup>, THUMB<sup>TM</sup>,  $\mu$ Vision<sup>TM</sup> of ARM Limited, UK. ANSI<sup>TM</sup> of American National Standards Institute. AUTOSAR<sup>TM</sup> of AUTOSAR development partnership. Bluetooth<sup>TM</sup> of Bluetooth SIG Inc. CAT-iq<sup>TM</sup> of DECT Forum. COLOSSUS<sup>TM</sup>, FirstGPS<sup>TM</sup> of Trimble Navigation Ltd. EMV<sup>TM</sup> of EMVCo, LLC (Visa Holdings Inc.). EPCOS<sup>TM</sup> of Epcos AG. FLEXGO<sup>TM</sup> of Microsoft Corporation. HYPERTERMINAL<sup>TM</sup> of Hilgraeve Incorporated. MCS<sup>TM</sup> of Intel Corp. IEC<sup>TM</sup> of Commission Electrotechnique Internationale. IrDA<sup>TM</sup> of Infrared Data Association Corporation. ISO<sup>TM</sup> of INTERNATIONAL ORGANIZATION FOR STANDARD-IZATION. MATLAB<sup>TM</sup> of MathWorks, Inc. MAXIM<sup>TM</sup> of Maxim Integrated Products, Inc. MICROTEC<sup>TM</sup>, NUCLEUS<sup>TM</sup> of Mentor Graphics Corporation. MIPI<sup>TM</sup> of MIPI Alliance, Inc. MIPS<sup>TM</sup> of MIPS Technologies, Inc., USA. muRata<sup>TM</sup> of MURATA MANU-FACTURING CO., MICROWAVE OFFICE<sup>TM</sup> (MWO) of Applied Wave Research Inc., OmniVision<sup>TM</sup> of OmniVision Technologies, Inc. Openwave<sup>TM</sup> of Openwave Systems Inc. RED HAT<sup>TM</sup> of Red Hat, Inc. RFMD<sup>TM</sup> of RF Micro Devices, Inc. SIRIUS<sup>TM</sup> of Sirius Satellite Radio Inc. SOLARIS<sup>TM</sup> of Sun Microsystems, Inc. SPANSION<sup>TM</sup> of Spansion LLC Ltd. Symbian<sup>TM</sup> of Symbian Software Limited. TAIYO YUDEN<sup>TM</sup> of Taiyo Yuden Co. TEAKLITE<sup>TM</sup> of CEVA, Inc. TEKTRONIX<sup>TM</sup> of Tektronix Inc. TOKO<sup>TM</sup> of TOKO KABUSHIKI KAISHA TA. UNIX<sup>TM</sup> of X/Open Company Limited. VERILOG<sup>TM</sup>, PALLADIUM<sup>TM</sup> of Cadence Design Systems, Inc. VLYNQ<sup>TM</sup> of Texas Instruments Incorporated. VXWORKS<sup>TM</sup>, WIND RIVER<sup>TM</sup> of WIND RIVER SYSTEMS, INC. ZETEX<sup>TM</sup> of Diodes Zetex.

Last Trademarks Update 2014-07-17

### **Contents**

| 1 | Features                                                                                                                  | 6                         |

|---|---------------------------------------------------------------------------------------------------------------------------|---------------------------|

| 2 | Product Description                                                                                                       | 6                         |

| 3 | Maximum Ratings                                                                                                           | 7                         |

| 4 | DC Characteristics                                                                                                        | 8                         |

| 5 | RF Characteristics         5.1 BAND 8          5.2 BAND 12          5.3 BAND 20          5.4 BAND 26          5.5 BAND 28 | 9<br>10<br>11<br>12<br>13 |

| 6 | MIPI RFFE Specification                                                                                                   | 14                        |

| 7 | Application Information                                                                                                   | 20                        |

| 8 | Package Information                                                                                                       | 22                        |

### **List of Figures**

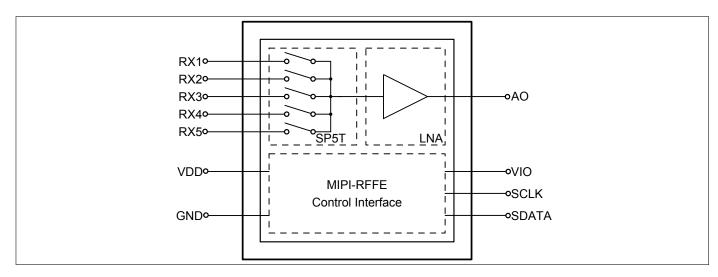

| 1  | BGM15LA12 Block diagram                                 |

|----|---------------------------------------------------------|

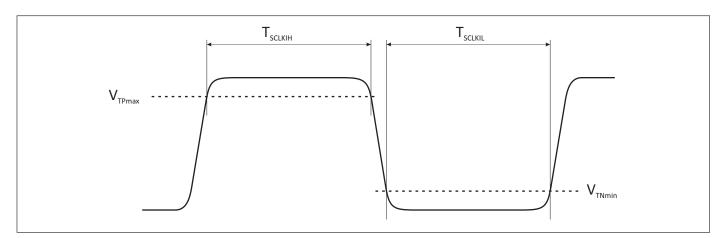

| 2  | Received clock signal constraints                       |

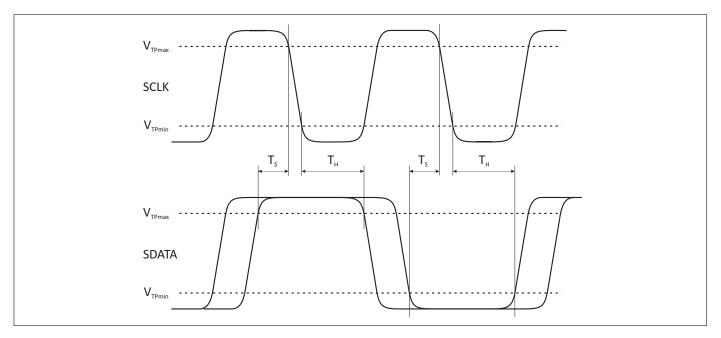

| 3  | Bus active data receiver timing requirements            |

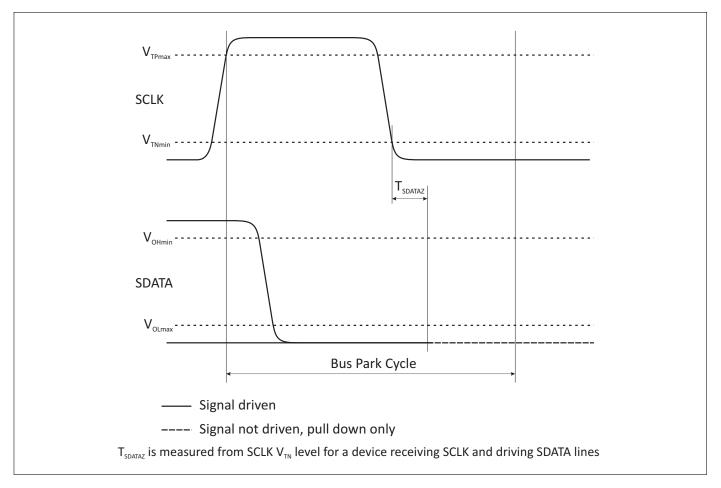

| 4  | Bus park cycle timing                                   |

| 5  | Bus active data transmission timing specification       |

| 6  | Requirements for VIO-initiated reset                    |

| 7  | BGM15LA12 Pin Configuration (top view)                  |

| 8  | BGM15LA12 Application Schematic                         |

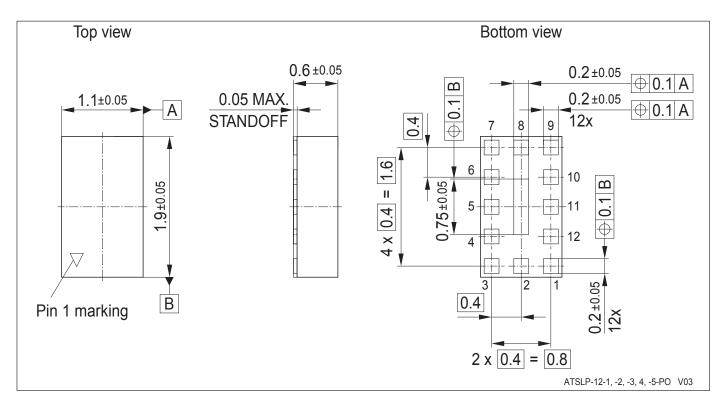

| 9  | ATSLP-12-1 Package Outline (top, side and bottom views) |

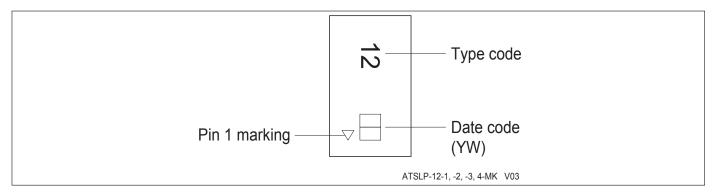

| 10 | Marking Specification (top view)                        |

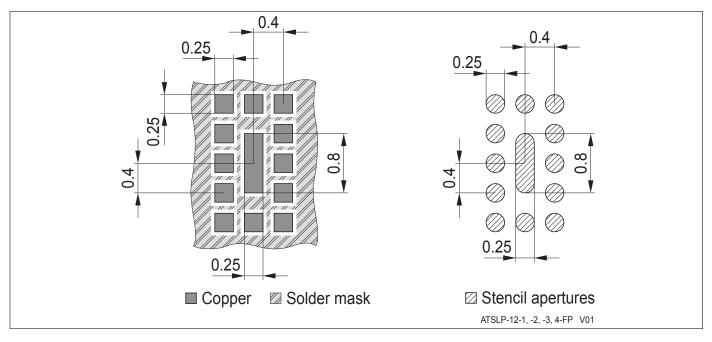

| 11 | Footprint Recommendation                                |

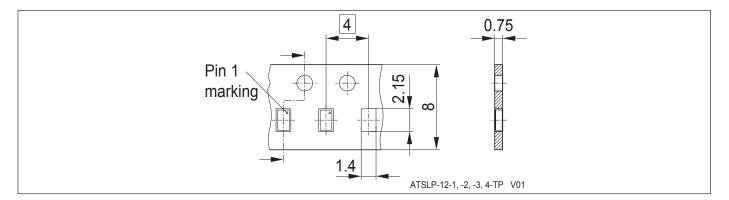

| 12 | ATSI P-12-1 Carrier Tane                                |

Data Sheet 4 Revision 3.0 - 2015-07-24

### **List of Tables**

|    | Ordering Information        |

|----|-----------------------------|

| 2  | Maximum Ratings             |

| 4  | DC Characteristics          |

| 5  | RF Characteristics Band 8   |

| 6  | RF Characteristics Band 12  |

| 7  | RF Characteristics Band 20  |

| 8  | RF Characteristics Band 26  |

| 9  | RF Characteristics Band 28  |

| 10 | MIPI Features               |

| 11 | Startup Behavior            |

| 12 | MIPI RFFE operating timing  |

| 13 | Register Mapping            |

| 14 | Truth Table, Register_0 19  |

| 15 | Pin Definition and Function |

| 16 | Bill of Materials           |

#### **BGM15LA12 Low-Band LNA Multiplexer Module**

#### 1 Features

Power gain: 17.5 dBLow noise figure: 1.1 dB

Low current consumption: 4.9 mA

Frequency range from 0.7 to 1.0 GHz

• RF output internally matched to 50  $\Omega$

· Low external component count

• High port-to-port-isolation

• Suitable for LTE / LTE-Advanced and 3G applications

• No decoupling capacitors required if no DC applied on RF lines

• On chip control logic including ESD protection

Supply voltage: 2.2 to 3.3 V

Integrated MIPI RFFE interface operating in 1.1 to 1.95 V voltage range

Software programmable MIPI RFFE USID

• Small form factor 1.1 mm x 1.9 mm

• High EMI robustness

RoHS and WEEE compliant package

### **2 Product Description**

The BGM15LA12 is a LNA multiplexer module for LTE low-band frequencies that increases the data rate while keeping flexibility and low footprint. It is a perfect solution for multimode handsets based on LTE-Advanced and WCDMA. The BGM15LA12 is controlled via a MIPI RFFE controller. The device configuration is shown in Fig. 12.

**Table 1: Ordering Information**

| Туре      | Package    | Marking |

|-----------|------------|---------|

| BGM15LA12 | ATSLP-12-1 | L1      |

(a) Infineon

Figure 1: BGM15LA12 Block diagram

### 3 Maximum Ratings

**Table 2: Maximum Ratings**

| Parameter                   | Symbol Values        |      |      |                      | Unit | Note / Test Condition    |

|-----------------------------|----------------------|------|------|----------------------|------|--------------------------|

|                             |                      | Min. | Тур. | Max.                 |      |                          |

| Supply Voltage VDD          | $V_{DD}$             | -0.3 | _    | 3.6                  | ٧    | 1                        |

| Voltage at RF pins Rx       | V <sub>Rx</sub>      | -0.3 | _    | 0.9                  | ٧    | _                        |

| Voltage at RF output pin AO | V <sub>AO</sub>      | -0.3 | _    | V <sub>DD</sub> +0.3 | ٧    | _                        |

| Voltage at GND pins         | $V_{GND}$            | -0.3 | _    | 0.3                  | ٧    | _                        |

| Current into pin VDD        | I <sub>DD</sub>      | _    | _    | 16                   | mA   | _                        |

| RF input power              | P <sub>IN</sub>      | _    | _    | 0                    | dBm  | _                        |

| Total power dissipation     | P <sub>tot</sub>     | _    | _    | 60                   | mW   |                          |

| Junction temperature        | T <sub>J</sub>       | _    | _    | 150                  | °C   | _                        |

| Ambient temperature range   | T <sub>A</sub>       | -40  | _    | 85                   | °C   | _                        |

| Storage temperature range   | T <sub>STG</sub>     | -65  | _    | 150                  | °C   | _                        |

| ESD capability, HBM         | V <sub>ESD_HBM</sub> | _    | _    | 1000                 | ٧    | according to JESD22A-114 |

| RFFE Supply Voltage         | V <sub>IO</sub>      | -0.5 | _    | 3.6                  | ٧    | _                        |

| DEEE Cupply Voltage Layele  | V <sub>SCLK</sub> ,  | -0.7 | _    | V <sub>IO</sub> +0.7 | V    | _                        |

| RFFE Supply Voltage Levels  | V <sub>SDATA</sub>   |      |      | (max.                |      |                          |

|                             |                      |      |      | 3.6)                 |      |                          |

<sup>&</sup>lt;sup>1</sup> All voltages refer to GND-Nodes unless otherwise noted

Attention: Stresses above the max. values listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Maximum ratings are absolute ratings; exceeding only one of these values may cause irreversible damage to the integrated circuit.

### **4 DC Characteristics**

Table 4: DC Characteristics at  $T_{\rm A}$  = 25 °C

| Parameter <sup>1</sup>                | Symbol            | Values              |      |                     | Unit | Note / Test Condition |

|---------------------------------------|-------------------|---------------------|------|---------------------|------|-----------------------|

|                                       |                   | Min.                | Тур. | Max.                |      |                       |

| Supply Voltage                        | $V_{DD}$          | 2.2                 | _    | 3.3                 | ٧    | _                     |

| Supply Current                        | I <sub>DD</sub>   | _                   | 4.9  | 5.9                 | mA   | ON-mode               |

|                                       |                   | _                   | 0.1  | 2                   | μΑ   | OFF-Mode              |

| RFFE supply voltage                   | V <sub>IO</sub>   | 1.1                 | 1.8  | 1.95                | V    | _                     |

| RFFE input high voltage <sup>2</sup>  | V <sub>IH</sub>   | 0.7*V <sub>IO</sub> | _    | V <sub>IO</sub>     | V    | _                     |

| RFFE input low voltage <sup>2</sup>   | V <sub>IL</sub>   | 0                   | _    | 0.3*V <sub>IO</sub> | ٧    | _                     |

| RFFE output high voltage <sup>2</sup> | V <sub>OH</sub>   | 0.8*V <sub>IO</sub> | _    | V <sub>IO</sub>     | ٧    | _                     |

| RFFE output low voltage <sup>2</sup>  | V <sub>OL</sub>   | 0                   | _    | 0.2*V <sub>IO</sub> | ٧    | _                     |

| RFFE control input capaci-            | C <sub>Ctrl</sub> | _                   | _    | 2                   | pF   | _                     |

| tance                                 |                   |                     |      |                     |      |                       |

| RFFE supply current                   | I <sub>VIO</sub>  | _                   | 15   | -                   | μΑ   | Idle State            |

<sup>&</sup>lt;sup>1</sup>Based on the application described in Chapter 7

<sup>&</sup>lt;sup>2</sup>SCLK and SDATA

### **5 RF Characteristics**

#### 5.1 BAND 8

Table 5: RF Characteristics Band 8 at  $T_{\rm A}$  = 25 °C,  $V_{\rm DD}$  = 2.8 V, f = 925 – 960 MHz, with matching described in Chapter 7 (C=1.1 pF, L=11 nH )

| Parameter <sup>1</sup>                                               | Symbol              |      | Values |      | Unit    | Note / Test Condition                             |  |

|----------------------------------------------------------------------|---------------------|------|--------|------|---------|---------------------------------------------------|--|

|                                                                      |                     | Min. | Тур.   | Max. |         |                                                   |  |

| Insertion power gain <sup>2</sup>                                    | $ S_{21} ^2$        | 14.3 | 15.8   | 17.3 | dB      | _                                                 |  |

| Noise figure <sup>2</sup>                                            | NF                  | _    | 1.1    | 1.6  | dB      | Z <sub>S</sub> =50 Ω                              |  |

| Input return loss <sup>2 3</sup>                                     | RLin                | 8    | 11     | _    | dB      | -                                                 |  |

| Output return loss <sup>2 3</sup>                                    | RLout               | 12   | >20    | _    | dB      | -                                                 |  |

| Reverse isolation AO to RX port <sup>2</sup>                         | $1/ S_{12} ^2$      | 19   | 23     | -    | dB      | -                                                 |  |

| Inband input 1dB-<br>compression point <sup>2 3</sup>                | IP <sub>1dB</sub>   | -11  | -8     | _    | dBm     | -                                                 |  |

| Inband input 3 <sup>rd</sup> -order intercept point <sup>2 3 4</sup> | IIP <sub>3</sub>    | -4   | -1     | _    | dBm     | $f_1$ =937 MHz, $f_2$ =947 MHz, $f_{12}$ =927 MHz |  |

| Isolation RX to RX port <sup>2 5</sup>                               | ISO                 | 35   | 40     | _    | dB      |                                                   |  |

| Isolation RX to AO port <sup>2 5</sup>                               | ISO                 | 24   | 29     | _    | dB      | forward direction                                 |  |

| Stability <sup>5</sup>                                               | k                   | >1   | -      | _    |         | f=20 MHz-10 GHz                                   |  |

| RF Rise Time RX Port                                                 | t <sub>on/off</sub> | 0.5  | 1      | 5    | $\mu$ S | 10 % to 90 % ON;                                  |  |

| On/Off <sup>5</sup>                                                  |                     |      |        |      |         | 90 % to 10 % ON                                   |  |

| Power Up Settling Time <sup>5</sup>                                  | t <sub>BC</sub>     | _    | 10     | 25   | $\mu$ S | After power down mode                             |  |

<sup>&</sup>lt;sup>1</sup>The parameter values are valid at any RX port using the matching described in Chapter 7

Data Sheet 9 Revision 3.0 - 2015-07-24

<sup>&</sup>lt;sup>2</sup>PCB losses are subtracted

<sup>&</sup>lt;sup>3</sup> Verification based on AQL; not 100% tested in production

$<sup>^{4}</sup>$ Input power =  $-30 \, dBm$  for each tone

<sup>&</sup>lt;sup>5</sup>Guaranteed by device design; not tested in production

#### 5.2 BAND 12

Table 6: RF Characteristics Band 12 at  $T_{\rm A}$  = 25 °C,  $V_{\rm DD}$  = 2.8 V, f = 729 – 746 MHz, with matching described in Chapter 7 (C=2.2 pF, L=16 nH)

| Parameter <sup>1</sup>                                               | Symbol                  | mbol Values |      |      | Unit    | Note / Test Condition                                                           |  |

|----------------------------------------------------------------------|-------------------------|-------------|------|------|---------|---------------------------------------------------------------------------------|--|

|                                                                      |                         | Min.        | Тур. | Max. |         |                                                                                 |  |

| Insertion power gain <sup>2</sup>                                    | $ S_{21} ^2$            | 15.2        | 16.7 | 18.2 | dB      | _                                                                               |  |

| Noise figure <sup>2</sup>                                            | NF                      | _           | 1.2  | 1.7  | dB      | $Z_{\rm S}$ =50 $\Omega$                                                        |  |

| Input return loss <sup>2 3</sup>                                     | <i>RL</i> <sub>in</sub> | 8           | 11   | _    | dB      | _                                                                               |  |

| Output return loss <sup>2 3</sup>                                    | RLout                   | 8           | 12   | _    | dB      | _                                                                               |  |

| Reverse isolation AO to RX port <sup>2 3</sup>                       | $1/ S_{12} ^2$          | 19          | 23   | _    | dB      | _                                                                               |  |

| Inband input 1dB-<br>compression point <sup>2 3</sup>                | IP <sub>1dB</sub>       | -14         | -11  | -    | dBm     | -                                                                               |  |

| Inband input 3 <sup>rd</sup> -order intercept point <sup>2 3 4</sup> | IIP <sub>3</sub>        | -7          | -4   | -    | dBm     | $f_1 = 732 \text{ MHz},  f_2 = 742 \text{ MHz}, $<br>$f_{12} = 722 \text{ MHz}$ |  |

| Isolation RX to RX port <sup>2 5</sup>                               | ISO                     | 34          | 39   | _    | dB      |                                                                                 |  |

| Isolation RX to AO port <sup>2 5</sup>                               | ISO                     | 24          | 29   | _    | dB      | forward direction                                                               |  |

| Stability <sup>5</sup>                                               | k                       | >1          | _    | _    |         | f=20 MHz-10 GHz                                                                 |  |

| RF Rise Time RX Port On/Off <sup>5</sup>                             | t <sub>on/off</sub>     | 0.5         | 1    | 5    | $\mu$ S | 10 % to 90 % ON;<br>90 % to 10 % ON                                             |  |

| Power Up Settling Time <sup>5</sup>                                  | t <sub>BC</sub>         | _           | 10   | 25   | μs      | After power down mode                                                           |  |

$<sup>^{\</sup>rm 1}{\rm The}$  parameter values are valid at any RX port using the matching described in Chapter 7  $^{\rm 2}{\rm PCB}$  losses are subtracted

Revision 3.0 - 2015-07-24 **Data Sheet** 10

<sup>&</sup>lt;sup>3</sup>Verification based on AQL; not 100% tested in production

$<sup>^{4}</sup>$ Input power =  $-30 \, dBm$  for each tone

<sup>&</sup>lt;sup>5</sup>Guaranteed by device design; not tested in production

#### 5.3 BAND 20

Table 7: RF Characteristics Band 20 at  $T_{\rm A}$  = 25 °C,  $V_{\rm DD}$  = 2.8 V, f = 791 – 821 MHz, with matching described in Chapter 7 (C=1.8 pF, L=15 nH)

| Parameter <sup>1</sup>                                                    | Symbol                   | Symbol Values |      | Unit | Note / Test Condition |                                                   |  |

|---------------------------------------------------------------------------|--------------------------|---------------|------|------|-----------------------|---------------------------------------------------|--|

|                                                                           |                          | Min.          | Тур. | Max. |                       |                                                   |  |

| Insertion power gain <sup>2</sup>                                         | $ S_{21} ^2$             | 15            | 16.5 | 18   | dB                    | _                                                 |  |

| Noise figure <sup>2</sup>                                                 | NF                       | _             | 1.15 | 1.65 | dB                    | Z <sub>S</sub> =50 Ω                              |  |

| Input return loss <sup>2 3</sup>                                          | <i>RL</i> <sub>in</sub>  | 8             | 11   | _    | dB                    | _                                                 |  |

| Output return loss <sup>2 3</sup>                                         | <i>RL</i> <sub>out</sub> | 11            | 19   | _    | dB                    | _                                                 |  |

| Reverse isolation AO to RX port <sup>2 3</sup>                            | $1/ S_{12} ^2$           | 20            | 24   | _    | dB                    | -                                                 |  |

| Inband input 1dB-<br>compression point <sup>2 3</sup>                     | IP <sub>1dB</sub>        | -13           | -10  | _    | dBm                   | -                                                 |  |

| Inband input 3 <sup>rd</sup> -order inter-<br>cept point <sup>2 3 4</sup> | IIP <sub>3</sub>         | -5            | -2   | _    | dBm                   | $f_1$ =801 MHz, $f_2$ =811 MHz, $f_{12}$ =791 MHz |  |

| Isolation RX to RX port <sup>2 5</sup>                                    | ISO                      | 34            | 39   | _    | dB                    |                                                   |  |

| Isolation RX to AO port <sup>2 5</sup>                                    | ISO                      | 24            | 29   | _    | dB                    | forward direction                                 |  |

| Stability <sup>5</sup>                                                    | k                        | >1            | _    | _    |                       | f=20 MHz-10 GHz                                   |  |

| RF Rise Time RX Port On/Off <sup>5</sup>                                  | t <sub>on/off</sub>      | 0.5           | 1    | 5    | $\mu$ S               | 10 % to 90 % ON;<br>90 % to 10 % ON               |  |

| Power Up Settling Time <sup>5</sup>                                       | t <sub>BC</sub>          | _             | 10   | 25   | $\mu$ s               | After power down mode                             |  |

$<sup>^{\</sup>rm 1}{\rm The}$  parameter values are valid at any RX port using the matching described in Chapter 7  $^{\rm 2}{\rm PCB}$  losses are subtracted

**Data Sheet** Revision 3.0 - 2015-07-24 11

<sup>&</sup>lt;sup>3</sup> Verification based on AQL; not 100% tested in production

$<sup>^{4}</sup>$ Input power =  $-30 \, dBm$  for each tone

<sup>&</sup>lt;sup>5</sup>Guaranteed by device design; not tested in production

#### 5.4 BAND 26

Table 8: RF Characteristics Band 26 at  $T_{\rm A}$  = 25 °C,  $V_{\rm DD}$  = 2.8 V, f = 859 – 894 MHz, with matching described in Chapter 7 (C=1.5 pF, L=13 nH)

| Parameter <sup>1</sup>                                                    | Symbol              |      | Values |      | Unit    | Note / Test Condition                             |  |

|---------------------------------------------------------------------------|---------------------|------|--------|------|---------|---------------------------------------------------|--|

|                                                                           |                     | Min. | Тур.   | Max. |         |                                                   |  |

| Insertion power gain <sup>2</sup>                                         | $ S_{21} ^2$        | 14.8 | 16.3   | 17.8 | dB      | _                                                 |  |

| Noise figure <sup>2</sup>                                                 | NF                  | _    | 1.2    | 1.7  | dB      | Z <sub>S</sub> =50 Ω                              |  |

| Input return loss <sup>2 3</sup>                                          | RL <sub>in</sub>    | 8    | 11     | _    | dB      | _                                                 |  |

| Output return loss <sup>2 3</sup>                                         | RL <sub>out</sub>   | 12   | >20    | _    | dB      | _                                                 |  |

| Reverse isolation AO to RX port <sup>2 3</sup>                            | $1/ S_{12} ^2$      | 19   | 23     | _    | dB      | -                                                 |  |

| Inband input 1dB-<br>compression point <sup>2 3</sup>                     | IP <sub>1dB</sub>   | -11  | -8     | _    | dBm     | -                                                 |  |

| Inband input 3 <sup>rd</sup> -order inter-<br>cept point <sup>2 3 4</sup> | IIP <sub>3</sub>    | -4   | -1     | -    | dBm     | $f_1$ =871 MHz, $f_2$ =881 MHz, $f_{12}$ =861 MHz |  |

| Isolation RX to RX port <sup>2 5</sup>                                    | ISO                 | 34   | 39     | _    | dB      |                                                   |  |

| Isolation RX to AO port <sup>2 5</sup>                                    | ISO                 | 24   | 29     | _    | dB      | forward direction                                 |  |

| Stability <sup>5</sup>                                                    | k                   | >1   | _      | _    |         | f=20 MHz-10 GHz                                   |  |

| RF Rise Time RX Port                                                      | t <sub>on/off</sub> | 0.5  | 1      | 5    | $\mu$ S | 10 % to 90 % ON;                                  |  |

| On/Off <sup>5</sup>                                                       |                     |      |        |      |         | 90 % to 10 % ON                                   |  |

| Power Up Settling Time <sup>5</sup>                                       | t <sub>BC</sub>     | _    | 10     | 25   | $\mu$ s | After power down mode                             |  |

$<sup>^{\</sup>rm 1}{\rm The}$  parameter values are valid at any RX port using the matching described in Chapter 7  $^{\rm 2}{\rm PCB}$  losses are subtracted

**Data Sheet** 12 Revision 3.0 - 2015-07-24

<sup>&</sup>lt;sup>3</sup> Verification based on AQL; not 100% tested in production

$<sup>^{4}</sup>$ Input power =  $-30 \, dBm$  for each tone

<sup>&</sup>lt;sup>5</sup>Guaranteed by device design; not tested in production

#### 5.5 BAND 28

Table 9: RF Characteristics Band 28 at  $T_{\rm A}$  = 25 °C,  $V_{\rm DD}$  = 2.8 V, f = 758 – 803 MHz, with matching described in Chapter 7 (C=2 pF, L=16 nH)

| Parameter <sup>1</sup>                                                    | Symbol                   | Symbol Values |      |      | Unit    | Note / Test Condition                                                         |  |

|---------------------------------------------------------------------------|--------------------------|---------------|------|------|---------|-------------------------------------------------------------------------------|--|

|                                                                           |                          | Min.          | Тур. | Max. |         |                                                                               |  |

| Insertion power gain <sup>2</sup>                                         | $ S_{21} ^2$             | 15.1          | 16.6 | 18.1 | dB      | _                                                                             |  |

| Noise figure <sup>2</sup>                                                 | NF                       | _             | 1.1  | 1.6  | dB      | Z <sub>S</sub> =50 Ω                                                          |  |

| Input return loss <sup>2 3</sup>                                          | RL <sub>in</sub>         | 8             | 11   | _    | dB      | _                                                                             |  |

| Output return loss <sup>2 3</sup>                                         | <i>RL</i> <sub>out</sub> | 11            | 16   | _    | dB      | _                                                                             |  |

| Reverse isolation AO to RX port <sup>2 3</sup>                            | $1/ S_{12} ^2$           | 21            | 25   | -    | dB      | -                                                                             |  |

| Inband input 1dB-<br>compression point <sup>2 3</sup>                     | IP <sub>1dB</sub>        | -13           | -10  | _    | dBm     | -                                                                             |  |

| Inband input 3 <sup>rd</sup> -order inter-<br>cept point <sup>2 3 4</sup> | IIP <sub>3</sub>         | -6            | -3   | _    | dBm     | $f_1 = 775 \text{ MHz}, $ $f_2 = 785 \text{ MHz},$ $f_{12} = 765 \text{ MHz}$ |  |

| Isolation RX to RX port <sup>2 5</sup>                                    | ISO                      | 34            | 39   | _    | dB      |                                                                               |  |

| Isolation RX to AO port <sup>2 5</sup>                                    | ISO                      | 24            | 29   | _    | dB      | forward direction                                                             |  |

| Stability <sup>5</sup>                                                    | k                        | >1            | _    | _    |         | f=20 MHz-10 GHz                                                               |  |

| RF Rise Time RX Port On/Off <sup>5</sup>                                  | t <sub>on/off</sub>      | 0.5           | 1    | 5    | $\mu$ S | 10 % to 90 % ON;<br>90 % to 10 % ON                                           |  |

| Power Up Settling Time <sup>5</sup>                                       | t <sub>BC</sub>          | _             | 10   | 25   | $\mu$ S | After power down mode                                                         |  |

$<sup>^{\</sup>rm 1}{\rm The}$  parameter values are valid at any RX port using the matching described in Chapter 7  $^{\rm 2}{\rm PCB}$  losses are subtracted

**Data Sheet** Revision 3.0 - 2015-07-24 13

<sup>&</sup>lt;sup>3</sup> Verification based on AQL; not 100% tested in production

$<sup>^{4}</sup>$ Input power =  $-30 \, dBm$  for each tone

<sup>&</sup>lt;sup>5</sup>Guaranteed by device design; not tested in production

### 6 MIPI RFFE Specification

All sequences are implemented according to the 'MIPI Alliance Specification for RF Front-End Control Interface' document version 1.10 - 26. July 2011.

**Table 10: MIPI Features**

| Feature                                  | Supported | Comment                                             |

|------------------------------------------|-----------|-----------------------------------------------------|

| Register write command sequence          | Yes       |                                                     |

| Register read command sequence           | Yes       |                                                     |

| Extended register write command sequence | No        | Up to 4 Bytes                                       |

| Extended register read command sequence  | No        | Up to 4 Bytes                                       |

| Register 0 write command sequence        | Yes       |                                                     |

| Trigger function                         | Yes       | Trigger assignment to each control register is sup- |

|                                          |           | ported                                              |

| Programmable USID                        | Yes       | 3 register command sequence and extended regis-     |

|                                          |           | ter command sequence                                |

| Status Register                          | Yes       | Register for debugging                              |

| Reset                                    | Yes       | By VIO, Power Mode and RFFE_STATUS                  |

| Group SID                                | Yes       |                                                     |

| USID_Sel pin                             | No        | External pin for changing USID is not implemented   |

| Full speed write                         | Yes       |                                                     |

| Half speed read                          | Yes       |                                                     |

| Full speed read                          | Yes       |                                                     |

Table 11: Startup Behavior

| Feature          | State     | Comment                                                                 |

|------------------|-----------|-------------------------------------------------------------------------|

| Power status     | LOW POWER | The chip is in low power mode after startup                             |

| Trigger function | ENABLED   | Trigger function is enabled after startup. Trigger function can be dis- |

|                  |           | abled via PM_TRIG register.                                             |

Data Sheet 14 Revision 3.0 - 2015-07-24

**Table 12: MIPI RFFE Operating Timing**

| Parameter             | Symbol    | Values |      |       | Unit    | Note / Test Condition  |

|-----------------------|-----------|--------|------|-------|---------|------------------------|

|                       |           | Min.   | Тур. | Max.  |         |                        |

| CCLK Eroquopov        | FSCLK     | 0.032  | _    | 26    | MHz     | Full speed             |

| SCLK Frequency        | FSCLK     | 0.032  | _    | 13    | MHz     | Half speed             |

| SCLK Period           | TSCLK     | 0.038  | -    | 32    | $\mu$ s | Full speed             |

| SOLIN I GIIOU         | TOOLK     | 0.077  | -    | 32    | $\mu$ S | Half speed             |

| SCLK Low Period       | TSCLKIL   | 11.25  | _    | _     | ns      | Full speed, see Fig. 2 |

| OLIN LOW I GIIOG      | TOOLNIL   | 24     | _    | _     | ns      | Half speed, see Fig. 2 |

| SCLK High Period      | TSCLKIH   | 11.25  | _    | _     | ns      | Full speed, see Fig. 2 |

| OCEN Flight Fellod    | TOOLKIIT  | 24     | _    | _     | ns      | Half speed, see Fig. 2 |

| SDATA Setup Time      | TS        | 1      | _    | _     | ns      | Full speed, see Fig. 3 |

|                       | 10        | 2      | _    | _     | ns      | Half speed, see Fig. 3 |

| SDATA Hold Time       | TH        | 5      | _    | _     | ns      | Full speed, see Fig. 3 |

| DDATA FIOID TIME      | 111       | 5      | _    | _     | ns      | Half speed, see Fig. 3 |

| SDATA Release Time    | TSDATAZ   | _      | _    | 10    | ns      | Full speed, see Fig. 4 |

| DAIA Helease Time     | TODAIAL   | _      | _    | 18    | ns      | Half speed, see Fig. 4 |

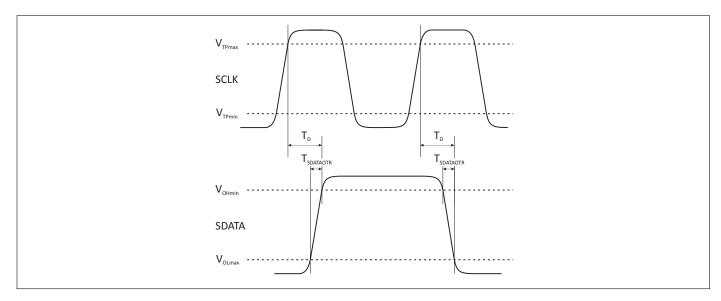

| Fime for Data Output  | TD        | _      | _    | 10.25 | ns      | Full speed, see Fig. 5 |

| ine ioi bata Output   | 10        | _      | _    | 22    | ns      | Half speed, see Fig. 5 |

| SDATA Rise/Fall Time  | TSDATAOTR | 2.1    | _    | 6.5   | ns      | Full speed, see Fig. 5 |

| DAIA HISE/I dii Hille | IODAIAOIT | 2.1    | _    | 10    | ns      | Half speed, see Fig. 5 |

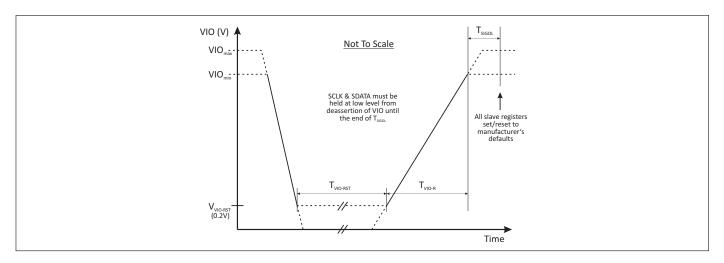

| IO Rise Time          | TVIO-R    | 10     | _    | 450   | $\mu$ S | See Fig. 6             |

| /IO Reset Time        | TVIO-RST  | 10     | -    | _     | $\mu$ s | See Fig. 6             |

| Reset Delay Time      | TSIGOL    | 0.12   | _    | _     | $\mu$ S | See Fig. 6             |

Figure 2: Received clock signal constraints

Figure 3: Bus active data receiver timing requirements

Figure 4: Bus park cycle timing

Data Sheet 16 Revision 3.0 - 2015-07-24

Figure 5: Bus active data transmission timing specification

Figure 6: Requirements for VIO-initiated reset

**Table 13: Register Mapping**

| Register | Register Name   | Data | Function              | Description                            | Default  | Broadcast_ID | Trigger | R/W |

|----------|-----------------|------|-----------------------|----------------------------------------|----------|--------------|---------|-----|

| Address  |                 | Bits |                       |                                        |          | Support      | Support |     |

| 0x0000   | REGISTER_0      | 7:0  | MODE_CTRL             | Module control                         | 00000000 | No           | Yes     | R/W |

| 0x001D   | PRODUCT_ID      | 7:0  | PRODUCT_ID            | This is a read-only register. However, | 11010001 | No           | No      | R   |

|          |                 |      |                       | during the programming of the USID     |          |              |         |     |

|          |                 |      |                       | a write command sequence is per-       |          |              |         |     |

|          |                 |      |                       | formed on this register, even though   |          |              |         |     |

|          |                 |      |                       | the write does not change its value.   |          |              |         |     |

| 0x001E   | MANUFACTURER_ID | 7:0  | MANUFACTURER_ID [7:0] | This is a read-only register. However, | 00011010 | No           | No      | R   |

|          |                 |      |                       | during the programming of the USID,    |          |              |         |     |

|          |                 |      |                       | a write command sequence is per-       |          |              |         |     |

|          |                 |      |                       | formed on this register, even though   |          |              |         |     |

|          |                 |      |                       | the write does not change its value.   |          |              |         |     |

Continued on next page

Table 13: Register Mapping - Continued from previous page

| Register<br>Address | Register Name | Data<br>Bits | Function                     | Description                                                                                                                                                                                         | Default | Broadcast_ID<br>Support | Trigger<br>Support | R/W |

|---------------------|---------------|--------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------------|--------------------|-----|

| 0x001C              | PM_TRIG       | 7:6          | PWR_MODE                     | 00: Normal operation 01: Default settings (STARTUP) 10: Low power (LOW POWER) 11: Reserved                                                                                                          | 10      | Yes                     | No                 | R/W |

|                     |               | 5            | TRIGGER_MASK_2               | If this bit is set, trigger 2 is disabled. When all triggers disabled, if writing to a register that is associated to trigger 2, the data goes directly to the desti- nation register.              | 0       | No                      | No                 |     |

|                     |               | 4            | TRIGGER_MASK_1               | If this bit is set, trigger 1 is disabled. When all triggers disabled, if writing to a register that is associated to trigger 1, the data goes directly to the desti- nation register.              | 0       | No                      | No                 |     |

|                     |               | 3            | TRIGGER_MASK_0               | If this bit is set, trigger 0 is disabled. When all triggers disabled, if writing to a register that is associated to trigger 0, the data goes directly to the desti- nation register.              | 0       | No                      | No                 |     |

|                     |               | 2            | TRIGGER_2                    | A write of a one to this bit loads trigger 2's registers.                                                                                                                                           | 0       | Yes                     | No                 |     |

|                     |               | 1            | TRIGGER_1                    | A write of a one to this bit loads trigger 1's registers.                                                                                                                                           | 0       | Yes                     | No                 | R/W |

|                     |               | 0            | TRIGGER_0                    | A write of a one to this bit loads trigger 0's registers.                                                                                                                                           | 0       | Yes                     | No                 |     |

| 0x001F              | MAN_USID      | 7:6          | SPARE                        | These are read-only bits that are reserved and yield a value of 0b00 at readback.                                                                                                                   | 00      | No                      | No                 | R/W |

|                     |               | 5:4          | MANUFACTURER_ID [9:8]        | These bits are read-only. However, during the programming of the USID, a write command sequence is performed on this register even though the write does not change its value.                      | 01      |                         |                    |     |

|                     |               | 3:0          | USID                         | Programmable USID. Performing a write to this register using the described programming sequences will program the USID in devices supporting this feature. These bits store the USID of the device. | 0001    |                         |                    |     |

| 0x001A              | RFFE_STATUS   | 7            | SOFTWARE RESET               | Normal operation     Software reset                                                                                                                                                                 | 0       | No                      | No                 | R/W |

|                     |               | 6            | COMMAND_FRAME_<br>PARITY_ERR | Command sequence received with parity error - discard command.                                                                                                                                      | 0       | No                      | No                 | R   |

|                     |               | 5            | COMMAND_LENGTH_ERR           | Command length error                                                                                                                                                                                | 0       |                         |                    |     |

|                     |               | 4            | ADDRESS_FRAME_<br>PARITY_ERR | Address frame parity error = 1                                                                                                                                                                      | 0       |                         |                    |     |

|                     |               | 3            | DATA_FRAME_<br>PARITY_ERR    | Data frame with parity error                                                                                                                                                                        | 0       |                         |                    |     |

|                     |               | 2            | READ_UNUSED_REG              | Read command to an invalid address                                                                                                                                                                  | 0       | ]                       |                    |     |

|                     |               | 1            | WRITE_UNUSED_REG             | Write command to an invalid address                                                                                                                                                                 | 0       | ]                       |                    |     |

|                     |               | 0            | BID_GID_ERR                  | Read command with a BROAD-<br>CAST_ID or GROUP_SID                                                                                                                                                  | 0       |                         |                    |     |

| 0x001B              | GROUP_SID     | 7:4          | RESERVED                     |                                                                                                                                                                                                     | 0       | No                      | No                 | R/W |

|                     |               | 3:0          | GROUP_SID                    | Group slave ID                                                                                                                                                                                      | 0       |                         |                    |     |

Table 14: Modes of Operation (Truth Table, Register\_0)

|       |            | REGISTER_0 Bits |    |    |    |    |    |    |    |

|-------|------------|-----------------|----|----|----|----|----|----|----|

| State | Mode       | D7              | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 1     | Isolation  | х               | х  | х  | 0  | 0  | 0  | 0  | 0  |

| 2     | RX1-AO     | х               | х  | х  | 0  | 0  | 0  | 0  | 1  |

| 3     | RX2-AO     | х               | х  | х  | 0  | 0  | 0  | 1  | 0  |

| 4     | RX3-AO     | х               | х  | х  | 0  | 1  | 0  | 0  | 0  |

| 5     | RX4-AO     | х               | х  | х  | 0  | 0  | 1  | 0  | 0  |

| 6     | RX5-AO     | х               | х  | х  | 1  | 0  | 0  | 0  | 0  |

| 7     | RX1&RX2-AO | х               | х  | х  | 0  | 0  | 0  | 1  | 1  |

| 8     | RX2&RX3-AO | х               | х  | х  | 0  | 1  | 0  | 1  | 0  |

| 9     | RX3&RX4-AO | х               | х  | х  | 0  | 1  | 1  | 0  | 0  |

| 10    | RX4&RX5-AO | х               | х  | х  | 1  | 0  | 1  | 0  | 0  |

| 11    | RX1&RX3-AO | х               | х  | х  | 0  | 1  | 0  | 0  | 1  |

| 12    | RX2&RX4-AO | х               | х  | х  | 0  | 0  | 1  | 1  | 0  |

| 13    | RX3&RX5-AO | х               | х  | х  | 1  | 1  | 0  | 0  | 0  |

| 14    | RX1&RX4-AO | х               | х  | Х  | 0  | 0  | 1  | 0  | 1  |

| 15    | RX2&RX5-AO | х               | х  | Х  | 1  | 0  | 0  | 1  | 0  |

| 16    | RX1&RX5-AO | x               | Х  | х  | 1  | 0  | 0  | 0  | 1  |

### 7 Application Information

### **Pin Configuration and Function**

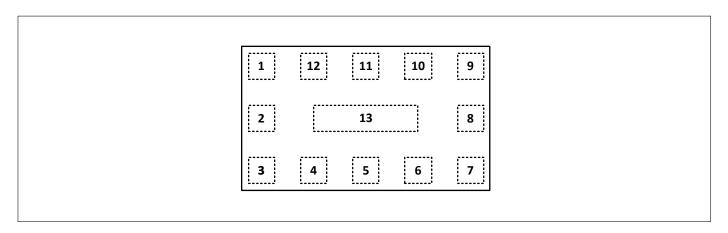

Figure 7: BGM15LA12 Pin Configuration (top view)

**Table 15: Pin Definition and Function**

| Name  | Function                                          |

|-------|---------------------------------------------------|

| SCLK  | MIPI RFFE Clock                                   |

| VIO   | MIPI RFFE Power Supply                            |

| RX5   | RF-Port RX No. 5                                  |

| RX4   | RF-Port RX No. 4                                  |

| RX3   | RF-Port RX No. 3                                  |

| RX2   | RF-Port RX No. 2                                  |

| RX1   | RF-Port RX No. 1                                  |

| GND   | Ground                                            |

| GND   | Ground                                            |

| AO    | RF-Output Port                                    |

| VDD   | Power Supply                                      |

| SDATA | MIPI RFFE Data IO                                 |

| GND   | Ground                                            |

|       | SCLK VIO RX5 RX4 RX3 RX2 RX1 GND GND AO VDD SDATA |

#### **Application Board Configuration**

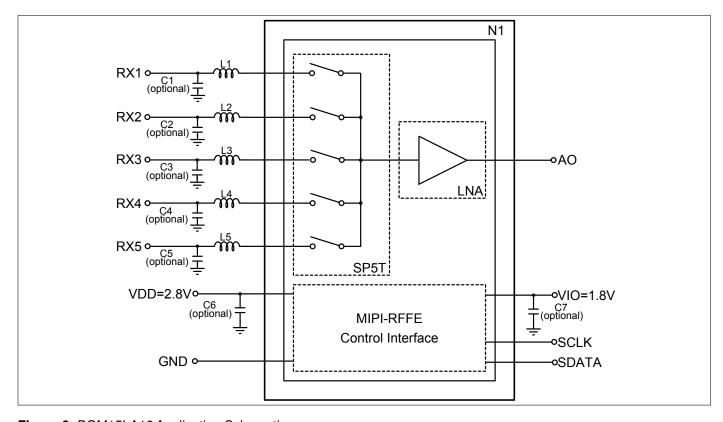

Figure 8: BGM15LA12 Application Schematic

**Table 16: Bill of Materials Table**

| Name -        | Value     | Daalsana   | BA f t       | Fation                               |

|---------------|-----------|------------|--------------|--------------------------------------|

| Name          | Value     | Package    | Manufacturer | Function                             |

| C1 (optional) | 2 pF      | 0402       | Various      | Input matching Band 28 <sup>2)</sup> |

| C2 (optional) | 1.1 pF    | 0402       | Various      | Input matching Band 8 <sup>2)</sup>  |

| C3 (optional) | 1.8 pF    | 0402       | Various      | Input matching Band 20 <sup>2)</sup> |

| C4 (optional) | 2.2 pF    | 0402       | Various      | Input matching Band 12 <sup>2)</sup> |

| C5 (optional) | 1.5 pF    | 0402       | Various      | Input matching Band 26 <sup>2)</sup> |

| C6 (optional) | 1 nF      | 0402       | Various      | RF Bypass <sup>1)</sup>              |

| C7 (optional) | 1 nF      | 0402       | Various      | RF Bypass <sup>1)</sup>              |

| L1            | 16 nH     | 0402       | Various      | Input matching Band 28 <sup>2)</sup> |

| L2            | 11 nH     | 0402       | Various      | Input matching Band 82)              |

| L3            | 15 nH     | 0402       | Various      | Input matching Band 20 <sup>2)</sup> |

| L4            | 18 nH     | 0402       | Various      | Input matching Band 12 <sup>2)</sup> |

| L5            | 13 nH     | 0402       | Various      | Input matching Band 26 <sup>2)</sup> |

| N1            | BGM15LA12 | ATSLP-12-1 | Infineon     | LNA Multiplexer Module               |

<sup>&</sup>lt;sup>1)</sup>RF bypass recommended to mitigate power supply noise.

<sup>2)</sup> The matching elements must be optimized with reference to the frequency band of interest. Each band can be arbiratily assigned to an RF port. The configuration shown in the table is only an example of the port assignment.

### 8 Package Information

Figure 9: ATSLP-12-1 Package Outline (top, side and bottom views)

Figure 10: Marking Specification (top view)

Figure 11: Footprint Recommendation

Figure 12: ATSLP-12-1 Carrier Tape

www.infineon.com

Published by Infineon Technologies AG