# Half-Bridge IPM for Low Voltage Applications

#### Description

The IRSM005-301MH is a general purpose half-bridge with integrated gate driver in an attractive 7x8mm PQFN package. It is a general purpose building block suitable for a variety of low voltage applications where power density is of critical importance. Typical examples would be advanced motor drives, dc-to-ac and dc-to-dc converters.

## Features

- Package with low thermal resistance and minimal parasitics

- Low on-resistance HEXFETs: 16 m $\Omega$  typ.

- Undervoltage lockout on Vcc and Vbs

- Independent gate drive in phase with logic input

- Gate drive supply range from 10V to 20V

- Propagation delay matched to defined spec

- 3.3V, 5V and 15V logic input compatible

- RoHS compliant

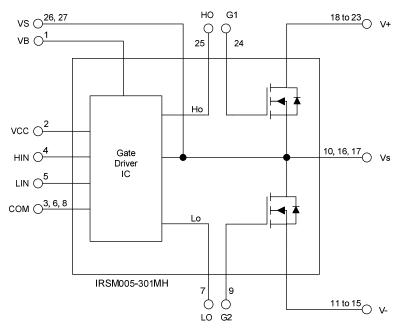

#### **Internal Electrical Schematic**

#### **Ordering Information**

| Orderable Part Number | Package Type | Form          | Quantity |

|-----------------------|--------------|---------------|----------|

| IRSM005-301MH         | PQFN 7x8mm   | Tray          | 1300     |

| IRSM005-301MHTR       | PQFN 7x8mm   | Tape and Reel | 2000     |

1 www.irf.com © 2014 International Rectifier

*i*MOTION™

## **Absolute Maximum Ratings**

Absolute maximum ratings indicate sustained limits beyond which damage to the module may occur. These are not tested at manufacturing. All voltage parameters are absolute voltages referenced to  $V_{SS}$  unless otherwise stated in the table. The thermal resistance rating is measured under board mounted and still air conditions.

| Symbol                       | Description                                                 | Min     | Мах      | Unit |

|------------------------------|-------------------------------------------------------------|---------|----------|------|

| V <sub>DS</sub>              | MOSFET Drain-to-Source Voltage                              |         | 100      | V    |

| Io                           | Maximum DC current per MOSFET @ $T_C$ =25°C (Note1)         |         | 30       | А    |

| P <sub>d</sub>               | Maximum Power dissipation per MOSFET @ $T_C = 100^{\circ}C$ |         | 13.5     | W    |

| T <sub>J</sub> (MOSFET & IC) | Maximum Operating Junction Temperature                      |         | 150      | °C   |

| T <sub>s</sub>               | Storage Temperature Range                                   | -40     | 150      | °C   |

| V <sub>B</sub>               | High side floating supply voltage                           | -0.3    | VS + 20  | V    |

| Vs                           | High side floating supply offset voltage                    | VB - 20 | VB +0.3  | V    |

| V <sub>CC</sub>              | Low Side fixed supply voltage                               | -0.3    | 20       | V    |

| V <sub>IN</sub>              | Logic input voltage LIN, HIN                                | -0.3    | VCC+0.3V | V    |

Note1: Calculated based on maximum junction temperature. Bond wires current limit is 20A

## **Inverter Static Electrical Characteristics**

$V_{BIAS}$  (V<sub>CC</sub>, V<sub>BS</sub>)=15V, TJ=25°C, unless otherwise specified.

| Symbol               | Description                       | Min  | Тур     | Мах        | Units             | Conditions                                                                           |

|----------------------|-----------------------------------|------|---------|------------|-------------------|--------------------------------------------------------------------------------------|

| V <sub>(BR)DSS</sub> | Drain-to-Source Breakdown Voltage | 100  |         |            | V                 | H <sub>IN</sub> =L <sub>IN</sub> =0V, I <sub>D</sub> =250µA                          |

| $V_{GS(TH)}$         | Gate Threshold Voltage            | 2.0  | 3.0     | 4.0        | V                 | I <sub>D</sub> =100μΑ                                                                |

| R <sub>DS(ON)</sub>  | Drain-to-Source Voltage           |      | 16      | 21         | mΩ                | I <sub>D</sub> =10A, T <sub>J</sub> =25°C                                            |

| TODS(ON)             | Drain-to-Source voltage           |      | 35      |            | 11152             | I <sub>D</sub> =10A, T <sub>J</sub> =150°C                                           |

|                      |                                   |      | 20      |            |                   | H <sub>IN</sub> =L <sub>IN</sub> =0V, V <sup>+</sup> =100V                           |

| IDSS                 | Zero Gate Voltage Drain Current   |      | 250     |            | μA                | H <sub>IN</sub> =L <sub>IN</sub> =0V, V <sup>+</sup> =100V,<br>T <sub>J</sub> =125°C |

| V <sub>SD</sub>      | MOSFET Diode Forward Voltage      |      | 0.7     | 0.82       | V                 | I <sub>F</sub> =10A                                                                  |

| VSD                  | Drop                              |      | 0.6     |            |                   | I <sub>F</sub> =10A, T <sub>J</sub> =125°C                                           |

| I <sub>GSS</sub>     | Gate to Source leakage            |      |         | +/-100     | nA                | V <sub>GS</sub> =+/-20V                                                              |

| RBSOA                | Reverse Bias Safe Operating Area  | FULL | SQUARE, | limited by | T <sub>Jmax</sub> | V <sup>+</sup> = 100V,<br>V <sub>CC</sub> =+15V to 0V                                |

| Q <sub>G</sub>       | Total gate charge                 |      | 36      | 54         |                   |                                                                                      |

| $Q_{GS}$             | Gate to source charge             |      | 7       |            | nC                | I <sub>D</sub> =26A<br>V <sub>DS</sub> = 20V<br>V <sub>GS</sub> =10V                 |

| $Q_{GD}$             | Gate to drain charge              |      | 11      |            |                   |                                                                                      |

| EAS                  | Single Pulse Avalanche Energy     | 6.1  | -       |            | mJ                |                                                                                      |

## **Recommended Operating Conditions Driver Function**

For proper operation the device should be used within the recommended conditions. All voltages are absolute referenced to COM. The VS offset is tested with all supplies biased at 15V differential. For more details, see IRS2005 data sheet.

| Symbol          | Definition                               | Min                | Тур                | Max                | Units |

|-----------------|------------------------------------------|--------------------|--------------------|--------------------|-------|

| VB              | High side floating supply voltage        | V <sub>S</sub> +10 | V <sub>S</sub> +15 | V <sub>S</sub> +20 | V     |

| Vs              | High side floating supply offset voltage |                    |                    | 100                | V     |

| V <sub>CC</sub> | Low side and logic fixed supply voltage  | 10                 | 15                 | 20                 | V     |

| V <sub>IN</sub> | Logic input voltage LIN, HIN             | СОМ                |                    | V <sub>CC</sub>    | V     |

| HIN             | High side PWM pulse width                | 1                  |                    |                    | μs    |

| Deadtime        | Suggested dead time between HIN and LIN  | 0.3                | 0.5                |                    | μs    |

#### **Static Electrical Characteristics Driver Function**

$V_{BIAS}$  (V\_{CC}, V\_{BS})=15V, T\_J=25^{\circ}C, unless otherwise specified. The  $V_{IN},$  and  $I_{IN}$  parameters are referenced to COM

| Symbol              | Definition                                                      | Min | Тур | Мах | Units                                 |

|---------------------|-----------------------------------------------------------------|-----|-----|-----|---------------------------------------|

| $V_{\text{IN,th+}}$ | Positive going input threshold for LIN, HIN                     | 2.5 |     |     | V                                     |

| $V_{\text{IN,th-}}$ | Negative going input threshold for LIN, HIN                     |     |     | 0.8 | V                                     |

| V <sub>BSUV+</sub>  | V <sub>BS</sub> supply undervoltage, Positive going threshold   | 8.0 | 8.9 | 9.8 | V                                     |

| V <sub>BSUV-</sub>  | V <sub>BS</sub> supply undervoltage, Negative going threshold   | 7.4 | 8.2 | 9.0 | V                                     |

| VBSUVH              | V <sub>BS</sub> supply undervoltage lock-out hysteresis         |     | 0.8 |     | V                                     |

| V <sub>CCUV+</sub>  | V <sub>CC</sub> / supply undervoltage, Positive going threshold | 8.0 | 8.9 | 9.8 | V                                     |

| V <sub>CCUV-</sub>  | V <sub>CC</sub> supply undervoltage, Negative going threshold   | 7.4 | 8.2 | 9.0 | V                                     |

| V <sub>CCUVH</sub>  | V <sub>CC</sub> supply undervoltage lock-out hysteresis         |     | 0.8 |     | V                                     |

| I <sub>QBS</sub>    | Quiescent V <sub>BS</sub> supply current                        |     | 30  | 75  | μA                                    |

| I <sub>QCC</sub>    | Quiescent V <sub>CC</sub> supply current                        |     | 150 | 520 | μA                                    |

| I <sub>LK</sub>     | Offset Supply Leakage Current                                   |     |     | 50  | μA                                    |

| I <sub>O+</sub>     | IC high output short circuit current                            | 200 | 290 |     | VO=0V<br>VIN=Logic<br>"1"<br>PW<10us  |

| I <sub>0-</sub>     | IC low output short circuit current                             |     | 600 |     | VO=15V<br>VIN=Logic<br>"0"<br>PW<10us |

| I <sub>IN+</sub>    | Input bias current V <sub>IN</sub> =5V for LIN, HIN             |     | 4   | 10  | μA                                    |

| I <sub>IN-</sub>    | Input bias current V <sub>IN</sub> =0V for LIN, HIN             |     | 0.5 | 1   | μA                                    |

## **Dynamic Electrical Characteristics Driver Function**

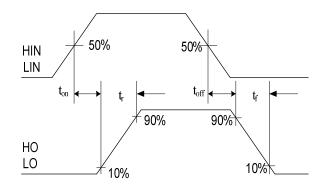

$V_{BIAS}$  ( $V_{CC}$ ,  $V_{BS}$ )=15V, TJ=25°C,  $C_L$ =1000pF unless otherwise specified. Driver only timing unless otherwise specified.

| Symbol           | Description                                                  | Min | Тур | Мах | Units | Conditions |

|------------------|--------------------------------------------------------------|-----|-----|-----|-------|------------|

| T <sub>ON</sub>  | Input to Output propagation turn-on delay time (see fig.3)   |     | 160 | 220 | ns    |            |

| T <sub>OFF</sub> | Input to Output propagation turn-off delay time (see fig. 3) |     | 150 | 220 | ns    |            |

| T <sub>R</sub>   | Input to Output turn-on rise time (see fig.3)                |     | 70  | 170 | ns    |            |

| T <sub>F</sub>   | Input to Output turn-off fall time (see fig. 3)              |     | 35  | 95  | ns    |            |

| MT               | Delay matching, HS and LS turn-<br>on/off                    |     |     | 50  | ns    |            |

#### **Thermal and Mechanical Characteristics**

| Symbol               | Description                                               | Min | Тур | Мах | Units | Conditions                                                  |

|----------------------|-----------------------------------------------------------|-----|-----|-----|-------|-------------------------------------------------------------|

| R <sub>th(J-B)</sub> | Thermal resistance, junction to mounting pad, each MOSFET |     | 3.8 |     | °C/W  | Standard reflow-solder process                              |

| R <sub>th(J-A)</sub> | Thermal resistance, junction to ambient, each MOSFET      |     | 40  |     | °C/W  | Mounted on 50mm <sup>2</sup> of four-layer FR4 with 28 vias |

## Input-Output Logic Level Table

| HIN | LIN | U,V,W         |

|-----|-----|---------------|

| HI  | HI  | Shoot-through |

| LO  | LO  | **            |

| HI  | LO  | V+            |

| LO  | HI  | 0             |

\* V+ if motor current is flowing into VS, 0 if current is flowing out of VS into the motor winding

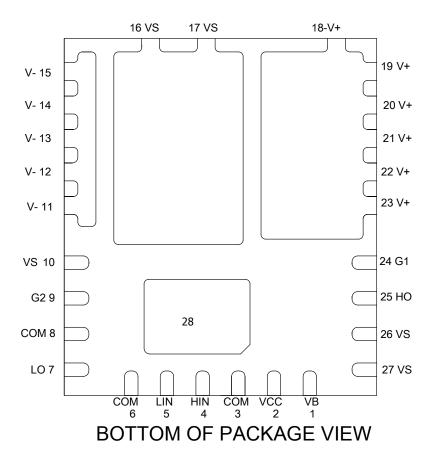

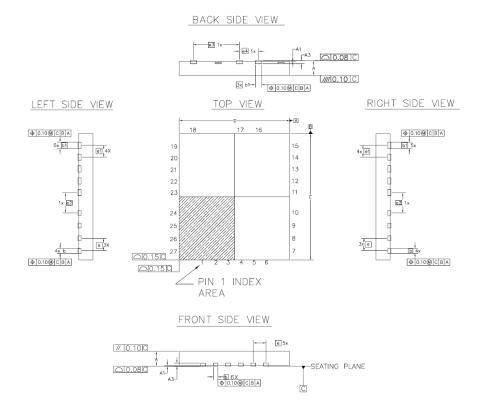

### Module Pin-Out Description

| Pin        | Name            | Description                                              |  |

|------------|-----------------|----------------------------------------------------------|--|

| 3, 6, 8    | СОМ             | Low Side Gate Driver Return                              |  |

| 2          | V <sub>CC</sub> | 15V Gate Drive Supply                                    |  |

| 4          | HIN             | Logic Input for High Side (Active High)                  |  |

| 5          | LIN             | Logic Input for Low Side (Active High)                   |  |

| 7          | LO              | Low Side Gate Drive Output                               |  |

| 9          | G2              | Low Side FET Gate                                        |  |

| 10, 16, 17 | Vs              | Phase Output                                             |  |

| 11 to 15   | V-              | Low Side Source Connection                               |  |

| 18 to 23   | V+              | DC Bus                                                   |  |

| 24         | G1              | High Side FET Gate                                       |  |

| 25         | HO              | High Side Gate Drive Output                              |  |

| 26, 27     | Vs              | Phase Output (-ve of Bootstrap Cap Connection)           |  |

| 1          | VB              | High Side Floating Supply (+ve Bootstrap Cap Connection) |  |

Exposed pad (Pin 28) has to be connected to COM for better electrical performance

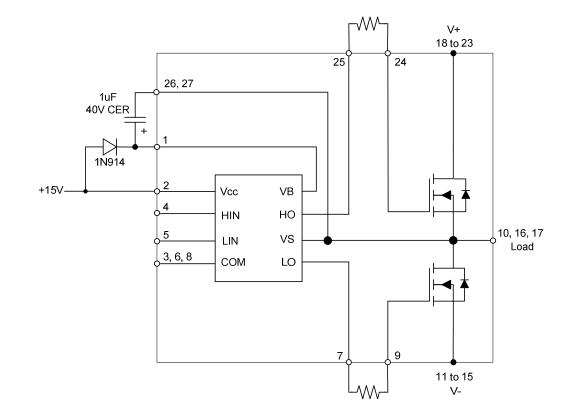

Figure 1: Typical Application Connection

- Bus capacitors should be mounted as close to the module bus terminals as possible to reduce ringing and EMI problems. Additional high frequency ceramic capacitor mounted close to the module pins will further improve performance.

- 2. Value of the boot-strap capacitors depends upon the switching frequency. Their selection should be made based on IR Design tip DT04-4 or application note AN-1044.

Figure 2. IC switching waveforms definitions.

6 <u>www.irf.com</u> © 2014 International Rectifier

*i*MOTION<sup>™</sup>

## Qualification

| Qualifica        | tion Level        | Industrial <sup>††</sup><br>(per JEDEC JESD 47E)               |  |

|------------------|-------------------|----------------------------------------------------------------|--|

| Moisture         | Sensitivity Level | MSL3 <sup>†††</sup><br>(per IPC/JEDEC J-STD-020C)              |  |

| ESD              | Machine Model     | Class A (±200V)<br>(per JEDEC standard JESD22-A115A)           |  |

| Human Body Model |                   | Class 2 (±2000V)<br>(per EIA/JEDEC standard EIA/JES-001A-2011) |  |

| RoHS Compliant   |                   | Yes                                                            |  |

† Qualification standards can be found at International Rectifier's web site <u>http://www.irf.com/</u>.

++ Higher qualification ratings may be available should the user have such requirements. Please contact your International Rectifier sales representative for further information.

+++ Higher MSL ratings may be available for the specific package types listed here. Please contact your International Rectifier sales representative for further information.

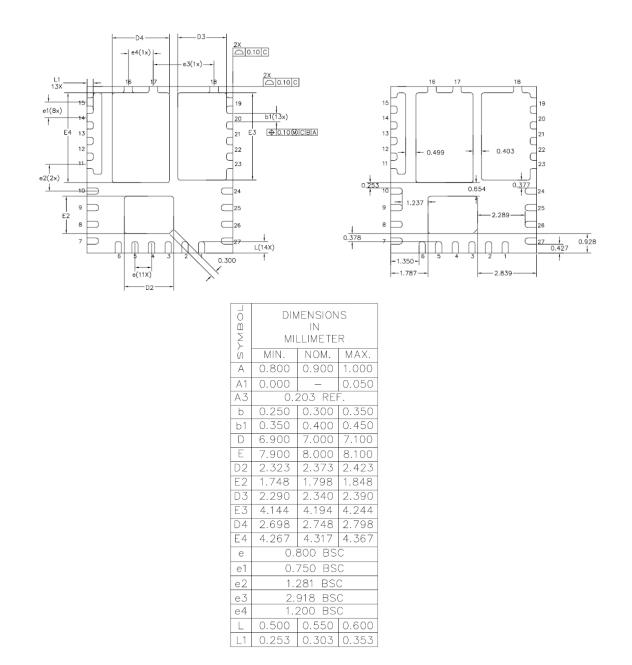

## Package Outline (Top & Side view)

| SYMBOL | DIMENSIONS<br>IN |         |       |  |  |  |

|--------|------------------|---------|-------|--|--|--|

| Ś      | MIL              | LIMETE  | R     |  |  |  |

| ́о     | MIN.             | NOM.    | MAX.  |  |  |  |

| А      | 0.800            | 0.900   | 1.000 |  |  |  |

| Α1     | 0.000            | —       | 0.050 |  |  |  |

| A3     | 0.2              | 203 REF |       |  |  |  |

| b      | 0.250            | 0.300   | 0.350 |  |  |  |

| b1     | 0.350            | 0.400   | 0.450 |  |  |  |

| D      | 6.900            | 7.000   | 7.100 |  |  |  |

| Ε      | 7.900            | 8.000   | 8.100 |  |  |  |

| D2     | 2.323            | 2.373   | 2.423 |  |  |  |

| E2     | 1.748            | 1.798   | 1.848 |  |  |  |

| D3     | 2.290            | 2.340   | 2.390 |  |  |  |

| E3     | 4.144            | 4.194   | 4.244 |  |  |  |

| D4     | 2.698            | 2.748   | 2.798 |  |  |  |

| E4     | 4.267            | 4.317   | 4.367 |  |  |  |

| е      | 0.8              | 800 BS  | С     |  |  |  |

| e1     | 0.1              | 750 BS  | С     |  |  |  |

| e2     | 1.1              | 281 BS( | 2     |  |  |  |

| eЗ     | 2.918 BSC        |         |       |  |  |  |

| e4     | 1.2              | 200 BS( | 0     |  |  |  |

| L      | 0.500            | 0.550   | 0.600 |  |  |  |

| L1     | 0.253            | 0.303   | 0.353 |  |  |  |

|        |                  |         |       |  |  |  |

## Package Outline (Bottom View, 1 of 2)

PACKAGE BOTTOM VIEW

- 1. For mounting instruction see AN-1168.

- 2. For recommended PCB via design see AN-1091.

- 3. For recommended design, solder profile, integration and rework guidelines see AN-1028.

- 4. For board inspection guidelines see AN-1133.

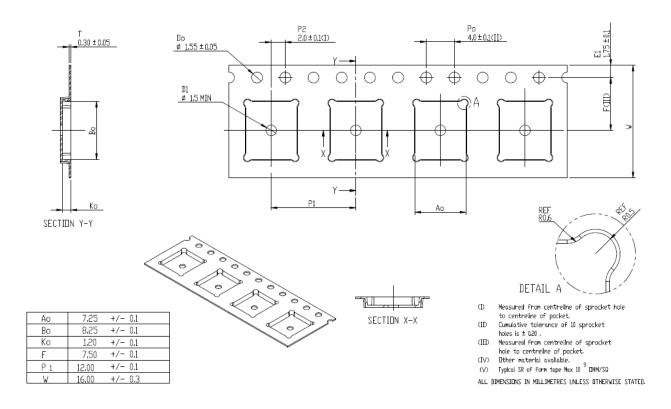

## **Tape and Reel Details**

Data and Specifications are subject to change without notice IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245, USA Tel: (310) 252-7105 TAC Fax: (310) 252-7903 Visit us at www.irf.com for sales contact information

11 www.irf.com © 2014 International Rectifier

*i*MOTION<sup>™</sup>