# International TOR Rectifier

# HIGH RELIABILITY HYBRID DC-DC CONVERTERS

#### **Description**

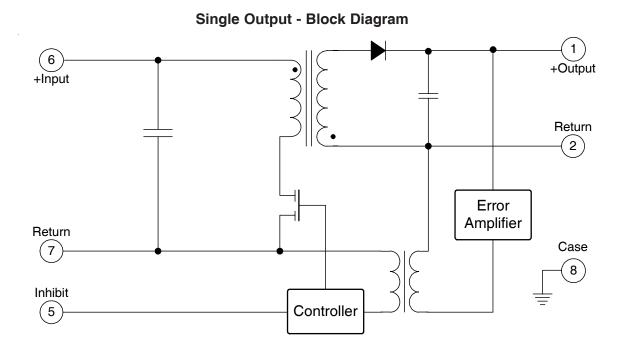

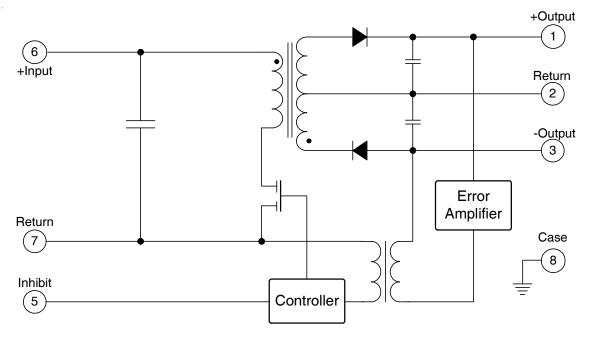

The ASAP Series of DC-DC converters are high reliability thick film hybrid converters that use flyback topology operating at a nominal frequency of 550KHz. High input to output isolation is achieved through the use of transformers in the flyback power and feedback circuits.

The advanced feedback design provides fast loop response for superior line and load transient characteristics and offers greater reliability than devices incorporating optical feedback circuits.

This device is designed to meet MIL-STD-704D input requirements offering full performance over a wide 15 to 50 volt input range and output power of up to 6.0 watts.

Connecting the inhibit pin (pin 5) to the input common (pin 7) will cause the converter to shut down. It is recommended that the inhibit pin be driven by an open collector device capable of sinking at least  $400\mu A$ . The open circuit voltage of the inhibit pin is  $11.5 \pm 0.5$  volts.

These converters are manufactured in a facility fully qualified to MIL-PRF-38534. All processes used to manufacture these converters have been qualified thereby enabling International Rectifier to deliver fully compliant devices. Four standard temperature grades are offered with the screening options. Refer to Screening Level section. The CH grade converters are fully compliant to MIL-PRF-38534 for class H. The HB grade converters are processed with the same screening as the CH grade, but do not have class H element evaluation as required by MIL-PRF-38534. These two grades are fully tested and operate over the full military temperature range without derating of output power. A commercial grade is also available. Variations in electrical, mechanical and screening requirements can be accommodated. Extensive computer simulation using complex modeling allows design modifications to be examined. Contact IR San Jose with specific requirements.

www.irf.com

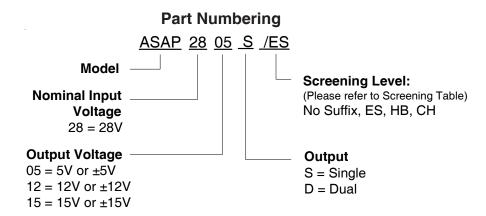

# **ASAP SERIES**

#### 28V Input, Single and Dual Output

#### **Features**

- Up To 6.0 Watt Output Power

- Availabe in Single and Dual Output Configurations Single Outputs: 5V, 12V and 15V

Dual Outputs: ± 5V, ± 12V and ± 15V

- High Reliability

- Wide Input Voltage Range, 15 To 50 Volts

- Indefinite Short Circuit and Overload Protection

- Popular Industry Standard Pin-Out

- Military Screening Available

- Parallel Seam Welded Package

- No External Capacitors Required

- Input Voltage Surge Protected to MIL-STD-704A 80V, 1 second

- Under Voltage Lockout

1

**Absolute Maximum Ratings**

Input Voltage -0.5V to 50V Continous, 80V for 1 second

Power Output Internally limited

Soldering Temperature 300°C for 10 seconds

Temperature Range Operating  $-55^{\circ}$ C to  $+125^{\circ}$ C Case Storage  $-65^{\circ}$ C to  $+150^{\circ}$ C

|                                                      | Conditions $-55^{\circ} \le T_{C} \le +125^{\circ}C$                          | Group A   | ASAP2805S/xx |      | x ASAP2812S/xx |       | ASAP2815S/xx |       |       |

|------------------------------------------------------|-------------------------------------------------------------------------------|-----------|--------------|------|----------------|-------|--------------|-------|-------|

| TEST                                                 | $V_{IN} = 28V \text{ dc } \pm 5\% \text{ C}_L = 0$ unless otherwise specified | Subgroups | Min          | Max  | Min            | Max   | Min          | Max   | Unit  |

| Output voltage                                       | I <sub>OUT</sub> = 0                                                          | 1         | 4.95         | 5.05 | 11.88          | 12.12 | 14.85        | 15.15 | V     |

|                                                      |                                                                               | 2, 3      | 4.90         | 5.10 | 11.76          | 12.24 | 14.70        | 15.30 |       |

| Output current 1                                     | $V_{IN} = 15, 28, and 50 V dc$                                                | 1, 2, 3   |              | 1200 |                | 500   |              | 400   | mA    |

| Output ripple voltage 2                              | $V_{IN} = 15, 28 \text{ and } 50 \text{ V dc}$                                | 1         |              | 60   |                | 60    |              | 60    | mV PP |

|                                                      |                                                                               | 2, 3      |              | 100  |                | 100   |              | 100   |       |

| Line regulation                                      | V <sub>IN</sub> = 15, 28, and 50 V dc                                         | 1         |              | ±25  |                | ±25   |              | ±25   | mV    |

|                                                      | I <sub>OUT</sub> = 0, 50%, 100% I <sub>MAX</sub>                              | 2, 3      |              | ±50  |                | ±50   |              | ±50   |       |

| Load regulation                                      | $V_{IN} = 15, 28, \text{ and } 50 \text{ V dc}$                               | 1         |              | ±25  |                | ±25   |              | ±25   | mV    |

|                                                      | I <sub>OUT</sub> = 0, 50%, 100% I <sub>MAX</sub>                              | 2, 3      |              | ±50  |                | ±50   |              | ±50   |       |

|                                                      | I <sub>OUT</sub> = 0 Pin 5 to Pin 7                                           | 1, 2, 3   |              | 18   |                | 18    |              | 18    | mA    |

| Input current                                        | I <sub>OUT</sub> = 0 Pin5 open                                                | , , ,     |              | 50   |                | 50    |              | 50    |       |

| Input ripple current 2                               | $I_{OUT} = I_{MAX}$                                                           | 1, 2, 3   |              | 100  |                | 100   |              | 100   | mA PP |

| Efficiency                                           | I <sub>OUT</sub> = I <sub>MAX</sub>                                           | 1         | - 66         |      | 71             |       | 71           |       | %     |

| ,<br>                                                |                                                                               | 2, 3      |              |      | 68             |       | 68           |       | /6    |

| Isolation - Input to<br>output or any pin to<br>case | V <sub>TEST</sub> 500 Vdc, Tc= +25°C                                          | 1         | 100          |      | 100            |       | 100          |       | MΩ    |

| Capacitive load 3, 4                                 | No effect on dc performance, Tc = +25°C                                       | 4         |              | 500  |                | 200   |              | 200   | μF    |

| Power dissipation, load                              | Overload <sup>5</sup>                                                         | 1, 2, 3   |              | 5.0  |                | 5.0   |              | 5.0   | w     |

| fault                                                | Short circuit                                                                 |           |              | 2.0  |                | 2.0   |              | 2.0   |       |

| Switching frequency 4                                | $I_{OUT} = I_{MAX}$                                                           | 4, 5, 6   | 500          | 600  | 500            | 600   | 500          | 600   | KHz   |

| Output response to step                              | ½ I <sub>MAX</sub> ⇔ I <sub>MAX</sub>                                         | 4         | -300         | +300 | -450           | +450  | -450         | +450  |       |

| transient load changes                               |                                                                               | 5, 6      | -450         | +450 |                |       | .00          | 1400  | mV pk |

|                                                      | 0 mA ⇔ I <sub>MAX</sub>                                                       | 4         | -500         | +500 | -750           | +750  | -750         | +750  |       |

|                                                      |                                                                               | 5, 6      | -750         | +750 |                |       |              |       |       |

| Recovery time, step                                  | $I_{OUT} = I_{MAX}$                                                           | 4, 5, 6   |              | 200  |                | 100   |              | 100   | μs    |

| transient load changes                               | 0 mA ⇔ ½ I <sub>MAX</sub>                                                     |           |              | 1.0  |                | 1.0   |              | 1.0   | ms    |

| Output response transient step line changes 4 8      | Input step 15 ⇔ 50 V dc I <sub>OUT</sub> = I <sub>MAX</sub>                   | 4, 5, 6   | -500         | 500  | -1000          | 1000  | -1000        | 1000  | mV pk |

| Recovery time transient step line changes 4, 7, 8    | Input step 15 ⇔ 50 V dc I <sub>OUT</sub> = I <sub>MAX</sub>                   | 4, 5, 6   |              | 800  |                | 800   |              | 800   | μs    |

| Turn on overshoot                                    | I <sub>OUT</sub> = 0 mA, I <sub>MAX</sub>                                     | 4, 5, 6   |              | 600  |                | 750   |              | 750   | mV pk |

| Turn on delay <sup>9</sup>                           | I <sub>OUT</sub> = 0 or I <sub>MAX</sub>                                      | 4, 5, 6   |              | 20   |                | 25    |              | 25    | ms    |

| Load fault recovery 4                                |                                                                               | 4, 5, 6   |              | 20   |                | 25    |              | 25    | ms    |

For Notes to Specifications, refer to page 3

#### Notes to Specifications for Tables on page 2

- 1. Parameter guaranteed and measured during line and load regulation tests.

- 2. Bandwidth guaranteed by design. Tested for 20 KHz to 2.0 MHz.

- 3. Capacitive load may be any value from 0 to the maximum limit without compromising dc performance. A capacitive load in excess of the maximum limit will not disturb loop stability but may interfere with the operation of the load fault detection circuitry, appearing as a short circuit during turn-on.

- 4. Parameter shall be tested as part of design characterization and after design or process changes.

- 5. An overload is that condition of load in excess of rated load but less than that necessary to trigger the short circuit protection and is the condition of maximum power dissipation.

- 6. Load step transition time between 2.0 and 10 microseconds.

- Recovery time is measured from the initiation of the transient to where V<sub>OUT</sub> has returned to within ±1.0 percent of V<sub>OUT</sub> at 50% load.

- 8. Input step transition time between 2.0 and 10 microseconds.

- 9. Turn-on delay time measurement is for either a step application of power at the input or the removal of a ground signal from the inhibit pin (pin 2) while power is applied to the input.

**Absolute Maximum Ratings**

Input Voltage -0.5V to 50V Continous, 80V for 1 second

Power Output Internally limited Soldering Temperature 300°C for 10 seconds

Temperature Range Operating -55°C to +125°C Case Storage -65°C to +150°C

|                                                              | Conditions<br>-55° ≤ T <sub>C</sub> ≤+125°C                                              | ASAP2805D/XX<br>Group A |       | ASAP2812D/XX |        | ASAP2815D/XX |        |        |                  |

|--------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------|-------|--------------|--------|--------------|--------|--------|------------------|

| TEST                                                         | $V_{IN} = 28V \text{ dc } \pm 5\% \text{ C}_L = 0$<br>unless otherwise specified         | Subgroups               | Min   | Max          | Min    | Max          | Min    | Max    | Unit             |

| Output voltage                                               | I <sub>OUT</sub> = 0                                                                     | 1                       | ±4.95 | ±5.05        | ±11.88 | ±12.12       | ±14.85 | ±15.15 | V                |

|                                                              | 301                                                                                      | 2, 3                    | ±4.90 | ±5.10        | ±11.76 | ±12.24       | ±14.70 | ±15.30 |                  |

| Output current 1, 2                                          | V <sub>IN</sub> = 15, 28, and 50 Vdc either output                                       | 1, 2, 3                 | 240   | 960          | 100    | 400          | 80     | 320    | mA               |

| Output ripple voltage 3, 4                                   | $V_{IN} = 15, 28 \text{ and } 50 \text{ Vdc}$                                            | 1, 2, 3                 |       | 100          |        | 200          |        | 200    | mV <sub>PP</sub> |

| Line regulation <sup>4</sup>                                 | V <sub>IN</sub> = 15, 28, and 50 Vdc<br>I <sub>OUT</sub> = 0, 50%, 100% I <sub>MAX</sub> | 1, 2, 3                 |       | ±50          |        | ±50          |        | ±50    | mV               |

| Load regulation <sup>4</sup>                                 | V <sub>IN</sub> = 15, 28, and 50 Vdc<br>I <sub>OUT</sub> = 0, 50%, 100% I <sub>MAX</sub> | 1, 2, 3                 |       | ±50          |        | ±50          |        | ±50    | mV               |

| Cross regulation <sup>5</sup>                                | 20% to 80% load change                                                                   | 1, 2, 3                 |       | 15           |        | 8.0          |        | 8.0    | %                |

| Input current                                                | I <sub>OUT</sub> = 0<br>Pin 5 connected to pin 7                                         | 1, 2, 3                 |       | 12           |        | 12           |        | 12     | mA               |

|                                                              | I <sub>OUT</sub> = 0 Pin5 open                                                           |                         |       | 60           |        | 60           |        | 60     |                  |

| Input ripple current 3, 4                                    | I <sub>OUT</sub> = I <sub>MAX</sub>                                                      | 1, 2, 3                 |       | 100          |        | 100          |        | 100    | mA PP            |

| Efficiency <sup>4</sup>                                      | $I_{OUT} = I_{MAX}$                                                                      | 1, 3                    | 70    |              | 71     |              | 71     |        | %                |

| •                                                            |                                                                                          | 2                       | 66    |              | 68     |              | 68     |        | ,-               |

| Isolation                                                    | Input to output or any pin to case (except pin 8) at 500 Vdc, Tc = +25° C                | 1                       | 100   |              | 100    |              | 100    |        | MΩ               |

| Capacitive load <sup>6, 7</sup>                              | No effect on dc performance, total for both outputs                                      | 4                       | 200   |              |        | 200          |        | 200    | μF               |

| Power dissipation load                                       | Overload <sup>8</sup>                                                                    | 1, 2, 3                 |       | 5.0          |        | 5.0          |        | 5.0    | w                |

| fault                                                        | Short circuit                                                                            | , ,, _, -,              |       | 2.0          |        | 2.0          |        | 2.0    |                  |

| Switching frequency 4                                        | $I_{OUT} = I_{MAX}$                                                                      | 4, 5, 6                 | 500   | 600          | 500    | 600          | 500    | 600    | KHz              |

| Output response to step                                      | I <sub>OUT</sub> = 50% ⇔ 100% I <sub>MAX</sub>                                           | 4, 5, 6                 | -400  | +400         | -400   | +400         | -400   | +400   | mV pk            |

| transient load changes<br>4, 9                               | I <sub>OUT</sub> = 0 ⇔ 50% I <sub>MAX</sub>                                              |                         | -800  | +800         | -800   | +800         | -800   | +800   |                  |

| Recovery time, step                                          | I <sub>OUT</sub> = 50% ⇔ 100% I <sub>MAX</sub>                                           | 4, 5, 6                 |       | 100          |        | 100          |        | 100    | μs               |

| transient load changes<br>4, 9, 10                           | I <sub>OUT</sub> = 0 ⇔ 50% I <sub>MAX</sub>                                              |                         |       | 2000         |        | 2000         |        | 2000   |                  |

| Output response transient step line changes                  | $V_{IN} = 15 \Leftrightarrow 50Vdc, I_{OUT} = I_{MAX}$                                   | 4, 5, 6                 | -750  | +750         | - 750  | +750         | -750   | +750   | mV pk            |

| Recovery time transient<br>step line changes<br>4, 7, 10, 11 | V <sub>IN</sub> = 15 ⇔ 50Vdc, I <sub>OUT</sub> = I <sub>MAX</sub>                        | 4, 5, 6                 |       | 1200         |        | 1200         |        | 1200   | μs               |

| Turn on overshoot <sup>4</sup>                               | I <sub>OUT</sub> = 0 and I <sub>MAX</sub>                                                | 4, 5, 6                 |       | 600          |        | 600          |        | 600    | mV pk            |

| Turn on delay 4, 12                                          | I <sub>OUT</sub> = 0 and I <sub>MAX</sub>                                                | 4, 5, 6                 |       | 25           |        | 25           |        | 25     | ms               |

| Load fault recovery 7                                        |                                                                                          | 4, 5, 6                 |       | 25           |        | 25           |        | 25     | ms               |

For Notes to Specifications, refer to page 5

#### Notes to Specifications for Table on page 4

- Parameter guaranteed by line, load, and cross regulation tests.

- Up to 80% of full power is available from either output provided the total output does not exceed 6.0 W.

- Bandwidth of DC to 20 MHz is guaranteed by design. Tested for 20 KHz to 2.0 MHz.

- Load current split equally between +V<sub>out</sub> and -V<sub>out</sub>.

1.2 watt load on output under test, 1.2 to 4.8 watt load change on other output.

- Capacitive load may be any value from 0 to the maximum limit without compromising DC performance. A capacitive load in excess of the maximum limit will not disturb loop stability but may interfere with the operation of the load fault detection circuitry, appearing as a short circuit during turn-on.

- 7. Parameter shall be tested as part of design characterization and after design or process changes. Thereafter, parameters shall be guaranteed to the limits specified.

- An overload is a condition with a load in excess of rated but less than that necessary to trigger the short circuit protection and is 8. the condition of maximum power dissipation.

- Load step transition time between 2.0 and 10 microseconds.

- 10. Recovery time is measured from the initiation of the transient to where  $V_{OUT}$  has returned to within  $\pm 1.0$  percent of  $V_{OUT}$  at 50%

- 11. Input step transition time between 2.0 and 10 microseconds.

- 12. Turn-on delay time measurements is for either a step application of power at the input or the removal of ground connection from enable pin (pin 5) with power applied to the input.

# **Dual Output - Block Diagram**

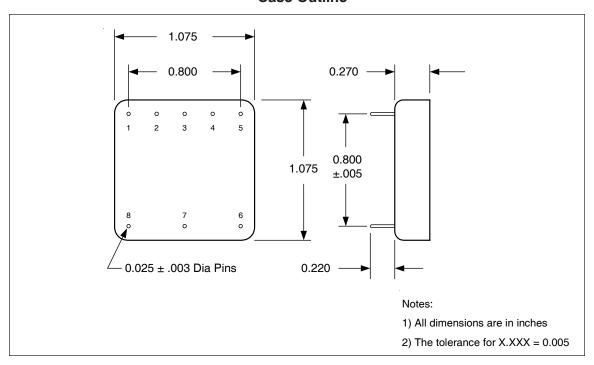

### **Case Outline**

**Single Output - Pin Designation**

| Pin # | Designation   |  |  |  |

|-------|---------------|--|--|--|

| 1     | + Output      |  |  |  |

| 2     | Output Return |  |  |  |

| 3     | N/C           |  |  |  |

| 4     | N/C           |  |  |  |

| 5     | Inhibit       |  |  |  |

| 6     | + Input       |  |  |  |

| 7     | Input Return  |  |  |  |

| 8     | Case          |  |  |  |

**Dual Output - Pin Designation**

| Pin #      | Designation   |  |  |  |  |

|------------|---------------|--|--|--|--|

| 1 + Output |               |  |  |  |  |

| 2          | Output Return |  |  |  |  |

| 3          | - Output      |  |  |  |  |

| 4          | N/C           |  |  |  |  |

| 5          | Inhibit       |  |  |  |  |

| 6          | + Input       |  |  |  |  |

| 7          | Input Return  |  |  |  |  |

| 8          | Case          |  |  |  |  |

|            |               |  |  |  |  |

## **Device Screening**

| Requirement           | MIL-STD-883 Method | No Suffix      | ES ②            | НВ              | СН              |  |

|-----------------------|--------------------|----------------|-----------------|-----------------|-----------------|--|

| Temerature Range      |                    | -20°C to +85°C | -55°C to +125°C | -55°C to +125°C | -55°C to +125°C |  |

| Element Evaluation    | MIL-PRF-38534      |                |                 |                 | Class H         |  |

| Internal Visual       | 2017               | 1              | Class H         | Class H         | Class H         |  |

| Temperature Cycle     | 1010               |                | Cond B          | Cond C          | Cond C          |  |

| Constant Acceleration | 2001, Y1 Axis      |                | 500 Gs          | 3000 Gs         | 3000 Gs         |  |

| PIND                  | 2020               |                |                 |                 |                 |  |

| Burn-In               | 1015               |                | 48 hrs @ 125°C  | 160 hrs@125°C   | 160 hrs@125°C   |  |

| Final Electrical      | MIL-PRF-38534      | 25°C           | 25°C ②          | -55°C, +25°C,   | -55°C, +25°C,   |  |

| ( Group A )           | & Specification    |                |                 | +125°C          | +125°C          |  |

| PDA                   | MIL-PRF-38534      |                |                 | 10%             | 10%             |  |

| Seal, Fine and Gross  | 1014               | Cond A         | Cond A, C       | Cond A, C       | Cond A, C       |  |

| Radiographic          | 2012               |                |                 | _               |                 |  |

| External Visual       | 2009               | ①              | Yes             | Yes             | Yes             |  |

#### Notes:

- ① Best commercial practice

- ② Samples tests at low and high temperatures

WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245, Tel: (310) 252-7105 IR SAN JOSE: 2520Junction Avenue, San Jose, California 95134, Tel: (408) 434-5000 Visit us at www.irf.com for sales contact information.

Data and specifications subject to change without notice. 10/2011