Technical Data

# Distributed System Interface (DSI) Sensor Interface

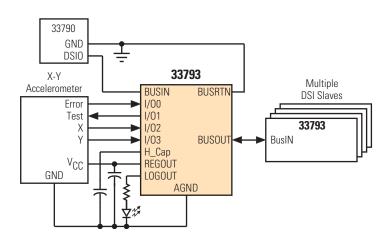

The 33793 is a slave Distributed System Interface (DSI) device that is optimized as a sensor interface. The device contains circuits to power sensors such as accelerometers and to digitize the analog level from the sensor. The device is controlled by commands over the DSI bus and returns measured data over the bus. This device is powered using SMARTMOS technology.

#### Features

- Conforms to DSI specification version 1

- 4-channel, 8-Bit analog-to-digital converter (ADC)

- 4 pins configurable as analog or logic inputs or as logic outputs

- Provides regulated +5.0 V output for sensor power from bus

- · Additional high-drive logic output

- · Undervoltage fault detection and signaling

- · On-board clock (no external elements required)

- · Field-programmable address

- · Default and field-programmable as a DSI daisy chain device

- · Recognizes reverse initialization for open bus fault tolerance

- · Detects short to battery on bus switch and prevents its closure

# 33793/A

## DISTRIBUTED SYSTEM INTERFACE

## Applications

- Simple bus-controlled part for remote control and sensing

- Automotive, aircraft, marine and industrial control and safety systems

- Heating and air-conditioning

Figure 1. 33793 Simplified Application Diagram

# **ORDERABLE PARTS**

#### Table 1. Orderable Part Variations

| Part Number    | Temperature (T <sub>A</sub> ) | Package   | Other Significant Device Variations |  |  |  |

|----------------|-------------------------------|-----------|-------------------------------------|--|--|--|

| MCZ33793EF/R2  | -40 to 150 °C                 | 40.001001 | Existing capacity                   |  |  |  |

| MCZ33793AEF/R2 | -40 10 150 C                  | 16 SOICN  | Capacity expansion                  |  |  |  |

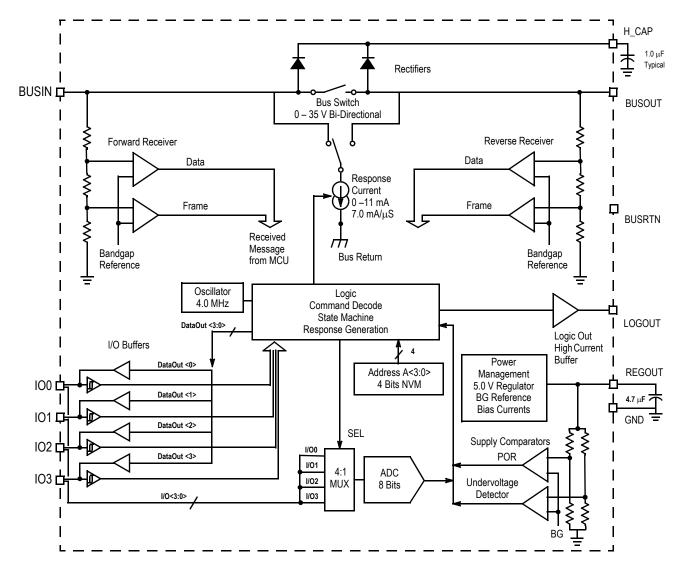

# INTERNAL BLOCK DIAGRAM

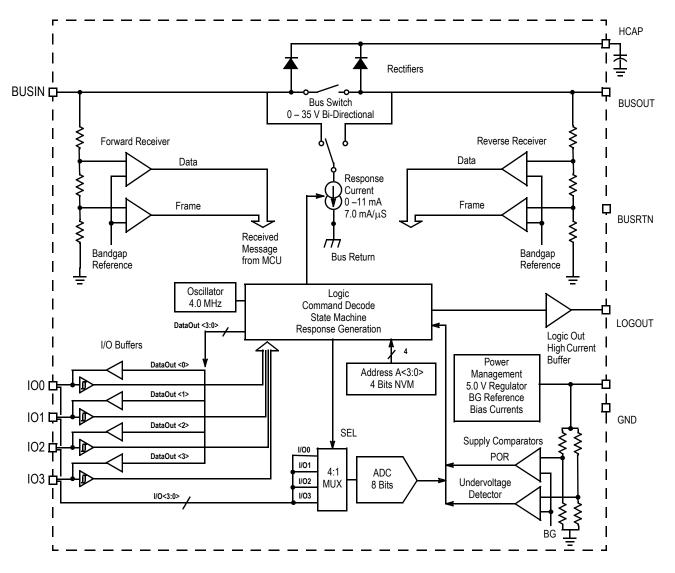

Figure 2. 33793 Simplified Internal Block Diagram

# **PIN CONNECTIONS**

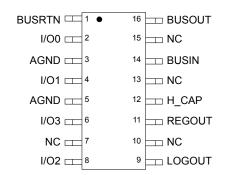

## Figure 3. 33793 Pin Connections

## Table 2. 33793 Pin Definitions

A functional description of each pin can be found in the Functional Pin Description section beginning on page 10.

| Pin Number    | Pin Name | Pin Function | Formal Name       | Definition                                                                                                                                                                         |

|---------------|----------|--------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | BUSRTN   | Power        | Bus Return        | This pin provides the common return for power and signalling.                                                                                                                      |

| 2             | I/O0     | Input/Output | Logic I/O         | This pin can be used to provide a logic level output, a logic input, or an analog-to-digital (A/D) input.                                                                          |

| 3, 5          | AGND     | Ground       | Analog Ground     | This pin is the low reference level and power return for the analog-to-digital converter (ADC).                                                                                    |

| 4             | I/O1     | Input/Output | Logic I/O         | This pin can be used to provide a logic level output, a logic input, or an A/D input.                                                                                              |

| 6             | I/O3     | Input/Output | Logic I/O         | This pin can be used to provide a logic level output, a logic input, or an A/D input.                                                                                              |

| 7, 10, 13, 15 | NC       | No Connect   | No Connect        | These pins have no internal connections.                                                                                                                                           |

| 8             | I/O2     | Input/Output | Logic I/O         | This pin can be used to provide a logic level output, a logic input, or an A/D input.                                                                                              |

| 9             | LOGOUT   | Output       | Logic Out         | This is a logic output with higher pull-up drive capability than the standard logic I/O.                                                                                           |

| 11            | REGOUT   | Output       | Regulator Output  | This pin provides a regulated 5.0 V output. The power is derived from the bus.                                                                                                     |

| 12            | H_CAP    | Output       | Holding Capacitor | A capacitor attached to this pin is charged by the bus during bus idle and supplies current to run the device and for external devices via the REGOUT pin during non-idle periods. |

| 14            | BUSIN    | Input        | DSI Bus Input     | This pin attaches to the bus and responds to initialization commands.                                                                                                              |

| 16            | BUSOUT   | Output       | DSI Bus Output    | This pin attaches to the bus and responds to reverse initialization commands.                                                                                                      |

# **ELECTRICAL CHARACTERISTICS**

## **MAXIMUM RATINGS**

## Table 3. Maximum Ratings

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Ratings                                               | Symbol            | Value                             | Unit |

|-------------------------------------------------------|-------------------|-----------------------------------|------|

| ELECTRICAL RATINGS                                    |                   |                                   |      |

| I/O Pin Voltage                                       | V <sub>IO</sub>   | -0.3 to V <sub>REGOUT</sub> + 0.5 | V    |

| I/O Pin Current                                       | I <sub>IO</sub>   | 5.0                               | mA   |

| BUSIN, BUSOUT, BUSRTN, and H_CAP Voltage              | V <sub>IN</sub>   | -0.3 to 40                        | V    |

| BUSIN, BUSOUT, BUSRTN, and H_CAP Current (Continuous) | I <sub>IN</sub>   | 250                               | mA   |

| ESD Protection <sup>(1)</sup>                         |                   |                                   | V    |

| Human Body Model                                      | V <sub>ESD1</sub> | ±2000                             |      |

| Machine Model                                         | V <sub>ESD2</sub> | ±200                              |      |

| THERMAL RATINGS                                       | •                 | •                                 | •    |

#### THERMAL RATINGS

| Storage Temperature                                                           | T <sub>STG</sub>    | -55 to 150 | °C   |

|-------------------------------------------------------------------------------|---------------------|------------|------|

| Operating Junction Temperature                                                | TJ                  | -40 to 150 | °C   |

| Peak Package Reflow Temperature During Reflow <sup>(2)</sup> , <sup>(3)</sup> | T <sub>PPRT</sub>   | Note 3.    | C    |

| Thermal Resistance Junction to Case                                           | $R_{	ext{	heta}JC}$ | 150        | °C/W |

Notes

ESD1 performed in accordance with the Human Body Model (C<sub>ZAP</sub> = 100 pF, R<sub>ZAP</sub> = 1500 Ω), ESD2 performed in accordance with the Machine Model (C<sub>ZAP</sub> = 200 pF, R<sub>ZAP</sub> = 0 Ω).

2. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

3. Freescale's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), Go to www.freescale.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics.

## STATIC ELECTRICAL CHARACTERISTICS

#### **Table 4. Static Electrical Characteristics**

Characteristics noted under conditions -0.3 V  $\leq$  V<sub>BUSIN</sub> or V<sub>BUSOUT</sub>  $\leq$  30 V, 5.5 V  $\leq$  V<sub>H\_CAP</sub>  $\leq$  30 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                                                               | Symbol             | Min  | Тур  | Max   | Unit            |

|--------------------------------------------------------------------------------------------------------------|--------------------|------|------|-------|-----------------|

| Internal Quiescent Current Drain                                                                             | l <sub>Q</sub>     |      |      |       | mA              |

| $V_{H_{CAP}}$ = 25 V, Logout = 0, I/O = Input                                                                |                    | -    | -    | 3.0   |                 |

| BUSIN or BUSOUT to H_CAP Rectifier Voltage Drop                                                              | V <sub>RECT</sub>  |      |      |       | V               |

| I <sub>BUSIN</sub> or I <sub>BUSOUT</sub> = 15 mA                                                            |                    | -    | 0.75 | 1.0   |                 |

| I <sub>BUSIN</sub> or I <sub>BUSOUT</sub> = 100 mA                                                           |                    | -    | 0.9  | 1.2   |                 |

| BUSIN + BUSOUT Bias Current                                                                                  | I <sub>BIAS</sub>  |      |      |       | μA              |

| $V_{BUSIN}$ or $V_{BUSOUT}$ = 8.0 V, $V_{H_{CAP}}$ = 9.0 V                                                   |                    | -100 | -    | 100   |                 |

| $V_{BUSIN}$ or $V_{BUSOUT}$ = 0.5 V, $V_{H_{CAP}}$ = 25 V                                                    |                    | -    | -    | 20    |                 |

| Rectifier Leakage Current                                                                                    | I <sub>RLKG</sub>  |      |      |       | μA              |

| $V_{BUSIN}$ or $V_{BUSOUT}$ = 5.0 V, $V_{H_{CAP}}$ = 25 V                                                    |                    | -20  | _    | 100   |                 |

| RegOut                                                                                                       | V <sub>REG</sub>   |      |      |       | V               |

| $5.5 \text{ V} \ge \text{V}_{\text{H}_{\text{CAP}}} \ge 25 \text{ V}, \text{ I}_{\text{RO}} = 12 \text{ mA}$ |                    | 4.75 | 5.0  | 5.25  |                 |

| RegOut Line Regulation                                                                                       | VR <sub>LINE</sub> |      |      |       | mV              |

| I <sub>RO</sub> = 12 mA, 5.5 V <u>≥</u> V <sub>H_CAP</sub> ≥ 25 V                                            |                    | _    | 71   | 180   |                 |

| RegOut Load Regulation                                                                                       | VR <sub>LD</sub>   |      |      |       | mV              |

| $I_{RO} = 0$ to 12 mA, 5.5 V $\ge$ V <sub>H_CAP</sub> $\ge$ 25 V                                             | 20                 | _    | 2.3  | 100   |                 |

| Undervoltage Lockout                                                                                         | V <sub>UVL</sub>   |      |      |       | V <sub>RO</sub> |

| Proportional to unloaded V <sub>REGOUT</sub>                                                                 | OVL                | 0.93 | 0.95 | 0.97  | NO              |

| Bus Switch Resistance                                                                                        | R <sub>SW</sub>    |      |      |       | Ω               |

| V <sub>BI</sub> = 8.0 V, I <sub>BO</sub> = -80 mA (Bus Switch Active)                                        | 31                 | _    | 4.0  | 8.0   |                 |

| /O0 and I/O3 Pull-down Current                                                                               | I <sub>PD</sub>    |      |      |       | μA              |

| 0 < V <sub>BUSIN</sub> or V <sub>BUSOUT</sub> < 1.0 V                                                        |                    | 7.0  | 11   | 13    |                 |

| /O1 and I/O2 Pull-up Current                                                                                 | I <sub>PU</sub>    |      |      |       | μA              |

| V <sub>RO</sub> < V <sub>BUSIN</sub> or V <sub>BUSOUT</sub> < V <sub>RO</sub> - 1.0 V                        |                    | -7.0 | -11  | -13   |                 |

| BUSIN and BUSOUT Logic Thresholds                                                                            |                    |      |      |       | V               |

| Low                                                                                                          | V <sub>THL</sub>   | 2.8  | 3.0  | 3.2   |                 |

| High                                                                                                         | V <sub>THH</sub>   | 5.5  | 6.0  | 6.5   |                 |

| _ogic Duty Cycle (assured by design)                                                                         |                    |      |      |       | %               |

| Logic 0                                                                                                      | D <sub>CL</sub>    | 10   | 33   | 40    |                 |

| Logic 1                                                                                                      | D <sub>CH</sub>    | 60   | 67   | 90    |                 |

| BUSIN + BUSOUT Response Current, V <sub>BUSIN</sub> and/or V <sub>BUSOUT</sub> = 4.0 V                       | I <sub>RSP</sub>   |      |      |       | mA              |

| MCZ339793EF                                                                                                  |                    | 9.9  | 11   | 12.1  |                 |

| MCZ33793AEF                                                                                                  |                    | 9.0  | 11   | 12.5  |                 |

| ADC Code Conversion Error (INL)                                                                              | ADC <sub>INL</sub> | -    | -    | < 1.0 | LSB             |

| ADC Full-scale Error                                                                                         | ADC <sub>FS</sub>  | -    | -    | 3     | counts          |

| /O Logic Input Thresholds                                                                                    |                    |      |      |       | V <sub>RO</sub> |

| Logic High                                                                                                   | V <sub>IH</sub>    | 0.7  | 0.54 | _     |                 |

| Logic Low                                                                                                    | V <sub>IL</sub>    | _    | 0.51 | 0.3   |                 |

### Table 4. Static Electrical Characteristics (continued)

Characteristics noted under conditions -0.3 V  $\leq$  V<sub>BUSIN</sub> or V<sub>BUSOUT</sub>  $\leq$  30 V, 5.5 V  $\leq$  V<sub>H\_CAP</sub>  $\leq$  30 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                                                                                                  | Symbol            | Min   | Тур   | Мах                  | Unit            |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------|-------|----------------------|-----------------|

| I/O Logic Output Levels                                                                                                                         |                   |       |       |                      |                 |

| Output Low (I <sub>L</sub> = 1.0 mA)                                                                                                            | V <sub>OL</sub>   | 0     | 0.08  | 0.5                  | V               |

| Output High (I <sub>L</sub> = -500 $\mu$ A)                                                                                                     | V <sub>OH</sub>   | 0.8   | 0.985 | 1.0                  | V <sub>RO</sub> |

| LOGOUT Output Levels                                                                                                                            |                   |       |       |                      | V               |

| Output Low ( $I_L = 500 \ \mu A$ )                                                                                                              | V <sub>LOL</sub>  | 0     | 0.2   | 0.5                  |                 |

| Output High (I <sub>L</sub> = -10 mA, 6.2 V $\leq$ V <sub>H_CAP</sub> $\leq$ 25 V)                                                              | V <sub>LOH1</sub> | 4.7   | 5.0   | 5.3                  |                 |

| Output High (I <sub>L</sub> = -100 $\mu$ A, 6.2 V $\leq$ V <sub>H_CAP</sub> $\leq$ 25 V)                                                        | V <sub>LOH2</sub> | -     | -     | V <sub>RO</sub> +0.5 |                 |

| Programming Time                                                                                                                                | T <sub>PROG</sub> |       |       |                      | ms              |

| From Positive Edge of BUSIN or BUSOUT $\ge$ V <sub>THH</sub> on Program Command to Following Command Negative Transition $\le$ V <sub>THH</sub> |                   | 100   | 200   | 1000                 |                 |

| NVM BUSIN or BUSOUT Programming Voltage                                                                                                         | NVM <sub>VP</sub> | 22.25 | -     | 30                   | V               |

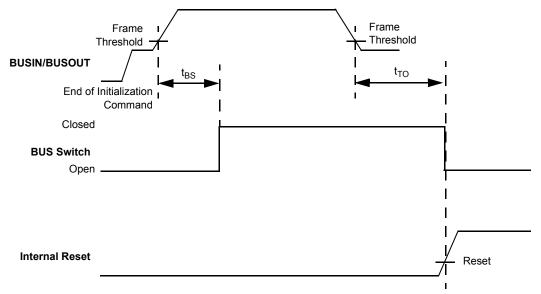

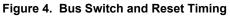

## **DYNAMIC ELECTRICAL CHARACTERISTICS**

#### **Table 5. Dynamic Electrical Characteristics**

$Characteristics noted under conditions -0.3 \ V \le V_{BUSIN} \ or \ V_{BUSOUT} \le 30 \ V, \ 5.5 \ V \le V_{H\_CAP} \le 30 \ V, \ -40^{\circ}C \le T_A \le 85^{\circ}C \ unless \ otherwise noted.$  Typical values noted reflect the approximate parameter means at  $T_A = 25^{\circ}C$  under nominal conditions unless otherwise noted.

| Characteristic                                                                                                                                                                                                      | Symbol           | Min | Тур | Max        | Unit  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|-----|------------|-------|

| Initialization to Bus Switch Closing                                                                                                                                                                                | t <sub>BS</sub>  | 100 | 150 | 200        | μS    |

| Loss of Signal Reset Time<br>Maximum Time Below Frame Threshold                                                                                                                                                     | t <sub>TO</sub>  | _   | _   | 100        | ms    |

| ADC Code Conversion Time (Go, No-Go Test)                                                                                                                                                                           | t <sub>ADC</sub> | -   | -   | 27         | μS    |

| BUSIN and BUSOUT Response Current Transition Time<br>1.0 to 9.0 mA Transition, 9.0 to 1.0 mA                                                                                                                        | t <sub>ITR</sub> | _   | 7.0 | 10         | mA/μs |

| BUSIN or BUSIN Timing to Response Current<br>BUSIN or BUSOUT Negative Voltage Transition = 3.0 V to I <sub>RSPH</sub> = 7.0 mA<br>BUSIN or BUSOUT Negative Voltage Transition = 3.0 V to I <sub>RSPL</sub> = 5.0 mA |                  | _   | _   | 3.3<br>3.3 | μs    |

## TIMING DIAGRAMS

Figure 5. Response Current Timing

# FUNCTIONAL DESCRIPTION

## **INTRODUCTION**

The 33793 is designed to be used with a sensor at a location that is remote from a centralized MCU. This device provides power, measurement, and communications between the remote sensor and the centralized MCU over a DSI bus. Sensors such as accelerometers can be powered from the regulated output of the device, and the resulting analog value from the sensor can be converted from an analog level to a digital value for transmission over the DSI bus in response to a query from the MCU. Four I/O lines can be configured by the central MCU over the DSI bus as analog inputs, digital inputs, or digital outputs. This allows more than one sensor to be remotely controlled and measured by a single 33793. Additionally, a high drive logic output is provided that can be used to power other low-power sensors.

Power is passed from BUSIN or BUSOUT through on-board rectifiers to a storage capacitor (referred to as the H\_CAP). The H\_CAP stores energy during the highest voltage excursions of the BUSIN or BUSOUT pin (idle) and supplies

energy to power the device during low excursions of BUSIN and BUSOUT.

The Regulator supplies an on-board regulated voltage for internal use, and the Power on Reset (POR) circuit provides a reset signal during low-voltage conditions and during power up/down. Some current is available for low-power sensors.

Data from the Central Control Unit (CCU) is applied to the BUSIN and/or BUSOUT pins as voltage levels that are sensed by the Level Detection circuitry. The Serial Decoder detects these transitions and decodes the incoming data. The Control Logic provides overall control of the 33793. It controls diagnostic testing and formats responses to commands with the message encoder. Responses are formed via a switched current source that is slew-rate controlled.

The one-time programmable (OTP) memory array provides the nonvolatile storage for the pre-programmed address. It is accessed via the Read/Write NVM command. It has a built-in hardware lock that only allows one write.

## FUNCTIONAL PIN DESCRIPTION

#### **BUS RETURN (BUSRTN)**

This pin provides the common return for power and signalling.

## INPUT/OUTPUT (I/O0, I/O1, I/O2, I/O3)

This pin can be used to provide a logic level output, a logic input, or an analog-to-digital (A/D) input.

## ANALOG GROUND (AGND)

This pin is the low reference level and power return for the analog-to-digital converter (ADC).

## LOGIC OUT (LOGOUT)

This is a logic output with higher pull-up drive capability than the standard logic I/O.

## **REGULATOR OUTPUT (REGOUT)**

This pin provides a regulated 5.0 V output. The power is derived from the bus.

## HOLDING CAPACITOR (H\_CAP)

A capacitor attached to this pin is charged by the bus during bus idle and supplies current to run the device and for external devices via the REGOUT pin during non-idle periods.

## **DSI BUS INPUT (BUSIN)**

This pin attaches to the bus and responds to initialization commands.

## **DSI BUS OUTPUT (BUSOUT)**

This pin attaches to the bus and responds to reverse initialization commands.

## FUNCTIONAL INTERNAL BLOCK DESCRIPTION

Refer to <u>Figure 2</u>, 33793 Internal Block Diagram, page <u>3</u>, for a simplified representation of the 33793's components.

## RECTIFIER

This rectifier or switch peak detects the bus signal into an external capacitor attached to H\_CAP. The capacitor supplies power during signaling while the input voltage is at a lower level.

The voltage waveform at BUSIN and/or BUSOUT and the size of the filter capacitor at H\_CAP must be such that the **33793**

voltage at H\_CAP will not drop below the frame threshold during signaling.

#### POR

The 33793 leaves the reset state when the voltage on H\_CAP rises above the Power-ON Reset threshold.

## TIMEOUT

A timeout timer keeps track of the length of the time when the input is not in idle mode. If this time exceeds a limit, the part

NP

is reset. The purpose of this is to allow the part to reset itself if the connection to the master is lost or if power is removed from the system.

#### **5.0 V REGULATOR**

The 5.0 V regulator supplies internal power for the device and also provides approximately 6.0 mA through the REGOUT pin to power an external sensor.

## UNDERVOLTAGE DETECTOR

The undervoltage detector monitors the output voltage of the 5.0 V regulator. If the REGOUT voltage drops too low for accurate A/D operation, a signal is sent to the control logic. The control logic will interpret this signal and, in response to a command, report a status indicating an undervoltage condition to have existed. When received, the command will clear the signal after having read the status. If the voltage is too low when the A/D conversion was completed, the returned value will be zero (binary 0000000).

## **IO PINS 0 TO 3**

The IO pins can serve as logic inputs, logic outputs, or analog inputs. At power-up or after a clear, the pins are all logic inputs and can be used to measure an analog level value for an analog value request command. The pins can be individually configured as logic inputs or outputs by the IO Control command. If the pin is configured as a logic output, reading the analog value will return the analog level the output is being driven to.

## ANALOG-TO-DIGITAL CONVERTER

The ADC is an 8-bit successive approximation type using onboard capacitive division. It uses the Clk signal from the onboard oscillator for sequencing.

The ADC uses REGOUT as a full-scale reference voltage and ground AGND for a zero-level reference.

The ADC signals when it has made a valid conversion by asserting a signal to the controller. If this signal is not asserted when a value is being captured by the controller, the controller will signal that an invalid A/D value was obtained.

The value of "0" (binary 0000000) is reserved by the control logic to signal an error. A value of "0" from the ADC will be reported as "1" (binary 00000001) by the control logic.

## SERIAL ENCODER

The Serial Encoder accepts the digitized value from the ADC and formatting/data from the Control Logic. A logic transition from Idle to Signal High and then to Signal Low at BUSIN will cause the first bit to be presented to the current switch (Response Loading). A transition to Signal High and back to Signal Low will cause the next bit to be presented to the current switch. This will continue until a transition back to Idle turns off the current switch.

#### SLEW

The slew circuit serves to reduce EMI produced as a result of switching the bus loading current sink element. The slew

#### SWITCHED CURRENT SOURCE

A "1" data return bit will be signaled by turning on a fixed current source. During signaling time, the 33793 will be using power from H\_CAP and not loading the bus for power. The current will be drawn from either BUSIN or BUSOUT or split between them. The split can be in any proportion as long as the total is correct.

The current source is turned off whenever the bus is at Idle level.

## LEVEL DETECTOR

The level detector contains comparators to determine if the BUSIN or BUSOUT is at idle, logic high, or logic low. The inputs from BUSIN and BUSOUT are sensed by the device so that if either side is driven by the signaling waveform while the other is not, the signaling will be detected. This circuit also provides a signal to indicate if the signal is being received on the BUSOUT pin. If a "reverse initialization" command is received, it can only be acted upon if the device is not already initialized and if the signal is present on BUSOUT.

## SERIAL DECODER

The Serial Decoder monitors transitions on the BUSIN or BUSOUT. When the 33793 is Idle and supplying power to itself and the external device(s) (via REGOUT), the input to BUSIN will be in the Idle state. A transition from this level to Signal Low (through Signal High) will start the process of decoding a word of data. BUSIN is driven from Signal Low to Signal High for each bit and back to Signal Low to start the next bit. The determination of whether the bit was a one or a zero is made by determining whether it spent more time low (a zero) or high (a one). The end of the word is signaled by a transition at the end of the last bit from Signal High to Idle. The advantage of this method is that it will accept data over a wide range of rates and is not dependent on an accurate clock.

The controller will typically indicate a logic zero by spending 2/3 of the bit period at Signal Low and 1/3 at Signal High. A logic one would be 1/3 of the bit period at Signal Low and 2/ 3 at Signal High.

#### CONTROL LOGIC

The control logic performs the digital operations carried out by this device. Its principle functions include:

- · Decoding input instructions.

- Control the general purpose I/O and LOGICOUT in response to BUSIN or BUSOUT commands.

- Control A/D conversions.

- Form response word.

- Capture and store address.

- Control BUSSW.

- · Reset device on power-up.

- · Control the general purpose I/O logic configuration.

- Read the general purpose I/O logic values and respond to request for these values.

- Generating a cycle redundancy check (CRC) for the received data and transmitted data in conformance with the DSI Bus Standard.

Additionally, the control logic performs error checking on the received data. If errors are found, no action is taken and no response is made. Errors include:

- CRC received doesn't match CRC of received data.

- Number of received bits is not 12 or 20.

## CLOCK

The clock is a low-stability type with the capacitor integrated onto the die. The signaling system and all internal operations are such that no external precision timing device is needed in the normal operation of this device.

## **BUS SWITCH (BUSSW)**

The bus switch passes signaling and power to all subsequent devices on the bus. It can block a voltage of either polarity up to the highest idle state level between BUSIN and BUSOUT.

## LOGICOUT

LOGICOUT is a logic level output with enhanced high-side drive capability.

## ADDRESSING

The 33793 IC supports both runtime programmable and preprogrammed addressing as defined in the DSI Specification. Runtime programmable addressing uses the daisy chain bus connection. Pre-programmed devices may either be connected in daisy chain or in parallel on the bus wires.

Programmable address devices all power up with a device address of \$0 in their address register and their bus switches open. In the daisy chain, if the first device receives the initialization command device on BUSIN, it will accept the address in the command and close its switch at the end of the command. The next device in the chain will now be able to receive the initialization command on its BUSIN and will accept the next address. This proceeds down the chain until the last device is addressed. The devices can also be initialized by the reverse initialization command if the signal is applied to BUSOUT.

Pre-programmed devices power up with their preprogrammed address in its address register. It will ignore all Initialization commands unless the address in the command matches its pre-programmed address. In this event the device stores the other information contained in the Initialization command.

## **OPERATIONAL MODES**

A device may be permanently programmed one time with an address using a two-command sequence. The first step is satisfied on the reception of an Initialization command with address set to zero, the PA[3:0] set to the address to be programmed, and the NV bit set. This will cause the address contained in the PA[3:0] bits to be stored in the address register and the bus switch closed. The second step is taken when a Read/Write NVM command is received with the PA[3:0] bits matching the A[3:0] bits and also matching the bits stored in the 33793 address register. This will cause the 33793 to permanently store this address into an internal NVM area.

#### MESSAGES

The messages follow the format defined in the Distributed Systems Interface Specification rev. 1.0 unless otherwise noted.

## **DSI BUS COMMANDS**

This device can recognize and respond to both long-word and short-word commands. A command word summary is shown in <u>Table 6</u>. SW in the "Size" column of the table indicates short-word commands and LW indicates long-word commands. Short-word commands may also be sent in the long-word format. However, when these commands are sent in the long-word format, it is recommended that the data byte be sent as \$00 to maintain future compatibility. All commands marked reserved should not be sent to 33793 slaves.

|    | Com | mand |    | 0:   | Description            |    |    |    |    | Data |     |     |     |

|----|-----|------|----|------|------------------------|----|----|----|----|------|-----|-----|-----|

| C3 | C2  | C1   | C0 | Size | Description            | D7 | D6 | D5 | D4 | D3   | D2  | D1  | D0  |

| 0  | 0   | 0    | 0  | LW   | Initialization         | NV | BS | G1 | G0 | PA3  | PA2 | PA1 | PA0 |

| 0  | 0   | 0    | 1  | SW   | Request Status         | -  | -  | _  | _  | _    | -   | -   | -   |

| 0  | 0   | 1    | 0  | SW   | Request Value 0        | -  | -  | _  | _  | _    | -   | -   | -   |

| 0  | 0   | 1    | 1  | LW   | I/O Control            | L3 | L2 | L1 | L0 | DR3  | DR2 | DR1 | DR0 |

| 0  | 1   | 0    | 0  | SW   | Request ID Information | _  | -  | _  | _  | _    | -   | -   | -   |

| 0  | 1   | 0    | 1  | SW   | Request Value 1        | -  | -  | _  | _  | _    | -   | -   | -   |

| 0  | 1   | 1    | 0  | SW   | Request Value 2        | _  | -  | _  | _  | _    | -   | -   | -   |

| 0  | 1   | 1    | 1  | SW   | Clear                  | _  | -  | _  | _  | _    | -   | -   | -   |

| 1  | 0   | 0    | 0  | SW   | Request Value 3        | -  | -  | _  | _  | _    | -   | -   | -   |

| 1  | 0   | 0    | 1  | LW   | Read/Write NVM         | 1  | 1  | 1  | 1  | PA3  | PA2 | PA1 | PA0 |

| 1  | 0   | 1    | 0  |      | Reserved               |    |    |    |    |      |     |     |     |

| 1  | 0   | 1    | 1  |      | Reserved               |    |    |    |    |      |     |     |     |

| 1  | 1   | 0    | 0  | SW   | Clear Logic Out        | -  | -  | _  | _  | _    | -   | -   | -   |

| 1  | 1   | 0    | 1  | SW   | Set Logic Out          | -  | -  | _  | -  | _    | -   | -   | -   |

| 1  | 1   | 1    | 0  |      | Reserved               |    |    |    |    |      |     |     |     |

| 1  | 1   | 1    | 1  | LW   | Reverse Initialization | NV | BS | G1 | G0 | PA3  | PA2 | PA1 | PA0 |

#### Table 6. DSI Bus Commands

Legend

BS = Controls closing of the Bus Switch (1 = close).

DR[3:0] = Direction of I/O. 1 = Output.

G[1:0] = Group assignment (the 33793 does not use these bits).

L[3:0] = Level to output on I/O if configured as outputs.

LO = Logic Out level.

PA[3:0] = Bus Address to set the device to.

NV = Allows nonvolatile address programming if set to "1".

## LONG- AND SHORT-WORD RESPONSES

The device responds to Long-word commands with long-word responses and short-word commands with short-word responses. Responses are sent during the next message following the command. A long-word response summary is found in <u>Table 7</u> and a short-word response summary is found in <u>Table 8</u>, page <u>15</u>.

| CMD<br>hex | Command<br>Description |      |       |    |    |   |   |   | Re | espons | se |    |    |     |     |     |     |

|------------|------------------------|------|-------|----|----|---|---|---|----|--------|----|----|----|-----|-----|-----|-----|

| 0          | Initialization         | A3   | A2    | A1 | A0 | 0 | 0 | 0 | BF | NV     | BS | G1 | G0 | PA3 | PA2 | PA1 | PA0 |

| 1          | Request Status         | A3   | A2    | A1 | A0 | 0 | 0 | 0 | 0  | NV     | U  | LO | BS | IO3 | IO2 | IO1 | 100 |

| 2          | Request Value 0        | A3   | A2    | A1 | A0 | 0 | 0 | 0 | 0  | B7     | B6 | B5 | B4 | B3  | B2  | B1  | B0  |

| 3          | I/O Control            | A3   | A2    | A1 | A0 | 0 | 0 | 0 | 0  | L3     | L2 | L1 | L0 | DR3 | DR2 | DR1 | DR0 |

| 4          | Request ID             | A3   | A2    | A1 | A0 | 0 | 0 | 0 | 0  | V2     | V1 | V0 | 0  | 0   | 0   | 1   | 1   |

| 5          | Request Value 1        | A3   | A2    | A1 | A0 | 0 | 0 | 0 | 0  | B7     | B6 | B5 | B4 | B3  | B2  | B1  | B0  |

| 6          | Request Value 2        | A3   | A2    | A1 | A0 | 0 | 0 | 0 | 0  | B7     | B6 | B5 | B4 | B3  | B2  | B1  | B0  |

| 7          | Clear                  | No R | espon | se |    |   |   |   |    |        |    |    |    |     |     |     |     |

| 8          | Request Value 3        | A3   | A2    | A1 | A0 | 0 | 0 | 0 | 0  | B7     | B6 | B5 | B4 | B3  | B2  | B1  | B0  |

| 9          | Read/Write NVM         | A3   | A2    | A1 | A0 | 0 | 0 | 0 | 0  | 1      | 1  | 1  | 1  | PA3 | PA2 | PA1 | PA0 |

| A          | Reserved               |      |       |    |    |   |   |   |    |        |    |    |    |     |     |     |     |

| В          | Reserved               |      |       |    |    |   |   |   |    |        |    |    |    |     |     |     |     |

| С          | Clear Logic Out        | A3   | A2    | A1 | A0 | 0 | 0 | 0 | 0  | NV     | U  | LO | BS | IO3 | IO2 | IO1 | 100 |

| D          | Set Logic Out          | A3   | A2    | A1 | A0 | 0 | 0 | 0 | 0  | NV     | U  | LO | BS | IO3 | IO2 | IO1 | IO0 |

| E          | Reserved               |      |       |    |    |   |   |   |    |        |    |    |    |     |     |     |     |

| F          | Reverse Initialization | A3   | A2    | A1 | A0 | 0 | 0 | 0 | BF | NV     | BS | G1 | G0 | PA3 | PA2 | PA1 | PA0 |

#### Table 7. Long-Word Response Summary

Legend

A[3:0] = Address bits. The slave address.

B[7:0] = 8-bit A/D value.

BF = Bus Fault

BS = Status of the Bus Switch (1 = close).

DR[3:0] = I/O direction bits (1 = Output).

G[1:0] = Group assignment (the 33793 does not use these bits).IO[3:0] = Logic level of I/O. L[3:0] = Level to output on I/O if configured as outputs.

LO = Logic Out level at the Logic Out pin.

NV = Allows nonvolatile address programming if set to "1".

PA[3:0] = Bus Address to set the device to.

U = Undervoltage Flag.

V[2:0] = Version number.

#### Table 8. Short-word Response Summary

| Command | Command<br>Description |             |     |          | R  | esponse |     |     |     |  |  |  |  |

|---------|------------------------|-------------|-----|----------|----|---------|-----|-----|-----|--|--|--|--|

| 0000    | Initialization         | Not Va      | lid |          |    |         |     |     |     |  |  |  |  |

| 0001    | Request Status         | NV          | U   | LO       | BS | IO3     | IO2 | IO1 | 100 |  |  |  |  |

| 0010    | Request Value 0        | B7          | B6  | B5       | B4 | В3      | B2  | B1  | В0  |  |  |  |  |

| 0011    | I/O Control            | Not Va      | lid |          |    |         | 1   |     |     |  |  |  |  |

| 0100    | Request ID Information | V2          | V1  | V0       | 0  | 0       | 0   | 1   | 1   |  |  |  |  |

| 0101    | Request Value 1        | B7          | B6  | B5       | B4 | В3      | B2  | B1  | B0  |  |  |  |  |

| 0110    | Request Value 2        | B7          | B6  | B5       | B4 | B3      | B2  | B1  | B0  |  |  |  |  |

| 0111    | Clear                  | No Response |     |          |    |         |     |     |     |  |  |  |  |

| 1000    | Request Value 3        | B7          | B6  | B5       | B4 | B3      | B2  | B1  | B0  |  |  |  |  |

| 1001    | Read/Write NVM         | Not Va      | lid |          |    |         | 1   |     |     |  |  |  |  |

| 1010    | Reserved               |             |     |          |    |         |     |     |     |  |  |  |  |

| 1011    | Reserved               |             |     |          |    |         |     |     |     |  |  |  |  |

| 1100    | Clear Logic Out        | NV          | U   | LO       | BS | IO3     | 102 | IO1 | 100 |  |  |  |  |

| 1101    | Set Logic Out          | NV          | U   | LO       | BS | IO3     | 102 | IO1 | 100 |  |  |  |  |

| 1110    | Reserved               |             |     |          |    |         |     |     |     |  |  |  |  |

| 1111    | Reverse Initialization | Not Va      | lid | <b>I</b> |    | 1       | 1   | 1   |     |  |  |  |  |

Legend

B[7:0] = 8-bit A/D value.

IO[3:0] = Logic level of I/O.

BS = Status of the Bus Switch (1 = close).

LO = Logic Out level at the Logic Out pin.

U = Undervoltage Flag.

V[2:0] = Version number.

## **DSI COMMANDS AND RESPONSES**

NV = Allows nonvolatile address programming if set to "1".

PA[3:0] = Bus Address to set the device to.

## INITIALIZATION COMMAND

The Initialization command must be sent to the 33793 before it may commence communications over the bus. The command may be used three ways. The first is to initialize a programmable address device. The second is the first step in assigning a pre-programmed address. The third is to initialize a pre-programmed device.

For the first case this command is sent to address zero with the NV bit set to zero. The command will be received by the next daisy chain device with its bus switch open. Reception of this command will assign the device address and group number.

For the second case the Initialization command is sent the same as the first except that the NV bit is set to one.

Reception of the command will assign the device address and group number. A Read/Write NVM command then may be sent to complete the setting of a pre-programmed address.

A pre-programmed device must be initialized by putting its address in both PA3:PA0 and A3:A0 fields.

Once a device has received an initialization command, it will ignore further initialization commands unless it has received a Clear command or undergone a power-up reset.

If BS = 1 and no faults are detected, initialization will cause the bus switch to close.

The command format is found in <u>Table 9</u>.

#### **Table 9. Initialization Command Format**

|      |        |    |    | Data |     |     |     | Address |    |    |    | Command |   |   |   | CRC |    |    |    |

|------|--------|----|----|------|-----|-----|-----|---------|----|----|----|---------|---|---|---|-----|----|----|----|

| NV   | BS     | G1 | G0 | PA3  | PA2 | PA1 | PA0 | A3      | A2 | A1 | A0 | 0       | 0 | 0 | 0 | X3  | X2 | X1 | X0 |

| Lege | _egend |    |    |      |     |     |     |         |    |    |    |         |   |   |   |     |    |    |    |

A[3:0] = Address bits. The slave address. BS = Bus Switch Position (1 = closed).

G[1:0] = Group bits (unused).

NV = Nonvolatile Memory Write. The value of the NV bit in the slave. PA[3:0] = Bus Address to set the device to.

X[3:0] = Cyclic Redundancy Check (CRC). The CRC as calculated by the master.

NV = Nonvolatile Memory Write. The value of the NV bit in the slave.

X[3:0] = Cyclic Redundancy Check (CRC). The CRC as calculated by

O and LOGICOUT. The command format is found in

X[3:0] = Cyclic Redundancy Check (CRC). The CRC as calculated by the

is generated if the command address field was \$0.

device. The response format is found in Table 12. The high byte is omitted during the short-word response. No response

PA[3:0] = Bus Address to set the device to.

#### **INITIALIZATION RESPONSE**

This response message is sent during the next message following a valid Initialization command to the addressed device. The response is shown in Table 10. Because this is a long-word only command, the short-word response is invalid.

#### Table 10. Initialization Response Format

|    | High Byte |    |    |   |   |   |    |    | Low Byte |    |    |     |     |     |     |    | CRC |    |    |  |

|----|-----------|----|----|---|---|---|----|----|----------|----|----|-----|-----|-----|-----|----|-----|----|----|--|

| A3 | A2        | A1 | A0 | 0 | 0 | 0 | BF | NV | BS       | G1 | G0 | PA3 | PA2 | PA1 | PA0 | X3 | X2  | X1 | X0 |  |

Legend

A[3:0] = Address bits. The slave address.

BF = Bus Fault. Bus out short to battery detected.

BS = Bus Switch Position (1 = closed).

G[1:0] = Group bits (unused).

#### **REQUEST STATUS COMMAND**

This command will cause the addressed device to return the status of the NV, U, and BS bits and the logic levels of the I/

#### **Table 11. Request Status Command Format**

the slave.

Table 11.

|   |   |   | 0 | )ata |   |   |   |    | Add | ress |    |   | Com | mand |    | RC |    |

|---|---|---|---|------|---|---|---|----|-----|------|----|---|-----|------|----|----|----|

| _ | _ | _ | _ | _    | _ | _ | _ | A3 | A2  | A1   | A0 | 0 | 0   | 0    | X3 | X1 | X0 |

master.

Legend

A[3:0] = Address bits. The address of the selected device. An address value of "0000" is ignored by all devices.

## **REQUEST STATUS RESPONSE**

This response message is sent during the next message following a valid Request Status command to the addressed

#### Table 12. Request Status Response Format

|       |    |    | High | Byte |   |   |   |    |   |    | Low By | /te |     |     |     |    | C  | RC |    |

|-------|----|----|------|------|---|---|---|----|---|----|--------|-----|-----|-----|-----|----|----|----|----|

| A3    | A2 | A1 | A0   | 0    | 0 | 0 | 0 | NV | U | LO | BS     | 103 | 102 | IO1 | 100 | X3 | X2 | X1 | X0 |

| Logor | d  |    |      |      |   |   |   |    |   |    |        |     |     |     |     |    |    |    |    |

| Legend                                    |  |

|-------------------------------------------|--|

| A[3:0] = Address bits. The slave address. |  |

| BS = Bus Switch Position (1 = closed).    |  |

| LO = Logic out driven level.              |  |

IO[3:0] = Values at logic I/Os.

NV = Nonvolatile Memory Write. The value of the NV bit in the slave. U = Undervoltage indicated true by a "1".

X[3:0] = Cyclic Redundancy Check (CRC). The CRC as calculated by the slave.

#### **REQUEST VALUE n COMMAND**

This command will cause the analog level at one of the four I/O lines to be measured and returned on the following

#### Table 13. Request Value n Command Format

|   | Data |   |   |   |   |   |   |   |    | Add | ress |    |    | Com | mand |    |    | С  | RC |    |

|---|------|---|---|---|---|---|---|---|----|-----|------|----|----|-----|------|----|----|----|----|----|

| _ |      | _ | _ | _ | _ | - | - | - | A3 | A2  | A1   | A0 | C3 | C2  | C1   | C0 | X3 | X2 | X1 | X0 |

Legend

A[3:0] = Address bits. The address of the selected device. An address value of "0000" is ignored by all devices. C[3:0] = Command number.

X[3:0] = Cyclic Redundancy Check (CRC). The CRC as calculated by the master.

command. The command format is found in Table 13. The

analog input measured is defined in Table 14.

#### Table 14. Analog Input Selection

| Command | A/D Input |

|---------|-----------|

| 0010    | I/O0      |

| 0101    | I/O1      |

| 0110    | I/O2      |

| 1000    | I/O3      |

#### **REQUEST VALUES RESPONSE**

This response is an 8-bit value representing the value measured by the ADC. The selection of "n" is a function of the command. This is shown in <u>Table 15</u>.

The read will be completed during the idle period and will represent the voltage at the end of the command. If an undervoltage condition exists at any time during the command or the measurement has not completed properly, a value of "00000000" will be returned. This is a reserved value to indicate a problem with the measurement. The minimum valid level reported will be "00000001". No response is generated if the command address field was \$0.

#### Table 15. Request Values Response Format

|    | High Byte |    |    |   |   |   |   |    |    |    | Lo | w Byte |    |    |  | CR |    |    |

|----|-----------|----|----|---|---|---|---|----|----|----|----|--------|----|----|--|----|----|----|

| A3 | A2        | A1 | A0 | 0 | 0 | 0 | 0 | D7 | D6 | D5 | D4 | D3     | D2 | D1 |  | X2 | X1 | X0 |

Legend

A[3:0] = Address bits. The address of the selected device. An address value of "0000" is ignored by all devices. D[7:0] = Measured value (MSB = D7).

in Table 16.

X[3:0] = Cyclic Redundancy Check (CRC).

## I/O CONTROL COMMAND

This register controls the I/O ports. When the "DR" bits are set, the corresponding I/O is enabled as an output. The "L" bit

#### Table 16. I/O Control Command Format

|    |    |    |    | Data |     |     |     |    | Add | ress |    |   | Com | mand |   |    | CI | RC |    |

|----|----|----|----|------|-----|-----|-----|----|-----|------|----|---|-----|------|---|----|----|----|----|

| L3 | L2 | L1 | L0 | DR3  | DR2 | DR1 | DR0 | A3 | A2  | A1   | A0 | 0 | 0   | 1    | 1 | Х3 | X2 | X1 | X0 |

Legend

A[3:0] = Address bits.

DR[3:0] = I/O direction bits. 1 = Output. All bits are set to "0" by reset/clear.

L[3:0] = Level to output on I/O if configured as output. All bits are set to "0" by reset/clear

settings control the level of the corresponding I/O if it is enabled as an output. The format of this command is shown

X[3:0] = Cyclic Redundancy Check (CRC). The CRC as calculated by the master.

## **I/O CONTROL RESPONSE**

The response indicates which I/O has been configured as outputs and their current values.

The values returned will be the values programmed. The values at the pins will not be the ones that were programmed if the pin has been forced to the opposite state. The response format is shown in <u>Table 17</u>. No response is generated if the command address field was \$0.

#### Table 17. I/O Control Response Format

|      |    |    | High | Byte |   |   |   |    |    |    | L  | ow Byte | 9   |     |     |    | C  | RC |    |

|------|----|----|------|------|---|---|---|----|----|----|----|---------|-----|-----|-----|----|----|----|----|

| A3   | A2 | A1 | A0   | 0    | 0 | 0 | 0 | L3 | L2 | L1 | L0 | DR3     | DR2 | DR1 | DR0 | X3 | X2 | X1 | X0 |

| Lege | nd |    |      |      |   |   |   |    |    |    |    |         |     |     |     |    |    |    |    |

A[3:0] = Address bits.

DR[3:0] = I/O enabled as outputs (1 = enabled as output).

L[3:0] = Programmed values.

in Table 18.

X[3:0] = Cyclic Redundancy Check (CRC). The CRC as calculated by the slave.

X[3:0] = Cyclic Redundancy Check (CRC). The CRC as calculated by the

addressed device. The response format is found in <u>Table 19</u>. The high byte is omitted during the short-word response. No

response is generated if the command address field was \$0.

response to the next message. The command format is found

## **REQUEST ID COMMAND**

This command will cause the device ID information to be read from internal storage and returned to the master during the

#### Table 18. Request ID Command Format

|   | Data |   |   |   |   |   |   | Add | ress |    |    | Com | mand |   | CF | RC |    |    |

|---|------|---|---|---|---|---|---|-----|------|----|----|-----|------|---|----|----|----|----|

| - | -    | - | - | - | - | - | - | A3  | A2   | A1 | A0 | 0   | 1    | 0 | 0  |    | X1 | X0 |

master.

Legend

A[3:0] = Address bits. The address of the selected device. An address value of "0000" is ignored by all devices.

## **REQUEST ID RESPONSE**

This response message is sent during the next message following a valid long-word Request ID command to the

#### Table 19. Request ID Response Format

|    | Add | ress |    |   | Sta | tus |   |    |    |    | Data |   |   |   |   | CF | ۲C |    |

|----|-----|------|----|---|-----|-----|---|----|----|----|------|---|---|---|---|----|----|----|

| A3 | A2  | A1   | A0 | 0 | 0   | 0   | 0 | V2 | V1 | V0 | 0    | 0 | 0 | 1 | 1 | X2 | X1 | X0 |

Legend

A[3:0] = Address bits. The slave address.

V[2:0] = Device version number. The silicon version number of the slave. device. For this device the device type is 00011 as indicated by the lowest bits.

## **CLEAR COMMAND**

This command will open the bus switch and reset all registers to the reset state. The command format is found in <u>Table 20</u>. No response is generated for the Clear command.

#### Table 20. Clear Command Format

|   |   |   |   | Data |   |   |   |    | Add | Iress |    |   |   | mand |   |    | С  | RC |    |

|---|---|---|---|------|---|---|---|----|-----|-------|----|---|---|------|---|----|----|----|----|

| - | - | - | - | -    | - | - | - | A3 | A2  | A1    | A0 | 0 | 1 | 1    | 1 | Х3 | X2 | X1 | X0 |

Legend

A[3:0] = Address bits. The address of the selected device. An address value of "0000" clears all devices.

## READ/WRITE NVM COMMAND

If the NV bit has been set by a previous Initialization command and the NVM has not been programmed previously, this command will permanently program the device's one-time programmable address and return the programmed value during the next message time. Once programmed, this nonvolatile address is used to set the X[3:0] = Cyclic Redundancy Check (CRC). The CRC as calculated by the master.

device address register on the next and all subsequent power-ups. If the device is not blank, this command will return the programmed value during the next message time.

Programming the NVM address to \$0 is allowed. This ensures that the device always acts as a dynamically addressable device and would be immune to any inadvertent future NVM programming sequences.

X[3:0] = Cyclic Redundancy Check (CRC). The CRC as calculated by the

Reads and writes are long-word commands only. The command format is found in Table 21.

#### Table 21. Read/Write NVM Command Format

|   |   |   |   |     |     |     |     |    | Add | lress |    |   | Com | mand |   |    | С  | RC |    |

|---|---|---|---|-----|-----|-----|-----|----|-----|-------|----|---|-----|------|---|----|----|----|----|

| 1 | 1 | 1 | 1 | PA3 | PA2 | PA1 | PA0 | A3 | A2  | A1    | A0 | 1 | 0   | 0    | 1 | Х3 | X2 | X1 | X0 |

Legend

A[3:0] = Address bits. These bits are the address of the device previously sent with the Initialization command. They must match the address in the PA[3:0] field and the address stored in the device X[3:0] = Cyclic Redundancy Check (CRC). The CRC as calculated by the address register.

PA[3:0] = Program Address bits. These bits are the address that is to be programmed into the slave.

master.

X[3:0] = Cyclic Redundancy Check (CRC). The CRC as calculated by the

Out. The Logic Out is also cleared at power-up or following a Clear command. The format of the Clear Logic Out command

## **READ/WRITE NVM RESPONSE**

This response message is sent during the next message following a valid Read/Write NVM command to the addressed

#### Table 22. Read/Write NVM Response Format

device. The response format is found in Table 22. The high byte is omitted during the short-word response. No response is generated if the command address field was \$0.

|    | High Byte |    |    |   |   |   |   |   |   |   | Low Byt | 9   |     |     |     | CI | RC |    |    |

|----|-----------|----|----|---|---|---|---|---|---|---|---------|-----|-----|-----|-----|----|----|----|----|

| A3 | A2        | A1 | A0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1       | PA3 | PA2 | PA1 | PA0 | X3 | X2 | X1 | X0 |

slave.

Legend

A[3:0] = Address bits. The slave address.

PA[3:0] = Programmed Address bits. The address that was programmed into the NVM address bits of the slave.

## CLEAR LOGIC OUT COMMAND

The Clear Logic Out command sets the Logic Out pin to a logic low. The compliment to this command is the Set Logic

#### Table 23. Clear Logic Out Command Format

|   | Data |   |   |   |   |   |  | Add | ress |    |    | Com | mand |   |   | CI | RC |    |    |

|---|------|---|---|---|---|---|--|-----|------|----|----|-----|------|---|---|----|----|----|----|

| _ | -    | _ | _ | — | - | _ |  | A3  | A2   | A1 | A0 | 1   | 1    | 0 | 0 | X3 | X2 | X1 | X0 |

is shown in Table 23.

Legend

A[3:0] = Address bits. The address of the selected device.

X[3:0] = Cyclic Redundancy Check (CRC). The CRC as calculated by the master.

generated if the command address field was \$0.

device. The response is shown in Table 24. No response is

## **CLEAR LOGIC OUT RESPONSE**

This response message is sent during the next message following a valid Clear Logic Out command to the addressed

#### Table 24. Clear Logic Out Response Format

|    | High Byte |    |    |   |   |   |   |    |   | Low B | yte |     |     |     |     | С  | RC |    |    |

|----|-----------|----|----|---|---|---|---|----|---|-------|-----|-----|-----|-----|-----|----|----|----|----|

| A3 | A2        | A1 | A0 | 0 | 0 | 0 | 0 | NV | U | LO    | BS  | 103 | 102 | 101 | 100 | X3 | X2 | X1 | X0 |

Legend

A[3:0] = Address bits. The slave address.

BS = Bus Switch Position (1=closed).

LO = Logic out driven level.

IO[3:0] = Values at logic I/Os.

NV = Nonvolatile Memory Write. The value of the NV bit in the slave. U = Undervoltage indicated true by a "1".

X[3:0] = Cyclic Redundancy Check (CRC). The CRC as calculated by the slave.

## SET LOGIC OUT COMMAND

The Set Logic Out command sets the Logic Out pin to a logic high. The compliment to this command is the Clear Logic Out.

## Table 25. Set Logic Out Command Format

|   | Data |   |   |   |   |   |   | Add | ress |    |    | Com | mand |   |   | RC |    |  |    |

|---|------|---|---|---|---|---|---|-----|------|----|----|-----|------|---|---|----|----|--|----|

| - |      | - | - | - | - | - | - | -   | A3   | A2 | A1 | A0  | 1    | 1 | 0 |    | X2 |  | X0 |

shown in Table 25.

Legend

A[3:0] = Address bits. The address of the selected device.

X[3:0] = Cyclic Redundancy Check (CRC). The CRC as calculated by the master.

generated if the command address field was \$0.

device. The response is shown in Table 26. No response is

The Logic Out is cleared at power-up or following a Clear command. The format of the Clear Logic Out command is

## SET LOGIC OUT RESPONSE

This response message is sent during the next message following a valid Set Logic Out command to the addressed

#### Table 26. Set Logic Out Response Format

|    |    |    | High | Byte |   |   |   |    |   |    | Low B | yte |     |     |     |    | С  | RC |    |

|----|----|----|------|------|---|---|---|----|---|----|-------|-----|-----|-----|-----|----|----|----|----|

| A3 | A2 | A1 | A0   | 0    | 0 | 0 | 0 | NV | U | LO | BS    | IO3 | 102 | 101 | 100 | X3 | X2 | X1 | X0 |

Legend

A[3:0] - Address bits. The slave address. BS = Bus Switch Position (1=closed) IO[3:0] = Values at logic I/Os. LO = Logic out driven level. NV = Nonvolatile Memory Write. The value of the NV bit in the slave. U = Undervoltage indicated true by a "1".

X[3:0] = Cyclic Redundancy Check (CRC). The CRC as calculated by the slave.

#### **REVERSE INITIALIZATION**

The Reverse Initialization is similar to the Initialization command and will only work under the condition that it has not already been initialized. The command may be used three ways. The first is to initialize a programmable address device. The second is the first step in assigning a preprogrammed address. The third is to initialize a preprogrammed device.

For the first case this command is sent to address zero with the NV bit set to zero. The command will be received by the next daisy chain device with its bus switch open. Reception of this command will assign the device address and the group number. Reception of this command will also cause the bus switch to close if BS = 1 and no fault is detected. For the second case the Initialization command is sent the same as the first except that the NV bit is set to one. Reception of the command will assign the device address and the group number and cause the bus switch to close if BS = 1 and there are no faults. A Read/Write NVM command then may be sent to complete the setting of a preprogrammed address.

A pre-programmed device must be initialized by putting its address in both PA3:PA0 and A3:A0 fields.

Once a device has received a reverse initialization command, it will ignore further reverse initialization commands or initialization commands unless it has received a Clear command or undergone a power-up reset.

The command format is found in <u>Table 27</u>.

#### Table 27. Reverse Initialization Command Format

|    |    |    | [  | Data |     |     |     |    | Add | ress |    |   | Com | mand |    | C  | RC |    |

|----|----|----|----|------|-----|-----|-----|----|-----|------|----|---|-----|------|----|----|----|----|

| NV | BS | G1 | G0 | PA3  | PA2 | PA1 | PA0 | A3 | A2  | A1   | A0 | 1 | 1   | 1    | X3 | X2 | X1 | X0 |

Legend

A[3:0] = Address bits. These bits are the slave address. For programmable devices these bits are all set to zero. For preprogrammed devices these bits contain the pre-programmed address and must match the PA[3:0] bits.

These bits are not used by this device and should be set to "0". PA[3:0] = Program Address bits. These bits are the address that is

to be stored into the slave's address register.

#### **REVERSE INITIALIZATION RESPONSE**

This response message is sent during the next message following a valid Reverse Initialization command to the addressed device. The response is shown in Table 28. Since

#### Table 28. Reverse Initialization Response Format

NV = Nonvolatile Memory Write. When set to a one, this bit allows a subsequent NVM command to store a nonvolatile address. When set to a zero, NVM programming is disallowed. Once a permanent address has been stored in the device, setting the NV bit to a one has no effect. G[1:0] = Group bits. These bits are the group number for the slave. X[3:0] = Cyclic Redundancy Check (CRC). The CRC as calculated by the master.

> this is a long-word only command, the short-word response is invalid. No response is generated if the command address field was \$0.

|    | High Byte |    |    |   |   |   |    |    |    | Low B | yte |     |     |     |     | С  | RC |    |    |

|----|-----------|----|----|---|---|---|----|----|----|-------|-----|-----|-----|-----|-----|----|----|----|----|

| A3 | A2        | A1 | A0 | 0 | 0 | 0 | BF | NV | BS | G1    | G0  | PA3 | PA2 | PA1 | PA0 | Х3 | X2 | X1 | X0 |

Legend

A[3:0] = Address bits. The slave address.

BF = Bus Fault. BUSIN short to battery detected.

BS = Controls closing of the Bus Switch (1=close).

NV = Nonvolatile Memory Write. The value of the NV bit in the slave. PA[3:0] = Bus Address to set the device to.

X[3:0] = Cyclic Redundancy Check (CRC). The CRC as calculated by the

G[1:0] = Group bits. Not used on this part, will be set to "0". The slave. group number programmed into the slave.

# **TYPICAL APPLICATIONS**

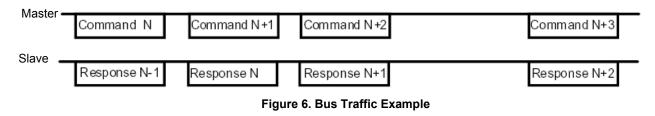

## **COMMUNICATION FORMAT**

DSI messages are composed of individual words separated by a frame delay. Transfers are full duplex. Command messages from the master occur at the same time as responses from the slaves. Slave responses to commands occur during the next command message. This allows slaves time to decode the command, retrieve the information and prepare to send it to the master. A bus traffic example is shown in Figure 6.

The example shows three commands separated by the minimum frame delay followed by a command after a longer delay.

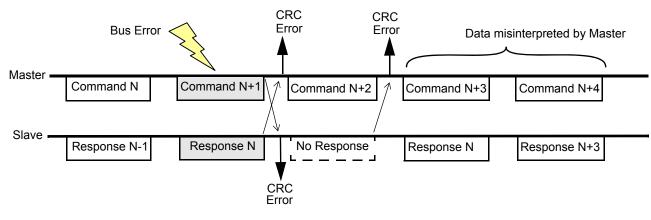

If there is a bus error (due to induced noise or a bus fault), both the master and slave devices will read bad data. The slave reacts to bad data by not sending a response during the next frame. The master will detect a CRC error once it receives the corrupted data sent by the slave, and once again when the slave fails to respond. This is illustrated in Figure 7. When this error occurs, the system software needs to acknowledge this condition and resend a command (any command of same size) so that it can receive the previous response just prior to the bus fault condition (in this case, Command N).

Failure to take corrective action will result in unintended errors as shown in Figure 7. In this case, the master will miss Responses N+1 and N+2 and will mistake them for N+3 and N+4. The master should send another N+1 command after the error is acknowledged to re-synchronize the command-response sequence.

Figure 7. Bus Traffic With Receive Errors (Master Reads Incorrect Data)

## **POWER UP RESET**

When power is first applied to the DSI bus, the system must allow enough time for the internal 5.0 volt regulator of each device to come up to a proper level. This implies that H\_CAP must charge up to  $V_{RECT}$  + 5.0 V, or approximately 6.0 volts. The time this takes is a function of the size of H\_CAP, and the current drive of the Master. The following equation can be used to estimate the minimum time to wait before sending an Initialization Command:

## $t_{MIN} \cong (H\_CAP \ x \ 6V) / I_{CHARGE}$

where  ${\rm I}_{\rm CHARGE}$  is the charging current provided by the DSI Master.

The above assumes a daisy-chain type of bus topology, and enough time must be allowed for all down-stream devices in the chain to charge up. For example, if device #1 has it's switch closed after its Initialization Command, then the system must wait for device #2 to power up before sending its Initialization Command, and so on down the line.

If the devices are attached in a parallel or point-to-point bus configuration, then the total capacitor value is the sum of all H\_CAPS.

In addition to the charge up time, enough time must be allocated for the bus fault test (see next section).

#### **BUS FAULTS**

A bus fault is defined as an external voltage on the "Inactive Side" of the Bus Switch that is greater than 3V (typical). *Inactive* refers to the side of the bus that is not yet connected to the bus. Just before a device is Forward Initialized, the inactive side is defined as BUSOUT. Similarly, just before a device is Reverse Initialized, the BUSIN is defined as the inactive side.

The test for a bus fault is only performed once during Forward or Reverse Initialization (when BS bit is set) by applying an 11 mA pull-down current to the inactive side of the Bus Switch and monitoring the voltage. The fault test takes approximately 200  $\mu$ S. If no fault is detected, the bus switch will be closed, and if a fault is detected, the bus switch will not close. The fault test applies to both programmed and unprogrammed devices.

Exception: In the case of a daisy-chain bus topology where the last device BUSOUT line connects to BUSIN of the first device (loop-back), then the fault test will NOT be executed since both BUSIN and BUSOUT are connected to active busses. It is up to the system software to run the appropriate diagnostic tests to resolve this special case. (One alternative is to use a separate DSI Master to handle the loop-back signal path. This second DSI Master is only activated in the case of a bus fault so that the last device can be accessed by means of a reverse initialization.)

## **GLOBAL ADDRESS 0**

Any time an Initialization or Reverse Initialization command is sent to the 33793 with an address of 0x0 (global address), the device behaves as follows:

- Device initializes to address 0.

- Bus switch remains open. This implies that in a daisychain bus topology, all devices past the first device will remain off.

- · NV and BS bits are not stored and have no effect.

Device will respond to further commands at address 0 (such as setting and clearing the I/O bits and LOGOUT) but there is no response (Master will read all zeros). If the devices are connected in a daisy chain, then only the fist device will respond.

• Subsequent writes to re-initialize the device will not be possible until the device is cleared.

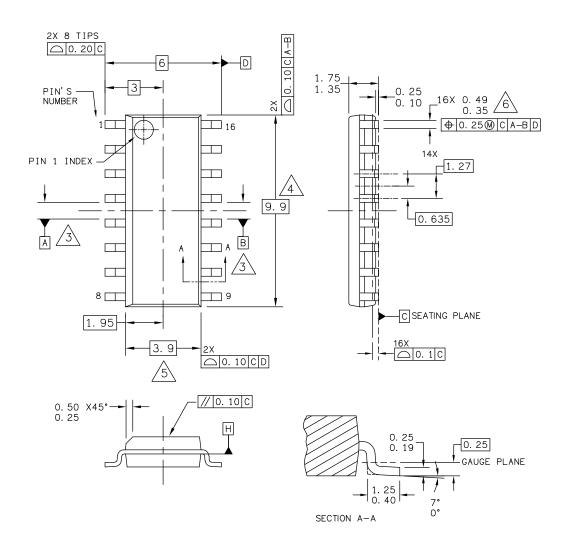

# PACKAGING

## **PACKAGE DIMENSIONS**

For the most current package revision, visit <u>www.freescale.com</u> and perform a keyword search using the "98A" listed below.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA | LOUTLINE     | PRINT VERSION NO | DT TO SCALE |

|---------------------------------------------------------|-----------|--------------|------------------|-------------|

| TITLE:                                                  |           |              | ): 98ASB42566B   | REV: M      |

| 16LD SOIC N/B, 1.<br>CASE-OUTLI                         |           | CASE NUMBER  | R: 751B-05       | 06 FEB 2006 |

| CASE-00TE1                                              |           | STANDARD: JE | EDEC MS-012AC    |             |

EF SUFFIX (PB-FREE) 16-PIN 98ASB42566B ISSUE M

# **REVISION HISTORY**

| Revision | Date    | Description of Changes                                                                                                                                                                                                                                                                                                                                                               |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12.0     | 8/2006  | <ul> <li>Implemented Revision History page</li> <li>Converted to Freescale format</li> <li>Added PC33793EF</li> <li>Added Feature bullets</li> <li>Rewrote and enhanced Device Operation - No electrical changes</li> <li>Updated to the prevailing Freescale form and style</li> <li>Removed PC33793EF and replaced with MCZ33793EF/R2 in the Ordering Information block</li> </ul> |

| 13.0     | 11/2006 | <ul> <li>Added MCZ33793AEF/R2 to the Ordering Information</li> <li>Added Orderable Parts</li> <li>Removed Peak Package Reflow Temperature During Reflow (solder reflow) parameter from Maximum Ratings on page 5. Added note with instructions to obtain this information from www.freescale.com.</li> </ul>                                                                         |

| 14.0     | 5/2010  | <ul> <li>Removed MC33973D references from the document</li> <li>Changed the max limit on the MCZ33793AEF from 12.1 to 12.5 mA on BUSIN +<br/>BUSOUT Response Current</li> <li>Minor format corrections.</li> </ul>                                                                                                                                                                   |

| 15.0     | 2/2014  | No technical changes. Revised back page. Updated document properties. Added SMARTMOS sentence to last paragraph.                                                                                                                                                                                                                                                                     |

#### How to Reach Us:

Home Page: freescale.com

Web Support: freescale.com/support Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document.

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: freescale.com/SalesTermsandConditions.

Freescale and the Freescale logo are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. SMARTMOS is a trademark of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© 2014 Freescale Semiconductor, Inc.

Document Number: MC33793 Rev 15.0 2/2014