### INTEGRATED CIRCUITS

# DATA SHEET

# **PCKV857**

70-190 MHz differential 1:10 clock driver

Product data Supersedes data of 2001 Dec 03 2002 Sep 13

### 70-190 MHz differential 1:10 clock driver

### **PCKV857**

#### **FEATURES**

- ESD classification testing is done to JEDEC Standard JESD22.

Protection exceeds 2000 V to HBM per method A114.

- Latch-up testing is done to JEDEC Standard JESD78 which exceeds 100 mA

- Optimized for clock distribution in DDR (Double Data Rate)

SDRAM applications as per JEDEC specifications

- 1-to-10 differential clock distribution

- Very low skew (< 100 ps) and jitter (< 100 ps)</li>

- Operation from 2.2 V to 2.7 V AV<sub>DD</sub> and 2.3 V to 2.7 V V<sub>DD</sub>

- SSTL\_2 interface clock inputs and outputs

- CMOS control signal input

- Test mode enables buffers while disabling PLL

- Low current power-down mode

- Tolerant of Spread Spectrum input clock

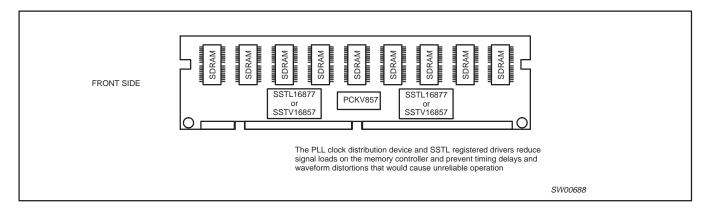

- Full DDR solution provided when used with SSTL16877 or SSTV16857

- Designed for DDR 200 and 266 DIMM applications

- Available in TSSOP-48, TVSOP-48, and VFBGA56 (8 no connects) packages

#### **DESCRIPTION**

The PCKV857 is a high-performance, low-skew, low-jitter zero delay buffer designed for 2.5 V  $\rm V_{DD}$  and 2.5 V  $\rm AV_{DD}$  operation and differential data input and output levels.

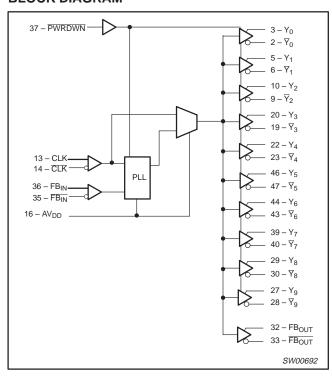

The PCKV857 is a zero delay buffer that distributes a differential clock input pair (CLK,  $\overline{\text{CLK}}$ ) to ten differential pairs of clock outputs (Y[0:9],  $\overline{\text{Y[0:9]}}$ ) and one differential pair feedback clock outputs (FB<sub>OUT</sub>,  $\overline{\text{FB}_{\text{OUT}}}$ ) . The clock outputs are controlled by the clock inputs (CLK,  $\overline{\text{CLK}}$ ), the feedback clocks (FB<sub>IN</sub>,  $\overline{\text{FB}_{\text{IN}}}$ ), and the analog power input (AV<sub>DD</sub>). When  $\overline{\text{PWRDWN}}$  is high, the outputs switch in phase and frequency with CLK. When  $\overline{\text{PWRDWN}}$  is low, all outputs are disabled to high impedance state (3-State), and the PLL is shut down (low power mode). The device also enters the low power mode when the input frequency falls below 20 MHz. An input frequency detection circuit will detect the low frequency condition and after applying a > 20 MHz input signal, the detection circuit turns on the PLL again and enables the outputs.

When  $AV_{DD}$  is grounded, the PLL is turned off and bypassed for test purposes. The PCKV857 is also able to track spread spectrum clocking for reduced EMI.

The PCKV857 is characterized for operation from 0 to +70 °C.

### ORDERING INFORMATION

| PACKAGES                           | TEMPERATURE RANGE | ORDER CODE | DRAWING NUMBER |

|------------------------------------|-------------------|------------|----------------|

| 48-Pin Plastic TSSOP               | 0 to +70 °C       | PCKV857DGG | SOT362-1       |

| 48-Pin Plastic TSSOP (TVSOP)       | 0 to +70 °C       | PCKV857DGV | SOT480-1       |

| 56-ball Plastic VFBGA <sup>1</sup> | 0 to +70 °C       | PCKV857EV  | SOT702-1       |

| NOTE:                              |                   |            |                |

1. 48 balls are connected, 8 balls are no-connects.

#### **PIN CONFIGURATION**

2002 Sep 13 2

### 70-190 MHz differential 1:10 clock driver

PCKV857

### **PIN DESCRIPTION**

| PINS                                                                              | SYMBOL                                                                      | DESCRIPTION                 |

|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------|

| 1, 7, 8, 18, 24, 25, 31, 41, 42, 48                                               | GND                                                                         | SSTL_2 ground pins          |

| 2, 3, 5, 6, 9, 10, 19, 20, 22, 23, 26, 27, 29, 30, 32, 33, 39, 40, 43, 44, 46, 47 | $Y_n, \overline{Y}_n, FB_{OUT}, \overline{FB_{OUT}}$                        | SSTL_2 differential outputs |

| 4, 11, 12, 15, 21, 28, 34, 38, 46                                                 | $V_{DDQ}$                                                                   | SSTL_2 power pins           |

| 13, 14, 35, 36                                                                    | CLK <sub>IN</sub> , CLK <sub>IN</sub> , FB <sub>IN</sub> , FB <sub>IN</sub> | SSTL_2 differential inputs  |

| 16                                                                                | $AV_DD$                                                                     | Analog power                |

| 17                                                                                | AGND                                                                        | Analog ground               |

| 37                                                                                | PWRDWN                                                                      | Power-down control input    |

### **BALL CONFIGURATION**

|   | 1                      | 2                | 3               | 4               | 5                 | 6                 |

|---|------------------------|------------------|-----------------|-----------------|-------------------|-------------------|

| A | GND                    | NC               | NC              | NC              | NC                | GND               |

| В | Y <sub>0</sub>         | ₹0               | V <sub>DD</sub> | V <sub>DD</sub> | $\nabla_5$        | Y <sub>5</sub>    |

| С | $\overline{Y}_1$       | Y <sub>1</sub>   | GND             | GND             | Y <sub>6</sub>    | ₹6                |

| D | $\overline{\forall}_2$ | GND              | Y <sub>2</sub>  | Y <sub>7</sub>  | GND               | ₹7                |

| E | $V_{DD}$               | $V_{DD}$         |                 |                 | $V_{DD}$          | PWRDWN            |

| F | CLK                    | CLK              |                 |                 | FB <sub>IN</sub>  | FB <sub>IN</sub>  |

| G | AV <sub>DD</sub>       | AGND             | V <sub>DD</sub> | $V_{DD}$        | FB <sub>OUT</sub> | FB <sub>OUT</sub> |

| н | $\overline{Y}_3$       | Y <sub>3</sub>   | GND             | GND             | Y <sub>8</sub>    | ₹8                |

| J | Y <sub>4</sub>         | $\overline{Y}_4$ | V <sub>DD</sub> | V <sub>DD</sub> | $\nabla_9$        | Y <sub>9</sub>    |

| к | GND                    | NC               | NC              | NC              | NC                | GND               |

SW00951

### 70-190 MHz differential 1:10 clock driver

PCKV857

#### **FUNCTION TABLE**

|                | INPUTS   |          |                | OUTI           | PUTS              |                   | PLL ON/OFF |  |

|----------------|----------|----------|----------------|----------------|-------------------|-------------------|------------|--|

| PWRDWN         | CLK      | CLK      | Y <sub>n</sub> | ₹ <sub>n</sub> | FB <sub>OUT</sub> | FB <sub>OUT</sub> | PLL ON/OFF |  |

| L              | L        | Н        | Z              | Z              | Z <sup>1</sup>    | Z <sup>1</sup>    | OFF        |  |

| L              | Н        | L        | Z              | Z              | Z <sup>1</sup>    | Z <sup>1</sup>    | OFF        |  |

| Н              | L        | Н        | L              | Н              | L                 | Н                 | ON         |  |

| Н              | Н        | L        | Н              | L              | Н                 | L                 | ON         |  |

| X <sup>2</sup> | < 20 MHz | < 20 MHz | Z              | Z              | $Z^1$             | Z <sup>1</sup>    | OFF        |  |

#### NOTES:

H = HIGH voltage level L = LOW voltage level

Z = high impedance OFF-state

X = don't care

Subject to change. May cause conflict with FB<sub>IN</sub> pins.

Additional feature that senses when the clock input is less than 20 MHz and places the part in sleep mode.

### **BLOCK DIAGRAM**

### 70-190 MHz differential 1:10 clock driver

PCKV857

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| SYMBOL           | PARAMETER                                     | CONDITION                    | LIM  | IITS                   | UNIT |

|------------------|-----------------------------------------------|------------------------------|------|------------------------|------|

| STINIBUL         | PARAIVIETER                                   | CONDITION                    | MIN  | MAX                    | UNIT |

| $V_{DDQ}$        | Supply voltage range                          |                              | 0.5  | 3.6                    | V    |

| AV <sub>DD</sub> | Supply voltage range                          |                              | 0.5  | 3.6                    | V    |

| VI               | Input voltage range                           | see Notes 2 and 3            | -0.5 | V <sub>DDQ</sub> + 0.5 | V    |

| Vo               | Output voltage range                          | see Notes 2 and 3            | -0.5 | V <sub>DDQ</sub> + 0.5 | V    |

| I <sub>IK</sub>  | Input clamp current                           | $V_I < 0$ or $V_I > V_{DDQ}$ | _    | ±50                    | mA   |

| I <sub>OK</sub>  | Output clamp current                          | $V_O < 0$ or $V_O > V_{DDQ}$ | _    | ±50                    | mA   |

| I <sub>O</sub>   | Continuous output current                     | $V_O = 0$ to $V_{DDQ}$       | _    | ±50                    | mA   |

|                  | Continuous current to GND or V <sub>DDQ</sub> |                              | _    | ±100                   | mA   |

| T <sub>stg</sub> | Storage temperature range                     |                              | -65  | +150                   | °C   |

#### NOTES:

2. The input and output negative voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

### RECOMMENDED OPERATING CONDITIONS<sup>1</sup>

| SYMBOL           | DADAMETED                                              |                                                  | CONDITION |                            | LIMITS              |                            | UNIT |

|------------------|--------------------------------------------------------|--------------------------------------------------|-----------|----------------------------|---------------------|----------------------------|------|

| STWIBUL          | PARAMETER                                              |                                                  | CONDITION | MIN                        | TYP                 | MAX                        | UNIT |

| $V_{DDQ}$        | Supply voltage range                                   |                                                  |           | 2.3                        | _                   | 2.7                        | V    |

| $AV_{DD}$        | Supply voltage range                                   |                                                  |           | 2.2                        | _                   | 2.7                        | V    |

| V <sub>IL</sub>  | Low level input voltage                                | CLK, CLK,<br>FB <sub>IN</sub> , FB <sub>IN</sub> |           | _                          | _                   | V <sub>DDQ</sub> /2 - 0.18 | V    |

|                  |                                                        | PWRDWN                                           |           | -0.3                       | _                   | 0.7                        |      |

| V <sub>IH</sub>  | High level input voltage  CLK, Cl FB <sub>IN</sub> , F |                                                  |           | V <sub>DDQ</sub> /2 + 0.18 | _                   | _                          | V    |

|                  |                                                        | PWRDWN                                           |           | 1.7                        | _                   | $V_{DDQ} + 0.3$            |      |

|                  | DC input signal voltage                                |                                                  | Note 2    | -0.3                       | _                   | $V_{DDQ}$                  | V    |

| V <sub>ID</sub>  | DC differential input signal voltage                   | CLK, FB <sub>IN</sub>                            | Note 3    | 0.36                       | _                   | V <sub>DDQ</sub> + 0.6     | V    |

| VID              | AC differential input signal voltage                   | CLK, FB <sub>IN</sub>                            | Note 3    | 0.7                        | _                   | V <sub>DDQ</sub> + 0.6     | V    |

| V <sub>OX</sub>  | Output differential cross-voltage                      |                                                  | Note 4    | $V_{DDQ}/2 - 0.2$          | V <sub>DDQ</sub> /2 | $V_{DDQ}/2 + 0.2$          | V    |

| V <sub>IX</sub>  | Input differential cross-voltage                       |                                                  | Note 4    | V <sub>DDQ</sub> /2 - 0.2  | _                   | $V_{DDQ}/2 + 0.2$          | V    |

| I <sub>OH</sub>  | High-level output current                              |                                                  |           | _                          | _                   | -12                        | mA   |

| I <sub>OL</sub>  | Low-level output current                               |                                                  |           | _                          | _                   | 12                         | mA   |

| SR               | Input slew rate                                        |                                                  |           | 1                          | _                   | 4                          | V/ns |

| T <sub>amb</sub> | Operating free-air temperature                         |                                                  |           | 0                          | _                   | 70                         | °C   |

#### NOTES

- 1. Unused inputs must be held high or low to prevent them from floating.

- 2. DC input signal voltage specifies the allowable DC execution of differential input.

- 3. Differential input signal voltage specifies the differential voltage |VTR VCP| required for switching, where VTR is the true input level and VCP is the complementary input level.

- 4. Differential cross-point voltage is expected to track variations of V<sub>CC</sub> and is the voltage at which the differential signals must be crossing.

5

2002 Sep 13

Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings

only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating

conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>3.</sup> This value is limited to 3.6 V maximum.

### 70-190 MHz differential 1:10 clock driver

PCKV857

#### DC ELECTRICAL CHARACTERISTICS

Over recommended operating conditions. Voltages are referenced to GND (ground = 0 V).

| SYMBOL            | PARAMETER                                                 | TEST CONDITIONS                                                                    |                        | LIMITS |      | UNIT |

|-------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------|------------------------|--------|------|------|

| STWIBUL           | PARAMETER                                                 | TEST CONDITIONS                                                                    | MIN                    | TYP    | MAX  | UNII |

| V <sub>IK</sub>   | Input voltage, all inputs                                 | $V_{DDQ} = 2.3 \text{ V}, I_{I} = -18 \text{ mA}$                                  | _                      | _      | -1.2 | V    |

| V                 | High lovel output voltege                                 | $V_{DDQ} = min to max, I_{OH} = -1 mA$                                             | V <sub>DDQ</sub> – 0.1 | _      | _    | V    |

| V <sub>OH</sub>   | High-level output voltage                                 | $V_{DDQ} = 2.3 \text{ V}, I_{OH} = -12 \text{ mA}$                                 | 1.7                    |        | _    | V    |

| V                 | Low-level output voltage                                  | $V_{DDQ}$ = min to max, $I_{OL}$ = 1 mA                                            | _                      | _      | 0.1  | V    |

| V <sub>OL</sub>   | $V_{DDQ} = 2.3 \text{ V}, I_{OL} = 12 \text{ mA}$         |                                                                                    | _                      | _      | 0.6  | V    |

| I <sub>I</sub>    | Input current                                             | $V_{DDQ} = 2.7 \text{ V}, V_{I} = 0 \text{ V to } 2.7 \text{ V}$                   | _                      |        | ±10  | μΑ   |

| I <sub>OZ</sub>   | High-impedance-state output current                       | $V_{DDQ} = 2.7 \text{ V}, V_{O} = V_{DDQ} \text{ or GND}$                          | _                      |        | ±10  | μΑ   |

| I <sub>DDPD</sub> | Power-down current on V <sub>DDQ</sub> + AV <sub>DD</sub> | CLK and CLK = 0 MHz,<br>PWRDWN = low;<br>Σ of I <sub>DD</sub> and AI <sub>DD</sub> | _                      | 30     | 100  | μА   |

| I <sub>DD</sub>   | Dynamic current on V <sub>DDQ</sub>                       | f <sub>O</sub> = 67 MHz to 190 MHz                                                 | _                      | 200    | 300  | mA   |

| Al <sub>DD</sub>  | Supply current on AV <sub>DD</sub>                        | f <sub>O</sub> = 67 MHz to 190 MHz                                                 | _                      | 8      | 10   | mA   |

| C <sub>I</sub>    | Input capacitance                                         | $V_{CC} = 2.5 \text{ V}, V_I = V_{CC} \text{ or GND}$                              | 2                      | 2.8    | 3    | pF   |

#### NOTE:

- This is intended to operate in the SSTL\_2 type IV unterminated mode without series resistors on the outputs.

All typical values are at respective nominal V<sub>DDQ</sub>.

- 3. Differential cross-point voltage is expected to track variations of V<sub>DDQ</sub> and is the voltage at which the differential signals must be crossing.

#### **TIMING REQUIREMENTS**

Over recommended ranges of supply voltage and operating free-air temperature.

| SYMBOL          | PARAMETER                       | MIN | MAX | UNIT |

|-----------------|---------------------------------|-----|-----|------|

| f <sub>CK</sub> | Operating clock frequency       | 60  | 190 | MHz  |

|                 | Input clock duty cycle          | 40  | 60  | %    |

|                 | Stabilization time <sup>1</sup> | 100 | _   | μs   |

6

### NOTE:

1. Time required for the integrated PLL circuit to obtain phase lock of its feedback signal to its reference signal after power-up.

2002 Sep 13

### 70-190 MHz differential 1:10 clock driver

PCKV857

### **AC CHARACTERISTICS**

GND = 0 V;  $t_{f}$  =  $t_{f}$   $\leq$  2.5 ns;  $C_{L}$  = 50 pF;  $R_{L}$  = 1  $k\Omega$

| SYMBOL                | PARAMETER                           | WAVEFORM | CONDITION                                  |                 | LIMITS |     | UNIT |

|-----------------------|-------------------------------------|----------|--------------------------------------------|-----------------|--------|-----|------|

| STWBOL                | PARAMETER                           | WAVEFORM | CONDITION                                  | MIN             | TYP    | MAX | UNII |

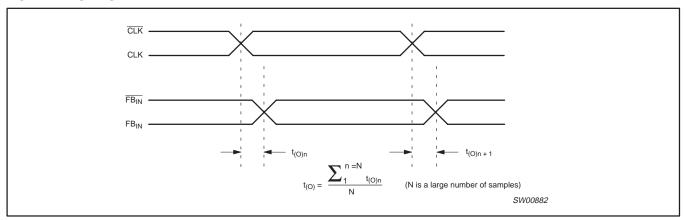

| t <sub>(O)</sub>      | Static phase offset                 | Figure 1 |                                            | -150            | 0      | 150 | ps   |

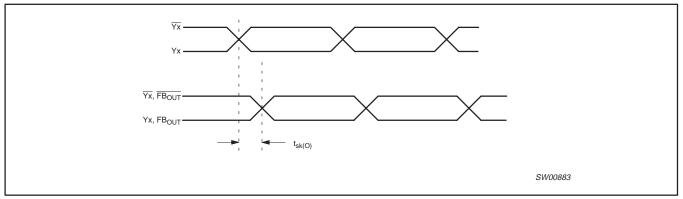

| t <sub>SK(O)</sub>    | Output clock skew                   | Figure 2 |                                            | _               | _      | 75  | ps   |

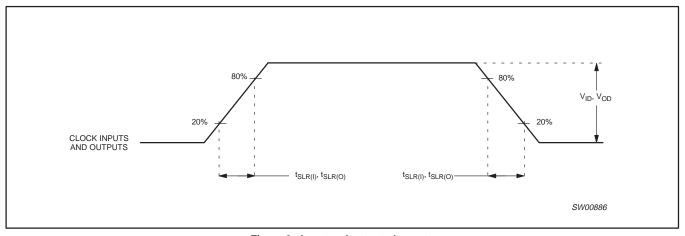

| t <sub>SLR(O)</sub>   | Output clock skew rate              | Figure 3 |                                            | 1               | _      | 2   | V/ns |

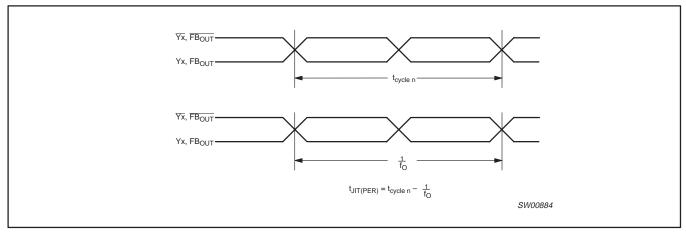

| t <sub>JIT(PER)</sub> | Jitter (period)                     | Figure 4 | $f_O = 67 \text{ MHz to } 200 \text{ MHz}$ | <del>-</del> 75 | _      | 75  | ps   |

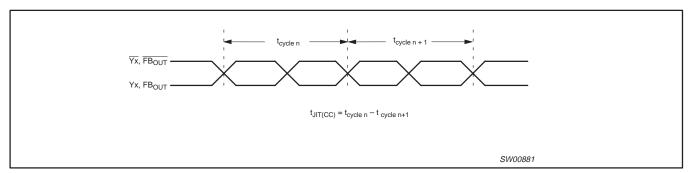

| t <sub>JIT(CC)</sub>  | Jitter (cycle-to-cycle)             | Figure 5 | $f_O = 67 \text{ MHz to } 200 \text{ MHz}$ | <del>-</del> 75 | _      | 75  | ps   |

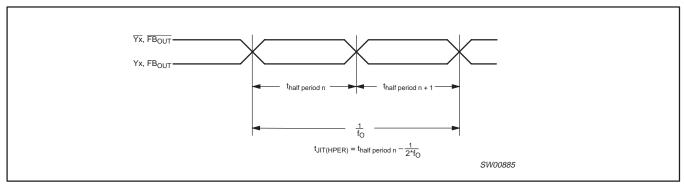

| tJIT(HPER)            | Half-period jitter                  | Figure 6 |                                            | -100            | _      | 100 | ps   |

| t <sub>PLH</sub> 1    | Low to high level propagation delay |          | Test mode/CLK to any output                | _               | 3.7    | _   | ns   |

| t <sub>PHL</sub> 1    | High to low level propagation delay |          | Test mode/CLK to any output                | _               | 3.7    | _   | ns   |

#### NOTE:

1. Refers to transition of noninverting output.

### 70-190 MHz differential 1:10 clock driver

PCKV857

### **AC WAVEFORMS**

Figure 1. Static phase offset

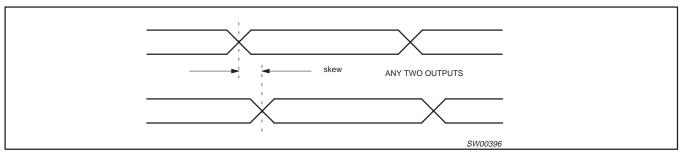

Figure 2. Output skew

Figure 3. Input and output slew rates

### 70-190 MHz differential 1:10 clock driver

PCKV857

Figure 4. Period jitter

Figure 5. Cycle-to-cycle jitter

Figure 6. Half-period jitter

Figure 7. Skew between any two outputs.

### 70-190 MHz differential 1:10 clock driver

PCKV857

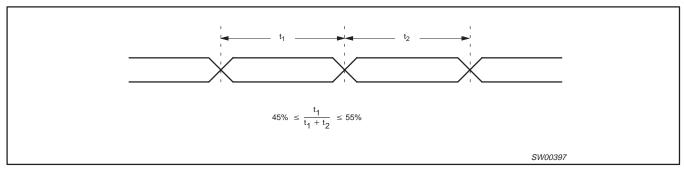

Figure 8. Duty cycle limits and measurement

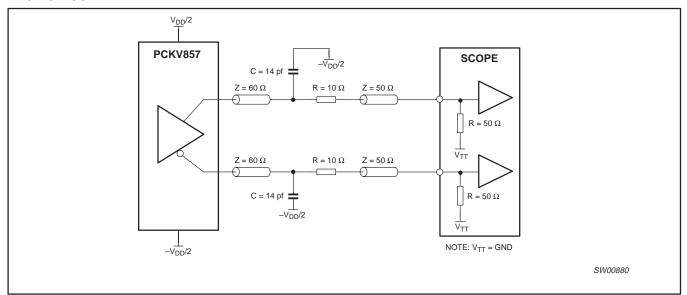

### **TEST CIRCUIT**

Figure 9. Output load test circuit

10

### 70-190 MHz differential 1:10 clock driver

PCKV857

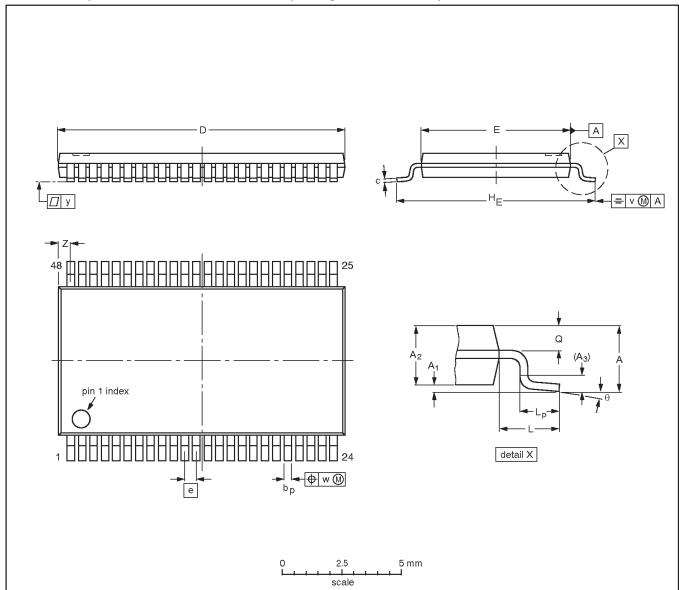

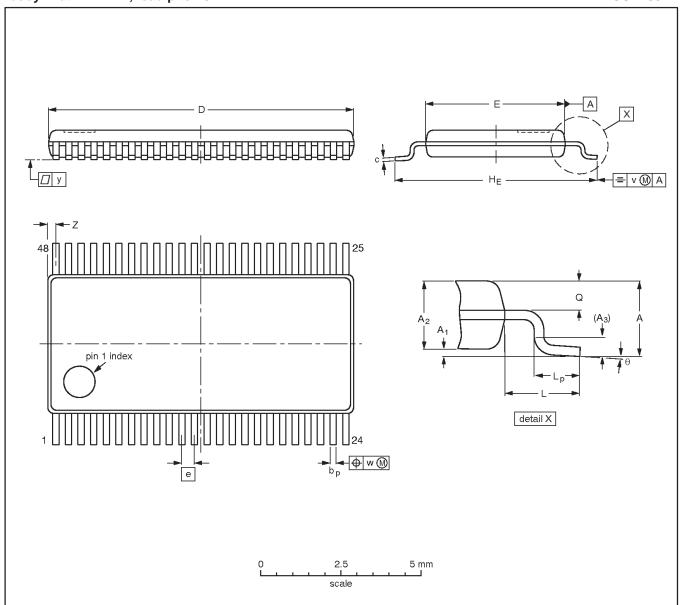

### TSSOP48: plastic thin shrink small outline package; 48 leads; body width 6.1 mm

SOT362-1

### DIMENSIONS (mm are the original dimensions).

| UNIT | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | А3   | bp           | С          | D <sup>(1)</sup> | E <sup>(2)</sup> | е   | HE         | L | Lp         | Q            | ٧    | w    | у   | Z          | θ        |

|------|-----------|----------------|----------------|------|--------------|------------|------------------|------------------|-----|------------|---|------------|--------------|------|------|-----|------------|----------|

| mm   | 1.2       | 0.15<br>0.05   | 1.05<br>0.85   | 0.25 | 0.28<br>0.17 | 0.2<br>0.1 | 12.6<br>12.4     | 6.2<br>6.0       | 0.5 | 8.3<br>7.9 | 1 | 0.8<br>0.4 | 0.50<br>0.35 | 0.25 | 0.08 | 0.1 | 0.8<br>0.4 | 8°<br>0° |

#### Notes

- 1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

- 2. Plastic interlead protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  |     | REFER  | RENCES |  | EUROPEAN   | ISSUE DATE                        |

|----------|-----|--------|--------|--|------------|-----------------------------------|

| VERSION  | IEC | JEDEC  | EIAJ   |  | PROJECTION | ISSUE DATE                        |

| SOT362-1 |     | MO-153 |        |  |            | <del>-95-02-10-</del><br>99-12-27 |

### 70-190 MHz differential 1:10 clock driver

PCKV857

TSSOP48: plastic thin shrink small outline package; 48 leads; body width 4.4 mm; lead pitch 0.4 mm

SOT480-1

### DIMENSIONS (mm are the original dimensions)

| UNIT | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | A <sub>3</sub> | ь <sub>р</sub> | С            | D (1)        | E <sup>(2)</sup> | е    | HE           | L    | Lp           | Q            | v    | w    | у    | Z <sup>(1)</sup> | θ        |

|------|-----------|----------------|----------------|----------------|----------------|--------------|--------------|------------------|------|--------------|------|--------------|--------------|------|------|------|------------------|----------|

| mm   | 1.10      | 0.15<br>0.05   | 0.95<br>0.85   | 0.25           | 0.23<br>0.13   | 0.20<br>0.09 | 9.80<br>9.60 | 4.50<br>4.30     | 0.40 | 6.60<br>6.20 | 1.00 | 0.70<br>0.50 | 0.40<br>0.30 | 0.20 | 0.07 | 0.08 | 0.40<br>0.10     | 8°<br>0° |

#### Notes

- 1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

- 2. Plastic interlead protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  | REFERENCES |        |      |  | EUROPEAN   | ISSUE DATE                       |

|----------|------------|--------|------|--|------------|----------------------------------|

| VERSION  | IEC        | JEDEC  | EIAJ |  | PROJECTION | 1330E DATE                       |

| SOT480-1 |            | MO-153 |      |  |            | <del>97-03-20-</del><br>99-12-27 |

12

### 70-190 MHz differential 1:10 clock driver

PCKV857

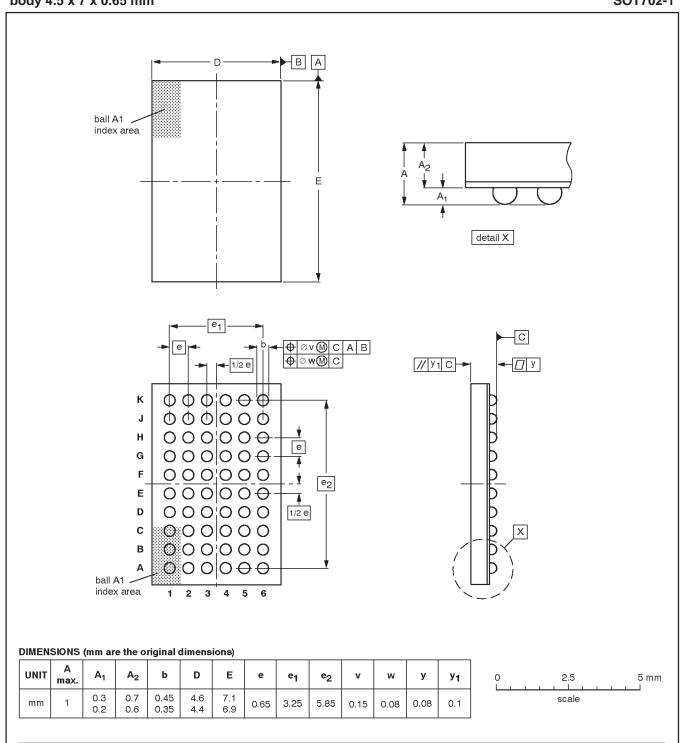

VFBGA56: plastic very thin fine-pitch ball grid array package; 56 balls; body  $4.5\ x\ 7\ x\ 0.65\ mm$

SOT702-1

| OUTLINE<br>VERSION | REFERENCES |        |       |  | EUROPEAN   | ISSUE DATE                       |

|--------------------|------------|--------|-------|--|------------|----------------------------------|

|                    | IEC        | JEDEC  | JEITA |  | PROJECTION | ISSUE DATE                       |

| SOT702-1           |            | MO-225 |       |  |            | <del>-01-06-25</del><br>02-08-08 |

|                    |            |        |       |  |            |                                  |

## 70-190 MHz differential 1:10 clock driver

PCKV857

### **REVISION HISTORY**

| Rev | Date        | Description                                                                                                                                                                                                              |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| _4  | 2002 Sep 06 | Product data (9397 750 10343); fourth version supersedes Product data 2001 Dec 03. Engineering Change Notice 853-2242 28874 (2002 Sep 09). Modifications: Add new package option (VFBGA) to existing product data sheet. |

| _3  | 2001 Dec 03 | Product data (9397 750 09244); third version                                                                                                                                                                             |

### 70-190 MHz differential 1:10 clock driver

PCKV857

#### Data sheet status

| Data sheet status <sup>[1]</sup> | Product<br>status <sup>[2]</sup> | Definitions                                                                                                                                                                                                                                                                                                            |

|----------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective data                   | Development                      | This data sheet contains data from the objective specification for product development.  Philips Semiconductors reserves the right to change the specification in any manner without notice.                                                                                                                           |

| Preliminary data                 | Qualification                    | This data sheet contains data from the preliminary specification. Supplementary data will be published at a later date. Philips Semiconductors reserves the right to change the specification without notice, in order to improve the design and supply the best possible product.                                     |

| Product data                     | Production                       | This data sheet contains data from the product specification. Philips Semiconductors reserves the right to make changes at any time in order to improve the design, manufacturing and supply. Changes will be communicated according to the Customer Product/Process Change Notification (CPCN) procedure SNW-SQ-650A. |

<sup>[1]</sup> Please consult the most recently issued datasheet before initiating or completing a design.

#### **Definitions**

**Short-form specification** — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

**Limiting values definition** — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

**Application information** — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### **Disclaimers**

Life support — These products are not designed for use in life support appliances, devices or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

Philips Semiconductors 811 East Arques Avenue P.O. Box 3409 Sunnyvale, California 94088–3409 Telephone 800-234-7381 © Copyright Philips Electronics North America Corporation 2002 All rights reserved. Printed in U.S.A.

Date of release: 09-02

Document order number: 9397 750 10343

Let's make things better.

Philips Semiconductors

<sup>[2]</sup> The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at URL http://www.semiconductors.philips.com.