# CX24109 Digital Satellite Tuner Rev. 01 — 13 November 2008

**Product data sheet**

# **Document information**

| Info     | Content |

|----------|---------|

| Keywords |         |

| Abstract |         |

# **Digital Satellite Tuner**

# **Ordering information**

| Type number | Description             | Package      |

|-------------|-------------------------|--------------|

| CX24109-11  | Digital Satellite Tuner | 48-pin eTQFP |

| CX24109-11Z |                         |              |

# **Revision history**

| Revision | Date     | Description                                                 |

|----------|----------|-------------------------------------------------------------|

| 01       | 20081113 | First NXP version based on the Conexant 102031A data sheet. |

# **Contact information**

For more information, please visit: <a href="http://www.nxp.com">http://www.nxp.com</a>

For sales office addresses, please send an email to: <a href="mailto:salesaddresses@nxp.com">salesaddresses@nxp.com</a>

CX24109\_N\_1

© NXP B.V. 2008. All rights reserved.

CX24109 **NXP Semiconductors Digital Satellite Tuner**

# **General description**

The CX24109 is a highly integrated, direct down-conversion satellite tuner intended for high-volume digital video, audio, and data receivers. When combined with the CX24121 QPSK demodulator/FEC decoder, the chip set provides a complete broadband satellite front-end solution capable of operating from 1-45 MSps in the most demanding satellite environments. It is compatible with international standards such as DVB and DSS. The highly integrated CX24109 reduces the tuner BOM cost and simplifies the RF layout.

## **Features**

- Zero-IF architecture eliminates the need for image reject filtering

- Integrated LNA

- Integrated LO with onboard VCO and synthesizer

- Single +5 V supply

- Reference oscillator output for demodulator

# **Applications**

- DBS set-top boxes

- Commercial digital video, audio, and data receivers

- Digital VCRs

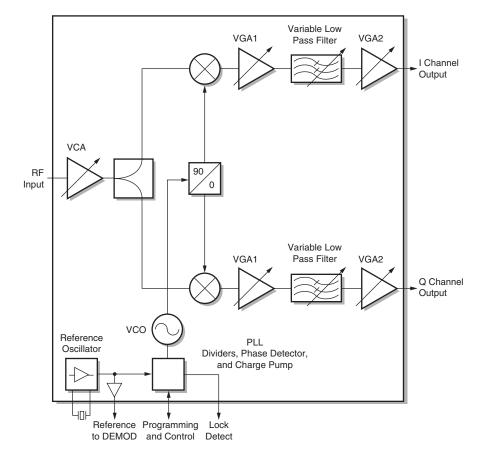

# **Block diagram**

3

Digital Satellite Tuner

4

CX24109

Digital Satellite Tuner

# **NXP Semiconductors**

# **Contents**

| Conter  | its                                | 5    |

|---------|------------------------------------|------|

| Figures | 8                                  | 7    |

| Tables  |                                    | 9    |

| 1       | Functional Description             | . 11 |

| 1.1     | Pinout Information                 | . 11 |

| 1.2     | Pin Description                    |      |

| 1.3     | Application Overview               |      |

| 1.4     | Signal Path                        | . 13 |

| 1.5     | AGC and Control                    | . 15 |

| 1.6     | Local Oscillator                   | . 15 |

| 1.7     | Programming Interface              | . 15 |

| 1.7.1   | Gain Equations                     | . 21 |

| 1.7.2   | Frequency Equations                | . 22 |

| 1.7.3   | Recommended Default Values         | . 22 |

| 2       | Applications                       | . 23 |

| 2.1     | AGC Input                          | . 23 |

| 2.2     | VCO Power Pin Ripple Requirement   | . 23 |

| 2.3     | Transmission Lines                 | . 23 |

| 2.4     | Example Schematic                  | . 23 |

| 2.5     | Typical Performance Curves         | . 26 |

| 3       | Parametric Data and Specifications | . 31 |

| 3.1     | Electrical Specifications          | . 31 |

| 3.1.1   | Standard Operating Conditions      | . 31 |

| 3.2     | Mechanical Specifications          |      |

| Legal i | nformation                         | . 39 |

Digital Satellite Tuner

CX24109

# **NXP Semiconductors**

# Digital Satellite Tuner

7

# **Figures**

| Fig. 1  | CX24109 Pin Diagram                                    | 11 |

|---------|--------------------------------------------------------|----|

| Fig. 2  | QPSK Demodulation Typical Application Block Diagram    | 13 |

| Fig. 3  | Detailed Functional Block Diagram                      | 14 |

| Fig. 4  | Serial Interface Programming Example                   | 16 |

| Fig. 5  | Programming Word Configuration                         | 16 |

| Fig. 6  | Simplified Application Schematic (Page 1 of 2)         | 24 |

| Fig. 7  | Simplified Application Schematic (Page 2 of 2)         | 25 |

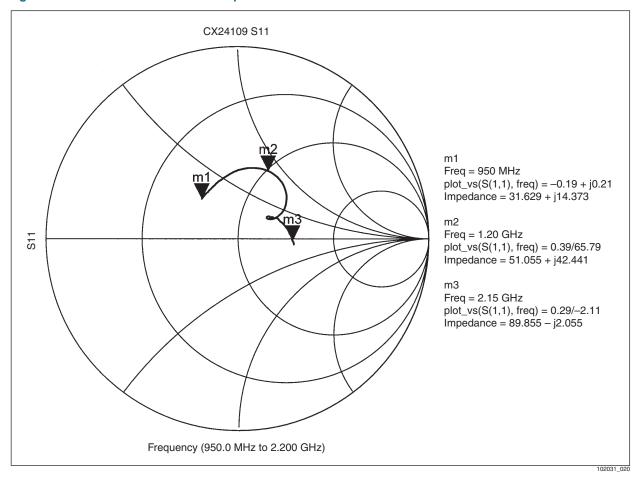

| Fig. 8  | Reflection Coefficient at Input of CX24109             | 26 |

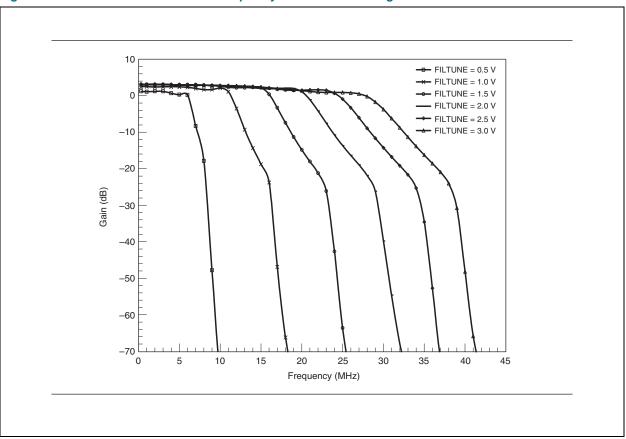

| Fig. 9  | Baseband Filter Gain vs. Frequency and FILTUNE Voltage | 27 |

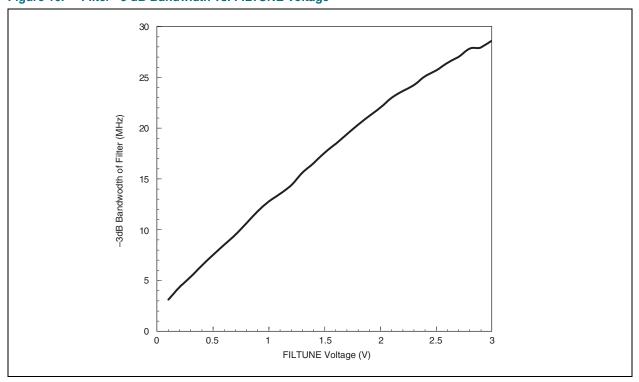

| Fig. 10 | Filter –3 dB Bandwidth vs. FILTUNE Voltage             | 27 |

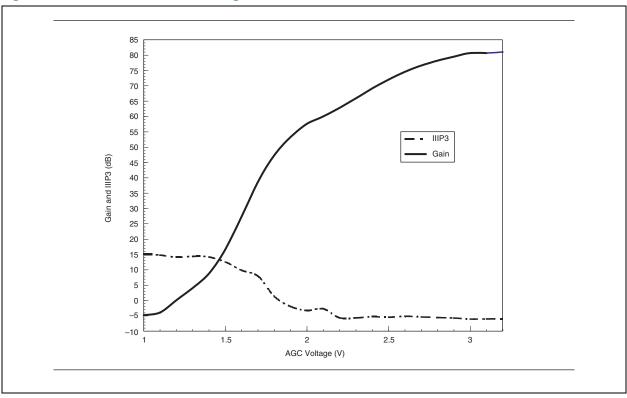

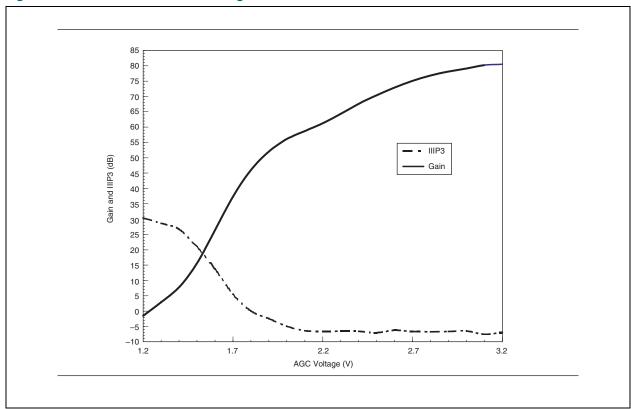

| Fig. 11 | Gain and IIP3 vs. AGC Voltage at 950 MHz               | 28 |

| Fig. 12 | Gain and IIP3 vs. AGC Voltage at 2150 MHz              | 28 |

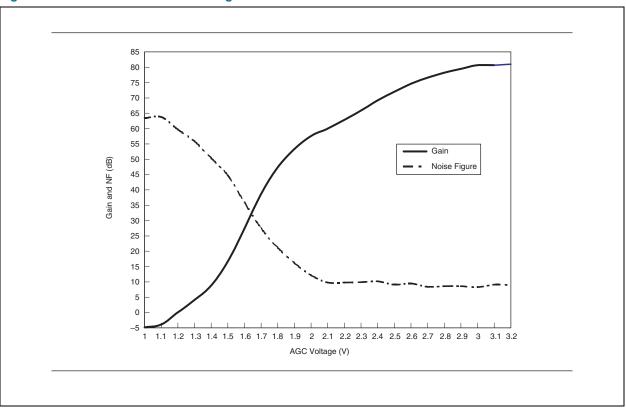

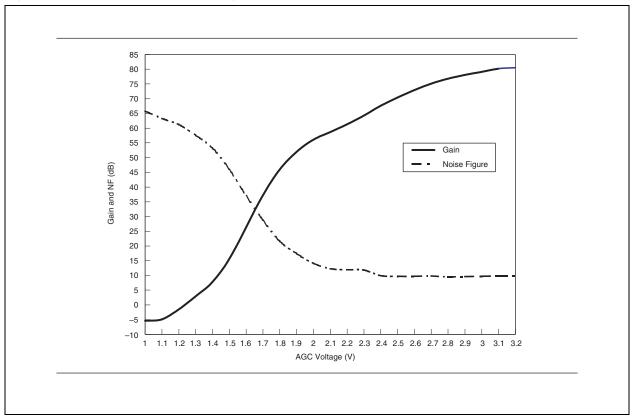

| Fig. 13 | Gain and NF vs. AGC Voltage at 950 MHz                 | 29 |

| Fig. 14 | Gain and NF vs. AGC Voltage at 2150 MHz                | 29 |

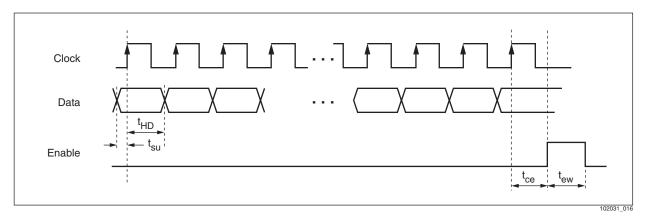

| Fig. 15 | Serial Programming Example                             | 33 |

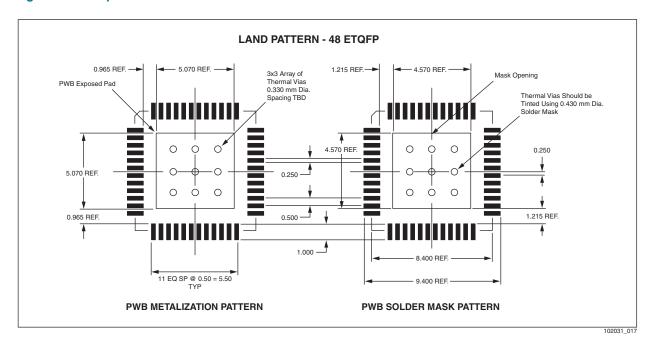

| Fig. 16 | 48-pin eTQFP Land Pattern                              | 36 |

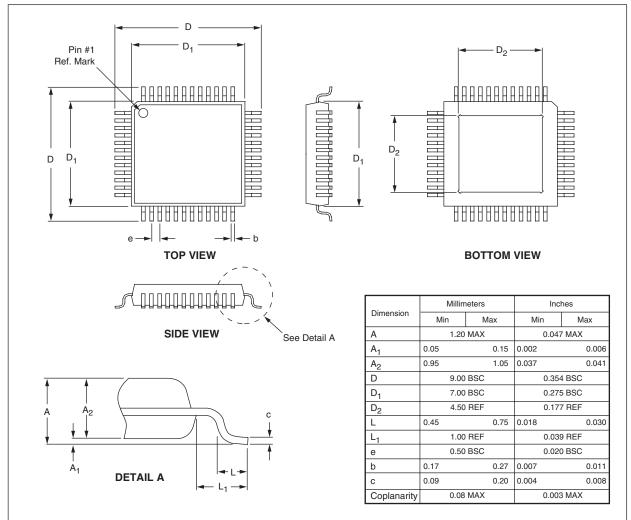

| Fig. 17 | 48-pin eTQFP Package Diagram                           | 37 |

|         |                                                        |    |

Digital Satellite Tuner

# Digital Satellite Tuner

# **Tables**

| Table 1.  | Pin Description                                               | . 11 |

|-----------|---------------------------------------------------------------|------|

| Table 2.  | Power Supply and Ground Pins                                  | 12   |

| Table 3.  | Programming Bit Mapping                                       |      |

| Table 4.  | Band Select Programming                                       | 18   |

| Table 5.  | VGA Programming                                               | 19   |

| Table 6.  | VCA Programming                                               |      |

| Table 7.  | PLL Programming                                               | 21   |

| Table 8.  | Recommended AGC Programming Values                            | 22   |

| Table 9.  | Recommended VCO Frequency vs. Charge Pump Current             | 22   |

| Table 10. | Recommended Charge Pump Polarity and Reference Divider Values | 22   |

| Table 11. | Absolute Maximum Ratings                                      |      |

| Table 12. | Operating Conditions                                          | 31   |

| Table 13. | DC Electrical Characteristics                                 | 32   |

| Table 14. | AC Electrical Characteristics                                 |      |

| Table 15. | RF Electrical Characteristics                                 | 33   |

| Table 16. | Baseband Frequency Response                                   | 36   |

|           |                                                               |      |

Digital Satellite Tuner

# CX24109

# **Chapter 1: Functional Description**

Rev. 01 — 13 November 2008

Product data sheet

11

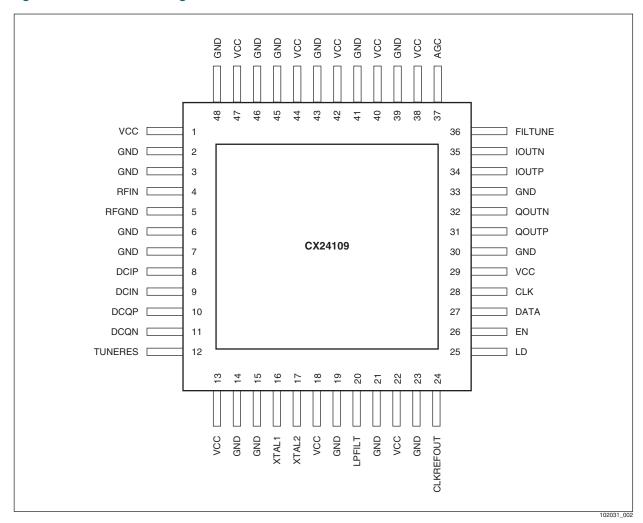

### 1.1 **Pinout Information**

CX24109 Pin Diagram Figure 1.

### 1.2 **Pin Description**

Table 1. **Pin Description**

**Product data sheet**

Downloaded from Arrow.com.

|          | •       |     |                                                                                                                                                                                                           |

|----------|---------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name | Pin No. | I/O | Description                                                                                                                                                                                               |

| RFIN     | 4       | I   | RF input signal pin.                                                                                                                                                                                      |

| AGC      | 37      | I   | AGC control input from the demodulator/FEC IC. It controls the gain of the RF attenuator and both baseband amplifiers. Minimum gain occurs at minimum voltage. Input impedance zin = 1 M $\Omega$ //20 pF |

| FILTUNE  | 36      | I   | Baseband filter control input from the demodulator/FEC IC. Minimum BW occurs at minimum voltage. Zin = 17 k $\Omega$ //20 pF.                                                                             |

CX24109\_N\_1 © NXP B.V. 2008. All rights reserved. Rev. 01 — 13 November 2008

# **Chapter 1: Functional Description**

Table 1. Pin Description

| Pin Name     | Pin No. | I/O | Description                                                                                                                                                                                                                                |

|--------------|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TUNERES      | 12      | _   | Filter reference. A resistor to ground from this pin sets the reference current for the tunable filter. See Figure 6 and Figure 7.                                                                                                         |

| IOUTP, IOUTN | 34, 35  | 0   | I channel output to the demodulator/FEC IC. Can be used balanced or single-ended. Zout = 1 k $\Omega$ //10 pF.                                                                                                                             |

| QOUTP, QOUTN | 31, 32  | 0   | Q channel output to the demodulator/FEC IC. Can be used balanced or single-ended. Zout = 1 k $\Omega$ //10 pF.                                                                                                                             |

| DCIP, DCIN   | 8, 9    | _   | I channel DC offset cancellation. A capacitor must be placed between these pins. See <a href="Figure 6">Figure 6</a> and <a href="Figure 7">Figure 7</a> .                                                                                 |

| DCQP, DCQN   | 10, 11  | _   | Q channel DC offset cancellation. A capacitor must be placed between these pins. See <u>Figure 6</u> and <u>Figure 7</u> .                                                                                                                 |

| LPFILT       | 20      | _   | Loop filter. A network with a capacitor in parallel with a series resistor and capacitor connected from this pin to ground determines the loop filter bandwidth. See <a href="Figure 6">Figure 6</a> and <a href="Figure 7">Figure 7</a> . |

| CLKREFOUT    | 24      | 0   | Clock reference output. This pin provides the reference clock for the demodulator/FEC IC. The maximum load allowed at this node is $Z_{LOAD}$ = 10 k $\Omega$ //20 pF.                                                                     |

| XTAL1, XTAL2 | 16, 17  | _   | Crystal inputs. A 10.111 MHz, series-resonant, fundamental crystal is placed between these two pins to create the system clock. See <a href="Figure 6">Figure 6</a> and <a href="Figure 7">Figure 7</a> .                                  |

| CLK          | 28      | I   | Serial bus clock signal.                                                                                                                                                                                                                   |

| EN           | 26      | I   | Serial bus latch enable.                                                                                                                                                                                                                   |

| DATA         | 27      | I   | Serial bus data pin.                                                                                                                                                                                                                       |

| LD           | 25      | 0   | The lock detect signal to the demodulator/FEC IC.<br>$Z_{LOAD}$ = 10 k $\Omega$ //20 pF. High is the locked state.                                                                                                                         |

Table 2. Power Supply and Ground Pins

| Pin Name | Pin No.                                                                       | I/O | Description       |

|----------|-------------------------------------------------------------------------------|-----|-------------------|

| VCC      | 1, 13, 18, 22,<br>29, 38, 40,<br>42, 44, 47                                   | Р   | +5 V power supply |

| GND      | 2, 3, 5, 6, 7,<br>14, 15, 19,<br>21, 23, 30,<br>33, 39, 41,<br>43, 45, 46, 48 | Р   | Ground            |

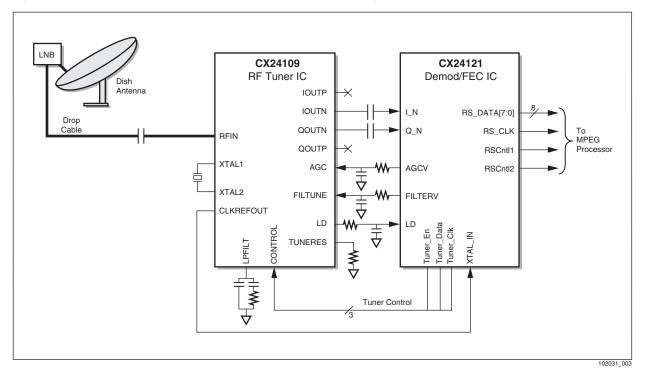

# 1.3 Application Overview

Several million Satellite Set-Top Boxes (STBs) are deployed in many different entertainment networks around the world today. The standards for each network may vary a little but the requirements for the tuner in the STB are essentially the same. Each receiver system in the

# **Chapter 1: Functional Description**

13

network requires an antenna, a Low Noise Block (LNB) downconverter, a drop cable, and an STB. The LNB converts the satellite downlink frequency to an intermediate L-band frequency where it is passed to the STB via the drop cable. The STB front end consists of a tuner and a demodulator/FEC IC. The satellite tuner must tune to the L-band frequency, downconvert the carrier, and separate it to baseband I and Q signals. The demodulator/FEC IC includes QPSK Demodulation, carrier tracking, AGC control, bit timing, and the required FEC for a given network service. Figure 2 illustrates a typical application block diagram for the CX24109/CX24121 chip set in an STB front end.

Figure 2. **QPSK Demodulation Typical Application Block Diagram**

### 1.4 **Signal Path**

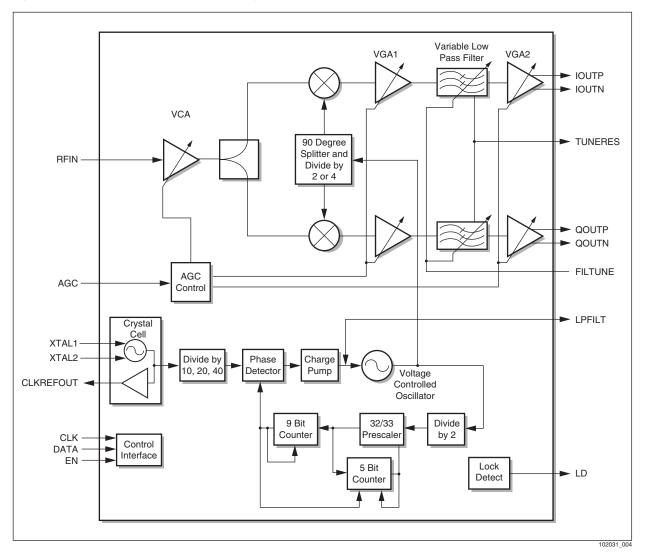

The CX24109 is a highly integrated, direct-down conversion satellite tuner. It consists of an LNA, variable RF attenuator, quadrature downconverter, variable IF gain amplifiers, variable low-pass filters, VCO, and synthesizer. A detailed block diagram of the IC is illustrated in Figure 3.

CX24109 N 1 © NXP B.V. 2008. All rights reserved Rev. 01 — 13 November 2008

# **Chapter 1: Functional Description**

Figure 3. Detailed Functional Block Diagram

# **Chapter 1: Functional Description**

The L-band output from the LNB enters the IC through the RFIN pin and is immediately amplified by the Voltage Controlled Attenuator block (VCA). The VCA functions as a variable gain LNA. The noise figure and gain of the VCA are the dominant factors for the tuner's noise figure. The signal is then quadrature downconverted to I and Q baseband channels. Additional amplifiers at baseband provide more variable gain for the AGC loop. Also at baseband, variable low-pass filters provide anti-alias filtering and eliminate noise power from adjacent carriers and spurious signals before they can impact the A/Ds in the demodulator IC.

# 1.5 AGC and Control

The AGC functionality for the CX24109 is split between the RF and baseband sections, and provides 80 dB of variable gain. The primary control for the AGC is an analog voltage from the demodulator IC. Programmable adjustments to the slope and offset of each variable gain component in the tuner are available through the AGC control registers. Programming information for the VGA and VCA is provided in <u>Tables 4</u> and <u>5</u>, respectively. The recommended default values for the programmable control bits versus symbol rate are listed in <u>Table 8</u>.

# 1.6 Local Oscillator

The local oscillator consists of a synthesizer and a VCO block, and is contained entirely within the CX24109. The VCO block uses an innovative architecture that requires only a 5 V source, eliminating the need for a 28 V power supply. It includes the required tank circuit.

The VCO block consists of a bank of eight oscillators operating at twice and four times the input frequency with a continuous range from 2200 MHz to 4400 MHz. The VCOs overlap to cover the frequency range from 950 MHz to 2150 MHz under all voltage, temperature, and process variations. The VCO tuning range, combined with programmable  $\div 2$  or  $\div 4$  frequency dividers, creates the continuous frequencies from 950 MHz to 2150 MHz for the local oscillator. A simple tuning algorithm must be run by the host processor one time at power-up to calibrate the VCO block. Conexant provides this program.

The synthesizer is also contained within the CX24109. It uses a 10.111 MHz reference frequency and a reference divider,  $\div R$ , to set the phase comparison frequency. Two programming bits are used to configure the reference divider to divide by 10, 20, or 40, which in turn sets the comparison frequency to 1.0111 MHz, 505 kHz, or 253 kHz, respectively. A reference divider of 10 is recommended. The comparison frequency also determines the frequency step size of the local oscillator. Another programmable divider is provided for the VCO output. It consists of a 32/33 prescaler, a 9-bit N-counter (N-divider), a 5-bit A-counter (A-divider), and a fixed  $\div$  2 block. The programmable divider divides the VCO output from its highest frequency to the minimum phase comparison frequency. The programmable charge pump includes output currents of 1 mA, 2 mA, 3 mA, and 4 mA. Programming information for the synthesizer can be found in Table 7. The recommended values for charge pump current, polarity, and referenced dividers are listed in Tables 9 and 10.

The typical loop filter bandwidth is set with external passive components and should be set between 8 kHz and 15 kHz.

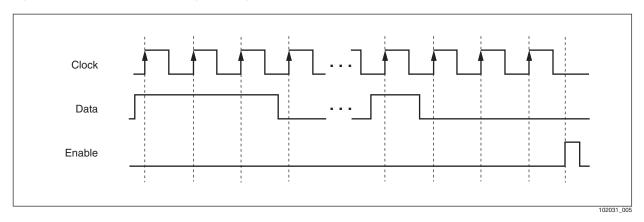

# 1.7 Programming Interface

A three-wire serial interface with Clock, Data, and Enable lines is used to program the CX24109. All digital signals are CMOS-compatible. The serial data carries the binary settings for the programmable dividers, the VCO band select, the voltage-controlled attenuator, and the voltage-controlled amplifiers. When the Enable line is low, data is shifted into an internal shift register on the rising edge of the clock, and when the Enable line goes high, the stored data is latched. The clock signal should be kept low when inactive. The maximum clock rate is 1 MHz. Figure 4 illustrates the relationship between the Clock, Data, and Enable signals.

CX24109\_N\_1 © NXP B.V. 2008. All rights reserved.

# **Chapter 1: Functional Description**

16

Figure 4. **Serial Interface Programming Example**

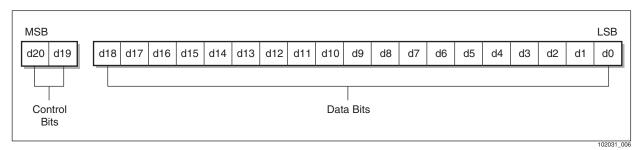

The internal shift register in the CX24109 is 21 bits long. When the data is latched into the IC, the two MSBs act as control bits, and the lower 19 bits are the data bits as illustrated in Figure 5. Data must be entered MSB first.

Figure 5. **Programming Word Configuration**

The control bits determine the functional block that is being programmed, while the data bits contain the specific control information. Table 3 provides a detail mapping of the control and data bits.

**Programming Bit Mapping (Sheet 1 of 2)** Table 3.

|           |                         |    |    | _  |    | _  | -        |     | -         |        |       |                  |   |   |          |          |        |   |   |          |

|-----------|-------------------------|----|----|----|----|----|----------|-----|-----------|--------|-------|------------------|---|---|----------|----------|--------|---|---|----------|

|           | Programming Bit Mapping |    |    |    |    |    |          |     |           |        |       |                  |   |   |          |          |        |   |   |          |

| 20<br>MSB | 19                      | 18 | 17 | 16 | 15 | 14 | 13       | 12  | 11        | 10     | 9     | 8                | 7 | 6 | 5        | 4        | 3      | 2 | 1 | 0<br>LSB |

|           | Band Select             |    |    |    |    |    |          |     |           |        |       |                  |   |   |          |          |        |   |   |          |

| 0         | 0                       | R  | R  | R  | R  | R  | R        | R   | $R^{(1)}$ | R      | V     | R <sup>(1)</sup> |   |   |          | Band     | Select |   |   |          |

|           |                         |    |    |    |    |    |          |     | VGA F     | rogran | nming |                  |   |   |          |          |        |   |   |          |

| 0         | 1                       | R  |    |    |    | V  | GA2 Offs | set |           |        |       |                  |   |   | V        | GA1 Offs | set    |   |   |          |

|           | VCA Programming         |    |    |    |    |    |          |     |           |        |       |                  |   |   |          |          |        |   |   |          |

| 1         | 1 0 R VCA Offset        |    |    |    |    |    |          |     |           |        |       |                  |   | ٧ | 'CA Slop | е        |        |   |   |          |

|           |                         | -  | -  |    |    |    |          |     |           |        |       | -                |   |   |          |          |        |   |   |          |

**PLL Programming**

# **Chapter 1: Functional Description**

**17**

### **Programming Bit Mapping (Sheet 2 of 2)** Table 3.

|   | Programming Bit Mapping |            |   |                           |     |                               |    |     |                           |     |  |  |  |  |

|---|-------------------------|------------|---|---------------------------|-----|-------------------------------|----|-----|---------------------------|-----|--|--|--|--|

| 1 | 1                       | ÷R Divider | Р | Charge<br>Pump<br>Current | MSB | ÷ N Divider <sup>(2)</sup> LS | ВМ | MSB | ÷A Divider <sup>(2)</sup> | LSB |  |  |  |  |

# GENERAL NOTES:

1. R means Reserved except for  $\div R$  which means reference divider.

P means Charge Pump Polarity

V means VCO Divide Select

FOOTNOTES:

(1) These Reserved locations must be set to zero. All other Reserved location values do not matter.

(2) These Divide ratios are binary coded.

# **Chapter 1: Functional Description**

Table 4. Band Select Programming

|       | Band Select |       |       |       |       |       |       |                                             |               |                |  |  |  |  |  |

|-------|-------------|-------|-------|-------|-------|-------|-------|---------------------------------------------|---------------|----------------|--|--|--|--|--|

| Bit 7 | Bit 6       | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Typical Receive<br>Frequency Range<br>(MHz) | VCO<br>Number | VCO<br>Divider |  |  |  |  |  |

| 0     | 1           | 0     | 0     | 0     | 0     | 0     | 0     | 950–1019                                    | 7             | 4              |  |  |  |  |  |

| 1     | 0           | 0     | 0     | 0     | 0     | 0     | 0     | 1019–1075                                   | 8             | 4              |  |  |  |  |  |

| 0     | 0           | 0     | 0     | 0     | 0     | 0     | 1     | 1075–1178                                   | 1             | 2              |  |  |  |  |  |

| 0     | 0           | 0     | 0     | 0     | 0     | 1     | 0     | 1178–1296                                   | 2             | 2              |  |  |  |  |  |

| 0     | 0           | 0     | 0     | 0     | 1     | 0     | 0     | 1296–1432                                   | 3             | 2              |  |  |  |  |  |

| 0     | 0           | 0     | 0     | 1     | 0     | 0     | 0     | 1432–1576                                   | 4             | 2              |  |  |  |  |  |

| 0     | 0           | 0     | 1     | 0     | 0     | 0     | 0     | 1576–1718                                   | 5             | 2              |  |  |  |  |  |

| 0     | 0           | 1     | 0     | 0     | 0     | 0     | 0     | 1718–1856                                   | 6             | 2              |  |  |  |  |  |

| 0     | 1           | 0     | 0     | 0     | 0     | 0     | 0     | 1856–2036                                   | 7             | 2              |  |  |  |  |  |

| 1     | 0           | 0     | 0     | 0     | 0     | 0     | 0     | 2036–2150                                   | 8             | 2              |  |  |  |  |  |

# VCO Divide Select

| Bit 9 | Function |

|-------|----------|

| 0     | ÷4       |

| 1     | ÷2       |

# **Chapter 1: Functional Description**

Table 5. VGA Programming

|        | VGA1 Offset |        |        |        |        |        |           |       |              |

|--------|-------------|--------|--------|--------|--------|--------|-----------|-------|--------------|

| Bit 8  | Bit 7       | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1     | Bit 0 | Offset in dB |

| 1      | 1           | 1      | 1      | 1      | 1      | 1      | 1         | 0     | -27.0        |

| 1      | 1           | 1      | 1      | 1      | 1      | 1      | 0         | 0     | -28.5        |

| 1      | 1           | 1      | 1      | 1      | 1      | 0      | 0         | 0     | -30.0        |

| 1      | 1           | 1      | 1      | 1      | 0      | 0      | 0         | 0     | -31.5        |

| 1      | 1           | 1      | 1      | 0      | 0      | 0      | 0         | 0     | -33.0        |

| 1      | 1           | 1      | 0      | 0      | 0      | 0      | 0         | 0     | -34.5        |

| 1      | 1           | 0      | 0      | 0      | 0      | 0      | 0         | 0     | -36.0        |

| 1      | 0           | 0      | 0      | 0      | 0      | 0      | 0         | 0     | -37.5        |

| 0      | 0           | 0      | 0      | 0      | 0      | 0      | 0         | 0     | -39.0        |

|        |             |        |        |        |        | VGA    | A2 Offset |       |              |

| Bit 17 | Bit 16      | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10    | Bit 9 | Offset in dB |

| 1      | 1           | 1      | 1      | 1      | 1      | 1      | 1         | 0     | 35           |

| 1      | 1           | 1      | 1      | 1      | 1      | 1      | 0         | 0     | 32           |

| 1      | 1           | 1      | 1      | 1      | 1      | 0      | 0         | 0     | 29           |

| 1      | 1           | 1      | 1      | 1      | 0      | 0      | 0         | 0     | 26           |

| 1      | 1           | 1      | 1      | 0      | 0      | 0      | 0         | 0     | 23           |

| 1      | 1           | 1      | 0      | 0      | 0      | 0      | 0         | 0     | 20           |

| 1      | 1           | 0      | 0      | 0      | 0      | 0      | 0         | 0     | 17           |

| 1      | 0           | 0      | 0      | 0      | 0      | 0      | 0         | 0     | 14           |

| 0      | 0           | 0      | 0      | 0      | 0      | 0      | 0         | 0     | 11           |

# **Chapter 1: Functional Description**

Table 6. VCA Programming

| Table 0. |           | A i logi | a      | ,      |        |        |          |       |               |  |

|----------|-----------|----------|--------|--------|--------|--------|----------|-------|---------------|--|

|          | VCA Slope |          |        |        |        |        |          |       |               |  |

| Bit 8    | Bit 7     | Bit 6    | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1    | Bit 0 | Slope in dB/V |  |

| 0        | 0         | 0        | 0      | 0      | 0      | 0      | 0        | 1     | 47.0          |  |

| 0        | 0         | 0        | 0      | 0      | 0      | 0      | 1        | 1     | 49.5          |  |

| 0        | 0         | 0        | 0      | 0      | 0      | 1      | 1        | 1     | 52.0          |  |

| 0        | 0         | 0        | 0      | 0      | 1      | 1      | 1        | 1     | 54.5          |  |

| 0        | 0         | 0        | 0      | 1      | 1      | 1      | 1        | 1     | 57.0          |  |

| 0        | 0         | 0        | 1      | 1      | 1      | 1      | 1        | 1     | 59.5          |  |

| 0        | 0         | 1        | 1      | 1      | 1      | 1      | 1        | 1     | 62.0          |  |

| 0        | 1         | 1        | 1      | 1      | 1      | 1      | 1        | 1     | 64.5          |  |

| 1        | 1         | 1        | 1      | 1      | 1      | 1      | 1        | 1     | 67.0          |  |

|          |           |          |        |        |        | VC     | A Offset |       |               |  |

| Bit 17   | Bit 16    | Bit 15   | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10   | Bit 9 | Offset in dB  |  |

| 0        | 0         | 0        | 0      | 0      | 0      | 0      | 0        | 1     | 90.00         |  |

| 0        | 0         | 0        | 0      | 0      | 0      | 0      | 1        | 1     | 94.25         |  |

| 0        | 0         | 0        | 0      | 0      | 0      | 1      | 1        | 1     | 98.50         |  |

| 0        | 0         | 0        | 0      | 0      | 1      | 1      | 1        | 1     | 102.75        |  |

| 0        | 0         | 0        | 0      | 1      | 1      | 1      | 1        | 1     | 107.00        |  |

| 0        | 0         | 0        | 1      | 1      | 1      | 1      | 1        | 1     | 111.25        |  |

| 0        | 0         | 1        | 1      | 1      | 1      | 1      | 1        | 1     | 115.50        |  |

| 0        | 1         | 1        | 1      | 1      | 1      | 1      | 1        | 1     | 119.75        |  |

| 1        | 1         | 1        | 1      | 1      | 1      | 1      | 1        | 1     | 124.00        |  |

# **Chapter 1: Functional Description**

Table 7. **PLL Programming**

| Tubio 7. TEETTO | J                   |                      |  |  |  |  |  |

|-----------------|---------------------|----------------------|--|--|--|--|--|

|                 | Charge Pump Current |                      |  |  |  |  |  |

| Bit 15          | Bit 14              | Current (mA)         |  |  |  |  |  |

| 0               | 0                   | 1                    |  |  |  |  |  |

| 0               | 1                   | 2                    |  |  |  |  |  |

| 1               | 0                   | 3                    |  |  |  |  |  |

| 1               | 1                   | 4                    |  |  |  |  |  |

|                 |                     | Charge Pump Polarity |  |  |  |  |  |

| Bit             | 16                  | Function             |  |  |  |  |  |

| (               | )                   | Positive             |  |  |  |  |  |

|                 | 1                   | Negative             |  |  |  |  |  |

|                 |                     | Reference Dividers   |  |  |  |  |  |

| Bit 18          | Bit 17              | Function             |  |  |  |  |  |

| 0               | 0                   | _                    |  |  |  |  |  |

| 0               | 1                   | Reserved             |  |  |  |  |  |

| 1               | 0                   | Reserved             |  |  |  |  |  |

| 1               | 1                   | ÷10                  |  |  |  |  |  |

### 1.7.1 **Gain Equations**

The RF block voltage gain  $(G_{RF})$  is equal to the VCA gain + the mixer gain.

$\begin{aligned} G_{RF} &= V_{AGC} \times VCA \ Slope - VCA \ Offset \ (in \ dB) + 23 \\ where \ the \ maximum \ value \ of \ G_{RF} \ \ is \ 23 \ dB, \ regardless \ of \ voltage \end{aligned}$

$\begin{aligned} VGA1 \ voltage \ gain \ (G_{VGA1}) \ is \ equal \ to \\ G_{VGA1} = \ V_{AGC} \times 26 + VGA1 \ Offset \ (in \ dB) \end{aligned}$

VGA2 voltage gain  $(G_{VGA2})$  is equal to  $G_{VGA2} = VGA2 \text{ Offset (in dB)}$

The total baseband voltage gain  $(G_{\mbox{\footnotesize Baseband}})$  is equal to

$G_{\text{Baseband}} = G_{\text{VGA1}} + G_{\text{Filter}} + G_{\text{VGA2}}$ =  $G_{\text{VGA1}} + 3 + G_{\text{VGA2}}$

# **Chapter 1: Functional Description**

# 1.7.2 Frequency Equations

The VCO frequency is determined by

$$\begin{aligned} F_{\text{VCO}} &= (F_{\text{Crystal}} \div R) \times (N + (A \div 32)) \times 32 \times 2 \\ &= (10.111 \div R) \times (N + (A \div 32)) \times 32 \times 2 \end{aligned}$$

NOTE: If A = 0, then N = N + 1

Remember, the incoming receive frequency is always lower than the VCO frequency, such that:

$$F_{Receive} = F_{VCO} \div 2 \text{ or } F_{VCO} \div 4$$

## 1.7.3 Recommended Default Values

# Table 8. Recommended AGC Programming Values

| VCA and VGA Slope and Offset vs. Symbol Rate |                     |                                |                                     |                     |                                         |                     |                           |

|----------------------------------------------|---------------------|--------------------------------|-------------------------------------|---------------------|-----------------------------------------|---------------------|---------------------------|

| Symbol Rate                                  | VCA Slope<br>(dB/V) | VCA Offset (dB) <sup>(1)</sup> | VGA1 Slope<br>(dB/V) <sup>(2)</sup> | VGA1 Offset<br>(dB) | VGA2<br>Slope (dB/<br>V) <sup>(2)</sup> | VGA2 Offset<br>(dB) | FILTUNE<br>Voltage<br>(V) |

| 1 to 5 MSps                                  | 52                  | 98.5<br>(102.75)               | 26                                  | -30                 | 0                                       | 29                  | 0.41                      |

| 5 to 15 MSps                                 | 57                  | 98.5<br>(107)                  | 26                                  | -33                 | 0                                       | 17                  | 0.90                      |

| 15 to 45 MSps                                | 59.5                | 98.5<br>(111.25)               | 26                                  | -36                 | 0                                       | 14                  | 2.70                      |

# FOOTNOTES:

Table 9. Recommended VCO Frequency vs. Charge Pump Current

| VCO Frequency                    | Charge Pump Current |

|----------------------------------|---------------------|

| Lower 50% VCO Frequency Range    | 2 mA                |

| Upper 50% of VCO Frequency Range | 3 mA                |

# Table 10. Recommended Charge Pump Polarity and Reference Divider Values

| Feature              | Specification |

|----------------------|---------------|

| Charge Pump Polarity | Negative      |

| Reference Divider    | ÷10           |

CX24109\_N\_1 © NXP B.V. 2008. All rights reserved.

<sup>(1)</sup> There is an interaction between the offset and slope settings in the RF block, so the actual settings will be different from the theoretical setting. Theoretical settings are given in parentheses.

<sup>(2)</sup> These values are for reference only. They are not programmable.

# CX24109

# Chapter 2: Applications Rev. 01 — 13 November 2008

**Product data sheet**

### 2.1 **AGC Input**

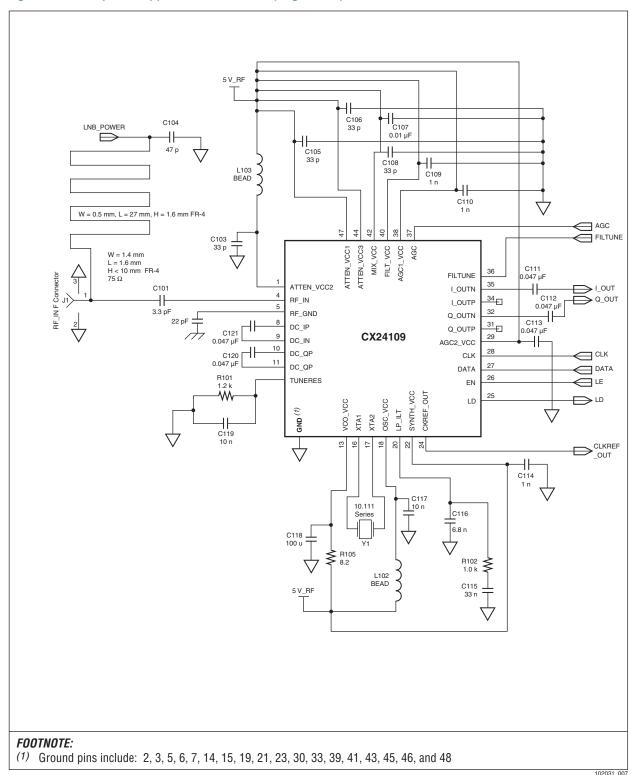

To prevent excessive current draw, a 10 k $\Omega$  resistor on the AGC pin is recommended. See Figure 6.

### **VCO Power Pin Ripple Requirement** 2.2

Care must be taken to reduce the power supply ripple on pin 13 (VCO power supply) in order to reduce phase noise. The power supply conditioning circuitry given in Figure 6 is suitable for most circumstances.

### **Transmission Lines** 2.3

Though the CX24109's RF layout is simple, there are two transmission lines that must be designed. The first transmission line is the LNB power line, which is located at the connector. The second transmission line is between the connector and the RF IN pin. The input transmission line must have a characteristic impedance of 75  $\Omega$ . The schematic gives recommended dimensions assuming a two-layer FR-4 board.

### **Example Schematic** 2.4

Figure 6 provides a simplified version of the CX24109/CX24121 reference design. For complete and current reference design information, contact your local Conexant sales office.

CX24109 N 1 © NXP B.V. 2008. All rights reserved.

Product data sheet

Rev. 01 — 13 November 2008 23

**Chapter 2: Applications**

Figure 6. Simplified Application Schematic (Page 1 of 2)

CX24109\_N\_1

**Product data sheet**

24

**Chapter 2: Applications**

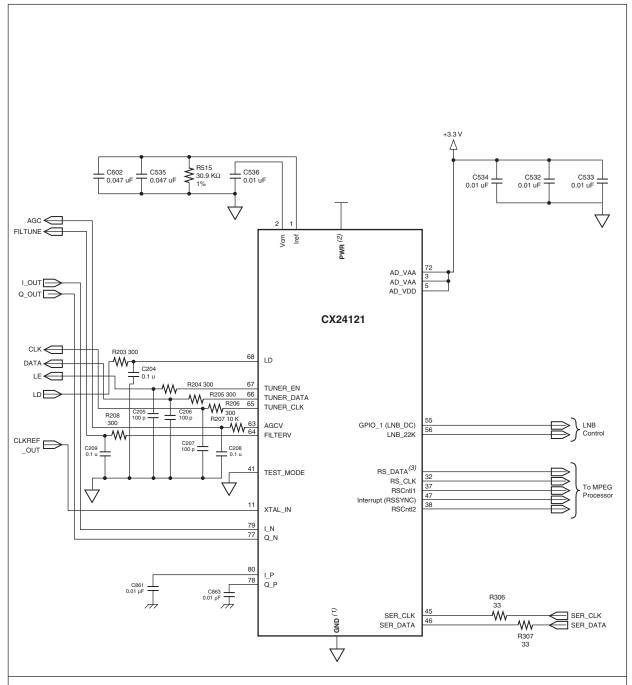

Figure 7. Simplified Application Schematic (Page 2 of 2)

## FOOTNOTE:

- (1) Ground Pins include: 4, 6, 8, 10, 15, 26, 30, 34, 50, 52, 62, 70, and 71.

- (2) Core (1.8 V) power pins include: 7, 9, 14, 29, 49, and 69. 3.3 V power pins include: 25, 33, 51, and 61.

- (3) RS\_DATA includes RS\_DATA0-RS\_DATA7 pins 35, 31, 28, 27, 24, 23, 22, and 21.

02031\_008

25

**Chapter 2: Applications**

# 2.5 Typical Performance Curves

Figure 8. Reflection Coefficient at Input of CX24109

Figure 9. Baseband Filter Gain vs. Frequency and FILTUNE Voltage

Figure 10. Filter -3 dB Bandwidth vs. FILTUNE Voltage

CX24109\_N\_1 © NXP B.V. 2008. All rights reserved. Rev. 01 — 13 November 2008

Figure 11. Gain and IIP3 vs. AGC Voltage at 950 MHz

Figure 12. Gain and IIP3 vs. AGC Voltage at 2150 MHz

Downloaded from Arrow.com.

29

Figure 13. Gain and NF vs. AGC Voltage at 950 MHz

Figure 14. Gain and NF vs. AGC Voltage at 2150 MHz

CX24109\_N\_1 © NXP B.V. 2008. All rights reserved. Rev. 01 — 13 November 2008

**Chapter 2: Applications**

**Product data sheet**

30

# CX24109

# Chapter 3: Parametric Data and Specifications Rev. 01 — 13 November 2008

Product data sheet

### **Electrical Specifications** 3.1

Table 11. **Absolute Maximum Ratings**

| Parameter            | Minimum | Maximum  | Units |

|----------------------|---------|----------|-------|

| Supply Voltage       | -0.3    | 6        | V     |

| Input Voltage Range  | -0.3    | Vcc +0.3 | V     |

| Storage Temperature  | -65     | +150     | °C    |

| Junction Temperature | _       | +150     | °C    |

### 3.1.1 **Standard Operating Conditions**

All specifications are valid under the operating conditions indicated in Tables 8, 9, 10, and 12.

**Operating Conditions** Table 12.

| Parameter                                | Conditions                   | Min  | Тур    | Max          | Units |

|------------------------------------------|------------------------------|------|--------|--------------|-------|

| Ambient Operating Temperature            | _                            | 0    | +25    | +70          | °C    |

| Maximum Operating Junction Temperature   | _                            | _    | _      | 125          | °C    |

| Supply Voltage                           | _                            | 4.75 | 5.0    | 5.25         | V     |

| Reference Oscillator Frequency           | Series resonant, fundamental | _    | 10.111 | _            | MHz   |

| Reference Oscillator Frequency Stability | Including temperature drift  | _    | _      | <u>+</u> 100 | ppm   |

| Loop Filter Bandwidth                    | _                            | _    | 10     | _            | kHz   |

© NXP B.V. 2008. All rights reserved. Rev. 01 — 13 November 2008 **Product data sheet** 31

# **Chapter 3: Parametric Data and Specifications**

**DC Electrical Characteristics** Table 13.

| Parameter                                          | Conditions                 | Min | Тур | Max  | Units     |

|----------------------------------------------------|----------------------------|-----|-----|------|-----------|

| Supply Current <sup>(1)</sup>                      | _                          | _   | 244 | 262  | mA        |

| Usable AGC Voltage Range, V <sub>AGC</sub>         | _                          | 1.3 | _   | 2.80 | V         |

| Impedance of AGC Input                             | at DC                      | _   | 1   | _    | $M\Omega$ |

| AGC Current, I <sub>AGC</sub>                      | _                          | _   | _   | 0.4  | mA        |

| Usable Filtune Voltage Range, V <sub>Filtune</sub> | _                          | 0   | _   | 3.0  | V         |

| Impedance of Filtune Input                         | at DC                      | _   | 17  | _    | kΩ        |

| Thermal Resistance of Package                      | $\theta$ ja <sup>(2)</sup> | _   | 42  | _    | °C/W      |

|                                                    | θјс                        | _   | 8.7 | _    | °C/W      |

Table 14. **AC Electrical Characteristics**

| Paramete                                  | er                                     | Conditions     | Min | Тур  | Max   | Units |

|-------------------------------------------|----------------------------------------|----------------|-----|------|-------|-------|

| Programming Clock Frequency               |                                        | _              | _   | _    | 1     | MHz   |

| Bus Timing                                | Data Setup, t <sub>SU</sub>            | See Figure 15. | _   | 10   | _     | ns    |

|                                           | Data Hold, t <sub>HD</sub>             |                | _   | 10   | _     | ns    |

|                                           | Enable Pulse<br>Width, t <sub>EW</sub> |                | 1   | _    | _     | μS    |

|                                           | Clock to Enable,<br>t <sub>CE</sub>    |                | _   | 1    | _     | μS    |

| Programming Lines:<br>Clock, Data, Enable | $V_{IH}$                               | _              | 2.1 | _    | _     | V     |

| Clock, Data, Litable                      | $V_{IL}$                               | _              | _   | _    | 0.8   | V     |

|                                           | I <sub>IH</sub>                        | _              | _   | _    | 0.5   | mA    |

|                                           | I <sub>IL</sub>                        | _              | _   | _    | -0.5  | mA    |

| LD and CLKREFOUT                          | V <sub>OH</sub>                        | _              | 2.3 | 2.65 | _     | V     |

|                                           | V <sub>OL</sub>                        | _              | _   | 0.9  | 1.125 | V     |

CX24109 N 1 © NXP B.V. 2008. All rights reserved. Rev. 01 — 13 November 2008

32

FOOTNOTES:

(1) Using 15–45 MSps programming values (see <u>Table 8</u>), V<sub>CC</sub> = 5.0 V, V<sub>AGC</sub> = 1.45 V, V<sub>Filtune</sub> = 2.7 V.

(2) Using a 2-layer CX24109/CX24121 reference design, where the package's exposed paddle is connected to the printed circuit board ground plane using thermal vias. The ground plane on the reference design is approximately 2-7/8 inches x 1-1/4 inches. Better thermal performance can be obtained by increasing ground plane coverage or increasing the number of attached printed circuit board layers.

# **Chapter 3: Parametric Data and Specifications**

33

Figure 15. Serial Programming Example

Table 15. RF Electrical Characteristics (Sheet 1 of 3)

| Parameter                               | Conditions                                                         | Min | Тур  | Max  | Units     |

|-----------------------------------------|--------------------------------------------------------------------|-----|------|------|-----------|

| Tuning Frequency                        | _                                                                  | 950 | _    | 2150 | MHz       |

| Input Power, Single $Tone^{(I)}$        | Depends on bandwidth of incoming signal and C/I                    | -81 | _    | -23  | dBm       |

| Aggregate Input Power <sup>(1)(2)</sup> | _                                                                  | _   | _    | -7   | dBm       |

| Input Impedance, Balanced $^{(I)}$      | $Z_{SOURCE} = 75 \Omega$                                           | _   | 75   | _    | Ω         |

| Input $VSWR^{(I)}$                      | _                                                                  | _   | 10   | _    | dB        |

| lout and Qout Output Voltage            | $R_{Load} = 1 k\Omega$                                             | _   | 0.5  | _    | $V_{P-P}$ |

| Maximum Conversion (Voltage) Gain       | V <sub>AGC</sub> =2.4 V, 1 MSps gain coefficients <sup>(1)</sup>   | 76  | 86   | 91   | dB        |

| Minimum Conversion (Voltage) Gain       | V <sub>AGC</sub> =1.45 V, 45 MSps gain coefficients <sup>(1)</sup> | 8   | 18   | 23   | dB        |

| Noise Figure (NF) $^{(I)}$ $^{(3)}$     | Pin = -43 dBm,<br>1–5 MSps gain coefficients <sup>(4)</sup>        | _   | 36   | 42   | dB        |

|                                         | Pin = -81 dBm,<br>1-5 MSps gain coefficients <sup>(5)</sup>        | _   | 10.5 | 14   | dB        |

|                                         | Pin = -34.5 dBm,<br>5–15 MSps gain coefficients <sup>(6)</sup>     | _   | 35   | 42   | dB        |

|                                         | Pin = -72 dBm,<br>5-15 MSps gain coefficients <sup>(7)</sup>       | _   | 10.5 | 14   | dB        |

|                                         | Pin = -30 dBm,<br>15-45 MSps gain coefficients <sup>(8)</sup>      | _   | 35   | 45   | dB        |

|                                         | Pin = -70 dBm,<br>15-45 MSps gain coefficients <sup>(9)</sup>      | _   | 10.5 | 14   | dB        |

CX24109\_N\_1 © NXP B.V. 2008. All rights reserved. Rev. 01 — 13 November 2008

# **Chapter 3: Parametric Data and Specifications**

34

Table 15. RF Electrical Characteristics (Sheet 2 of 3)

| Parameter                             | Conditions                                                                             | Min | Тур   | Max | Units        |

|---------------------------------------|----------------------------------------------------------------------------------------|-----|-------|-----|--------------|

| IIP3 (Out-of-band) <sup>(1) (4)</sup> | $\pm$ (31 and 60) MHz, Pin = -42 dBm,<br>1–5 MSps gain coefficients <sup>(4)</sup>     | -2  | 4.0   | _   | dBm          |

|                                       | $\pm$ (91 and 180) MHz, Pin = -42 dBm,<br>1–5 MSps gain coefficients <sup>(4)</sup>    | 5.5 | 9.4   | _   | dBm          |

|                                       | $\pm$ (31 and 60) MHz, Pin = -81 dBm,<br>1-5 MSps gain coefficients                    | -35 | -25.0 |     | dBm          |

|                                       | $\pm$ (91 and 180) MHz, Pin = -81 dBm,<br>1-5 MSps gain coefficients <sup>(5)</sup>    | -39 | -7.2  | _   | dBm          |

|                                       | $\pm$ (31 and 60) MHz, Pin = -34.5 dBm,<br>5–15 MSps gain coefficients <sup>(6)</sup>  | 0   | 5.0   | _   | dBm          |

|                                       | $\pm$ (91 and 180) MHz, Pin = -34.5 dBm,<br>5–15 MSps gain coefficients <sup>(6)</sup> | 5.5 | 9.8   | _   | dBm          |

|                                       | $\pm$ (31 and 60) MHz, Pin = -72 dBm,<br>5-15 MSps gain coefficients <sup>(7)</sup>    | -35 | -25.5 | _   | dBm          |

|                                       | $\pm$ (91 and 180) MHz, Pin = -72 dBm,<br>5-15 MSps gain coefficients <sup>(7)</sup>   | -30 | -6.5  | _   | dBm          |

|                                       | $\pm$ (31 and 60) MHz, Pin = -30 dBm,<br>15-45 MSps gain coefficients <sup>(8)</sup>   | -2  | 5.5   | _   | dBm          |

|                                       | $\pm$ (91 and 180) MHz, Pin = -30 dBm,<br>15-45 MSps gain coefficients <sup>(8)</sup>  | 5.7 | 10.5  | _   | dBm          |

|                                       | $\pm$ (31 and 60) MHz, Pin = -70 dBm,<br>15-45 MSps gain coefficients <sup>(9)</sup>   | -35 | -24.5 | _   | dBm          |

|                                       | $\pm$ (91 and 180) MHz, Pin = -70 dBm,<br>15-45 MSps gain coefficients <sup>(9)</sup>  | -28 | -6.5  | _   | dBm          |

| IIP3 <sub>I</sub> (Inband)            | 1 MSps coefficients and $V_{AGC} = 1.5 V^{(I)}$                                        | _   | -30   | _   | dBm          |

|                                       | 1 MSps coefficients and $V_{AGC} = 2.4 V^{(1)}$                                        | _   | -65   | _   | dBm          |

| I/Q Phase Difference                  | _                                                                                      | _   | 3     | 13  | <u>+</u> deg |

| I/Q Amplitude Ratio                   | _                                                                                      | _   | 1     | 3   | <u>+</u> dB  |

| LO Leakage                            | 950 to 2150 MHz <sup>(1)</sup>                                                         | _   | -80   | -70 | dBm          |

| 2LO-RF Rejection                      | $C/I = 10 \text{ dB V}_{AGC} = 1.5 \text{ V}^{(I)}$                                    | -30 | -45   | _   | dB           |

| 2RF-LO Rejection                      | $C/I = 10 \text{ dB}^{(I)}$                                                            | -30 | -50   | _   | dB           |

© NXP B.V. 2008. All rights reserved. Rev. 01 — 13 November 2008

# **Chapter 3: Parametric Data and Specifications**

35

RF Electrical Characteristics (Sheet 3 of 3) Table 15.

| Parameter                           | Conditions                                                                | Min | Тур         | Max  | Units  |

|-------------------------------------|---------------------------------------------------------------------------|-----|-------------|------|--------|

| VCO and Synthesizer                 |                                                                           |     |             |      |        |

| Reference Oscillator Phase Noise    | Measured at 400 Hz                                                        | _   | -130        | _    | dBc/Hz |

| Spurious                            | At 1, 10.111, and 30 MHz offsets with 2 mA charge pump and 10 kHz loop BW | -30 | -45         | _    | dBc    |

| VCO Tuning Sensitivity              | _                                                                         | 100 | _           | 330  | MHz/V  |

| LO Phase Noise at 950 MHz-1450 MHz  | 10 kHz offset                                                             | _   | <b>-</b> 75 | _    | dBc/Hz |

|                                     | 100 kHz offset                                                            | _   | -97         | _    | dBc/Hz |

| LO Phase Noise at 1450 MHz-2150 MHz | 10 kHz offset                                                             | _   | -69         | _    | dBc/Hz |

|                                     | 100 kHz offset                                                            | _   | -94         | _    | dBc/Hz |

| LO Phase Noise at 950 MHz-2150 MHz  | 10 kHz offset +100 kHz offset                                             | _   | _           | -158 | dBc/Hz |

| Local Oscillator Settling Time      | All frequencies, VCOs and modes                                           | _   | 1           | _    | ms     |

### GENERAL NOTES:

1. Values in this table are valid under the operating conditions listed in Tables 8, 9, and 10, using a reference divider of 10, unless otherwise

# FOOTNOTES:

- $^{(I)}$  This measurement is made at RFIN of CX24109.

- (2) Aggregate average power of 40 QPSK modulated carriers.

- (3) All NF and IIP3 measurements/specifications are made by setting a specific input level for the desired symbol rate and adjusting the AGC level to obtain the desired output level of 0.5 Vpp.

- (4) This level is derived assuming –23 dBm is the maximum level of all other transponders and that the operating symbol rate is 1 MSps. Assume C/I of 7 dB and a bandwidth scaling of 10 log (20 MHz / 1 MHz), thus, Pin = -23 dBm - 7 dB - 10 log (20 / 1) = -43 dBm.

- This level is derived from Pin =  $P_{Transponder} L_{Path} + G_{Antenna} + G_{LNBmin} L_{Cable}$ . Where the operating symbol rate is 1 MSps and  $P_{Transponder}$  is at a minimum.  $P_{Transponder} = 10 \log ((1E6 / 45E6) 10^{(82-4)/10}) = +61 dBm$ . Therefore,  $P_{Transponder} = 40 \log ((1E6 / 45E6) 10^{(82-4)/10}) = +61 dBm$ . 45 dB - 20 dB = -81 dBm.

- (6) This level is derived assuming –23 dBm is the maximum level of all other transponders and that the operating symbol rate is 7 MSps. Assume C/I of 7 dB and a bandwidth scaling of 10 log (20 MHz / 7 MHz), thus, Pin = -23 dBm - 7 dB - 10 log 20 / 7 = -34.5 dBm.

- This level is derived from Pin =  $P_{Transponder} L_{Path} + G_{Antenna} + G_{LNBmin} L_{Cable}$ . Where the operating symbol rate is 7 MSps and  $P_{Transponder} = 10 log ((7E6 / 45E6) 10^{(82-4)/10}) = +70 dBm.$  Therefore,  $P_{Transponder} = 70 dB + 38 dB + 45 dB - 20 dB = -72 dBm$

- (8) This level is derived assuming –23 dBm is the maximum level of all other transponders, an operating symbol rate of 20 MSps and a C/I of

- (9) Assume a symbol rate of 20 MSps.

# **Chapter 3: Parametric Data and Specifications**

Table 16. **Baseband Frequency Response**

| Parameter                                   | Conditions                               | Min | Тур  | Max | Units |

|---------------------------------------------|------------------------------------------|-----|------|-----|-------|

| Minimum Cutoff Frequency, F <sub>1 dB</sub> | Measured at minimum $V_{\text{Filtune}}$ | 1.4 | _    | 2.6 | MHz   |

| Minimum Cutoff Frequency, F <sub>1 dB</sub> | Measured at maximum V <sub>Filtune</sub> | 27  | _    | _   | MHz   |

| Tuning Voltage Transfer Function            | 0 V < V <sub>Filtune</sub> < 3.0 V       | _   | 10.5 | _   | MHz/V |

| Passband Ripple                             | 0 < Freq < F <sub>1 dB</sub>             | _   | _    | 1.0 | dB    |

| Stopband Attenuation                        | $F > 2.6 \times F_{1 dB}$                | 35  | _    | _   | dB    |

| Stopband Attenuation                        | 5 × F <sub>1 dB</sub> < F < 2 GHz        | 45  | _    | _   | dB    |

### **Mechanical Specifications** 3.2

48-pin eTQFP Land Pattern

CX24109\_N\_1 © NXP B.V. 2008. All rights reserved. Rev. 01 — 13 November 2008

**Product data sheet**

36

# **Chapter 3: Parametric Data and Specifications**

Figure 17. 48-pin eTQFP Package Diagram

102031\_018

37

Chapter 3: Parametric Data and Specifications

CX24109\_N\_1 © NXP B.V. 2008. All rights reserved. Rev. 01 — 13 November 2008

38

# **Digital Satellite Tuner**

# Legal information

# Data sheet status

| Document status [1][2]         | Product status[3] | Definition                                                                            |

|--------------------------------|-------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet   | Development       | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet | Qualification     | This document contains data from the preliminary specification.                       |

| Product [short] data sheet     | Production        | This document contains the product specification.                                     |

- Please consult the most recently issued document before initiating or completing a design.

- The term 'short data sheet' is explained in section "Definitions".

- The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL http://www.nxp.com.

# **Definitions**

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

# **Disclaimers**

General — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental

damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

Applications — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) may cause permanent damage to the device. Limiting values are stress ratings only and operation of the device at these or any other conditions above those given in the Characteristics sections of this document is not implied. Exposure to limiting values for extended periods may affect device reliability.

Terms and conditions of sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nxp.com/profile/terms, including those pertaining to warranty, intellectual property rights infringement and limitation of liability, unless explicitly otherwise agreed to in writing by NXP Semiconductors. In case of any inconsistency or conflict between information in this document and such terms and conditions, the latter will prevail.

No offer to sell or license — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

Quick reference data — The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.

## **Trademarks**

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

CX24109 N 1

Product data sheet

39

**Digital Satellite Tuner**

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

founded by

© NXP B.V. 2008.

All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 13 November 2

Date of release: 13 November 2008 Document identifier: CX24109\_N\_1