# ADC1206S040/055/070

Single 12 bits ADC, up to 40 MHz, 55 MHz or 70 MHz

Rev. 03 — 2 July 2012

Product

Product data sheet

#### **General description** 1.

The ADC1206S040/055/070 are a family of BiCMOS 12-bit Analog-to-Digital Converters (ADC) optimized for a wide range of applications such as cellular infrastructures, professional telecommunications, imaging, and digital radio. It converts the analog input signal into 12-bit binary coded digital words at a maximum sampling rate of 70 MHz. All static digital inputs (SH, CE and OTC) are Transistor-Transistor Logic (TTL) and CMOS compatible and all outputs are CMOS compatible. A sine wave clock input signal can also be used.

#### **Features** 2.

- 12-bit resolution

- Sampling rate up to 70 MHz

- -3 dB bandwidth of 245 MHz

- 5 V power supplies and 3.3 V output power supply

- Binary or twos complement CMOS outputs

- In-range CMOS compatible output

- TTL and CMOS compatible static digital inputs

- TTL and CMOS compatible digital outputs

- Differential AC or Positive Emitter-Coupled Logic (PECL) clock input; TTL compatible

- Power dissipation 550 mW (typical)

- Low analog input capacitance (typical 2 pF), no buffer amplifier required

- Integrated sample and hold amplifier

- Differential analog input

- External amplitude range control

- Voltage controlled regulator included

- -40 °C to +85 °C ambient temperature

## **Applications**

High-speed analog-to-digital conversion for:

- Cellular infrastructure

- Professional telecommunication

- Digital radio

- Radar

- Medical imaging

- Fixed network

- Cable modem

- Barcode scanner

- Cable Modern Termination System (CMTS)/

Data Over Cable Service Interface Specification (DOCSIS)

### 4. Quick reference data

#### Table 1. Quick reference data

$V_{CCA} = V2$  to V44, V3 to V4 and V41 to V40 = 4.75 V to 5.25 V;

$V_{CCD}$  = V37 to V38 and V15 to V17 = 4.75 V to 5.25 V;  $V_{CCO}$  = V33 to V34 = 3.0 V to 3.6 V; AGND and DGND shorted together;  $T_{amb}$  = -40 °C to 85 °C;  $V_{I(IN)(p-p)} - V_{I(INN)(p-p)}$  = 1.9 V;

$V_{ref} = V_{CCA3} - 1.75 \ V; \ V_{l(cm)} = V_{CCA3} - 1.6 \ V; \ typical \ values \ measured \ at \ V_{CCA} = V_{CCD} = 5 \ V \ and \ V_{CCO} = 3.3 \ V, \ T_{amb} = 25 \ ^{\circ}\text{C} \ and \ C_L = 10 \ pF; \ unless \ otherwise \ specified.$

| Symbol                | Parameter                     | Conditions                                                               | Min  | Тур  | Max         | Unit |

|-----------------------|-------------------------------|--------------------------------------------------------------------------|------|------|-------------|------|

| $V_{CCA}$             | analog supply voltage         |                                                                          | 4.75 | 5.0  | 5.25        | V    |

| $V_{CCD}$             | digital supply voltage        |                                                                          | 4.75 | 5.0  | 5.25        | V    |

| V <sub>CCO</sub>      | output supply voltage         |                                                                          | 3.0  | 3.3  | 3.6         | V    |

| I <sub>CCA</sub>      | analog supply current         |                                                                          | -    | 78   | 87          | mA   |

| I <sub>CCD</sub>      | digital supply current        |                                                                          | -    | 27   | 30          | mA   |

| I <sub>cco</sub>      | output supply current         | $f_{clk}$ = 20 MHz<br>$f_i$ = 400 kHz                                    | -    | 3    | 4           | mA   |

| INL                   | integral non-linearity        | $f_{clk}$ = 20 MHz<br>$f_i$ = 400 kHz                                    | -    | ±2.6 | ±4.5        | LSB  |

| DNL                   | differential<br>non-linearity | $f_{clk}$ = 20 MHz<br>$f_i$ = 400 kHz<br>(no missing code<br>guaranteed) | -    | ±0.5 | +1.1 – 0.95 | LSB  |

| f <sub>clk(max)</sub> | maximum clock                 | ADC1206S040H                                                             | 40   | -    | -           | MHz  |

|                       | frequency                     | ADC1206S055H                                                             | 55   | -    | -           | MHz  |

|                       |                               | ADC1206S070H                                                             | 70   | -    | -           | MHz  |

| P <sub>tot</sub>      | total power dissipation       | $f_{clk}$ = 55 MHz<br>$f_i$ = 20 MHz                                     | -    | 550  | 660         | mW   |

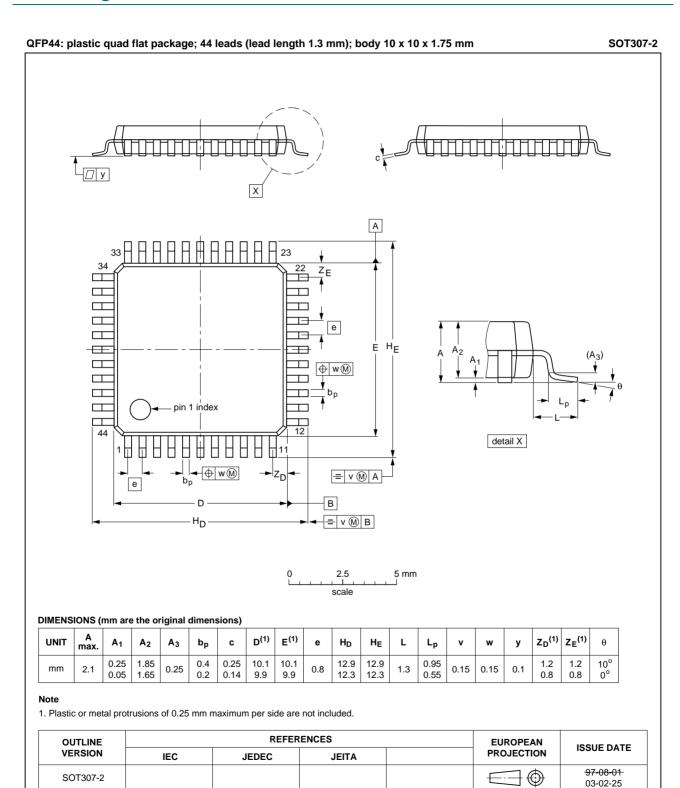

# 5. Ordering information

Table 2. Ordering information

| Type number  | Package |                                                                                                |          |                    |  |  |  |

|--------------|---------|------------------------------------------------------------------------------------------------|----------|--------------------|--|--|--|

|              | Name    | Description                                                                                    | Version  | frequency<br>(MHz) |  |  |  |

| ADC1206S040H | QFP44   | plastic quad flat package; 44 leads (lead length 1.3 mm); body 10 $\times$ 10 $\times$ 1.75 mm | SOT307-2 | 40                 |  |  |  |

| ADC1206S055H | QFP44   | plastic quad flat package; 44 leads (lead length 1.3 mm); body 10 $\times$ 10 $\times$ 1.75 mm | SOT307-2 | 55                 |  |  |  |

| ADC1206S070H | QFP44   | plastic quad flat package; 44 leads (lead length 1.3 mm); body 10 $\times$ 10 $\times$ 1.75 mm | SOT307-2 | 70                 |  |  |  |

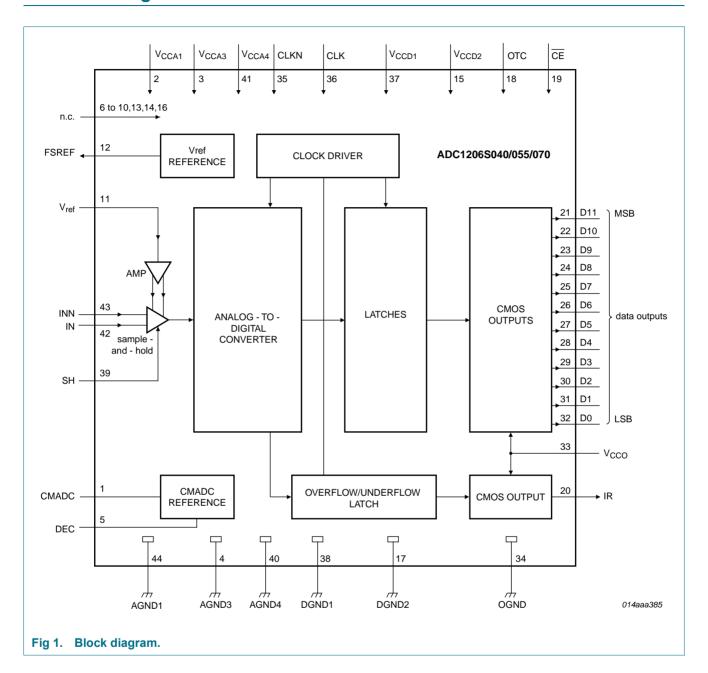

#### **Block diagram** 6.

3 of 31

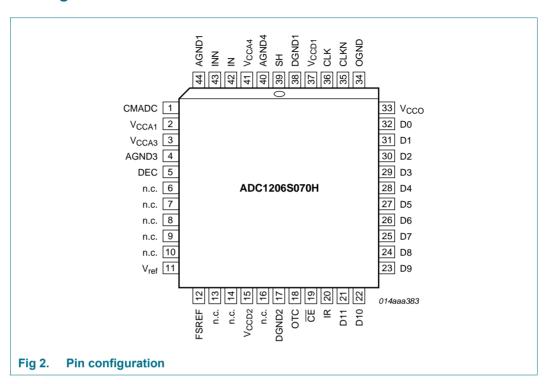

# 7. Pinning information

### 7.1 Pinning

### 7.2 Pin description

Table 3. Pin description

| riii description |                                          |

|------------------|------------------------------------------|

| Pin              | Description                              |

| 1                | regulator output common mode ADC input   |

| 2                | analog supply voltage 1 (5 V)            |

| 3                | analog supply voltage 3 (5 V)            |

| 4                | analog ground 3                          |

| 5                | decoupling node                          |

| 6                | not connected                            |

| 7                | not connected                            |

| 8                | not connected                            |

| 9                | not connected                            |

| 10               | not connected                            |

| 11               | reference voltage input                  |

| 12               | full-scale reference output              |

| 13               | not connected                            |

| 14               | not connected                            |

| 15               | digital supply voltage 2 (5 V)           |

| 16               | not connected                            |

|                  | Pin  1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 |

3ADC1206S040\_055\_070\_3 © IDT 2012. All rights reserved.

Table 3.

Pin description ...continued

| Symbol DGND2 OTC CE IR D11 | Pin 17 18 19 20 | Description digital ground 2 control input twos complement output; active HIGH chip enable input (CMOS level; active LOW) |

|----------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------|

| OTC<br>CE<br>IR            | 18<br>19<br>20  | control input twos complement output; active HIGH chip enable input (CMOS level; active LOW)                              |

| CE<br>IR                   | 19<br>20        | chip enable input (CMOS level; active LOW)                                                                                |

| IR                         | 20              |                                                                                                                           |

|                            |                 |                                                                                                                           |

| D11                        |                 | in-range output                                                                                                           |

| <b>D</b> 1 1               | 21              | data output; bit 11 (Most Significant Bit (MSB))                                                                          |

| D10                        | 22              | data output; bit 10                                                                                                       |

| D9                         | 23              | data output; bit 9                                                                                                        |

| D8                         | 24              | data output; bit 8                                                                                                        |

| D7                         | 25              | data output; bit 7                                                                                                        |

| D6                         | 26              | data output; bit 6                                                                                                        |

| D5                         | 27              | data output; bit 5                                                                                                        |

| D4                         | 28              | data output; bit 4                                                                                                        |

| D3                         | 29              | data output; bit 3                                                                                                        |

| D2                         | 30              | data output; bit 2                                                                                                        |

| D1                         | 31              | data output; bit 1                                                                                                        |

| D0                         | 32              | data output; bit 0 (Least Significant Bit (LSB))                                                                          |

| V <sub>CCO</sub>           | 33              | output supply voltage (3.3 V)                                                                                             |

| OGND                       | 34              | output ground                                                                                                             |

| CLKN                       | 35              | complementary clock input                                                                                                 |

| CLK                        | 36              | clock input                                                                                                               |

| V <sub>CCD1</sub>          | 37              | digital supply voltage 1 (5 V)                                                                                            |

| DGND1                      | 38              | digital ground 1                                                                                                          |

| SH                         | 39              | sample-and-hold enable input (CMOS level; active HIGH)                                                                    |

| AGND4                      | 40              | analog ground 4                                                                                                           |

| V <sub>CCA4</sub>          | 41              | analog supply voltage 4 (5 V)                                                                                             |

| IN                         | 42              | analog input voltage                                                                                                      |

| INN                        | 43              | complementary analog input voltage                                                                                        |

| AGND1                      | 44              | analog ground 1                                                                                                           |

# 8. Limiting values

Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol           | Parameter                 | Conditions                          | Min      | Max  | Unit |

|------------------|---------------------------|-------------------------------------|----------|------|------|

| $V_{CCA}$        | analog supply voltage     |                                     | [1] -0.3 | +7.0 | V    |

| $V_{CCD}$        | digital supply voltage    |                                     | [1] -0.3 | +7.0 | V    |

| V <sub>CCO</sub> | output supply voltage     |                                     | [1] -0.3 | +7.0 | V    |

| $\Delta V_{CC}$  | supply voltage difference | $V_{CCA} - V_{CCD}$                 | -1.0     | +1.0 | V    |

|                  |                           | $V_{CCD} - V_{CCO}$                 | -1.0     | +4.0 | V    |

|                  |                           | V <sub>CCA</sub> – V <sub>CCO</sub> | -1.0     | +4.0 | V    |

Table 4. Limiting values ...continued

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol            | Parameter                        | Conditions                                 | Min        | Max       | Unit |

|-------------------|----------------------------------|--------------------------------------------|------------|-----------|------|

| $V_{i(IN)}$       | input voltage on pin IN          | referenced to AGND                         | 0.3        | $V_{CCA}$ | V    |

| $V_{i(INN)}$      | input voltage on pin INN         |                                            | 0.3        | $V_{CCA}$ | V    |

| $V_{i(clk)(p-p)}$ | peak-to-peak clock input voltage | differential clock drive at pins 35 and 36 | -          | $V_{CCD}$ | V    |

| Io                | output current                   |                                            | -          | 10        | mA   |

| T <sub>stg</sub>  | storage temperature              |                                            | <b>-55</b> | +150      | °C   |

| T <sub>amb</sub>  | ambient temperature              |                                            | -40        | +85       | °C   |

| Tj                | junction temperature             |                                            | -          | 150       | °C   |

<sup>[1]</sup> The supply voltages  $V_{CCA}$ ,  $V_{CCD}$  and  $V_{CCO}$  may have any value between -0.3 V and +7.0 V provided that the supply voltage differences  $\Delta V_{CC}$  are respected.

### 9. Thermal characteristics

Table 5. Thermal characteristics

| Symbol        | Parameter                                   | Conditions  | Тур | Unit |

|---------------|---------------------------------------------|-------------|-----|------|

| $R_{th(j-a)}$ | thermal resistance from junction to ambient | in free air | 75  | K/W  |

### 10. Characteristics

#### Table 6. Characteristics

$V_{CCA}$  = V2 to V44, V3 to V4 and V41 to V40 = 4.75 V to 5.25 V;  $V_{CCD}$  = V37 to V38 and V15 to V17 = 4.75 V to 5.25 V;  $V_{CCO}$  = V33 to V34 = 3.0 V to 3.6 V; AGND and DGND shorted together;  $T_{amb}$  = -40 °C to 85 °C;

$V_{l(IN)(p-p)} - V_{l(INN)(p-p)} = 1.9 \text{ V}; V_{ref} = V_{CCA3} - 1.75 \text{ V}; V_{l(cm)} = V_{CCA3} - 1.6 \text{ V}; typical values measured at } V_{CCA} = V_{CCD} = 5 \text{ V}$  and  $V_{CCO} = 3.3 \text{ V}, T_{amb} = 25 ^{\circ}\text{C}$  and  $C_L = 10 \text{ pF};$  unless otherwise specified.

| Symbol           | Parameter                 | Conditions                                         | Test<br>[1] | Min  | Тур | Max  | Unit |

|------------------|---------------------------|----------------------------------------------------|-------------|------|-----|------|------|

| Supplies         |                           |                                                    |             |      |     |      |      |

| $V_{CCA}$        | analog supply voltage     |                                                    |             | 4.75 | 5.0 | 5.25 | V    |

| $V_{CCD}$        | digital supply<br>voltage |                                                    |             | 4.75 | 5.0 | 5.25 | V    |

| V <sub>CCO</sub> | output supply voltage     |                                                    |             | 3.0  | 3.3 | 3.6  | V    |

| I <sub>CCA</sub> | analog supply current     |                                                    | I           | -    | 78  | 87   | mA   |

| I <sub>CCD</sub> | digital supply current    |                                                    | I           | -    | 27  | 30   | mA   |

| I <sub>CCO</sub> | output supply             | $f_{Clk}$ = 20 MHz; $f_i$ = 400 kHz                | I           | -    | 3   | 4    | mA   |

|                  | current                   | $f_{clk} = 40 \text{ MHz}; f_i = 4.43 \text{ MHz}$ | С           | -    | 6.2 | 9    | mA   |

|                  |                           | $f_{clk}$ = 55 MHz; $f_i$ = 20 MHz                 | I           | -    | 9.5 | 12   | mA   |

| P <sub>tot</sub> | total power dissipation   | $f_{clk}$ = 55 MHz $f_i$ = 20 MHz                  |             | -    | 550 | 660  | mW   |

3ADC1206S040\_055\_070\_3 © IDT 2012. All rights reserved.

Table 6. Characteristics ...continued

$V_{CCA}$  = V2 to V44, V3 to V4 and V41 to V40 = 4.75 V to 5.25 V;  $V_{CCD}$  = V37 to V38 and V15 to V17 = 4.75 V to 5.25 V;  $V_{CCO}$  = V33 to V34 = 3.0 V to 3.6 V; AGND and DGND shorted together;  $T_{amb}$  = -40 °C to 85 °C;

$V_{I(IN)(p-p)} - V_{I(INN)(p-p)} = 1.9 \text{ V}; V_{ref} = V_{CCA3} - 1.75 \text{ V}; V_{I(cm)} = V_{CCA3} - 1.6 \text{ V}; typical values measured at } V_{CCA} = V_{CCD} = 5 \text{ V}$  and  $V_{CCO} = 3.3 \text{ V}, T_{amb} = 25 ^{\circ}\text{C}$  and  $C_L = 10 \text{ pF};$  unless otherwise specified.

| Symbol            | Parameter                                     | Conditions                                             | Test<br>[1] | Min                     | Тур                     | Max                     | Unit      |

|-------------------|-----------------------------------------------|--------------------------------------------------------|-------------|-------------------------|-------------------------|-------------------------|-----------|

| Inputs            |                                               |                                                        |             |                         |                         |                         |           |

| CLK and C         | CLKN referenced to                            | DGND <sup>[2]</sup>                                    |             |                         |                         |                         |           |

| V <sub>IL</sub>   | LOW-level                                     | PECL mode; V <sub>CCD</sub> = 5 V                      | I           | 3.19                    | -                       | 3.52                    | ٧         |

|                   | input voltage                                 | TTL mode                                               | С           | 0                       | -                       | 0.8                     | ٧         |

| V <sub>IH</sub>   | HIGH-level                                    | PECL mode; V <sub>CCD</sub> = 5 V                      | I           | 3.83                    | -                       | 4.12                    | ٧         |

|                   | input voltage                                 | TTL mode                                               | С           | 2.0                     | -                       | V <sub>CCD</sub>        | V         |

| I <sub>IL</sub>   | LOW-level input current                       | $V_{CLK}$ or $V_{CLKN}$ = 3.19 V                       | С           | -10                     | -                       | -                       | μΑ        |

| I <sub>IH</sub>   | HIGH-level input current                      | $V_{CLK}$ or $V_{CLKN}$ = 3.83 V                       | С           | -                       | -                       | 10                      | μΑ        |

| $V_{i(dif)(p-p)}$ | peak-to-peak<br>differential<br>input voltage | AC driving mode;<br>DC voltage level = 2.5 V           | С           | 1                       | 1.5                     | 2.0                     | V         |

| R <sub>i</sub>    | input resistance                              | f <sub>clk</sub> = 55 MHz                              | D           | 2                       | -                       | -                       | kΩ        |

| C <sub>i</sub>    | input<br>capacitance                          | f <sub>clk</sub> = 55 MHz                              | D           | -                       | -                       | 2                       | pF        |

| OTC, SH a         | and CE (referenced                            | I to DGND); see Table 8 and 9                          |             |                         |                         |                         |           |

| V <sub>IL</sub>   | LOW-level input voltage                       |                                                        | I           | 0                       | -                       | 0.8                     | V         |

| V <sub>IH</sub>   | HIGH-level input voltage                      |                                                        | I           | 2.0                     | -                       | $V_{CCD}$               | V         |

| I <sub>IL</sub>   | LOW-level input current                       | V <sub>IL</sub> = 0.8 V                                | I           | -20                     | -                       | -                       | μΑ        |

| I <sub>IH</sub>   | HIGH-level input current                      | V <sub>IH</sub> = 2.0 V                                | I           | -                       | -                       | 20                      | μΑ        |

| IN and INN        | (referenced to AC                             | SND); see Table 7, V <sub>ref</sub> = V <sub>CCA</sub> | 3 – 1.7     | 5 V                     |                         |                         |           |

| I <sub>IL</sub>   | LOW-level input current                       | SH = HIGH                                              | С           | -                       | 10                      | -                       | μΑ        |

| l <sub>IH</sub>   | HIGH-level input current                      | SH = HIGH                                              | С           | -                       | 10                      | -                       | μΑ        |

| R <sub>i</sub>    | input resistance                              | f <sub>i</sub> = 20 MHz                                | D           | -                       | 14                      | -                       | $M\Omega$ |

| Ci                | input<br>capacitance                          | f <sub>i</sub> = 20 MHz                                | D           | -                       | 450                     | -                       | pF        |

| $V_{I(cm)}$       | common-mode input voltage                     | $V_{I(IN)} = V_{I(INN)}$<br>output code 2047           | С           | V <sub>CCA3</sub> – 1.7 | V <sub>CCA3</sub> – 1.6 | V <sub>CCA3</sub> – 1.2 | V         |

| Voltage co        | ontrolled regulato                            | r output CMADC                                         |             |                         |                         |                         |           |

| $V_{O(cm)}$       | common-mode output voltage                    |                                                        | l           | -                       | V <sub>CCA3</sub> – 1.6 | -                       | V         |

| I <sub>load</sub> | load current                                  |                                                        | I           | -                       | 1                       | 2                       | mA        |

3ADC1206S040\_055\_070\_3

Table 6. Characteristics ...continued

$V_{CCA} = V2$  to V44, V3 to V4 and V41 to V40 = 4.75 V to 5.25 V;  $V_{CCD} = V37$  to V38 and V15 to V17 = 4.75 V to 5.25 V;  $V_{CCO} = V33$  to V34 = 3.0 V to 3.6 V; AGND and DGND shorted together;  $T_{amb} = -40$  °C to 85 °C;

$V_{I(INN)(p-p)} - V_{I(INN)(p-p)} = 1.9 \text{ V}; V_{ref} = V_{CCA3} - 1.75 \text{ V}; V_{I(cm)} = V_{CCA3} - 1.6 \text{ V}; typical values measured at } V_{CCA} = V_{CCD} = 5 \text{ V}$  and  $V_{CCO} = 3.3 \text{ V}, T_{amb} = 25 ^{\circ}\text{C}$  and  $C_L = 10 \text{ pF};$  unless otherwise specified.

| Symbol                | Parameter                                     | Conditions                                                                                                              | Test<br>[1]          | Min                     | Тур                                     | Max                       | Unit       |

|-----------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------|-----------------------------------------|---------------------------|------------|

| Voltage in            | put V <sub>ref</sub> <sup>[3]</sup>           |                                                                                                                         |                      |                         |                                         |                           |            |

| V <sub>ref</sub>      | reference<br>voltage                          | full-scale fixed voltage;<br>f <sub>i</sub> = 20 MHz; f <sub>clk</sub> = 55 MHz                                         | С                    | -                       | V <sub>CCA3</sub> – 1.75                | -                         | V          |

| I <sub>ref</sub>      | reference<br>current                          |                                                                                                                         | С                    | -                       | 0.3                                     | 10                        | μΑ         |

| $V_{i(dif)(p-p)}$     | peak-to-peak<br>differential<br>input voltage | $V_{I(IN)(p-p)} - V_{I(INN)(p-p)};$<br>$V_{ref} = V_{CCA3} - 1.75 \text{ V};$<br>$V_{I(cm)} = V_{CCA3} - 1.6 \text{ V}$ | С                    | -                       | 1.9                                     | -                         | V          |

| Voltage co            | ontrolled regulato                            | r output FSREF                                                                                                          |                      |                         |                                         |                           |            |

| V <sub>O(ref)</sub>   | reference<br>output voltage                   | $V_{I(IN)(p-p)} - V_{I(INN)(p-p)} = 1.9 \text{ V}$                                                                      | I                    | -                       | V <sub>CCA3</sub> – 1.75                | -                         | V          |

| Digital out           | puts D11 to D0 a                              | nd IR (referenced to OGND)                                                                                              |                      |                         |                                         |                           |            |

| $V_{OL}$              | LOW-level output voltage                      | I <sub>OL</sub> = 2 mA                                                                                                  | I                    | 0                       | -                                       | 0.5                       | V          |

| V <sub>OH</sub>       | HIGH-level output voltage                     | $I_{OH}$ = $-0.4$ mA                                                                                                    | I                    | V <sub>CCCO</sub> - 0.5 | -                                       | V <sub>CCO</sub>          | V          |

| Io                    | output current                                | 3-state output level between 0.5 V and V <sub>CCO</sub>                                                                 | I                    | -20                     | -                                       | +20                       | μΑ         |

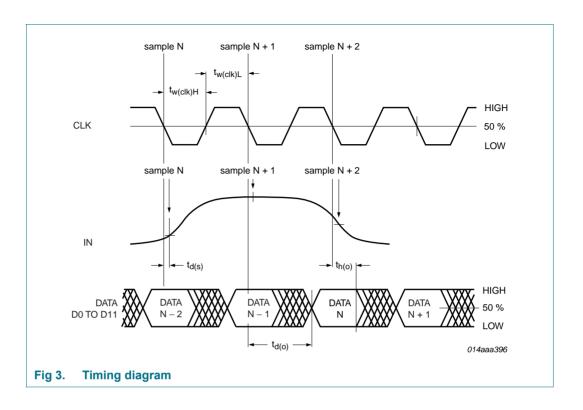

| Switching             | characteristics;                              | Clock frequency f <sub>clk</sub> ; see Fig                                                                              | ure 3                |                         |                                         |                           |            |

| f <sub>clk(min)</sub> | minimum clock frequency                       | SH = HIGH                                                                                                               | С                    | -                       | -                                       | 7                         | MHz        |

| f <sub>clk(max)</sub> |                                               | ADC1206S040H                                                                                                            | С                    | 40                      | -                                       | -                         | MHz        |

|                       | frequency                                     | ADC1206S055H                                                                                                            | I                    | 55                      | -                                       | -                         | MHz        |

|                       |                                               | ADC1206S070H                                                                                                            | С                    | 70                      | -                                       | -                         | MHz        |

| t <sub>w(clk)H</sub>  | HIGH clock pulse width                        | f <sub>i</sub> = 20 MHz                                                                                                 | С                    | 6.8                     | -                                       | -                         | ns         |

| t <sub>w(clk)L</sub>  | LOW clock pulse width                         | f <sub>i</sub> = 20 MHz                                                                                                 | С                    | 6.8                     | -                                       | -                         | ns         |

| Analog si             | gnal processing;                              | 50 % clock duty factor; V <sub>I(IN)(</sub>                                                                             | <sub>(p-p)</sub> - V | $V_{I(INN)(p-p)} = 1.$  | 9 V; V <sub>ref</sub> = V <sub>CC</sub> | <sub>A3</sub> – 1.75 V; s | ee Table 7 |

| Linearity             |                                               |                                                                                                                         |                      |                         |                                         |                           |            |

| INL                   | integral<br>non-linearity                     | $f_{Clk}$ = 20 MHz; $f_i$ = 400 kHz                                                                                     | I                    | -                       | ±2.6                                    | ±4.5                      | LSB        |

| DNL                   | differential<br>non-linearity                 | $f_{clk}$ = 20 MHz; $f_i$ = 400 kHz<br>(no missing code<br>guaranteed)                                                  | I                    | -                       | ±0.5                                    | +1.1 – 0.95               | LSB        |

| Eoffset               | offset error                                  | $V_{CCA} = V_{CCD} = 5 \text{ V};$<br>$V_{CCO} = 3.3 \text{ V};$ $T_{amb} = 25 \text{ °C};$<br>output code = 2047       | С                    | -25                     | +5                                      | +25                       | mV         |

| E <sub>G</sub>        | gain error                                    | spread from device to device; $V_{CCA} = V_{CCD} = 5 \text{ V}$ ; $V_{CCO} = 3.3 \text{ V}$ ; $T_{amb} = 25 \text{ °C}$ | С                    | <b>-7</b>               | -                                       | +7                        | %FS        |

3ADC1206S040\_055\_070\_3

Table 6. Characteristics ...continued

$V_{CCA}$  = V2 to V44, V3 to V4 and V41 to V40 = 4.75 V to 5.25 V;  $V_{CCD}$  = V37 to V38 and V15 to V17 = 4.75 V to 5.25 V;  $V_{CCO}$  = V33 to V34 = 3.0 V to 3.6 V; AGND and DGND shorted together;  $T_{amb}$  = -40 °C to 85 °C;

$V_{I(IN)(p-p)} - V_{I(INN)(p-p)} = 1.9 \text{ V}; V_{ref} = V_{CCA3} - 1.75 \text{ V}; V_{I(cm)} = V_{CCA3} - 1.6 \text{ V}; typical values measured at } V_{CCA} = V_{CCD} = 5 \text{ V}$  and  $V_{CCO} = 3.3 \text{ V}, T_{amb} = 25 ^{\circ}\text{C}$  and  $C_L = 10 \text{ pF};$  unless otherwise specified.

| Symbol               | Parameter                          | Conditions                          | Test<br>[1] | Min | Тур             | Max | Unit |

|----------------------|------------------------------------|-------------------------------------|-------------|-----|-----------------|-----|------|

| Bandwidth            | $(f_{clk} = 55 \text{ MHz})^{[4]}$ |                                     |             |     |                 |     |      |

| В                    | bandwidth                          | -3 dB; full-scale input             | С           | 220 | 245             | -   | MHz  |

| Harmonics            |                                    |                                     |             |     |                 |     |      |

| $\alpha_{2H}$ second |                                    | ADC1206S040H; (f <sub>clk</sub> = 4 | 0 MHz)      |     |                 |     |      |

|                      | harmonic level                     | f <sub>i</sub> = 4.43 MHz           | С           | -   | <b>-78</b>      | -   | dBFS |

|                      |                                    | f <sub>i</sub> = 10 MHz             | С           | -   | <b>-77</b>      | -   | dBFS |

|                      |                                    | f <sub>i</sub> = 15 MHz             | С           | -   | <b>-74</b>      | -   | dBFS |

|                      |                                    | f <sub>i</sub> = 20 MHz             | С           | -   | <del>-7</del> 1 | -   | dBFS |

|                      |                                    | ADC1206S055H; (f <sub>clk</sub> = 5 | 5 MHz)      |     |                 |     |      |

|                      |                                    | f <sub>i</sub> = 4.43 MHz           | С           | -   | <b>-77</b>      | -   | dBFS |

|                      |                                    | f <sub>i</sub> = 10 MHz             | С           | -   | <b>-77</b>      | -   | dBFS |

|                      |                                    | f <sub>i</sub> = 15 MHz             | С           | -   | <b>-76</b>      | -   | dBFS |

|                      |                                    | f <sub>i</sub> = 20 MHz             | I           | -   | <b>-73</b>      | -   | dBFS |

|                      |                                    | ADC1206S070H; (f <sub>clk</sub> = 7 | 0 MHz)      |     |                 |     |      |

|                      |                                    | f <sub>i</sub> = 4.43 MHz           | С           | -   | <b>-76</b>      | -   | dBFS |

|                      |                                    | f <sub>i</sub> = 10 MHz             | С           | -   | <b>-74</b>      | -   | dBFS |

|                      |                                    | f <sub>i</sub> = 15 MHz             | С           | -   | <del>-7</del> 0 | -   | dBFS |

| αзн                  | third harmonic                     | ADC1206S040H; (f <sub>clk</sub> = 4 | 0 MHz)      |     |                 |     |      |

|                      | level                              | f <sub>i</sub> = 4.43 MHz           | С           | -   | <b>−74</b>      | -   | dBFS |

|                      |                                    | f <sub>i</sub> = 10 MHz             | С           | -   | <b>-74</b>      | -   | dBFS |

|                      |                                    | f <sub>i</sub> = 15 MHz             | С           | -   | <b>-74</b>      | -   | dBFS |

|                      |                                    | f <sub>i</sub> = 20 MHz             | С           | -   | <b>-73</b>      | -   | dBFS |

|                      |                                    | ADC1206S055H; (f <sub>clk</sub> = 5 | 5 MHz)      |     |                 |     |      |

|                      |                                    | f <sub>i</sub> = 4.43 MHz           | С           | -   | -74             | -   | dBFS |

|                      |                                    | f <sub>i</sub> = 10 MHz             | С           | -   | -74             | -   | dBFS |

|                      |                                    | f <sub>i</sub> = 15 MHz             | С           | -   | -74             | -   | dBFS |

|                      |                                    | f <sub>i</sub> = 20 MHz             | I           | -   | -72             | -   | dBFS |

|                      |                                    | ADC1206S070H; (f <sub>clk</sub> = 7 | 0 MHz)      |     |                 |     |      |

|                      |                                    | f <sub>i</sub> = 4.43 MHz           | С           | -   | -74             | -   | dBFS |

|                      |                                    | f <sub>i</sub> = 10 MHz             | С           | -   | -74             | -   | dBFS |

|                      |                                    | f <sub>i</sub> = 15 MHz             | С           | -   | -73             | -   | dBFS |

Characteristics ...continued

$V_{CCA} = V2$  to V44, V3 to V4 and V41 to V40 = 4.75 V to 5.25 V;  $V_{CCD} = V37$  to V38 and V15 to V17 = 4.75 V to 5.25 V;  $V_{CCO}$  = V33 to V34 = 3.0 V to 3.6 V; AGND and DGND shorted together;  $T_{amb}$  = -40 °C to 85 °C;

$V_{I(IN)(p-p)} - V_{I(INN)(p-p)} = 1.9 \text{ V}; V_{ref} = V_{CCA3} - 1.75 \text{ V}; V_{I(cm)} = V_{CCA3} - 1.6 \text{ V}; typical values measured at } V_{CCA} = V_{CCD} = 5 \text{ V}$  and  $V_{CCO} = 3.3 \text{ V}, T_{amb} = 25 ^{\circ}\text{C}$  and  $C_L = 10 \text{ pF};$  unless otherwise specified.

| Symbol                      | Parameter                       | Conditions                                      | <b>Test</b> [1] | Min | Тур        | Max | Unit |

|-----------------------------|---------------------------------|-------------------------------------------------|-----------------|-----|------------|-----|------|

| Total harm                  | onic distortion <sup>[5]</sup>  |                                                 |                 |     |            |     |      |

| THD                         | total harmonic                  | ADC1206S040H; (f <sub>clk</sub> = 40 N          | ЛHz)            |     |            |     |      |

|                             | distortion                      | f <sub>i</sub> = 4.43 MHz                       | С               | -   | -68        | -   | dBFS |

|                             |                                 | f <sub>i</sub> = 10 MHz                         | С               | -   | -68        | -   | dBFS |

|                             |                                 | f <sub>i</sub> = 15 MHz                         | С               | -   | -68        | -   | dBFS |

|                             |                                 | f <sub>i</sub> = 20 MHz                         | С               | -   | -68        | -   | dBFS |

|                             |                                 | ADC1206S055H; (f <sub>clk</sub> = 55 N          | ЛHz)            |     |            |     |      |

|                             |                                 | f <sub>i</sub> = 4.43 MHz                       | С               | -   | -68        | -   | dBFS |

|                             |                                 | f <sub>i</sub> = 10 MHz                         | С               | -   | -68        | -   | dBFS |

|                             |                                 | f <sub>i</sub> = 15 MHz                         | С               | -   | -68        | -   | dBFS |

|                             |                                 | f <sub>i</sub> = 20 MHz                         | I               | -   | -68        | -   | dBFS |

|                             |                                 | ADC1206S070H; (f <sub>clk</sub> = 70 N          | ЛHz)            |     |            |     |      |

|                             |                                 | f <sub>i</sub> = 4.43 MHz                       | С               | -   | -68        | -   | dBFS |

|                             |                                 | f <sub>i</sub> = 10 MHz                         | С               | -   | <b>–67</b> | -   | dBFS |

|                             |                                 | f <sub>i</sub> = 15 MHz                         | С               | -   | <b>–67</b> | -   | dBFS |

| Thermal n                   | oise (f <sub>clk</sub> = 55 MHz | 2)                                              |                 |     |            |     |      |

| $N_{\text{th}(\text{RMS})}$ | RMS thermal noise               | shorted input; SH = HIGH;<br>$f_{clk}$ = 55 MHz | С               | -   | 0.45       | -   | LSB  |

| Signal-to-r                 | noise ratio <sup>[6]</sup>      |                                                 |                 |     |            |     |      |

| S/N                         | signal-to-noise                 | ADC1206S040H; $(f_{clk} = 40 \text{ N})$        | ЛHz)            |     |            |     |      |

|                             | ratio                           | f <sub>i</sub> = 4.43 MHz                       | С               | -   | 64         | -   | dBFS |

|                             |                                 | f <sub>i</sub> = 10 MHz                         | С               | -   | 64         | -   | dBFS |

|                             |                                 | f <sub>i</sub> = 15 MHz                         | С               | -   | 64         | -   | dBFS |

|                             |                                 | f <sub>i</sub> = 20 MHz                         | С               | -   | 64         | -   | dBFS |

|                             |                                 | ADC1206S055H; (f <sub>clk</sub> = 55 N          | ЛHz)            |     |            |     |      |

|                             |                                 | f <sub>i</sub> = 4.43 MHz                       | С               | -   | 64         | -   | dBFS |

|                             |                                 | f <sub>i</sub> = 10 MHz                         | С               | -   | 64         | -   | dBFS |

|                             |                                 | f <sub>i</sub> = 15 MHz                         | С               | -   | 64         | -   | dBFS |

|                             |                                 | f <sub>i</sub> = 20 MHz                         | I               | -   | 64         | -   | dBFS |

|                             |                                 | ADC1206S070H; (f <sub>clk</sub> = 70 N          | ЛHz)            |     |            |     |      |

|                             |                                 | f <sub>i</sub> = 4.43 MHz                       | С               | -   | 64         | -   | dBFS |

|                             |                                 | f <sub>i</sub> = 10 MHz                         | С               | -   | 64         | -   | dBFS |

|                             |                                 | f <sub>i</sub> = 15 MHz                         | С               | -   | 63         | -   | dBFS |

|                             |                                 |                                                 |                 |     |            |     |      |

10 of 31

Table 6. Characteristics ...continued

$V_{CCA} = V2$  to V44, V3 to V4 and V41 to V40 = 4.75 V to 5.25 V;  $V_{CCD} = V37$  to V38 and V15 to V17 = 4.75 V to 5.25 V;  $V_{CCO} = V33$  to V34 = 3.0 V to 3.6 V; AGND and DGND shorted together;  $T_{amb} = -40$  °C to 85 °C;

$V_{I(IN)(p-p)} - V_{I(INN)(p-p)} = 1.9 \text{ V}; V_{ref} = V_{CCA3} - 1.75 \text{ V}; V_{I(cm)} = V_{CCA3} - 1.6 \text{ V}; typical values measured at } V_{CCA} = V_{CCD} = 5 \text{ V}$  and  $V_{CCO} = 3.3 \text{ V}, T_{amb} = 25 ^{\circ}\text{C}$  and  $C_L = 10 \text{ pF};$  unless otherwise specified.

| Symbol        | Parameter                              | Conditions                                       | Test<br>[1] | Min | Тур  | Max | Unit |  |  |

|---------------|----------------------------------------|--------------------------------------------------|-------------|-----|------|-----|------|--|--|

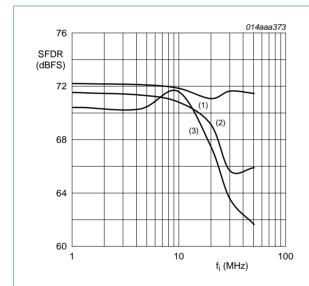

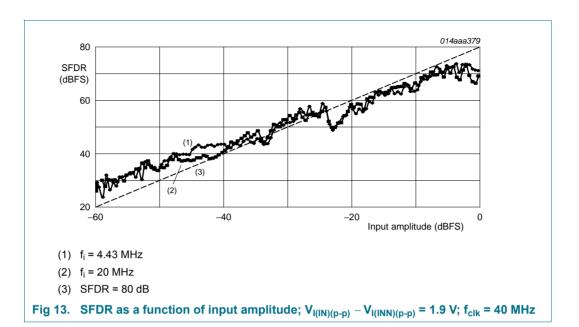

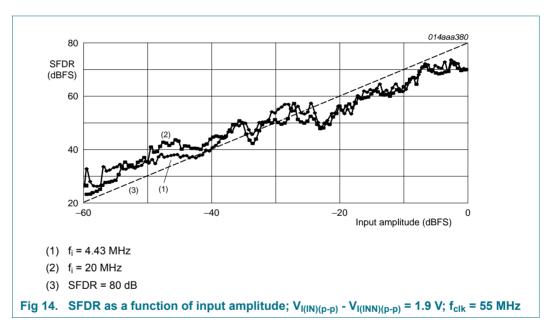

| Spurious fr   | ee dynamic range                       | see Figure 7, 13 and 14                          |             |     |      |     |      |  |  |

| SFDR          | spurious free                          | ADC1206S040H; (f <sub>clk</sub> = 40 MHz)        |             |     |      |     |      |  |  |

|               | dynamic range                          | f <sub>i</sub> = 4.43 MHz                        | С           | -   | 72   | -   | dBFS |  |  |

|               |                                        | f <sub>i</sub> = 10 MHz                          | С           | -   | 71   | -   | dBFS |  |  |

|               |                                        | f <sub>i</sub> = 15 MHz                          | С           | -   | 71   | -   | dBFS |  |  |

|               |                                        | f <sub>i</sub> = 20 MHz                          | С           | -   | 69   | -   | dBFS |  |  |

|               |                                        | ADC1206S055H; (f <sub>clk</sub> = 55 MHz)        |             |     |      |     |      |  |  |

|               |                                        | f <sub>i</sub> = 4.43 MHz                        | С           | -   | 72   | -   | dBFS |  |  |

|               |                                        | f <sub>i</sub> = 10 MHz                          | С           | -   | 71   | -   | dBFS |  |  |

|               |                                        | f <sub>i</sub> = 15 MHz                          | С           | -   | 71   | -   | dBFS |  |  |

|               |                                        | f <sub>i</sub> = 20 MHz                          | I           | -   | 69   | -   | dBFS |  |  |

|               |                                        | ADC1206S070H; (f <sub>clk</sub> = 70 M           | IHz)        |     |      |     |      |  |  |

|               |                                        | f <sub>i</sub> = 4.43 MHz                        | С           | -   | 70   | -   | dBFS |  |  |

|               |                                        | f <sub>i</sub> = 10 MHz                          | С           | -   | 69   | -   | dBFS |  |  |

|               |                                        | f <sub>i</sub> = 15 MHz                          | С           | -   | 69   | -   | dBFS |  |  |

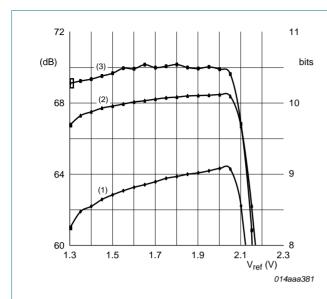

| Effective n   | umber of bits <sup>[7]</sup>           |                                                  |             |     |      |     |      |  |  |

| ENOB          | effective<br>number of bits            | ADC1206S040H; (f <sub>clk</sub> = 40 MHz)        |             |     |      |     |      |  |  |

|               |                                        | f <sub>i</sub> = 4.43 MHz                        | С           | -   | 10.1 | -   | bits |  |  |

|               |                                        | f <sub>i</sub> = 10 MHz                          | С           | -   | 10.1 | -   | bits |  |  |

|               |                                        | f <sub>i</sub> = 15 MHz                          | С           | -   | 10.1 | -   | bits |  |  |

|               |                                        | f <sub>i</sub> = 20 MHz                          | С           | -   | 10   | -   | bits |  |  |

|               |                                        | ADC1206S055H; (f <sub>clk</sub> = 55 M           | lHz)        |     |      |     |      |  |  |

|               |                                        | f <sub>i</sub> = 4.43 MHz                        | С           | -   | 10.1 | -   | bits |  |  |

|               |                                        | f <sub>i</sub> = 10 MHz                          | С           | -   | 10.1 | -   | bits |  |  |

|               |                                        | f <sub>i</sub> = 15 MHz                          | С           | -   | 10   | -   | bits |  |  |

|               |                                        | f <sub>i</sub> = 20 MHz                          | I           | -   | 10   | -   | bits |  |  |

|               |                                        | ADC1206S070H; (f <sub>clk</sub> = 70 MHz)        |             |     |      |     |      |  |  |

|               |                                        | f <sub>i</sub> = 4.43 MHz                        | С           | -   | 10   | -   | bits |  |  |

|               |                                        | f <sub>i</sub> = 10 MHz                          | С           | -   | 10   | -   | bits |  |  |

|               |                                        | f <sub>i</sub> = 15 MHz                          | С           | -   | 10   | -   | bits |  |  |

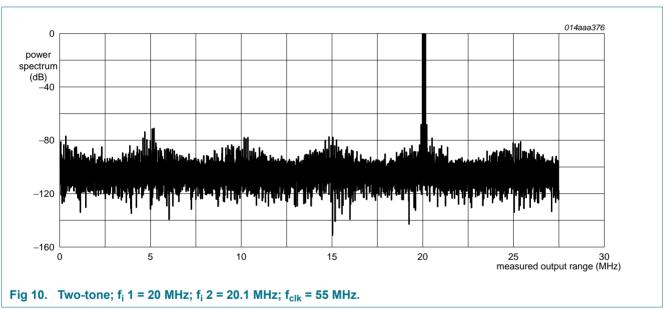

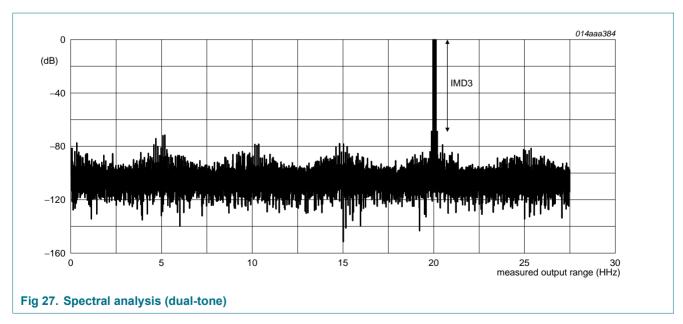

| Two-tone I    | ntermodulation; (f <sub>c</sub>        | $_{lk}$ = 55 MHz; $f_i$ = 20 MHz) <sup>[8]</sup> |             |     |      |     |      |  |  |

| $\alpha_{IM}$ | intermodulation suppression            |                                                  | С           | -   | -68  | -   | dB   |  |  |

| IMD3          | third-order intermodulation distortion |                                                  | С           | -   | -70  | -   | dB   |  |  |

3ADC1206S040\_055\_070\_3

#### Characteristics ... continued

$V_{CCA} = V2$  to V44, V3 to V4 and V41 to V40 = 4.75 V to 5.25 V;  $V_{CCD} = V37$  to V38 and V15 to V17 = 4.75 V to 5.25 V; V<sub>CCO</sub> = V33 to V34 = 3.0 V to 3.6 V; AGND and DGND shorted together; T<sub>amb</sub> = −40 °C to 85 °C;

$V_{I(IN)(p-p)} - V_{I(INN)(p-p)} = 1.9 \text{ V}; V_{ref} = V_{CCA3} - 1.75 \text{ V}; V_{I(cm)} = V_{CCA3} - 1.6 \text{ V};$ typical values measured at  $V_{CCA} = V_{CCD} = 5 \text{ V}$ and  $V_{CCO} = 3.3 \text{ V}$ ,  $T_{amb} = 25 \text{ }^{\circ}\text{C}$  and  $C_{L} = 10 \text{ pF}$ ; unless otherwise specified.

| Symbol                 | Parameter                             | Conditions                                        | Test<br>[1] | Min | Тур               | Max | Unit         |

|------------------------|---------------------------------------|---------------------------------------------------|-------------|-----|-------------------|-----|--------------|

| Bit error rate         | e (f <sub>clk</sub> = 55 MHz)         |                                                   |             |     |                   |     |              |

| BER                    | bit error rate                        | $f_i$ = 20 MHz; $V_I$ = $\pm 16$ LSB at code 2047 | С           | -   | 10 <sup>-14</sup> | -   | times/sample |

| Timing (C <sub>L</sub> | = 10 pF) <sup>[9]</sup>               |                                                   |             |     |                   |     |              |

| $t_{d(s)}$             | sampling delay time                   |                                                   | С           | -   | 0.25              | 1   | ns           |

| $t_{h(o)}$             | output hold<br>time                   |                                                   | С           | 4   | 6.4               | -   | ns           |

| $t_{d(o)}$             | output delay<br>time                  |                                                   | С           | -   | 9.0               | 13  | ns           |

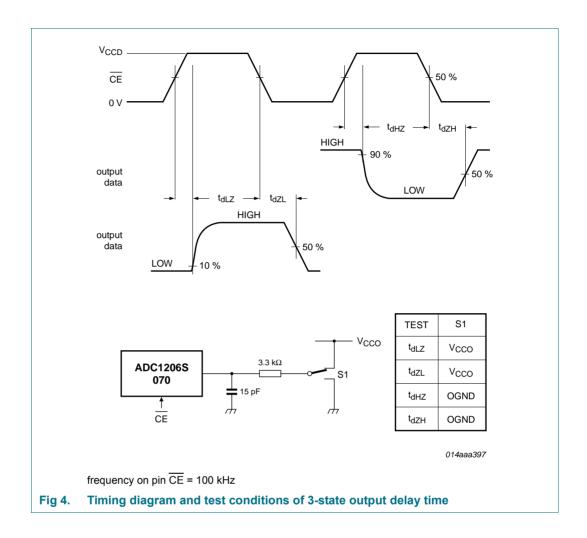

| 3-state out            | put delay times;                      | see Figure 4                                      |             |     |                   |     |              |

| t <sub>dZH</sub>       | float to active<br>HIGH delay<br>time |                                                   | С           | -   | 5.1               | 9.0 | ns           |

| t <sub>dZL</sub>       | float to active<br>LOW delay<br>time  |                                                   | С           | -   | 7.0               | 11  | ns           |

| t <sub>dHZ</sub>       | active HIGH to float delay time       |                                                   | С           | -   | 9.7               | 14  | ns           |

| t <sub>dLZ</sub>       | active LOW to float delay time        |                                                   | С           | -   | 9.5               | 13  | ns           |

- [1] D = guaranteed by design; C = guaranteed by characterization; I = 100 % industrially tested.

- [2] The circuit has two clock inputs: CLK and CLKN. There are 5 modes of operation:

- a) PECL mode 1: (DC level vary 1:1 with V<sub>CCD</sub>) CLK and CLKN inputs are at differential PECL levels.

- b) PECL mode 2: (DC level vary 1:1 with V<sub>CCD</sub>) CLK input is at PECL level and sampling is taken on the falling edge of the clock input signal. A DC level of 3.65 V has to be applied on CLKN decoupled to GND via a 100 nF capacitor.

- c) PECL mode 3: (DC level vary 1:1 with V<sub>CCD</sub>) CLKN input is at PECL level and sampling is taken on the rising edge of the clock input signal. A DC level of 3.65 V has to be applied on CLK decoupled to GND via a 100 nF capacitor.

- d) Differential AC driving mode 4: When driving the CLK input directly and with any AC signal of minimum 1 V (p p) and with a DC level of 2.5 V, the sampling takes place at the falling edge of the clock signal. When driving the CLKN input with the same signal. sampling takes place at the rising edge of the clock signal. It is recommended to decouple the CLKN or CLK input to DGND via a 100 nF capacitor.

- e) TTL mode 1: CLK input is at TTL level and sampling is taken on the falling edge of the clock input signal. In that case the CLKN pin has to be connected to the ground.

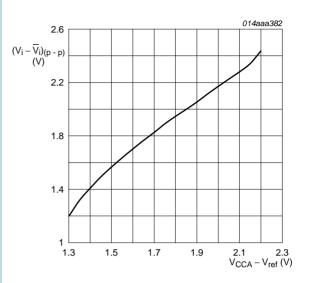

- The ADC input range can be adjusted with an external reference connected to V<sub>ref</sub> pin. This voltage has to be referenced to V<sub>CCA</sub>; see Figure 12.

- The -3 dB analog bandwidth is determined by the 3 dB reduction in the reconstructed output, the input being a full-scale sine wave.

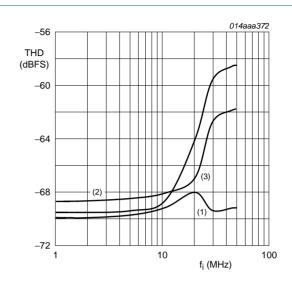

- Total Harmonic Distortion (THD) is obtained with the addition of the first five harmonics:

THD =

$$20 \log \sqrt{\frac{(\alpha_{2H})^2 + (\alpha_{3H})^2 + (\alpha_{4H})^2 + (\alpha_{5H})^2 + (\alpha_{6H})^2}{(\alpha_{1H})^2}}$$

where  $\alpha_{1H}$  is the fundamental harmonic referenced at 0 dB for a full-scale sine wave input; see Figure 6.

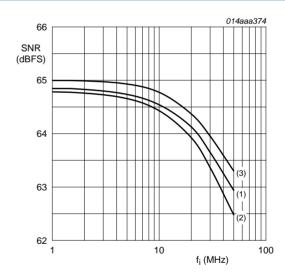

Signal-to-noise ratio (S/N) takes into account all harmonics above five and noise up to Nyquist frequency; see Figure 8.

12 of 31

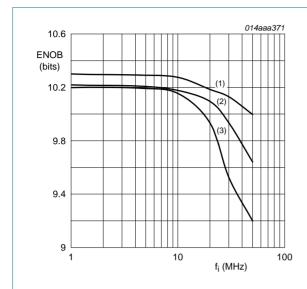

- [7] Effective number of bits are obtained via a fast Fourier transform (FFT). The calculation takes into account all harmonics and noise up to half of the clock frequency (Nyquist frequency). Conversion to Single-to-noise-and-distortion-ratio (SINAD) is given by SINAD = ENOB  $\times$  6.02 + 1.76 dB; see Figure 5.

- Intermodulation measured relative to either tone with analog input frequencies of 20 and 20.1 MHz. The two input signals have the same amplitude and the total amplitude of both signals provides full-scale to the converter (-6 dB below full-scale for each input signal). IMD3 is the ratio of the RMS value of either input tone to the RMS value of the worst case third order intermodulation product.

- Output data acquisition: the output data is available after the maximum delay of  $t_{d(o)}$ ; see Figure 3.

## 11. Additional information relating to Table 6

Table 7. Output coding with differential inputs (typical values to AGND);  $V_{I(IN)(p-p)} - V_{I(INN)(p-p)} = 1.9 \text{ V}, V_{ref} = V_{CCA3} - 1.75 \text{ V}$

|              | - I(II4)(h-h)                  | - I(IIAIA)(h-h)   | , -161       | - CCAS                      |                                   |

|--------------|--------------------------------|-------------------|--------------|-----------------------------|-----------------------------------|

| Code         | V <sub>I(IN)(p-p)</sub><br>(V) | $V_{I(INN)(p-p)}$ | IR           | Binary outputs<br>D11 to D0 | Twos complement outputs D11 to D0 |

| Underflow    | < 3.125                        | < 4.075           | 0            | 0000 0000 0000              | 10 0000 0000 00                   |

| 0            | 3.125                          | 4.075             | 1            | 0000 0000 0000              | 10 0000 0000 00                   |

| 1            | -                              | -                 | 1            | 0000 0000 0001              | 10 0000 0000 01                   |

| $\downarrow$ | -                              | -                 | $\downarrow$ | <b>\</b>                    | $\downarrow$                      |

| 2047         | 3.6                            | 3.6               | $\downarrow$ | 01 1111 1111 11             | 11 1111 1111 11                   |

| $\downarrow$ | -                              | -                 | $\downarrow$ | <b>\</b>                    | $\downarrow$                      |

| 4094         | -                              | -                 | 1            | 1111 1111 1110              | 0111 1111 1110                    |

| 4095         | 4.075                          | 3.125             | 1            | 1111 1111 1111              | 0111 1111 1111                    |

| Overflow     | > 4.075                        | < 3.125           | 0            | 1111 1111 1111              | 0111 1111 1111                    |

#### Table 8. **Mode selection**

| ОТС              | CE | D0 to D11 and IR         |

|------------------|----|--------------------------|

| 0                | 0  | binary; active           |

| 1                | 0  | two's complement; active |

| X <sup>[1]</sup> | 1  | high-impedance           |

<sup>[1]</sup> X = don't care.

Table 9. Sample-and-hold selection

| SH | Sample-and-hold         |

|----|-------------------------|

| 1  | active                  |

| 0  | inactive; tracking mode |

13 of 31

14 of 31

15 of 31

- (1) 40 MHz

- (2) 55 MHz

- (3) 70 MHz

Fig 5. Effective Number Of Bits (ENOB) as a function of input frequency (sample device).

- (1) 40 MHz

- (2) 55 MHz

- (3) 70 MHz

Fig 6. Total Harmonic Distortion (THD) as a function of input frequency (sample device).

- (1) 40 MHz

- (2) 55 MHz

- (3) 70 MHz

Fig 7. Spurious Free Dynamic Range (SFDR) as a function of input frequency (sample device).

- (1) 40 MHz

- (2) 55 MHz

- (3) 70 MHz

Fig 8. Signal-to-Noise ratio (S/N) as a function of input frequency (sample device).

18 of 31

- (1) S/N

- (2) ENOB

- (3) SFDR

Fig 15. ENOB, SFDR and S/R as a function of V<sub>ref</sub>;  $f_{clk}$  = 55 MHz;  $f_i$  = 4.43 MHz

Fig 16. ADC full-scale;  $V_{I(IN)(p\text{-}p)} - V_{I(INN)(p\text{-}p)}$  as a function of  $V_{CCA} - V_{ref}$

20 of 31

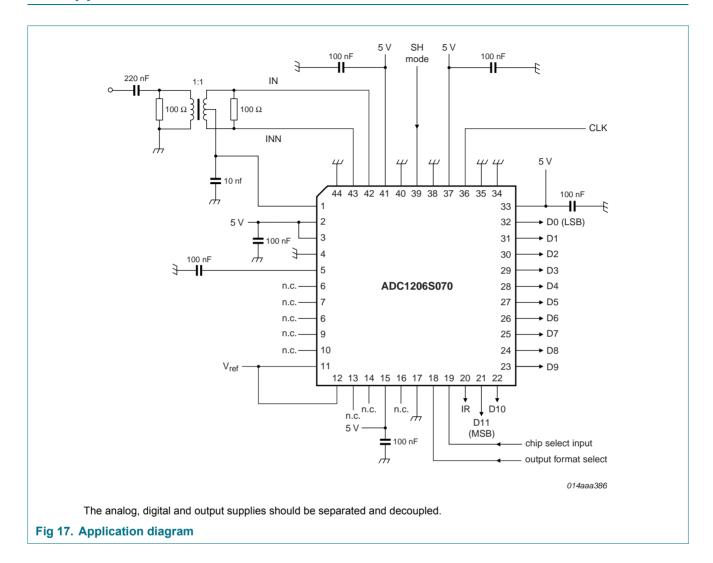

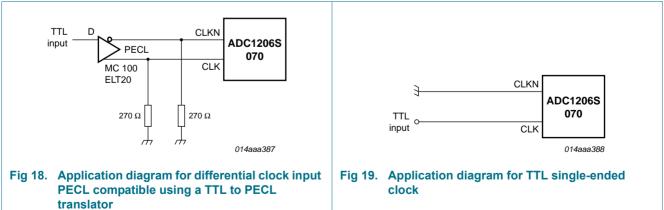

## 12. Application information

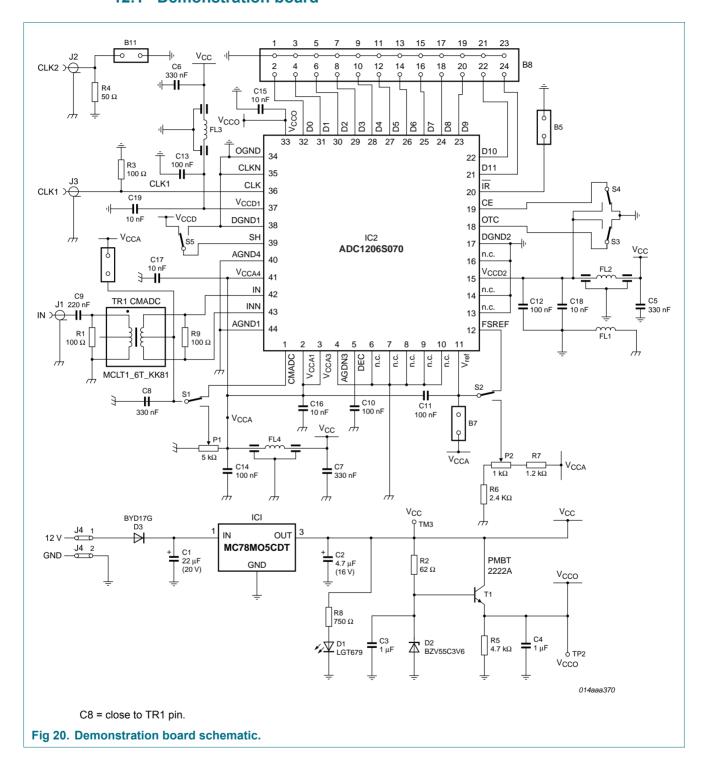

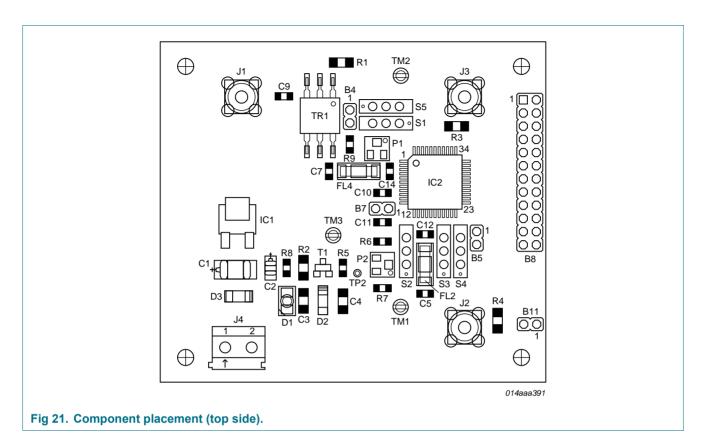

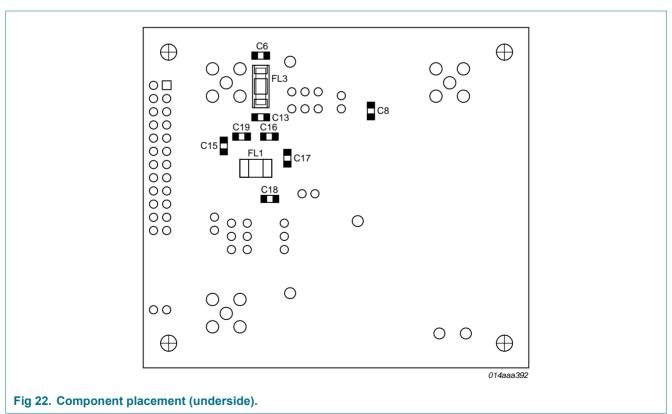

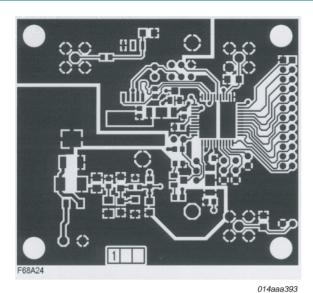

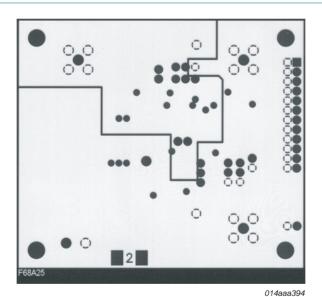

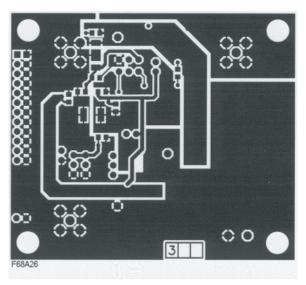

### 12.1 Demonstration board

Fig 23. PCB layout (top layer).

Fig 24. PCB layout (ground layer).

**Product data sheet**

24 of 31

014aaa395

Fig 25. PCB layout (power plane).

### 12.2 Alternative parts

The following alternative parts are also available:

Table 10. Alternative parts

| Type number | Description        |     | Sampling frequency |

|-------------|--------------------|-----|--------------------|

| ADC1006S055 | Single 10 bits ADC | [1] | 55 MHz             |

| ADC1006S070 | Single 10 bits ADC | [1] | 70 MHz             |

<sup>[1]</sup> Pin to pin compatible

### 12.3 Recommended companion chip

The recommended companion chip is the TDA9901 wide band differential digital controlled variable gain amplifier.

# 13. Support information

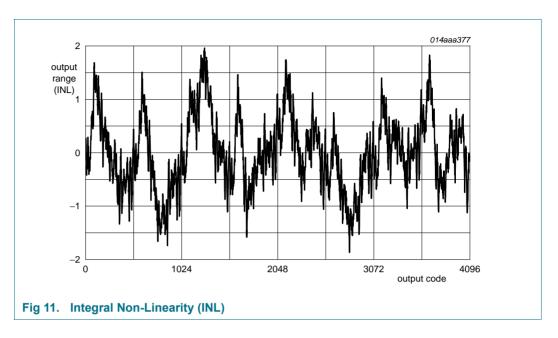

### 13.1 Non-linearities

### 13.1.1 Integral Non-Linearity (INL).

It is defined as the deviation of the transfer function from a best fit straight line (linear regression computation). The INL of the code i is obtained from the equation:

$$INL(i) = \frac{V_{in}(i) - V_{in}(ideal)}{S}$$

where

$$i = 0 \cdot (2^n - 1)$$

and

3ADC1206S040\_055\_070\_3 © IDT 2012. All rights reserved.

S = slope of the ideal straight line = code width; i = code value.

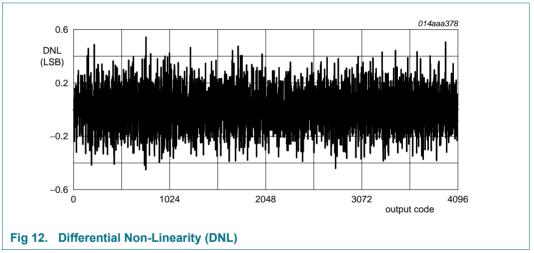

#### 13.1.2 Differential Non-Linearity (DNL).

It is the deviation in code width from the value of 1 LSB.  $DNL(i) = \frac{V_{in}(i+1) - V_{in}(i)}{c} - I$

where

$$i = 0 \cdot (2^n - 2)$$

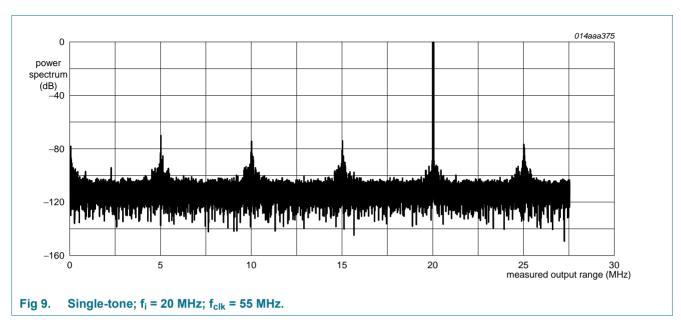

### 13.2 Dynamic parameters (single tone)

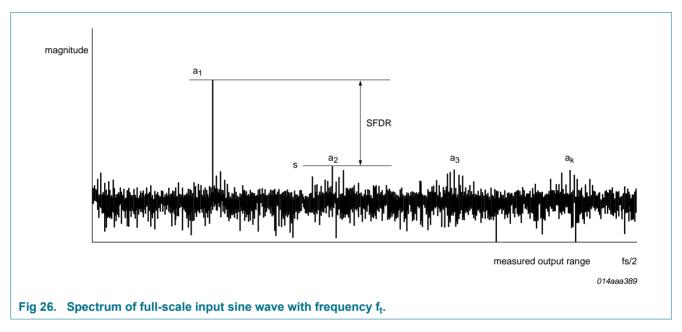

Figure 26 shows the spectrum of a full-scale input sine wave with frequency f<sub>t</sub>, conforming to coherent sampling ( $f_t/f_s = M/N$ , where M is the number of cycles and N is number of samples, M and N being relatively prime), and digitized by the ADC under test.

**Remark:** in the following equations, P<sub>noise</sub> is the power of the terms which include the effects of random noise, non-linearities, sampling time errors, and "quantization noise".

### 13.2.1 Signal-to-noise and distortion (SINAD)

The ratio of the output signal power to the noise-plus-distortion power for a given sample rate and input frequency, excluding the DC component:

$$SINAD[db] = 10log \left[ \frac{P_{signal}}{P_{noise + distortion}} \right]$$

#### 13.2.2 Effective Number Of Bits (ENOB)

**Product data sheet**

Downloaded from Arrow.com.

It is derived from SINAD and gives the theoretical resolution an ideal ADC would require to obtain the same SINAD measured on the real ADC. A good approximation gives:

26 of 31

$$ENOB = (SINAD[dB] - (1 \cdot 76))/(6 \cdot 02)$$

### 13.2.3 Total Harmonic Distortion (THD)

The ratio of the power of the harmonics to the power of the fundamental. For k-1

harmonics the THD is:

$$THD[dB] = 10log \left[ \frac{P_{harmonics}}{P_{signal}} \right]$$

where

$$P_{harmonics} = \alpha |_2^2 + \alpha |_3^2 + \alpha |_k^2$$

$$P_{signal} = \alpha |_{I}^{2}$$

The value of k is usually 6 (i.e. calculation of THD is done on the first 5 harmonics).

### 13.2.4 Signal-to-Noise ratio (S/N)

The ratio of the output signal power to the noise power, excluding the harmonics and the

DC component.

$$S/N[dB] = 10log \left[ \frac{P_{signal}}{P_{noise}} \right]$$

### 13.2.5 Spurious Free Dynamic Range (SFDR)

The number SFDR specifies available signal range as the spectral distance between the amplitude of the fundamental and the amplitude of the largest spurious (harmonic and

non-harmonic, excluding DC component).

$$SFDR[dB] = 20log \frac{\alpha_I}{max(s)}$$

### 13.3 Intermodulation distortion

#### 13.3.1 Spectral analysis (dual-tone)

From a dual-tone input sinusoid ( $f_t$  1 and  $f_t$  2, these frequencies being chosen according to the coherence criterion), the intermodulation distortion products IMD2 and IMD3 (respectively, 2nd and 3rd order components) are defined, as follows.

### 13.3.2 IMD2 (IMD3)

The ratio of the RMS value of either tone to the RMS value of the worst second (third) order intermodulation product.

The total intermodulation distortion IMD is given by

$$IMD[dB] = 10log \left[ \frac{P_{intermod}}{P_{signal}} \right]$$

where,

$$\begin{aligned} P_{intermod} &= \alpha \big|_{im}^2 (f_{t1} - f_{t2}) - \alpha \big|_{im}^2 (f_{t1} + f_{t2}) + \alpha \big|_{im}^2 (f_{t1} - 2f_{t2}) \\ &+ \alpha \big|_{im}^2 (f_{t1} + 2f_{t2}) + \alpha \big|_{im}^2 (2f_{t1} - f_{t2}) + \alpha \big|_{im}^2 (2f_{t1} + f_{t2}) \end{aligned}$$

$$P_{signal} = \alpha^2(f_{tl}) + \alpha^2(f_{t2})$$

and

$$\alpha \big|_{im}^2 (f_t)$$

is the power in the intermodulation component at frequency ft.

### 13.4 Noise Power Ratio (NPR)

When using a notch-filtered broadband white-noise generator as the input to the ADC under test, the Noise Power Ratio is defined as the ratio of the average out-of-notch to the in-notch power spectral density magnitudes for the FFT spectrum of the ADC output sample set.

## 14. Package outline

Fig 28. SOT307-2 (QFP44)

3ADC1206S040\_055\_070\_3 © IDT 2012. All rights reserved.

# 15. Revision history

### Table 11. Revision history

| Document ID           | Release date                                                        | Data sheet status  | Change notice | Supersedes            |  |

|-----------------------|---------------------------------------------------------------------|--------------------|---------------|-----------------------|--|

| ADC1206S040_055_070_3 | 20120702                                                            | Product data sheet | -             | ADC1206S040_055_070_2 |  |

| ADC1206S040_055_070_2 | 20080812                                                            | Product data sheet | -             | ADC1206S040_055_070_1 |  |

| Modifications:        | Corrections made to DNL value in Table 1.                           |                    |               |                       |  |

|                       | <ul> <li>Corrections made to several entries in Table 6.</li> </ul> |                    |               |                       |  |

|                       | <ul> <li>Corrections made to note in Figure 4.</li> </ul>           |                    |               |                       |  |

| ADC1206S040_055_070_1 | 20080612                                                            | Product data sheet | -             | -                     |  |

### 16. Contact information

For more information or sales office addresses, please visit: <a href="http://www.idt.com">http://www.idt.com</a>

## 17. Contents

| 1    | General description 1                         | 13     | Support information                    | 25 |

|------|-----------------------------------------------|--------|----------------------------------------|----|

| 2    | Features                                      | 13.1   | Non-linearities                        | 25 |

| 3    | Applications                                  | 13.1.1 | Integral Non-Linearity (INL)           |    |

| 4    | Quick reference data 2                        | 13.1.2 | Differential Non-Linearity (DNL)       |    |

| _    |                                               | 13.2   | Dynamic parameters (single tone)       | 26 |

| 5    | Ordering information                          | 13.2.1 | Signal-to-noise and distortion (SINAD) | 26 |

| 6    | Block diagram                                 | 13.2.2 | Effective Number Of Bits (ENOB)        |    |

| 7    | Pinning information 4                         | 13.2.3 | Total Harmonic Distortion (THD)        | 27 |

| 7.1  | Pinning                                       | 13.2.4 | Signal-to-Noise ratio (S/N)            | 27 |

| 7.2  | Pin description 4                             | 13.2.5 | Spurious Free Dynamic Range (SFDR)     | 27 |

| 8    | Limiting values 5                             | 13.3   | Intermodulation distortion             |    |

| 0    | Thermal characteristics 6                     | 13.3.1 | Spectral analysis (dual-tone)          | 27 |

| 9    |                                               | 13.3.2 | IMD2 (IMD3)                            | 28 |

| 10   | Characteristics 6                             | 13.4   | Noise Power Ratio (NPR)                |    |

| 11   | Additional information relating to Table 6 13 | 14     | Package outline                        |    |

| 12   | Application information 21                    | 15     | Revision history                       |    |

| 12.1 | Demonstration board                           |        | _                                      |    |

| 12.2 | Alternative parts                             | 16     | Contact information                    | 30 |

| 12.3 | Recommended companion chip                    | 17     | Contents                               | 31 |

|      |                                               |        |                                        |    |