Single 10 bits ADC, up to 30 MHz, 40 MHz or 50 MHz Rev. 04 — 2 July 2012 Product

Product data sheet

#### **General description** 1.

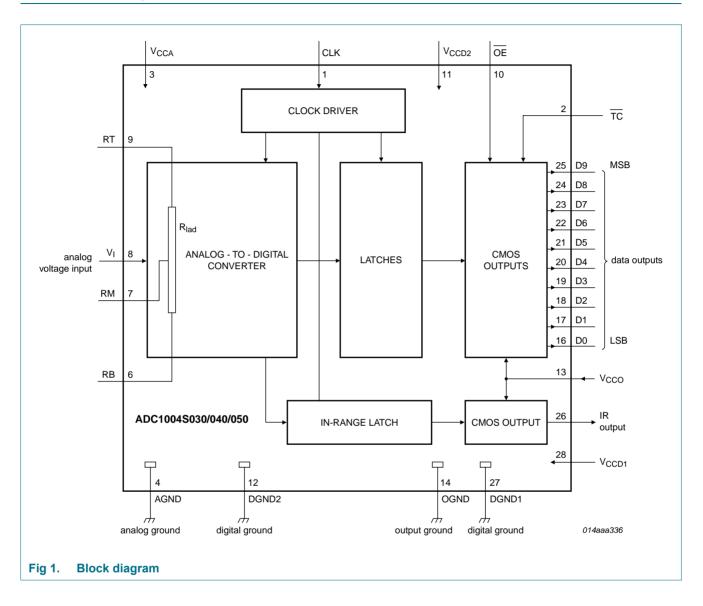

The ADC1004S030/040/050 are a family of 10-bit high-speed low-power Analog-to-Digital Converters (ADC) for professional video and other applications. They convert the analog input signal into 10-bit binary-coded digital signals at a maximum sampling rate of 50 MHz. All digital inputs and outputs are Transistor-Transistor Logic (TTL) and CMOS compatible, although a low-level sine wave clock input signal is allowed.

The device requires an external source to drive its reference ladder. If the application requires that the reference is driven via internal sources, Integrated Device Technology recommends you use one of the ADC1003S030/040/050 family.

#### **Features** 2.

- 10-bit resolution

- Sampling rate up to 50 MHz

- DC sampling allowed

- One clock cycle conversion only

- High signal-to-noise ratio over a large analog input frequency range (9.4 effective bits at 4.43 MHz full-scale input at f<sub>clk</sub> = 40 MHz)

- No missing codes guaranteed

- In-Range (IR) CMOS output

- TTL and CMOS levels compatible digital inputs

- 3 V to 5 V CMOS digital outputs

- Low-level AC clock input signal allowed

- External reference voltage regulator

- Power dissipation only 175 mW (typical)

- Low analog input capacitance, no buffer amplifier required

- No sample-and-hold circuit required

#### **Applications** 3.

- Video data digitizing

- Radar

- Transient signal analysis

- ΣΔ modulators

- Medical imaging

- Barcode scanner

- Global Positioning System (GPS) receiver

Cellular base stations

## 4. Quick reference data

### Table 1. Quick reference data

$V_{CCA} = V3$  to V4 = 4.75 V to 5.25 V;  $V_{CCD} = V11$  to V12 and V28 to V27 = 4.75 V to 5.25 V;  $V_{CCO} = V13$  to V14 = 3.0 V to 5.25 V; AGND and DGND shorted together;  $T_{amb} = 0$  °C to +70 °C; typical values measured at  $V_{CCA} = V_{CCD} = 5$  V and  $V_{CCO} = 3.3$  V;  $V_{i(a)(p-p)} = 2.0$  V; $C_L = 15$  pF and  $T_{amb} = 25$  °C; unless otherwise specified.

| anno                  | , I                        |                                          |      |      |      |      |

|-----------------------|----------------------------|------------------------------------------|------|------|------|------|

| Symbol                | Parameter                  | Conditions                               | Min  | Тур  | Мах  | Unit |

| V <sub>CCA</sub>      | analog supply voltage      |                                          | 4.75 | 5.0  | 5.25 | V    |

| V <sub>CCD</sub>      | digital supply voltage     |                                          | 4.75 | 5.0  | 5.25 | V    |

| V <sub>CCO</sub>      | output supply voltage      |                                          | 3.0  | 3.3  | 5.25 | V    |

| I <sub>CCA</sub>      | analog supply current      |                                          | -    | 18   | 24   | mA   |

| I <sub>CCD</sub>      | digital supply current     |                                          | -    | 16   | 21   | mA   |

| I <sub>CCO</sub>      | output supply current      | f <sub>clk</sub> = 40 MHz;<br>ramp input | -    | 1    | 2    | mA   |

| INL                   | integral non-linearity     | f <sub>clk</sub> = 40 MHz;<br>ramp input | -    | ±0.8 | ±2.0 | LSB  |

| DNL                   | differential non-linearity | f <sub>clk</sub> = 40 MHz;<br>ramp input | -    | ±0.5 | ±0.9 | LSB  |

| f <sub>clk(max)</sub> | maximum clock frequency    | ADC1004S030TS                            | 30   | -    | -    | MHz  |

|                       |                            | ADC1004S040TS                            | 40   | -    | -    | MHz  |

|                       |                            | ADC1004S050TS                            | 50   | -    | -    | MHz  |

| P <sub>tot</sub>      | total power dissipation    | f <sub>clk</sub> = 40 MHz;<br>ramp input | -    | 175  | 247  | mW   |

|                       |                            |                                          |      |      |      |      |

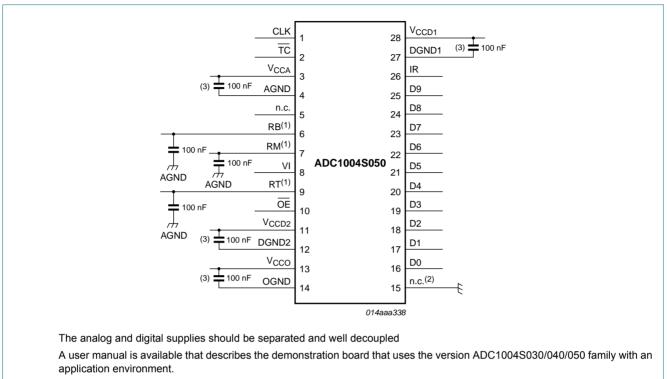

# 5. Ordering information

### Table 2.Ordering information

| Type number   | Package |                                                                      |          |                    |  |  |

|---------------|---------|----------------------------------------------------------------------|----------|--------------------|--|--|

|               | Name    | Description                                                          | Version  | frequency<br>(MHz) |  |  |

| ADC1004S030TS | SSOP28  | plastic shrink small outline package; 28 leads;<br>body width 5.3 mm | SOT341-1 | 30                 |  |  |

| ADC1004S040TS | SSOP28  | plastic shrink small outline package; 28 leads;<br>body width 5.3 mm | SOT341-1 | 40                 |  |  |

| ADC1004S050TS | SSOP28  | plastic shrink small outline package; 28 leads;<br>body width 5.3 mm | SOT341-1 | 50                 |  |  |

Downloaded from Arrow.com.

Single 10 bits ADC, up to 30 MHz, 40 MHz or 50 MHz

# 6. Block diagram

## Single 10 bits ADC, up to 30 MHz, 40 MHz or 50 MHz

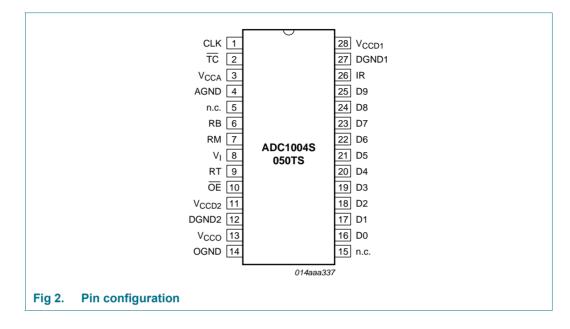

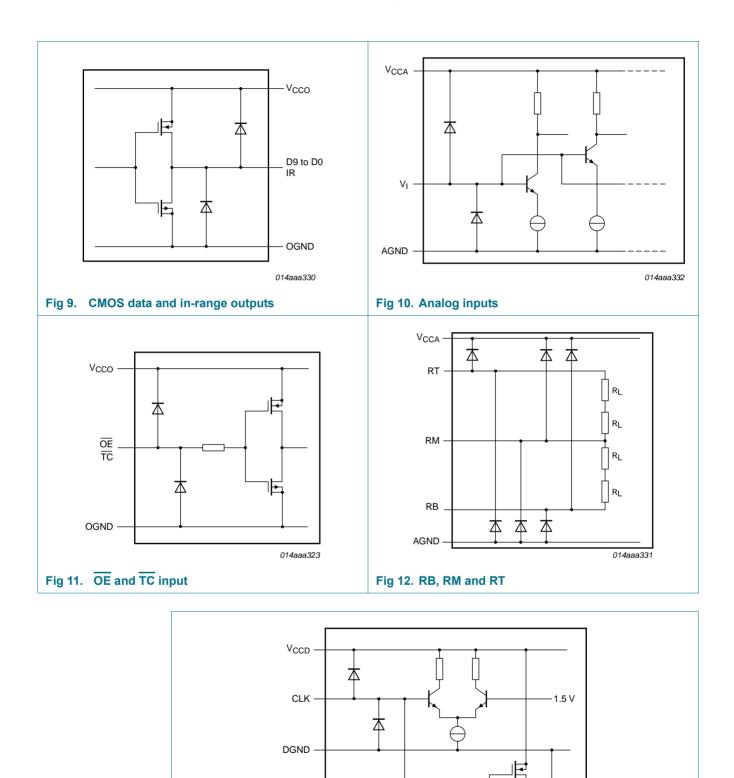

## 7. Pinning information

## 7.1 Pinning

## 7.2 Pin description

| Table 3.          | Pin description |                                                    |

|-------------------|-----------------|----------------------------------------------------|

| Symbol            | Pin             | Description                                        |

| CLK               | 1               | clock input                                        |

| TC                | 2               | two's complement input (active LOW)                |

| V <sub>CCA</sub>  | 3               | analog supply voltage (5 V)                        |

| AGND              | 4               | analog ground                                      |

| n.c.              | 5               | not connected                                      |

| RB                | 6               | reference voltage BOTTOM input                     |

| RM                | 7               | reference voltage MIDDLE                           |

| VI                | 8               | analog input voltage                               |

| RT                | 9               | reference voltage TOP input                        |

| OE                | 10              | output enable input (CMOS level input, active LOW) |

| V <sub>CCD2</sub> | 11              | digital supply voltage 2 (5 V)                     |

| DGND2             | 12              | digital ground 2                                   |

| V <sub>CCO</sub>  | 13              | supply voltage for output stages (3 V to 5 V)      |

| OGND              | 14              | output ground                                      |

| n.c.              | 15              | not connected                                      |

| D0                | 16              | data output; bit 0 (Least Significant Bit (LSB))   |

| D1                | 17              | data output; bit 1                                 |

| D2                | 18              | data output; bit 2                                 |

| D3                | 19              | data output; bit 3                                 |

Single 10 bits ADC, up to 30 MHz, 40 MHz or 50 MHz

| Table 3.          | Pin description | continued                                       |

|-------------------|-----------------|-------------------------------------------------|

| Symbol            | Pin             | Description                                     |

| D4                | 20              | data output; bit 4                              |

| D5                | 21              | data output; bit 5                              |

| D6                | 22              | data output; bit 6                              |

| D7                | 23              | data output; bit 7                              |

| D8                | 24              | data output; bit 8                              |

| D9                | 25              | data output; bit 9 (Most Significant Bit (MSB)) |

| IR                | 26              | in-range data output                            |

| DGND1             | 27              | digital ground 1                                |

| V <sub>CCD1</sub> | 28              | digital supply voltage 1 (5 V)                  |

## 8. Limiting values

## Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol                   | Parameter                           | Conditions            | Min                 | Max              | Unit |

|--------------------------|-------------------------------------|-----------------------|---------------------|------------------|------|

| V <sub>CCA</sub>         | analog supply voltage               |                       | <sup>[1]</sup> –0.3 | +7.0             | V    |

| V <sub>CCD</sub>         | digital supply voltage              |                       | <sup>[1]</sup> –0.3 | +7.0             | V    |

| V <sub>CCO</sub>         | output supply voltage               |                       | <sup>[1]</sup> –0.3 | +7.0             | V    |

| $\Delta V_{CC}$          | supply voltage difference           | $V_{CCA} - V_{CCD}$   | -0.1                | +1.0             | V    |

|                          |                                     | $V_{CCA} - V_{CCO}$   | -0.1                | +4.0             | V    |

|                          |                                     | $V_{CCD} - V_{CCO}$   | -0.1                | +4.0             | V    |

| VI                       | input voltage                       | referenced to<br>AGND | -0.3                | +7.0             | V    |

| V <sub>i(clk)(p-p)</sub> | peak-to-peak clock input<br>voltage | referenced to<br>DGND | -                   | V <sub>CCD</sub> | V    |

| lo                       | output current                      |                       | -                   | 10               | mA   |

| T <sub>stg</sub>         | storage temperature                 |                       | -55                 | +150             | °C   |

| T <sub>amb</sub>         | ambient temperature                 |                       | -40                 | +85              | °C   |

| Tj                       | junction temperature                |                       | -                   | 150              | °C   |

| -                        |                                     |                       |                     |                  |      |

[1] The supply voltages V<sub>CCA</sub>, V<sub>CCD</sub> and V<sub>CCO</sub> may have any value between -0.3 V and +7.0 V provided that the supply voltage differences  $\Delta V_{CC}$  are respected.

# 9. Thermal characteristics

| Table 5.             | Thermal characteristics                     |             |     |      |

|----------------------|---------------------------------------------|-------------|-----|------|

| Symbol               | Parameter                                   | Conditions  | Тур | Unit |

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient | in free air | 110 | K/W  |

# **10. Characteristics**

### Table 6. Characteristics

$V_{CCA}$  = V3 to V4 = 4.75 V to 5.25 V;  $V_{CCD}$  = V11 to V12 and V28 to V27 = 4.75 V to 5.25 V;

$V_{CCO}$  = V13 to V14 = 3.0 V to 5.25 V; AGND and DGND shorted together;  $T_{amb}$  = 0 °C to +70 °C; typical values measured at  $V_{CCA}$  =  $V_{CCD}$  = 5 V and  $V_{CCO}$  = 3.3 V;  $C_L$  = 15 pF and  $T_{amb}$  = 25 °C; unless otherwise specified.

| Symbol                | Parameter                      | Conditions                               | Min   | Тур  | Max               | Unit |

|-----------------------|--------------------------------|------------------------------------------|-------|------|-------------------|------|

| Supply                |                                |                                          |       |      |                   |      |

| V <sub>CCA</sub>      | analog supply voltage          |                                          | 4.75  | 5.0  | 5.25              | V    |

| V <sub>CCD</sub>      | digital supply voltage         |                                          | 4.75  | 5.0  | 5.25              | V    |

| V <sub>CCO</sub>      | output supply voltage          |                                          | 3.0   | 3.3  | 5.25              | V    |

| $\Delta V_{CC}$       | supply voltage difference      | $V_{CCA} - V_{CCD}$                      | -0.20 | -    | +0.20             | V    |

|                       |                                | $V_{CCA} - V_{CCO}$                      | -0.20 | -    | +2.25             | V    |

|                       |                                | $V_{CCD} - V_{CCO}$                      | -0.20 | -    | +2.25             | V    |

| I <sub>CCA</sub>      | analog supply current          |                                          | -     | 18   | 24                | mA   |

| I <sub>CCD</sub>      | digital supply current         |                                          | -     | 16   | 21                | mA   |

| I <sub>CCO</sub>      | output supply current          | f <sub>clk</sub> = 40 MHz;<br>ramp input | -     | 1    | 2                 | mA   |

| P <sub>tot</sub>      | total power dissipation        | f <sub>clk</sub> = 40 MHz;<br>ramp input | -     | 175  | 247               | mW   |

| Inputs                |                                |                                          |       |      |                   |      |

| Clock inpu            | ut CLK (referenced to DGND     | [1]                                      |       |      |                   |      |

| V <sub>IL</sub>       | LOW-level input voltage        |                                          | 0     | -    | 0.8               | V    |

| V <sub>IH</sub>       | HIGH-level input voltage       |                                          | 2     | -    | V <sub>CCD</sub>  | V    |

| IIL                   | LOW-level input current        | V <sub>clk</sub> = 0.8 V                 | -1    | -    | +1                | μA   |

| I <sub>IH</sub>       | HIGH-level input current       | $V_{clk}$ = 2 V                          | -     | 2    | 10                | μΑ   |

| Zi                    | input impedance                | f <sub>clk</sub> = 40 MHz                | -     | 2    | -                 | kΩ   |

| Ci                    | input capacitance              |                                          | -     | 2    | -                 | pF   |

| Inputs OE             | and TC (referenced to DGN      | D); see Table 8                          |       |      |                   |      |

| V <sub>IL</sub>       | LOW-level input voltage        |                                          | 0     | -    | 0.8               | V    |

| V <sub>IH</sub>       | HIGH-level input voltage       |                                          | 2     | -    | V <sub>CCD</sub>  | V    |

| IIL                   | LOW-level input current        | V <sub>IL</sub> = 0.8 V                  | -1    | -    | -                 | μΑ   |

| I <sub>IH</sub>       | HIGH-level input current       | V <sub>IH</sub> = 2 V                    | -     | -    | 1                 | μA   |

| VI (analog            | input voltage referenced to    | AGND)                                    |       |      |                   |      |

| IIL                   | LOW-level input current        | V <sub>I</sub> = V <sub>RB</sub> = 1.3 V | -     | 0    | -                 | μA   |

| I <sub>IH</sub>       | HIGH-level input current       | $V_{I} = V_{RT} = 3.67 V$                | -     | 35   | -                 | μA   |

| Zi                    | input impedance                | f <sub>i</sub> = 4.43 MHz                | -     | 8    | -                 | kΩ   |

| Ci                    | input capacitance              |                                          | -     | 5    | -                 | pF   |

| Referenc              | e voltages for the resistor I  | adder; see Table 7                       |       |      |                   |      |

| V <sub>RB</sub>       | voltage on pin RB              |                                          | 1.2   | 1.3  | 2.45              | V    |

| V <sub>RT</sub>       | voltage on pin RT              |                                          | 3.2   | 3.67 | $V_{CCA}\!-\!0.8$ | V    |

| V <sub>ref(dif)</sub> | differential reference voltage | $V_{RT} - V_{RB}$                        | 2.0   | 2.37 | 3.0               | V    |

| I <sub>ref</sub>      | reference current              | V <sub>RT</sub> – V <sub>RB</sub> = 2.37 | -     | 9.7  | -                 | mA   |

ADC1004S030\_040\_050\_4

### Table 6. Characteristics ...continued

$V_{CCA} = V3$  to V4 = 4.75 V to 5.25 V;  $V_{CCD} = V11$  to V12 and V28 to V27 = 4.75 V to 5.25 V;  $V_{CCO} = V13$  to V14 = 3.0 V to 5.25 V; AGND and DGND shorted together;  $T_{amb} = 0$  °C to +70 °C; typical values measured at  $V_{CCA} = V_{CCD} = 5$  V and  $V_{CCO} = 3.3$  V;  $C_L = 15$  pF and  $T_{amb} = 25$  °C; unless otherwise specified.

| Symbol                 | Parameter                               | Conditions                                                               |     | Min           | Тур  | Max              | Unit |

|------------------------|-----------------------------------------|--------------------------------------------------------------------------|-----|---------------|------|------------------|------|

| R <sub>lad</sub>       | ladder resistance                       |                                                                          |     | -             | 245  | -                | Ω    |

| TC <sub>Rlad</sub>     | ladder resistor temperature coefficient |                                                                          |     | -             | 456  | -                | mΩ/K |

| V <sub>offset</sub>    | offset voltage                          | BOTTOM;<br>V <sub>RT</sub> – V <sub>RB</sub> = 2.37                      | [2] | -             | 175  | -                | mV   |

|                        |                                         | TOP;<br>V <sub>RT</sub> – V <sub>RB</sub> = 2.37                         | [2] | -             | 175  | -                | mV   |

| V <sub>i(a)(p-p)</sub> | peak-to-peak analog input<br>voltage    |                                                                          | [3] | 1.7           | 2.02 | 2.55             | V    |

| Digital ou             | Itputs D9 to D0 and IR (refe            | renced to OGND)                                                          |     |               |      |                  |      |

| V <sub>OL</sub>        | LOW-level output voltage                | I <sub>OL</sub> = 1 mA                                                   |     | 0             | -    | 0.5              | V    |

| V <sub>OH</sub>        | HIGH-level output voltage               | I <sub>OH</sub> = -1 mA                                                  |     | $V_{CCO}-0.5$ | -    | V <sub>CCO</sub> | V    |

| I <sub>O</sub>         | output current                          | in 3-state mode;<br>$0.5 V < V_O < V_{CCO}$                              |     | -20           | -    | +20              | μA   |

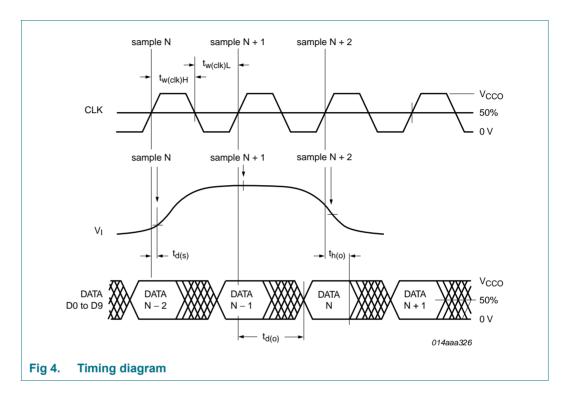

| Switching              | g characteristics; Clock inp            | ut CLK; see Figure 4 <sup>[1]</sup>                                      |     |               |      |                  |      |

| f <sub>clk(max)</sub>  | maximum clock frequency                 | ADC1004S030TS                                                            |     | 30            | -    | -                | MHz  |

|                        |                                         | ADC1004S040TS                                                            |     | 40            | -    | -                | MHz  |

|                        |                                         | ADC1004S050TS                                                            |     | 50            | -    | -                | MHz  |

| t <sub>w(clk)H</sub>   | HIGH clock pulse width                  | full effective<br>bandwidth                                              |     | 8.5           | -    | -                | ns   |

| t <sub>w(clk)L</sub>   | LOW clock pulse width                   | full effective<br>bandwidth                                              |     | 5.5           | -    | -                | ns   |

| Analog s               | ignal processing                        |                                                                          |     |               |      |                  |      |

| Linearity              |                                         |                                                                          |     |               |      |                  |      |

| INL                    | integral non-linearity                  | f <sub>clk</sub> = 40 MHz;<br>ramp input                                 |     | -             | ±0.8 | ±2.0             | LSB  |

| DNL                    | differential non-linearity              | f <sub>clk</sub> = 40 MHz;<br>ramp input                                 |     | -             | ±0.5 | ±0.9             | LSB  |

| E <sub>offset</sub>    | offset error                            | middle code;<br>V <sub>RB</sub> = 1.3 V;<br>V <sub>RT</sub> = 3.67 V     |     | -             | ±1   | -                | LSB  |

| E <sub>G</sub>         | gain error                              | from device to device;<br>$V_{RB}$ = 1.3 V;<br>$V_{RT}$ = 3.67 V         | [4] | -             | ±0.1 | -                | %    |

| Bandwidt               | n (f <sub>clk</sub> = 40 MHz)           |                                                                          |     |               |      |                  |      |

| В                      | bandwidth                               | full-scale sine wave                                                     | [5] | -             | 15   | -                | MHz  |

|                        |                                         | 75 % full-scale sine wave                                                |     | -             | 20   | -                | MHz  |

|                        |                                         | small signal at<br>mid-scale;<br>V <sub>I</sub> = ±10 LSB at code<br>512 |     | -             | 350  | -                | MHz  |

### Table 6. Characteristics ...continued

$V_{CCA} = V3$  to V4 = 4.75 V to 5.25 V;  $V_{CCD} = V11$  to V12 and V28 to V27 = 4.75 V to 5.25 V;  $V_{CCO} = V13$  to V14 = 3.0 V to 5.25 V; AGND and DGND shorted together;  $T_{amb} = 0$  °C to +70 °C; typical values measured at  $V_{CCA} = V_{CCD} = 5$  V and  $V_{CCO} = 3.3$  V;  $C_L = 15$  pF and  $T_{amb} = 25$  °C; unless otherwise specified.

| Symbol           | Parameter                                   | Conditions                                                                                   | Min   | Тур               | Max | Unit          |

|------------------|---------------------------------------------|----------------------------------------------------------------------------------------------|-------|-------------------|-----|---------------|

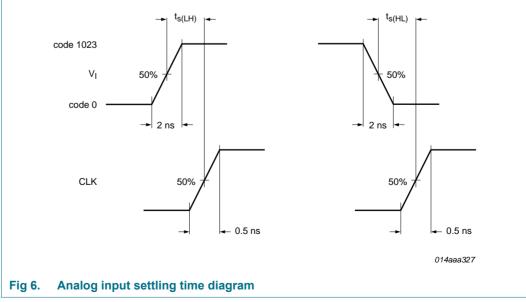

| s(LH)            | LOW to HIGH settling time                   | full-scale square                                                                            | [6] _ | 1.5               | 3.0 | ns            |

| s(HL)            | HIGH to LOW settling time                   | wave; see Figure 6                                                                           | -     | 1.5               | 3.0 | ns            |

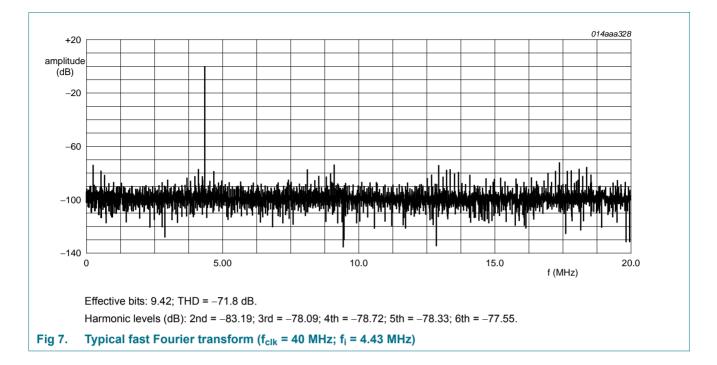

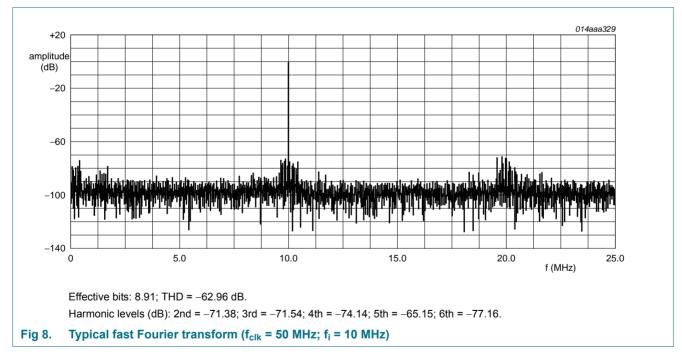

| Harmonic         | s (f <sub>clk</sub> = 40 MHz); see Figure 7 | 7 and 8                                                                                      |       |                   |     |               |

| α <sub>1H</sub>  | first harmonic level                        | f <sub>i</sub> = 4.43 MHz                                                                    | -     | -                 | 0   | dB            |

| α <sub>2H</sub>  | second harmonic level                       | f <sub>i</sub> = 4.43 MHz                                                                    | -     | -75               | -65 | dB            |

| α <sub>3H</sub>  | third harmonic level                        | f <sub>i</sub> = 4.43 MHz                                                                    | -     | -72               | -65 | dB            |

| THD              | total harmonic distortion                   | f <sub>i</sub> = 4.43 MHz                                                                    | -     | -64               | -   | dB            |

| Signal-to-       | noise ratio; see Figure 7 and               | 8[7]                                                                                         |       |                   |     |               |

| S/N              | signal-to-noise ratio                       | full scale;<br>without harmonics;<br>f <sub>clk</sub> = 40 MHz;<br>f <sub>i</sub> = 4.43 MHz | 55    | 58                | -   | dB            |

| Effective I      | oits; see Figure 7 and 8 <sup>[7]</sup>     |                                                                                              |       |                   |     |               |

| ENOB             | effective number of bits                    | ADC1004S030TS;<br>f <sub>clk</sub> = 30 MHz                                                  |       |                   |     |               |

|                  |                                             | f <sub>i</sub> = 4.43 MHz                                                                    | -     | 9.4               | -   | bit           |

|                  |                                             | f <sub>i</sub> = 7.5 MHz                                                                     | -     | 9.1               | -   | bit           |

|                  |                                             | ADC1004S040TS;<br>f <sub>clk</sub> = 40 MHz                                                  |       |                   |     |               |

|                  |                                             | f <sub>i</sub> = 4.43 MHz                                                                    | -     | 9.4               | -   | bit           |

|                  |                                             | f <sub>i</sub> = 7.5 MHz                                                                     | -     | 9.0               | -   | bit           |

|                  |                                             | f <sub>i</sub> = 10 MHz                                                                      | -     | 8.9               | -   | bit           |

|                  |                                             | f <sub>i</sub> = 15 MHz                                                                      | -     | 8.1               | -   | bit           |

|                  |                                             | ADC1004S050TS;<br>f <sub>clk</sub> = 50 MHz                                                  |       |                   |     |               |

|                  |                                             | f <sub>i</sub> = 4.43 MHz                                                                    | -     | 9.3               | -   | bit           |

|                  |                                             | f <sub>i</sub> = 7.5 MHz                                                                     | -     | 8.9               | -   | bit           |

|                  |                                             | f <sub>i</sub> = 10 MHz                                                                      | -     | 8.8               | -   | bit           |

|                  |                                             | f <sub>i</sub> = 15 MHz                                                                      | -     | 8.0               | -   | bit           |

| Two-tone         | intermodulation <sup>[8]</sup>              |                                                                                              |       |                   |     |               |

| α <sub>IM</sub>  | intermodulation<br>suppression              | f <sub>clk</sub> = 40 MHz                                                                    | -     | -69               | -   | dB            |

| Bit error r      | ate                                         |                                                                                              |       |                   |     |               |

| BER              | bit error rate                              | $f_{clk}$ = 40 MHz;<br>$f_i$ = 4.43 MHz;<br>$V_l$ = ±16 LSB at code<br>512                   | -     | 10 <sup>-13</sup> | -   | times/samples |

| Differentia      | al gain <sup>[9]</sup>                      |                                                                                              |       |                   |     |               |

| G <sub>dif</sub> | differential gain                           | f <sub>clk</sub> = 40 MHz;<br>PAL modulated ramp                                             | -     | 0.8               | -   | %             |

### Table 6. Characteristics ...continued

$V_{CCA} = V3$  to V4 = 4.75 V to 5.25 V;  $V_{CCD} = V11$  to V12 and V28 to V27 = 4.75 V to 5.25 V;  $V_{CCO} = V13$  to V14 = 3.0 V to 5.25 V; AGND and DGND shorted together;  $T_{amb} = 0$  °C to +70 °C; typical values measured at  $V_{CCA} = V_{CCD} = 5$  V and  $V_{CCO} = 3.3$  V;  $C_L = 15$  pF and  $T_{amb} = 25$  °C; unless otherwise specified.

| Symbol            | Parameter                                            | Conditions                                       | Min | Тур | Max | Unit |  |

|-------------------|------------------------------------------------------|--------------------------------------------------|-----|-----|-----|------|--|

| Differentia       | Differential phase [9]                               |                                                  |     |     |     |      |  |

| φdif              | differential phase                                   | f <sub>clk</sub> = 40 MHz;<br>PAL-modulated ramp | -   | 0.4 | -   | deg  |  |

| Timing (f         | <sub>clk</sub> = 40 MHz; C <sub>L</sub> = 15 pF); se | e Figure 4 <sup>[10]</sup>                       |     |     |     |      |  |

| t <sub>d(s)</sub> | sampling delay time                                  |                                                  | -   | 3   | -   | ns   |  |

| t <sub>h(o)</sub> | output hold time                                     |                                                  | 4   | -   | -   | ns   |  |

| t <sub>d(o)</sub> | output delay time                                    | V <sub>CCO</sub> = 4.75 V                        | -   | 10  | 13  | ns   |  |

|                   |                                                      | V <sub>CCO</sub> = 3.15 V                        | -   | 12  | 15  | ns   |  |

| CL                | load capacitance                                     |                                                  | -   | -   | 15  | pF   |  |

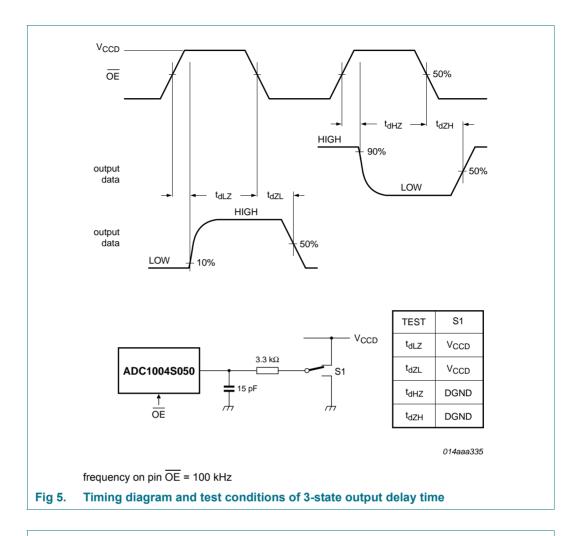

| 3-state or        | utput delay times; see Figur                         | re 5                                             |     |     |     |      |  |

| t <sub>dZH</sub>  | float to active HIGH delay time                      |                                                  | -   | 5.5 | 8.5 | ns   |  |

| t <sub>dZL</sub>  | float to active LOW delay time                       |                                                  | -   | 12  | 15  | ns   |  |

| t <sub>dHZ</sub>  | active HIGH to float delay time                      |                                                  | -   | 19  | 24  | ns   |  |

| t <sub>dLZ</sub>  | active LOW to float delay time                       |                                                  | -   | 12  | 15  | ns   |  |

[1] In addition to a good layout of the digital and analog ground, it is recommended that the rise and fall times of the clock must not be less than 0.5 ns.

- [2] Analog input voltages producing code 0 up to and including code 1023:

- a) V<sub>offset</sub> BOTTOM is the difference between the analog input which produces data equal to 00 and the reference voltage on pin RB (V<sub>RB</sub>) at T<sub>amb</sub> = 25 °C.

- b) V<sub>offset</sub> TOP is the difference between the reference voltage on pin RT (V<sub>RT</sub>) and the analog input which produces data outputs equal to code 1023 at T<sub>amb</sub> = 25 °C.

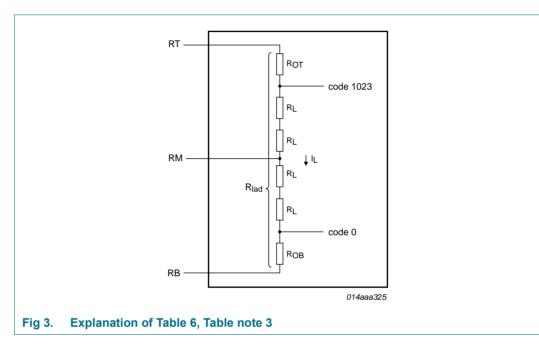

- [3] In order to ensure the optimum linearity performance of such converter architecture the lower and upper extremities of the converter reference resistor ladder (corresponding to output codes 0 and 1023 respectively) are connected to pins RB and RT via offset resistors R<sub>OB</sub> and R<sub>OT</sub> as shown in Figure 3.

- a) The current flowing into the resistor ladder is  $I = \frac{V_{RT} V_{RB}}{R_{OB} + R_L + R_{OT}}$  and the full-scale input range at the converter, to cover code 0

to 1023 is

$$V_I = R_L \times I_L = \frac{R_L}{R_{OB} + R_L + R_{OT}} \times (V_{RT} + V_{RB}) = 0.852 \times (V_{RT} - V_{RB})$$

b) Since R<sub>L</sub>, R<sub>OB</sub> and R<sub>OT</sub> have similar behavior with respect to process and temperature variation, the ratio  $\frac{R_L}{R_{OB} + R_L + R_{OT}}$

will be kept reasonably constant from device to device. Consequently, the variation of the output codes at a given input voltage depends mainly on the difference  $V_{RT} - V_{RB}$  and its variation with temperature and supply voltage. When several ADCs are connected in parallel and fed with the same reference source, the matching between each of them is optimized.

[4]

$$E_G = \frac{(V_{1023} - V_0) - V_{i(p-p)}}{V_{i(p-p)}} \times 100$$

- [5] The analog bandwidth is defined as the maximum input sine wave frequency which can be applied to the device. No glitches greater than 2 LSB, neither any significant attenuation are observed in the reconstructed signal.

- [6] The analog input settling time is the minimum time required for the input signal to be stabilized after a sharp full-scale input (square wave signal) in order to sample the signal and obtain correct output data.

ADC1004S030\_040\_050\_4

## Single 10 bits ADC, up to 30 MHz, 40 MHz or 50 MHz

- [7] Effective bits are obtained via a Fast Fourier Transform (FFT) treatment taking 8000 acquisition points per equivalent fundamental period. The calculation takes into account all harmonics and noise up to half of the clock frequency (Nyquist frequency). Conversion to signal-to-noise ratio: SINAD = ENOB × 6.02 + 1.76 dB.

- [8] Intermodulation measured relative to either tone with analog input frequencies of 4.43 MHz and 4.53 MHz. The two input signals have the same amplitude and the total amplitude of both signals provides full-scale to the converter.

- [9] Measurement carried out using video analyzer VM700A, where the video analog signal is reconstructed through a digital-to-analog converter.

- [10] Output data acquisition: the output data is available after the maximum delay time of t<sub>d(max)</sub>. For 50 MHz version Integrated Device Technology recommends the lowest possible output load.

# **11. Additional information relating to Table 6**

| Table 7. | Output coding and input voltage (typical values; referenced to AGND, V <sub>RB</sub> = 1.3 V, |

|----------|-----------------------------------------------------------------------------------------------|

|          | V <sub>RT</sub> = 3.67 V)                                                                     |

| Code         | V <sub>i(a)(p-p)</sub><br>(V) | IR           | Binary outputs D9 to D0 | Two's complement outputs D9 to D0 |

|--------------|-------------------------------|--------------|-------------------------|-----------------------------------|

| Underflow    | < 1.475                       | 0            | 00 0000 0000            | 10 0000 0000                      |

| 0            | 1.475                         | 1            | 00 0000 0000            | 10 0000 0000                      |

| 1            | -                             | 1            | 00 0000 0001            | 10 0000 0001                      |

| $\downarrow$ | -                             | $\downarrow$ | $\downarrow$            | $\downarrow$                      |

| 1022         | -                             | 1            | 11 1111 1110            | 01 1111 1110                      |

| 1023         | 3.495                         | 1            | 11 1111 1111            | 01 1111 1111                      |

| Overflow     | > 3.495                       | 0            | 11 1111 1111            | 01 1111 1111                      |

|              |                               |              |                         |                                   |

## Single 10 bits ADC, up to 30 MHz, 40 MHz or 50 MHz

| Table 8. | Mode sele | ction                    |                |

|----------|-----------|--------------------------|----------------|

| тс       | OE        | D9 to D0                 | IR             |

| Х        | 1         | high impedance           | high impedance |

| 0        | 0         | active; two's complement | active         |

| 1        | 0         | active; binary           | active         |

ADC1004S030\_040\_050\_4

## Single 10 bits ADC, up to 30 MHz, 40 MHz or 50 MHz

ADC1004S030\_040\_050\_4

## Single 10 bits ADC, up to 30 MHz, 40 MHz or 50 MHz

ADC1004S030\_040\_050\_4

Single 10 bits ADC, up to 30 MHz, 40 MHz or 50 MHz

ADC1004S030\_040\_050\_4

Product data sheet

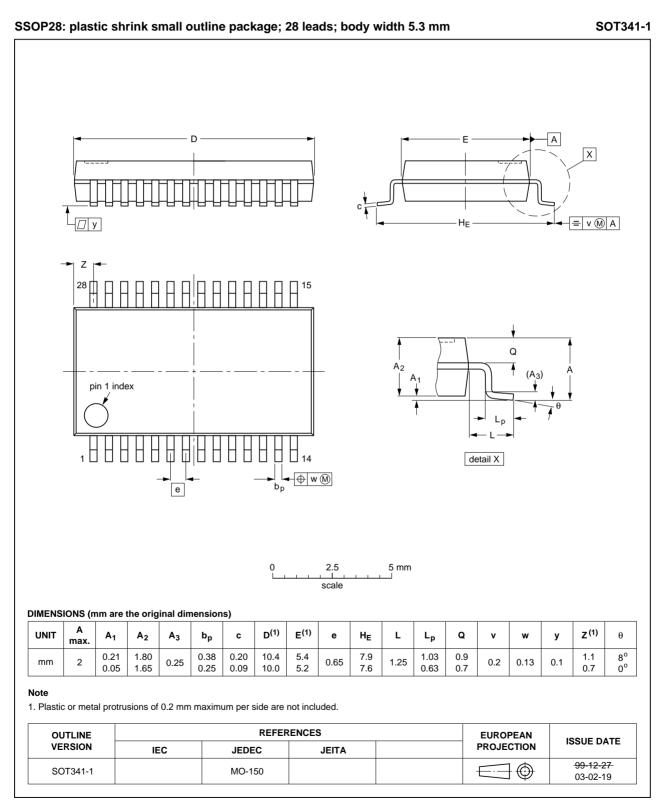

Fig 13. CLK input

© IDT 2012. All rights reserved.

E

014aaa324

Single 10 bits ADC, up to 30 MHz, 40 MHz or 50 MHz

# 12. Application information

- (1) RB, RM and RT are decoupled to AGND.

- (2) Pin 15 may be connected to DGND in order to prevent noise influence.

- (3) Decoupling capacitor for supplies; must be placed close to the device.

Fig 14. Application diagram

## 12.1 Alternative parts

The following alternative parts are also available:

### Table 9. Alternative parts

| Type number | Description                                               | Sampling frequency |

|-------------|-----------------------------------------------------------|--------------------|

| ADC1003S030 | Single 10 bits ADC, with voltage regulator <sup>[1]</sup> | 30 MHz             |

| ADC1003S040 | Single 10 bits ADC, with voltage regulator <sup>[1]</sup> | 40 MHz             |

| ADC1003S050 | Single 10 bits ADC, with voltage regulator <sup>[1]</sup> | 50 MHz             |

| ADC1005S060 | Single 10 bits ADC <sup>[1]</sup>                         | 60 MHz             |

| ADC0804S030 | Single 8 bits ADC <sup>[1]</sup>                          | 30 MHz             |

| ADC0804S040 | Single 8 bits ADC <sup>[1]</sup>                          | 40 MHz             |

| ADC0804S050 | Single 8 bits ADC <sup>[1]</sup>                          | 50 MHz             |

[1] Pin to pin compatible

ADC1004S030\_040\_050\_4

## Single 10 bits ADC, up to 30 MHz, 40 MHz or 50 MHz

# 13. Package outline

### Fig 15. Package outline SOT341-1 (SSOP28)

ADC1004S030\_040\_050\_4

## Single 10 bits ADC, up to 30 MHz, 40 MHz or 50 MHz

# 14. Revision history

| Release date                   | Data sheet status                                                                | Change notice                                                                                                                                                                                                                          | Supersedes                                                                                                                                                                                                                                                       |  |  |

|--------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 20120702                       | Product data sheet                                                               | -                                                                                                                                                                                                                                      | ADC1004S030_040_050_3                                                                                                                                                                                                                                            |  |  |

| 20080807                       | Product data sheet                                                               | -                                                                                                                                                                                                                                      | ADC1004S030_040_050_2                                                                                                                                                                                                                                            |  |  |

| <ul> <li>Correction</li> </ul> | s made to the table description                                                  | on in Table 1.                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                  |  |  |

| <ul> <li>Correction</li> </ul> | s made to several entries in                                                     | Table 6.                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                  |  |  |

| Corrections made to Figure 12. |                                                                                  |                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                  |  |  |

| 20080616                       | Product data sheet                                                               | -                                                                                                                                                                                                                                      | ADC1004S030_040_050_1                                                                                                                                                                                                                                            |  |  |

| 20080611                       | Product data sheet                                                               | -                                                                                                                                                                                                                                      | -                                                                                                                                                                                                                                                                |  |  |

|                                | Release date<br>20120702<br>20080807<br>• Correction<br>• Correction<br>20080616 | Release dateData sheet status20120702Product data sheet20080807Product data sheet• Corrections made to the table description<br>• Corrections made to several entries in<br>• Corrections made to Figure 12.20080616Product data sheet | Release dateData sheet statusChange notice20120702Product data sheet-20080807Product data sheet-• Corrections made to the table description in Table 1• Corrections made to several entries in Table 6• Corrections made to Figure 1220080616Product data sheet- |  |  |

# **15. Contact information**

For more information or sales office addresses, please visit: http://www.idt.com

# 16. Contents

| 1   | General description    | 9  |

|-----|------------------------|----|

| 2   | Features 1             | 10 |

| 3   | Applications           | 11 |

| 4   | Quick reference data 2 | 12 |

| 5   | Ordering information 2 | 12 |

| 6   | Block diagram 3        | 13 |

| 7   | Pinning information 4  | 14 |

| 7.1 | Pinning 4              | 15 |

| 7.2 | Pin description 4      | 16 |

| 8   | Limiting values 5      |    |

| 9    | Thermal characteristics                    | 5  |

|------|--------------------------------------------|----|

| 10   | Characteristics                            | 6  |

| 11   | Additional information relating to Table 6 | 10 |

| 12   | Application information                    | 15 |

| 12.1 | Alternative parts                          | 15 |

| 13   | Package outline                            | 16 |

| 14   | Revision history                           | 17 |

| 15   | Contact information                        | 17 |

| 16   | Contents                                   | 18 |

ADC1004S030\_040\_050\_4