# **High Side** SMART HotPlug<sup>™</sup> IC/Inrush **Limiter/Circuit Breaker**

The NIS5102 is a controller/FET IC that saves design time and reduces the number of components required for a complete hot swap application. It is designed for +12 V applications.

This chip includes a time delay for sequencing applications. It has a dual function OVLO pin that allows multiple units to be ganged together for simultaneous turn-on and shutdown, allowing units to be operated in parallel. It allows for user selectable undervoltage and overvoltage lockout levels. Its unique current limit circuit allows for adjustable current limit levels with no external power resistor. An internal temperature limiting circuit greatly increases the reliability of this device.

#### Features

- Integrated Power Device

- Power Device Thermally Protected

- No External Current Shunt Required

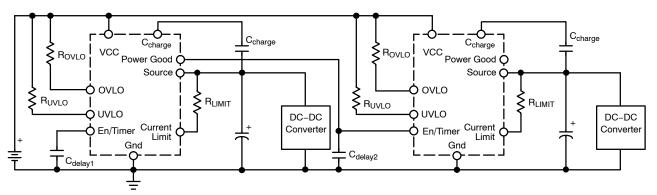

- Simultaneous Shutdown and Startup for Parallel Operation

- Enable/Timer Pin

- Power Good

- 9.0 to 18 V Input Range

- $10 \text{ m}\Omega$

- Main/Mirror MOSFET Current Ratio 1000:1

- Pb-Free Packages are Available

#### **Typical Applications**

- High Availability Systems

- Electronic Circuit Breaker

- 12 V Distributed Architecture

## **ON Semiconductor®**

http://onsemi.com

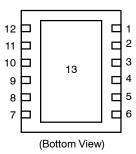

### **PIN CONNECTIONS**

#### **ORDERING INFORMATION**

| lemany Protected                                                                                                             |                                                                                                                  | = vvater Lot                                                 |                                                     |

|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------|

| rent Shunt Required                                                                                                          |                                                                                                                  | Year                                                         |                                                     |

|                                                                                                                              |                                                                                                                  | Work Week                                                    |                                                     |

|                                                                                                                              | u e                                                                                                              | FD-Flee                                                      |                                                     |

|                                                                                                                              | 5.0                                                                                                              |                                                              |                                                     |

| 5                                                                                                                            | PIN C                                                                                                            | CONNECTIO                                                    | ONS                                                 |

| Range                                                                                                                        |                                                                                                                  |                                                              | _                                                   |

|                                                                                                                              | 12 🗖                                                                                                             |                                                              |                                                     |

| SFET Current Ratio 1000:1                                                                                                    |                                                                                                                  |                                                              | <b>2</b>                                            |

| es are Available                                                                                                             | 10                                                                                                               | 10                                                           | <b>d</b> 3                                          |

|                                                                                                                              | 9 🗖                                                                                                              | 13                                                           | <b>d</b> 4                                          |

| ns                                                                                                                           | 8 🗖                                                                                                              |                                                              | <b>5</b>                                            |

| y Systems                                                                                                                    | 7 6                                                                                                              |                                                              |                                                     |

| t Breaker                                                                                                                    |                                                                                                                  |                                                              |                                                     |

|                                                                                                                              |                                                                                                                  |                                                              |                                                     |

| Architecture                                                                                                                 |                                                                                                                  | (Bottom View)                                                | )                                                   |

| Architecture                                                                                                                 |                                                                                                                  | (Bottom View)                                                | )                                                   |

| Architecture                                                                                                                 | ORDERI                                                                                                           | (Bottom View)                                                |                                                     |

| Architecture                                                                                                                 | ORDERI                                                                                                           |                                                              |                                                     |

| Architecture<br>PIERSER<br>PIERSER<br>PIERSER                                                                                | ORDERI<br>Device<br>NIS5102QP1HT1<br>(Latchoff)                                                                  | NG INFORM                                                    | IATION                                              |

| utdown and Startup for Parallel Operation  Range  SFET Current Ratio 1000:1  s are Available  Systems t Breaker Architecture | ORDERI<br>Device<br>NIS5102QP1HT1<br>(Latchoff)<br>NIS5102QP1HT1G<br>(Latchoff)                                  | NG INFORM<br>Package<br>9x9 mm<br>12 Pin PLLP                | AATION<br>Shipping <sup>†</sup><br>1500/Tape & Reel |

| Architecture                                                                                                                 | ORDERI<br>Device<br>NIS5102QP1HT1<br>(Latchoff)<br>NIS5102QP1HT1G<br>(Latchoff)<br>NIS5102QP2HT1<br>(Auto–Retry) | NG INFORM<br>Package<br>9x9 mm<br>12 Pin PLLP<br>12 Pin PLLP | AATION<br>Shipping <sup>†</sup><br>1500/Tape & Reel |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

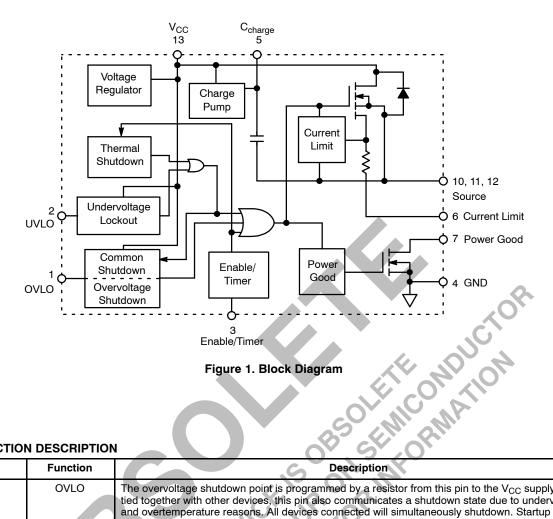

#### **PIN FUNCTION DESCRIPTION**

| Pin        | Function            | Description                                                                                                                                                                                                                                                                                                                                                  |  |

|------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1          | OVLO                | The overvoltage shutdown point is programmed by a resistor from this pin to the V <sub>CC</sub> supply. When tied together with other devices, this pin also communicates a shutdown state due to undervoltage and overtemperature reasons. All devices connected will simultaneously shutdown. Startup for this condition may be simultaneous or sequenced. |  |

| 2          | UVLO                | A resistor from $V_{CC}$ to the UVLO pin adjusts the voltage at which the device will turn on.                                                                                                                                                                                                                                                               |  |

| 3          | Enable/Timer        | A high level signal on this pin allows the device to begin operation. Connection of a capacitor will delay turn on for timing purposes. A low input signal inhibits the operation, and communicates to any other paralleled devices (via the OVLO pin) to shutdown. This signal can also be used to reset the thermal latch.                                 |  |

| 4          | Ground              | Negative input voltage to the device. This is used as the internal reference for the IC.                                                                                                                                                                                                                                                                     |  |

| 5          | C <sub>charge</sub> | An external capacitor is required from this pin to the source pin. This is the storage capacitor for the internal charge pump. A small internal capacitor is included for noise filtering.                                                                                                                                                                   |  |

| 6          | I <sub>LIMIT</sub>  | A resistor (R <sub>LIMIT</sub> ) tied from this pin to the source pin sets the current limit level.                                                                                                                                                                                                                                                          |  |

| 7          | Power Good          | A high impedance signal on this pin indicates that the power device is conducting.                                                                                                                                                                                                                                                                           |  |

| 8, 9       | No Connection       | -                                                                                                                                                                                                                                                                                                                                                            |  |

| 10, 11, 12 | Source              | Source of power FET, which is also the switching node for the load.                                                                                                                                                                                                                                                                                          |  |

| 13         | V <sub>CC</sub>     | Positive input voltage to the device.                                                                                                                                                                                                                                                                                                                        |  |

| Rating                                                                                        | Symbol            | Value        | Unit         |

|-----------------------------------------------------------------------------------------------|-------------------|--------------|--------------|

| Input Voltage, Operating, Steady-State (Input + to Input -)                                   | V <sub>in</sub>   | –0.3 to 18   | V            |

| Input Voltage, Operating, Transient (Input + to Input -), 1 second                            | V <sub>in</sub>   | –0.3 to 25   | V            |

| Drain Voltage, Operating, Steady-State (Drain to Input -)                                     | V <sub>DD</sub>   | –0.3 to 18   | V            |

| Drain Voltage, Operating, Transient (Drain to Input -), 1 second                              | V <sub>DD</sub>   | -0.3 to 25   | V            |

| Drain Current, Peak                                                                           | I <sub>Dpk</sub>  | 20           | А            |

| Continuous Current (T <sub>A</sub> = $25^{\circ}$ C, 0.5 in <sup>2</sup> pad)                 | I <sub>Davg</sub> | 10           | А            |

| Voltage on Power Good Pin (Pin 7)                                                             | V <sub>max7</sub> | 20           | V            |

| Thermal Resistance, Junction-to-Air<br>0.5 in <sup>2</sup> Copper<br>1 in <sup>2</sup> Copper | Q <sub>JA</sub>   | 76.5<br>41.2 | °C/W<br>°C/W |

| Thermal Resistance, Junction-to-Lead                                                          | Q <sub>JL</sub>   | 3.2          | °C/W         |

| Power Dissipation ( $T_A = 25^{\circ}C$ , 0.5 in <sup>2</sup> pad)                            | P <sub>max</sub>  | 1.4          | W            |

| Operating Temperature Range (Note 1)                                                          | TJ                | -40 to 175   | °C           |

| Non-Operating Temperature Range                                                               | TJ                | -55 to 175   | °C           |

| Lead Temperature, Soldering (10 Sec)                                                          | TL                | 235          | °C           |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

1. Actual maximum junction temperature is limited by an internal protection circuit and will not reach the absolute maximum temperature as specified.

## **ELECTRICAL CHARACTERISTICS** (V<sub>CC</sub> = 12 V, R<sub>LIMIT</sub> = 36 $\Omega$ , C<sub>Charge</sub> = 100 pF, T<sub>J</sub> = 25°C unless otherwise noted.)

| Characteristic                                                                                                   | Symbol             | Min   | Тур   | Max   | Unit    |

|------------------------------------------------------------------------------------------------------------------|--------------------|-------|-------|-------|---------|

| POWER FET                                                                                                        | L 4.               |       |       |       |         |

| Delay Time (Enable High to I <sub>S</sub> = 100 mA)                                                              | T <sub>dly</sub>   | -     | 2.0   | -     | ms      |

| Charging Time (I <sub>S</sub> = 100 mA to I <sub>S</sub> = 5.0 A, R <sub>LIMIT</sub> = 36 $\Omega$ )             | 0 t <sub>chg</sub> | -     | 1.0   | -     | ms      |

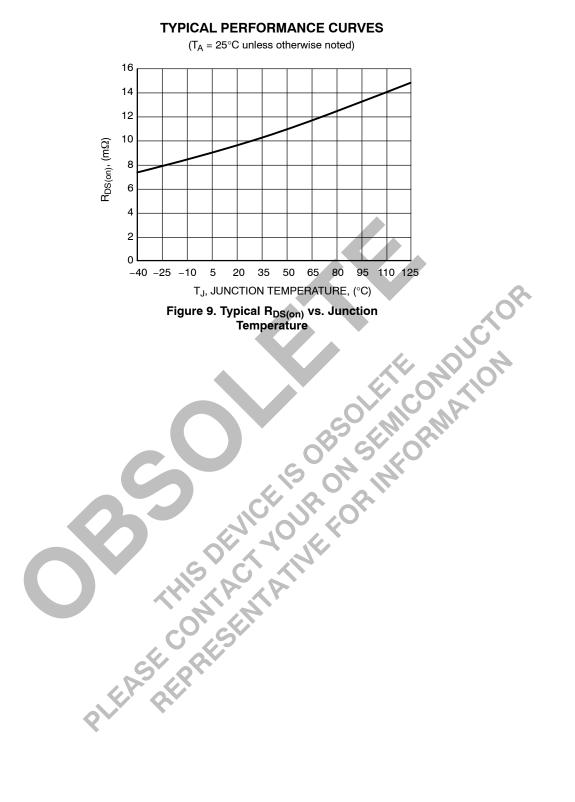

| ON Resistance (V <sub>CC</sub> = 12 V, I <sub>S</sub> = 5.0 A) (Note 2)                                          | R <sub>DSon</sub>  | -     | 10    | 13    | mΩ      |

| Zero Gate Voltage Drain Current<br>(V <sub>DS</sub> = 12 V <sub>dc</sub> , V <sub>GS</sub> = 0 V <sub>dc</sub> ) | I <sub>DSS1</sub>  | -     | -     | 10    | μΑ      |

| Zero Gate Voltage Drain Current<br>(V <sub>DS</sub> = 18 V <sub>dc</sub> , V <sub>GS</sub> = 0 V <sub>dc</sub> ) | I <sub>DSS2</sub>  | -     | -     | 100   | μΑ      |

| Output Capacitance ( $V_{DS}$ = 12 $V_{dc}$ , $V_{GS}$ = 0 $V_{dc}$ , f = 10 kHz)                                | -                  | -     | -     | -     | pF      |

| THERMAL LIMIT                                                                                                    |                    |       |       |       |         |

| Shutdown Temperature (Note 3)                                                                                    | T <sub>SD</sub>    | 125   | 135   | 145   | °C      |

| Hysteresis (Note 3)                                                                                              | T <sub>hyst</sub>  | -     | 40    | -     | °C      |

| OVER/UNDERVOLTAGE                                                                                                |                    |       |       |       |         |

| UVLO Turn-on (Input + Increasing, Rext <sub>UVLO</sub> = 620 k)                                                  | V <sub>on</sub>    | 10.05 | 11.15 | 12.30 | V       |

| UVLO Hysteresis (Input + Decreasing, Rext <sub>UVLO</sub> = 620 k)                                               | V <sub>hyst</sub>  | 0.45  | 0.62  | 0.75  | V       |

| OVLO Turn-off (Input + Increasing, Rext <sub>UVLO</sub> = 620 k)                                                 | V <sub>off</sub>   | 14.0  | 16.4  | 19.0  | V       |

| OVLO Hysteresis (Input + Decreasing, Rext <sub>UVLO</sub> = 620 k)                                               |                    | 0.6   | 0.78  | 1.0   | V       |

| PARALLEL SHUTDOWN (Alternate Function on OVLO Pin)                                                               |                    |       |       |       |         |

| Device Fan-out (Minimum External Resistor Value = 2.0 k $\Omega$ (Note 3)                                        | N <sub>fan</sub>   | -     | -     | 4.0   | Devices |

| Shutdown Voltage Threshold (OVLO Pin)                                                                            | V <sub>SD</sub>    | 0.6   | 0.8   | -     | V       |

| Shutdown State Output Voltage (Isink = 2.0 mA)                                                                   | Vlow               | -     | 0.3   | 0.4   | V       |

| 2 Pulse Test: Pulse width 300 us. duty cycle 2%                                                                  |                    |       |       |       |         |

2. Pulse Test: Pulse width 300  $\mu s,$  duty cycle 2%.

3. Verified by design.

| Characteristic                                                                               |                      | Min | Тур      | Max        | Unit   |

|----------------------------------------------------------------------------------------------|----------------------|-----|----------|------------|--------|

| CURRENT LIMIT                                                                                |                      |     |          |            |        |

| Current Limit (Short Circuit, $R_{LIMIT}$ = 36 $\Omega$ )                                    | I <sub>LIM1</sub>    | 3.8 | 4.8      | 5.8        | А      |

| Current Limit (Overload, R <sub>LIMIT</sub> = 36 Ω) (Note 3)                                 |                      | 7.0 | 7.8      | 8.6        | А      |

| ENABLE/TIMER                                                                                 |                      | •   |          | <u> </u>   |        |

| Enable Voltage (Turn-On)                                                                     | V <sub>ENon</sub>    | 2.2 | -        | -          | V      |

| Enable Voltage (Turn-Off)                                                                    | V <sub>ENoff</sub>   | -   | -        | 1.6        | V      |

| Charging Current (Into External Capacitor)                                                   | I <sub>Charge</sub>  | 65  | 77       | 88         | μΑ     |

| Turn-on Delay (Time from Enable High to I <sub>source</sub> = 100 mA)                        |                      | -   | 2.2      | -          | ms     |

| CHARGE PUMP                                                                                  |                      |     |          |            |        |

| $C_{Charge}$ (Voltage on Pin 5 with Respect to Ground) $V_{CC}$ = 18 Vdc                     | V <sub>Ccharge</sub> | _   | 18<br>26 | -          | V<br>V |

| POWER GOOD                                                                                   |                      |     |          | \$         |        |

| Power Good $\rightarrow$ High Z Signal when FET is Fully Enhanced                            | -                    | -   | -~       | <b>D</b> - | -      |

| Low Z State Output Voltage (I <sub>Sink</sub> = 2 mA)                                        | Vpin7                | -   | 230      | 300        | mV     |

| Leakage Current (Vpin7 = 12 V, High Z State)                                                 | I <sub>Leak</sub>    |     | 2.0      | 10         | μΑ     |

| Power Good Delay<br>(Time from Power FET is Fully Enhanced to Power Good FET Changing State) | t <sub>pwrgood</sub> | 01  | 15       | -          | ms     |

| TOTAL DEVICE                                                                                 | 0                    |     |          |            |        |

| Bias Current (Operational, V <sub>CC</sub> = 12 V)                                           | I <sub>Bias</sub>    |     | 1.3      | 2.0        | mA     |

| Bias Current (Non-operational, V <sub>CC</sub> = 7 V))                                       | I <sub>Bias</sub>    | 0-  | 400      | 700        | μΑ     |

| Minimum Operating Voltage                                                                    | Vcc <sub>min</sub>   | -   | 8.5      | 9.0        | V      |

| ng Voltage                |                           | S | Vcc <sub>min</sub> |

|---------------------------|---------------------------|---|--------------------|

| 0                         | - Will                    |   | FOR                |

|                           | Output Current            |   | P                  |

| $\mathbf{O}^{\mathbf{v}}$ | Source Voltage            |   |                    |

|                           | Enable/Timer<br>Threshold |   |                    |

| PLE                       |                           |   |                    |

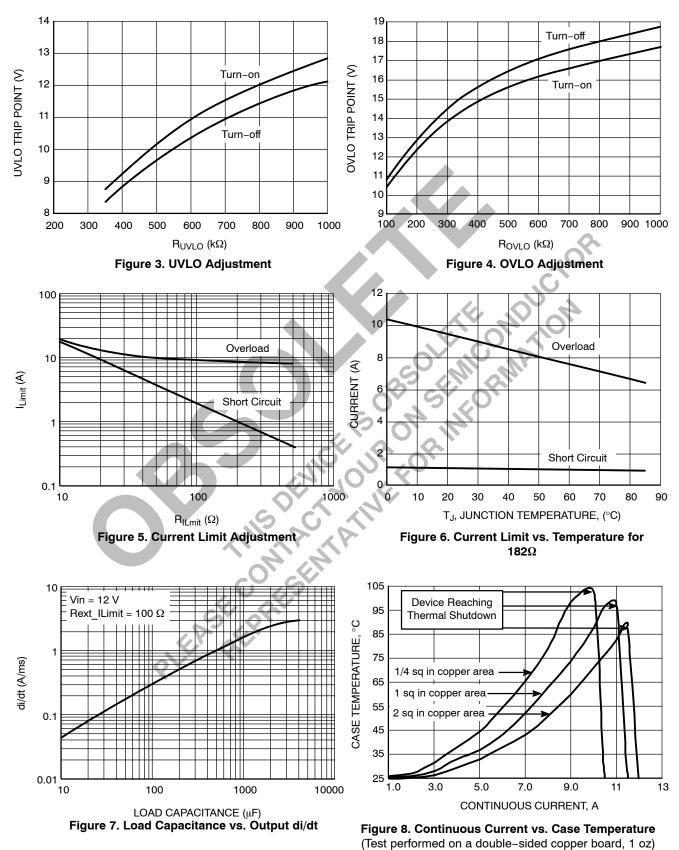

### **TYPICAL PERFORMANCE CURVES**

(T<sub>A</sub> = 25°C unless otherwise noted)

20 ms/div **Output Voltage** (2 V/div) Output (2 A/div) Overload Current Thermal Shutdown Short Ckt-Volt Gnd Crnt Gnd 51Ω Sense Resistor

(T<sub>A</sub> = 25°C unless otherwise noted)

Figure 10. Current Waveforms for Overload, Short Circuit and Thermal Shutdown

#### TYPICAL APPLICATION CIRCUITS AND OPERATION WAVEFORMS (continued)

$(T_A = 25^{\circ}C \text{ unless otherwise noted})$

Figure 16. Turn-on Sequencing Using Power Good Signal

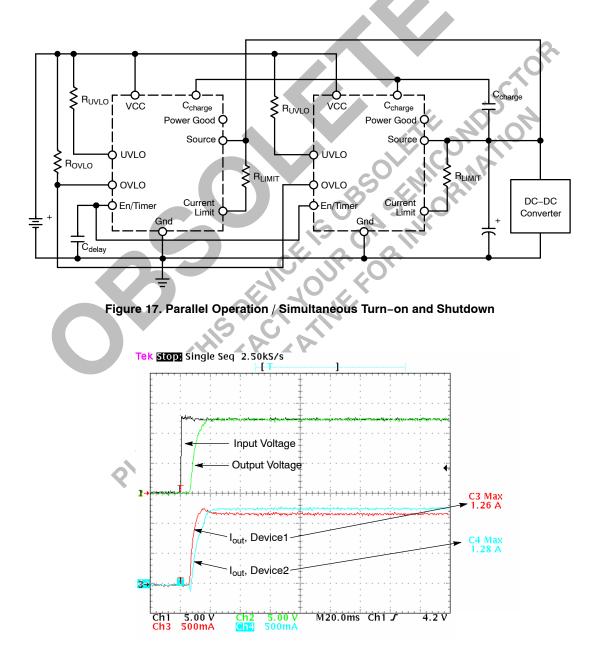

Figure 18. Turn-on Waveforms for Parallel Operation

#### **OPERATING DESCRIPTION**

#### Operation

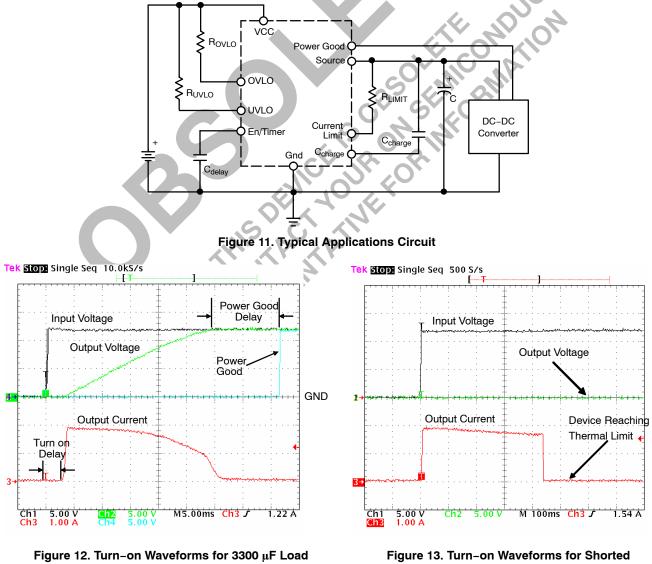

The NIS5102 has a variety of shutdown and protection features that make this part extremely versatile as well as rugged. For the unit to operate, the input voltage must be within the operating range of the part which is set by the UVLO and OVLO bias resistors. The enable must also be high for operation. Current and thermal limit circuits constantly monitor the operation and will protect the unit if either of these parameters exceeds its preset limit.

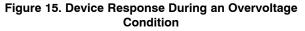

An additional shutdown method, is the use of the OVLO pin, which can be tied in parallel. This allows multiple units to be either operated in parallel, and will shutdown and turn on simultaneously for any fault other than an overvoltage, or it allows these hot plug devices to control independent loads, and shutdown and turn on simultaneously.

#### Faults

Once the load capacitance is charged, the SENSEFET<sup>™</sup> will become fully enhanced as long as the current does not

reach the current limit threshold, or is shutdown due to an overvoltage, undervoltage or thermal fault. Both the UVLO and OVLO circuits incorporate hysteresis to assure clean turn-on and turn-offs with no chatter. The thermal latching circuit will require the input power to be recycled to resume operation after a fault. The current limit is always active, so any transient or overload will always be limited.

#### **Circuit Description**

#### **Enable/Timer**

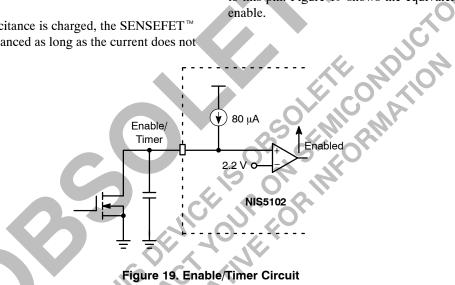

The enable/timer pin can function either as a direct enable pin, or as a time delay. In the enable mode, an open collector device is connected to this pin. When the device is in its low impedance mode, this pin is low and the operation of the chip is disabled. If a time delay is required, a capacitor is added to this pin. Figure 19 shows the equivalent circuit for the enable.

If a capacitor is added without an open collector device, the turn on will be delayed from the time at which the UVLO voltage is reached. If an open collector device is also used, the delay will start from the time that it goes into its high impedance state. The capacitor is charged by an internal current source.

There is an inherent delay in the turn on of the hot plug device, due to the method of gate drive used. The gate of the power FET is charged through a high impedance resistor, and from the time that the gate starts charging until the time that it reaches its threshold voltage, there will be no conduction. Once the gate reaches its threshold voltage, the output current will begin a controlled ramp up phase.

This delay will be added to any timing delay due to the enable/timer circuit.

#### Power Good

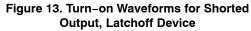

The power good circuit monitors the  $V_{\mbox{GS}}$  voltage of the power SENSEFET and compares it with the output voltage of the internal charge pump. Once the V<sub>GS</sub> of the power SENSEFET reaches around 90% of the internal charge pump output voltage, the power good will change its state from low impedance to high impedance but only after the power good delay has elapsed. Figure 12 shows the power good behavior during the startup of the NIS5102 device, an external pullup resistor from power good to V<sub>CC</sub> was used.

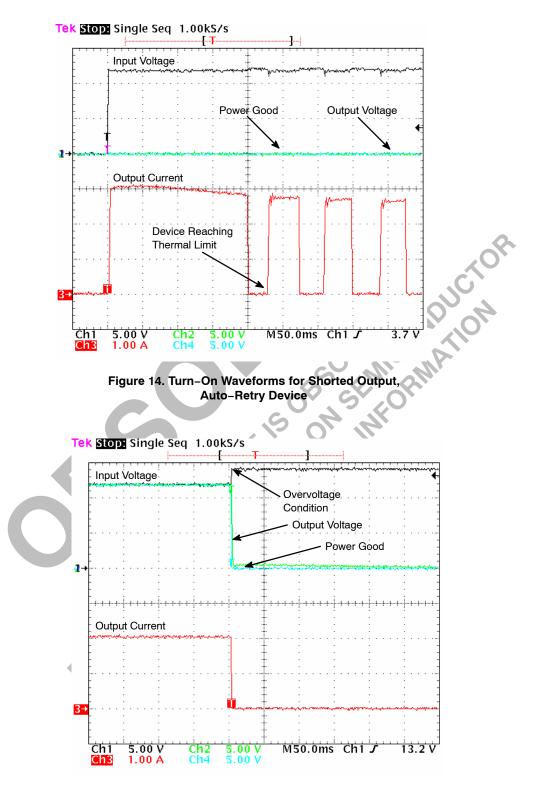

The power good will change its state from high impedance to low impedance in the event of any fault condition such as short circuit and overvoltage.

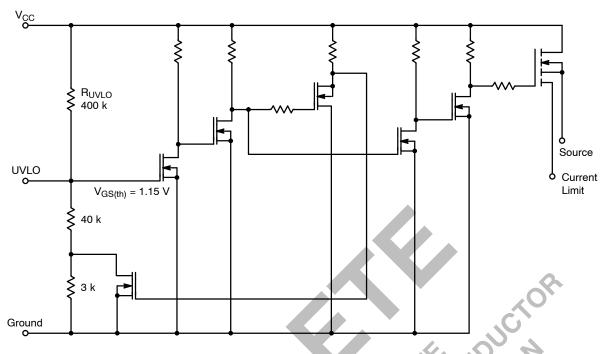

#### Undervoltage Lockout

The UVLO circuit holds the chip off when the input voltage is less than the turn-on limit. It includes internal hysteresis to assure clean on/off switching. An internal divider sets the turn-on voltage level at 16 V. This voltage can be reduced by adding an external resistor from the UVLO pin to the V<sub>CC</sub> pin. The equivalent circuit is shown in Figure 20.

Figure 20. Equivalent Undervoltage Lockout Circuit

The theoretical equation for the UVLO turn-on voltage is:

RUVLO (KΩ) =

$$\frac{400 \text{ V}_{in} - 460}{17.5 - \text{V}_{in}}$$

The UVLO trip point voltage calculated through the theoretical formula may show small variations with respect to Figure 3, therefore it is recommended to use the formulas gotten from the UVLO characterization, which are shown below:

$R_{UVLO}$  (k $\Omega$ ) = e [(UVLO + 14.647)/3.9858]; for  $T_J$  = 250 where "UVLO" is the desired undervoltage lockout value, and  $R_{UVLO}$  is the programming resistor from the UVLO pin to the V<sub>CC</sub> pin.

To reduce nuisance tripping due to transients and noise spikes, a capacitor may be added from the UVLO pin to ground. This will create a low pass filter with a cutoff frequency of f. The required capacitance on this pin is:

$$CUVLO = \frac{1}{2\pi \cdot f\left[43 \text{ K} + \left(\frac{R_{UVLO} \cdot 400 \text{ K}}{R_{UVLO} + 400 \text{ K}}\right)\right]}$$

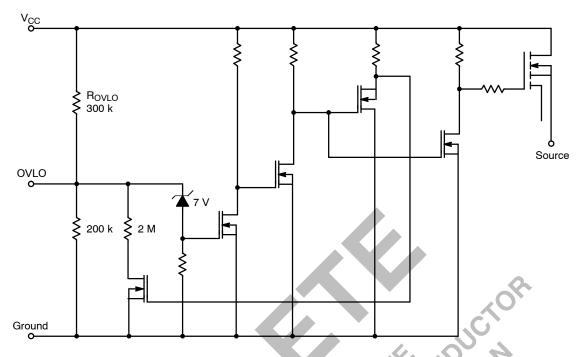

#### Overvoltage Lockout and Parallel Shutdown

The overvoltage lockout (OVLO) is a dual function pin. This pin will normally be biased somewhere between ground and the input voltage, due to an internal voltage divider which sets the turn–off voltage level at 22 V. This voltage level can be reduced by adding an external resistor from the OVLO pin to the  $V_{CC}$  pin. When the input voltage reaches the programmed trip point, operation of the device is inhibited.

Figure 21 shows the equivalent circuit.

Figure 21. Equivalent Overvoltage Lockout Circuit

The theoretical equation for the OVLO turn-on voltage is:

$$ROVLO (K\Omega) = \frac{300 V_{in} - 2100}{21.8 - V_{in}}$$

The OVLO trip point voltage calculated through the theoretical formula may show small variations with respect to Figure 4, therefore it is recommended to use the formulas gotten from the OVLO characterization, which are shown below:

$$ROVLO (k\Omega) = e [(OVLO + 5.2)/3.46]; for T_J = 25Q$$

where "OVLO" is the desired overvoltage lockout value, and  $R_{\rm OVLO}$  is the programming resistor from the OVLO pin to the  $V_{\rm CC}$  pin.

To reduce nuisance tripping due to transients and noise spikes, a capacitor may be added from the OVLO pin to ground. This will create a low pass filter with a cutoff frequency of f. The required capacitance on this pin is:

$$C_{OVLO} = \frac{[1 + (8.83 E^{-6} \cdot R_{OVLO})]}{2\pi \cdot f \cdot R_{OVLO}}$$

This pin is also used as a common shutdown pin. In this mode, if this pin is pulled to ground, it will shutdown the chip and all chips connected to its OVLO pin.

The OVLO pin has an internal switch to ground that will pull it low, whenever the device is disabled due to any fault other than an Overvoltage condition. An enable pin shutdown is not considered a fault and will not cause a common shutdown. This feature allows multiple units to turn on and off simultaneously by tying the OVLO pins together in parallel. This can be used for operating several hot plug devices in parallel, or for use with separate loads, when all devices need to startup and shutdown simultaneously.

#### Temperature Limit

The temperature limit circuit senses the temperature of the Power FET and removes the gate drive if the maximum level is exceeded. For the auto-retry device, there is a nominal hysteresis of 40°C for this circuit. After a thermal shutdown, the device will automatically restart when the temperature drops to a safe level as determined by the hysteresis. The latching thermal circuit can be reset either by recycling the input power, or by toggling the enable signal.

#### **Current Limit**

An external resistor from the current limit pin to the source pins set the level at which the device will limit the current. The plot of resistance vs. current limit includes two curves, one for short circuit and one for overload.

A short circuit condition is one in which the SENSEFET is not fully enhanced, and is therefore in a high impedance mode of operation. In this case there are many hundreds of millivolts across the drain to source pins of the SENSEFET. This occurs when the output sees a very low impedance short as well as when the capacitor is charging at turn on. In both cases there are several volts or more across the FET.

An overload condition is one in which the SENSEFET is still fully enhanced and the drain to source voltage is the product of the drain current and the on resistance of the FET.

The sense voltage out of the SENSEFET has a different relation to the drain current in these two conditions. The difference in current limit levels for these two cases is called DI, where:

$\Delta I = V_{ref}/R_{DSon}$

For this equation,  $V_{ref}$  is the reference voltage of the current limit circuit, and  $R_{DSon}$  is the on resistance of the SENSEFET. For more information on this, see application note AND8140/D, "SMART HotPlug<sup>TM</sup> Current Limit Function".

This inherent property of the SENSEFET allows for simple dual level current limiting, in which a short circuit condition will see a lower level of limiting than will an overload. This operation will exist in start up as well as under normal operation, so the device will be able to differentiate between a short and an overload.

As with all SMART HotPlug devices, the current limit will never shutdown the device. Only the thermal limit will stop the flow of current to the load. Once the current is stopped due to the thermal limit, it will remain off until input power is recycled for the latching version, or it will continuously retry to start again if it is the auto–retry version.

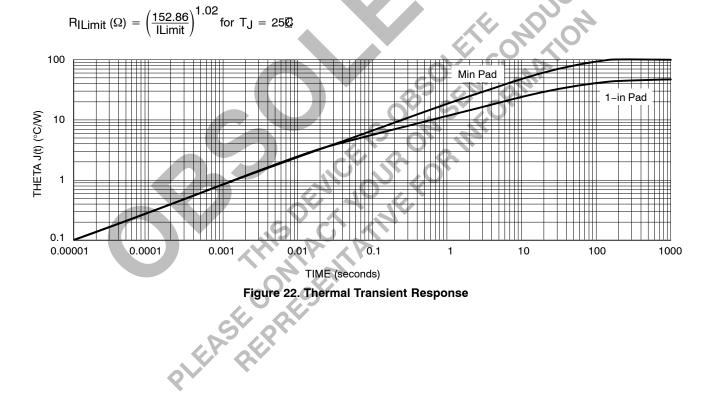

The ILimit graph shown in Figure 5 was generated from the data of the ILimit characterization, the formula for the short circuit curve is: where "ILimit" is the desired short circuit ILimit value, and R<sub>ILimit</sub> is the programming resistor from the ILimit pin to the source pin.

#### Turn-on Surge

During the turn-on event, there is a large amount of energy dissipated due to the linear operation of the power device. The energy rating is the amount of energy that the device can absorb before the thermal limit circuit will shut the unit down. This is very important specially for the latch off device as it determines the maximum load capacitance that the device can charge before the thermal limit shuts the device down. The calculation of this is not very simple as it depends on several factors such as the input voltage (Vin), load capacitance (CL), current limit settings (ILimit) and device's thermal transient response, therefore, it is recommended to do lab evaluations for these purposes. Figure 22 shows the device's thermal transient response for minimum pad.

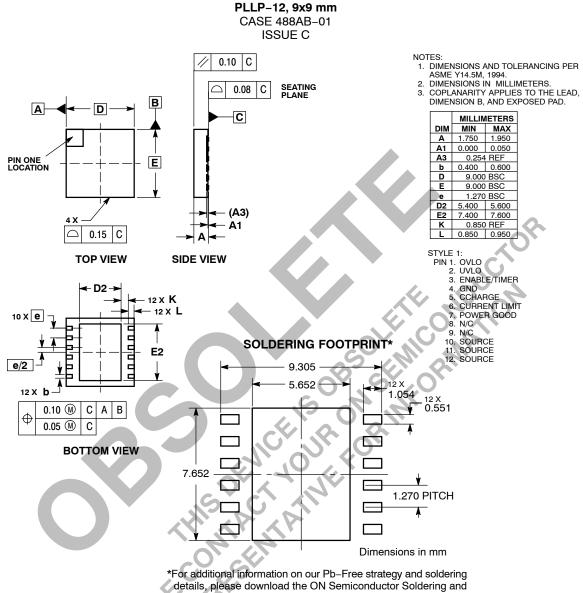

#### PACKAGE DIMENSIONS

Mounting Techniques Reference Manual, SOLDERRM/D.

The product described herein (NIS5102), may be covered by one or more of the following U.S. patents: 6,781,502; 6,865,063; 7,099,135. There may be other patents pending. SMART HotPlug and SENSEFET are trademarks of Semiconductor Components Industries, LLC.

ON Semiconductor and IIII are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other application is unich the failure of the SCILLC product costs of any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use payle copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5773-3850 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative