# 1/4 and 1/3-Duty General-Purpose LCD Driver

www.onsemi.com

#### Overview

The LC450029PKB is 1/4 duty and 1/3 duty general-purpose microcontrollercontrolled LCD drivers that can be used in applications such as frequency display in products with electronic tuning. In addition to being capable to drive up to 208 segments directly. The internal oscillation circuit helps to reduce the number of external resistors and capacitors required. The chip shape is slim for COG (Chip-On-Glass) implementation. The operating temperature range is from  $-40^{\circ}$ C to  $+105^{\circ}$ C

#### Application

• Car or general consumer electronic LCD display equipment.

#### Features

- Selectable 1/4-duty or 1/3-duty drive by the serial control data When 1/4-duty: Capable of driving up to 208 segments

- When 1/3-duty: Capable of driving up to 159 segments

- 1/3-bias only

- Serial data input supports CCB\* format communication with the system controller. (For 5 V operation only)

- The power-saving mode is selectable by the serial control data, and supports low power consumption.

- Adjustable the frame frequency of the common and segment output waveforms by the serial control data

- Selectable the internal oscillator operating or external clock operating mode by the serial control data

- High generality, since display data is displayed directly without the intervention of a decoder circuit.

- The  $\overline{\text{INH}}$  pad allows all LCD segments to be forced to the off state.

- With a built-in oscillator circuit (External resistors and capacitors are unnecessary.)

- The stability of the LCD bias voltage is high by a built-in LCD bias generator with voltage-follower buffers.

- Shipping form: Chip with Au bumps in tray.

- Allowable operating voltage (V<sub>DD</sub>, V<sub>DD</sub>I) :+4.5 V to +6.0 V

- Allowable wide operating temperature ranges  $:-40^{\circ}$ C to  $+105^{\circ}$ C

\* Computer Control Bus (CCB) is an ON Semiconductor's original bus format and the bus addresses are controlled by ON Semiconductor.

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 25 of this data sheet.

## Specifications

#### Absolute Maximum Ratings at Ta = 25°C, V<sub>SS</sub> = 0 V

| Parameter              | Symbol                                        | Conditions                         | Ratings                       | Unit |

|------------------------|-----------------------------------------------|------------------------------------|-------------------------------|------|

| Maximum supply voltage | V <sub>DD</sub> max,<br>V <sub>DD</sub> I max | V <sub>DD</sub> =V <sub>DD</sub> I | -0.3 to +6.5                  | V    |

| Input voltage          | VIN1                                          | CE, CL, DI, INH                    | –0.3 to +6.5                  |      |

|                        | V <sub>IN</sub> 2                             | OSCI                               | –0.3 to V <sub>DD</sub> I+0.3 | V    |

| Output voltage         | VOUT                                          | S1 to S53, COM1 to COM4            | –0.3 to V <sub>DD</sub> +0.3  | V    |

| Output current         | IOUT1                                         | S1 to S53                          | 300                           | μA   |

|                        | IOUT <sup>2</sup>                             | COM1 to COM4                       | 3                             | mA   |

| Operating temperature  | Topr                                          |                                    | -40 to +105                   | °C   |

| Storage temperature    | Tstg                                          |                                    | -55 to +125                   | °C   |

(Note) Power supply pads (V<sub>DD</sub>, V<sub>DD</sub>I) should connect all pads to the same power supply. (See sample applications circuits)

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

#### Allowable Operating Ranges at Ta = -40 to +105°C, V<sub>SS</sub> = 0 V

| Parameter                          | Symbol                                 |                                                   |                        | Ratings            |     |                      | Unit |

|------------------------------------|----------------------------------------|---------------------------------------------------|------------------------|--------------------|-----|----------------------|------|

| Parameter                          | Symbol                                 |                                                   |                        | min                | typ | max                  | Unit |

| Supply voltage                     | V <sub>DD</sub> ,<br>V <sub>DD</sub> I | VDD=VDDI                                          |                        | 4.5                |     | 6.0                  | V    |

| Input high-level voltage           | V <sub>IH</sub> 1                      | CE, CL, DI, IN                                    | Ħ                      | 0.8V <sub>DD</sub> |     | 6.0                  | V    |

|                                    | V <sub>IH</sub> 2                      | OSCI: Externa                                     | I clock operating mode | 0.8V <sub>DD</sub> |     | V <sub>DD</sub> I    | v    |

| Input low-level voltage            | V <sub>IL</sub> 1                      | CE, CL, DI, IN                                    | Ħ                      | 0                  |     | 0.2V <sub>DD</sub> I | V    |

|                                    | V <sub>IL</sub> 2                      | OSCI: Externa                                     | I clock operating mode | 0                  |     | 0.2V <sub>DD</sub> I | v    |

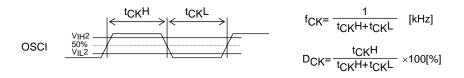

| External clock operating frequency | fCK                                    | OSCI: External clock operating mode<br>[Figure 4] |                        | 10                 | 300 | 600                  | kHz  |

| External clock duty cycle          | DCK                                    | OSCI: External clock operating mode<br>[Figure 4] |                        | 30                 | 50  | 70                   | %    |

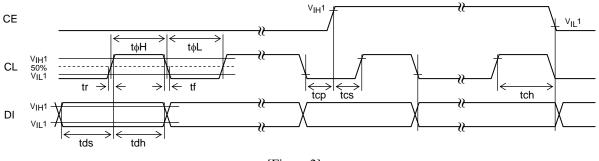

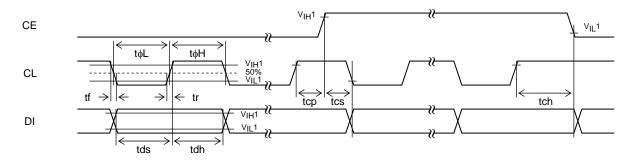

| Data setup time                    | tds                                    | CL, DI                                            | [Figure 2] [Figure 3]  | 160                |     |                      | ns   |

| Data hold time                     | tdh                                    | CL, DI                                            | [Figure 2] [Figure 3]  | 160                |     |                      | ns   |

| CE wait time                       | tcp                                    | CE, CL                                            | [Figure 2] [Figure 3]  | 160                |     |                      | ns   |

| CE setup time                      | tcs                                    | CE, CL                                            | [Figure 2] [Figure 3]  | 160                |     |                      | ns   |

| CE hold time                       | tch                                    | CE, CL                                            | [Figure 2] [Figure 3]  | 160                |     |                      | ns   |

| High-level clock pulse width       | tφH                                    | CL [Figure 2] [Figure 3]                          |                        | 160                |     |                      | ns   |

| Low-level clock pulse width        | tφL                                    | CL [Figure 2] [Figure 3]                          |                        | 160                |     |                      | ns   |

| Rise time                          | tr                                     | CE, CL, DI [Figure 2] [Figure 3]                  |                        |                    | 160 |                      | ns   |

| Fall time                          | tf                                     | CE, CL, DI                                        | [Figure 2] [Figure 3]  |                    | 160 |                      | ns   |

| INH switching time                 | tc                                     | ĪNH, CE                                           | [Figure 5] [Figure 6]  | 10                 |     |                      | μS   |

(Note) Power supply pads (V<sub>DD</sub>, V<sub>DD</sub>I) should connect all pads to the same power supply. (See sample applications circuits)

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

| Doromotor                              | Cumbal             | Pin                                 | Conditions                                                                                                                                                           | Ratings                    |                      |                            | Unit |

|----------------------------------------|--------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------|----------------------------|------|

| Parameter                              | Symbol             | PIN                                 | Conditions                                                                                                                                                           | min                        | typ                  | max                        | Uni  |

| Hysteresis                             | V <sub>H</sub> 1   | CE, CL, DI, INH                     |                                                                                                                                                                      |                            | 0.1V <sub>DD</sub> I |                            | v    |

|                                        | V <sub>H</sub> 2   | OSCI                                | External clock operating mode                                                                                                                                        |                            | 0.1V <sub>DD</sub> I |                            | v    |

| Input high-level                       | I <sub>IH</sub> 1  | CE, CL, DI, INH                     | VI = 6.0 V                                                                                                                                                           |                            |                      | 5.0                        |      |

| current                                | I <sub>IH</sub> 2  | OSCI                                | V <sub>I</sub> = V <sub>DD</sub> I, External clock<br>operating mode                                                                                                 |                            |                      | 5.0                        | μA   |

| Input low-level                        | l <sub>IL</sub> 1  | CE, CL, DI, INH                     | $V_{I} = 0 V$                                                                                                                                                        | -5.0                       |                      |                            |      |

| current                                | IIL2               | OSCI                                | V <sub>I</sub> = 0 V, External clock<br>operating mode                                                                                                               | -5.0                       |                      |                            | μA   |

| Output high-<br>level voltage          | V <sub>OH</sub> 1  | S1 to S53                           | I <sub>O</sub> = -20 μA                                                                                                                                              | V <sub>DD</sub><br>-0.9    |                      |                            | V    |

|                                        | V <sub>OH</sub> 2  | COM1<br>to COM4                     | I <sub>O</sub> = -100 μA                                                                                                                                             | V <sub>DD</sub><br>-0.9    |                      |                            | V    |

| Output low-level voltage               | V <sub>OL</sub> 1  | S1 to S53                           | I <sub>O</sub> = 20 μA                                                                                                                                               |                            |                      | 0.9                        | V    |

|                                        | V <sub>OL</sub> 2  | COM1<br>to COM4                     | I <sub>O</sub> = 100 μA                                                                                                                                              |                            |                      | 0.9                        |      |

| Output middle-<br>level voltage *1     | V <sub>MID</sub> 1 | S1 to S53                           | I <sub>O</sub> = ±20 μA                                                                                                                                              | 2/3V <sub>DD</sub><br>-0.9 |                      | 2/3V <sub>DD</sub><br>+0.9 |      |

|                                        | V <sub>MID</sub> 2 | S1 to S53                           | I <sub>O</sub> = ±20 μA                                                                                                                                              | 1/3V <sub>DD</sub><br>-0.9 |                      | 1/3V <sub>DD</sub><br>+0.9 | V    |

|                                        | V <sub>MID</sub> 3 | COM1<br>to COM4                     | I <sub>O</sub> = ±100 μA                                                                                                                                             | 2/3V <sub>DD</sub><br>_0.9 |                      | 2/3V <sub>DD</sub><br>+0.9 |      |

|                                        | V <sub>MID</sub> 4 | COM1<br>to COM4                     | I <sub>O</sub> = ±100 μA                                                                                                                                             | 1/3V <sub>DD</sub><br>-0.9 |                      | 1/3V <sub>DD</sub><br>+0.9 |      |

| Oscillator<br>frequency                | fosc               | Internal oscillator circuit         | Internal oscillator operating mode                                                                                                                                   | 210                        | 300                  | 390                        | kHz  |

| Current drain<br>(Total value of       | I <sub>DD</sub> 1  | V <sub>DD</sub> , V <sub>DD</sub> I | <power-saving mode=""><br/>V<sub>DD</sub> = V<sub>DD</sub>I = 6.0 V</power-saving>                                                                                   |                            | 40                   | 100                        |      |

| V <sub>DD</sub> and V <sub>DD</sub> I) | I <sub>DD</sub> 2  | V <sub>DD</sub> , V <sub>DD</sub> I | <pre><internal mode="" operating="" oscillator=""> VDD = VDDI = 6.0 V Driver outputs are open.</internal></pre>                                                      |                            | 200                  | 400                        | μA   |

|                                        | I <sub>DD</sub> 3  | V <sub>DD</sub> , V <sub>DD</sub> I | <external clock="" mode="" operating=""><br/><math>V_{DD} = V_{DD}I = 6.0 V</math><br/><math>f_{CK} = 300 \text{ kHz}</math><br/>Driver outputs are open.</external> |                            | 170                  | 340                        |      |

#### Electrical Characteristics for the Allowable Operating Ranges

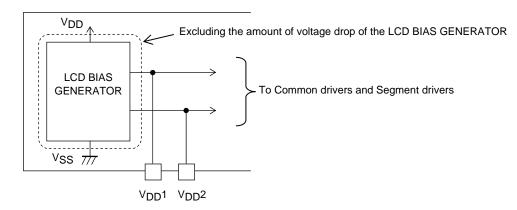

\*1: Excluding the amount of voltage drop of the LCD BIAS GENERATOR which generates V<sub>DD</sub>1 and V<sub>DD</sub>2. (See Figure 1.)

[Figure 1]

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

#### (1) When CL is stopped at the low level

[Figure 2]

(2) When CL is stopped at the high level

[Figure 3]

(3) OSCI pad clock timing in external clock operating mode

[Figure 4]

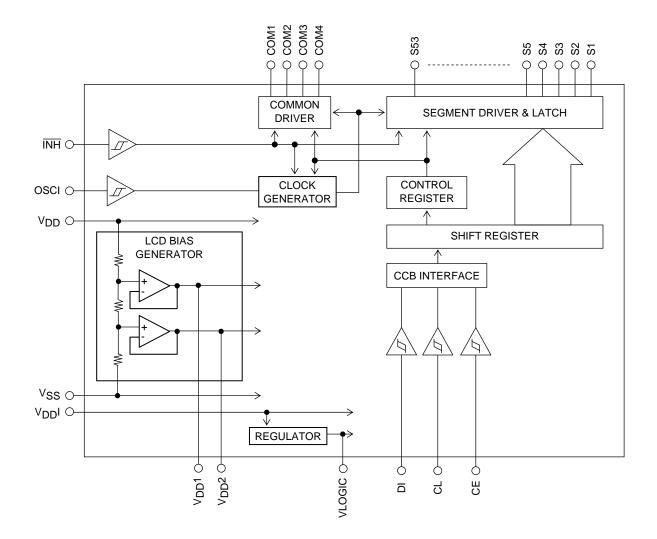

#### **Block Diagram**

#### **Pad Functions**

| Symbol            | Pad No.           | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Active | I/O  | Handling<br>when<br>unused |

|-------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|----------------------------|

| COM1 to<br>COM4   | 2 to 5            | Common driver outputs.<br>The frame frequency is fo[Hz].<br>COM4 pad outputs the V <sub>SS</sub> level in 1/3-duty.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -      | 0    | OPEN                       |

| S1 to S53         | 6 to 58           | Segment outputs for displaying the display data transferred by serial data input.<br>S51 pad outputs the V <sub>SS</sub> level in 1/4-duty.<br>S52 pad and S53 pad output the V <sub>SS</sub> level at the control data DN="0".<br>S53 pad outputs the V <sub>SS</sub> level at external clock operating mode.                                                                                                                                                                                                                                                                                                                                                                                                 | -      | 0    | OPEN                       |

| ĪNH               | 61                | Display off control input<br>• INH = low (V <sub>SS</sub> )Display forced off (V <sub>SS</sub> level Output)<br>S1 to S53 = low (V <sub>SS</sub> )<br>COM1 to COM4 = low (V <sub>SS</sub> )<br>The internal oscillator stops.<br>Stops inputting external clock.<br>Serial data transfer can be used.<br>• INH = high (V <sub>DD</sub> )Display on<br>Enables the internal oscillator circuit.<br>(Internal oscillator operating mode)<br>Enables external clock input.<br>(External clock operating mode)<br>While display on, LCD outputs force off (V <sub>SS</sub> level output)<br>by the control data BU="1".<br>While display on, LCD outputs off (off waveforms output)<br>by the control data SC="1". | L      | I    | GND<br>(V <sub>SS</sub> )  |

| CE<br>DI          | 62<br>63          | Serial data transfer inputs. Must be connected to the controller.<br>CE: Chip enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | н      | I    | GND                        |

| CL                | 64                | DI: Transfer data<br>CL: Synchronization clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        | I    | (V <sub>SS</sub> )         |

| VLOGIC            | 65                | Used to monitor pad for the power supply voltage of the logic circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -      | 0    | OPEN                       |

| V <sub>DD</sub> I | 66 to 71          | Power supply pad. A power voltage of 4.5 to 6.0V must be applied to these pads.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -      | -    | -                          |

| OSCI              | 72                | This pad can also be used as the external clock input pad when the external clock operating mode is selected by control data.<br>This pad must be connected to GND at internal oscillator operating mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -      | I    | GND<br>(V <sub>SS</sub> )  |

| V <sub>SS</sub>   | 73 to 90          | Ground pad. Must be connected to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -      | -    | -                          |

| V <sub>DD</sub> 2 | 91                | Used to monitor pad for the LCD drive bias voltage (1/3 $V_{\mbox{DD}}).$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -      | 0    | OPEN                       |

| V <sub>DD</sub> 1 | 92                | Used to monitor pad for the LCD drive bias voltage (2/3 $\mathrm{V}_{\mbox{DD}}).$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -      | 0    | OPEN                       |

| V <sub>DD</sub>   | 93 to 105         | Power supply pad. A power voltage of 4.5 to 6.0V must be applied to these pads.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -      | -    | -                          |

| DUMMY             | 1, 59,<br>60, 106 | Dummy pad. Must not be used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -      | OPEN | OPEN                       |

(Note)

• Power supply pads (V<sub>DD</sub>, V<sub>DD</sub>I) should connect all pads to the same power supply. (See sample applications circuits)

• GND pad (VSS) should <u>connect</u> all pads to the GND.

• When logic input pads (INH, CE, DI, CL, OSCI) are not used, must be fixed to GND (VSS).

$\bullet$  Must not use monitor pads (VLOGIC, VDD1, VDD2) in an external circuit.

• Must not connect dummy pad (DUMMY) mutually. Moreover, never use it in an external circuit.

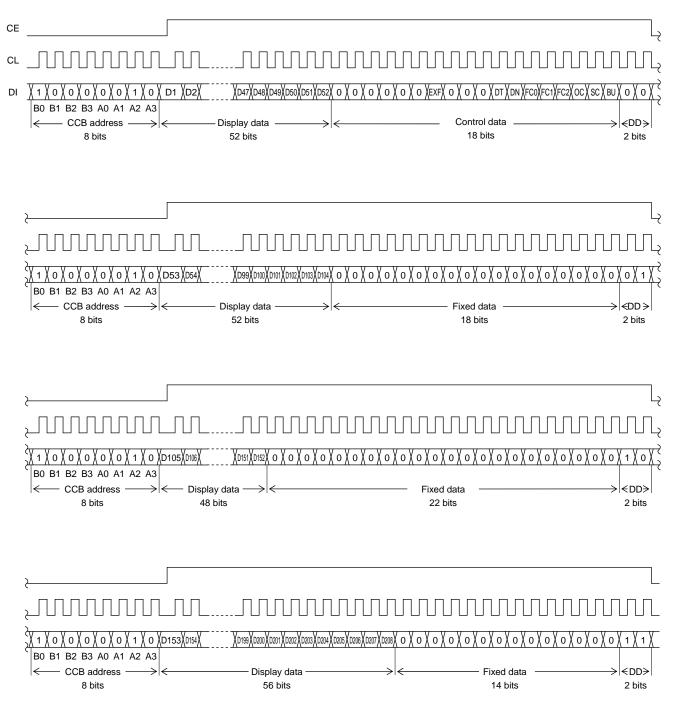

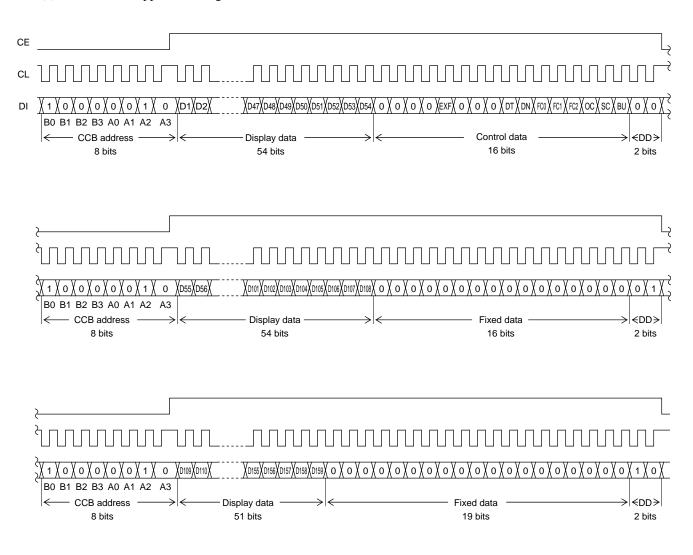

#### Serial Data Input

1. 1/4 duty

(1) When CL is stopped at the low level

Note: DD is the direction data.

(2) When CL is stopped at the high level

Note: DD is the direction data.

- CCB address ..... "41H"

- D1 to D208 ..... Display data

- EXF ...... Ratio of dividing frequency in external clock operating mode setting control data

- DT ..... 1/4-duty drive or 1/3-duty drive switching control data

- DN ..... The number of the maximum display segments setting control data

- FC0 to FC2 ..... Common/segment output waveform frame frequency control data

- OC ...... Internal oscillator operating mode/external clock operating mode switching control data

- SC ..... Segment on/off (off waveform output) control data

- BU ...... Normal mode/power-saving mode control data

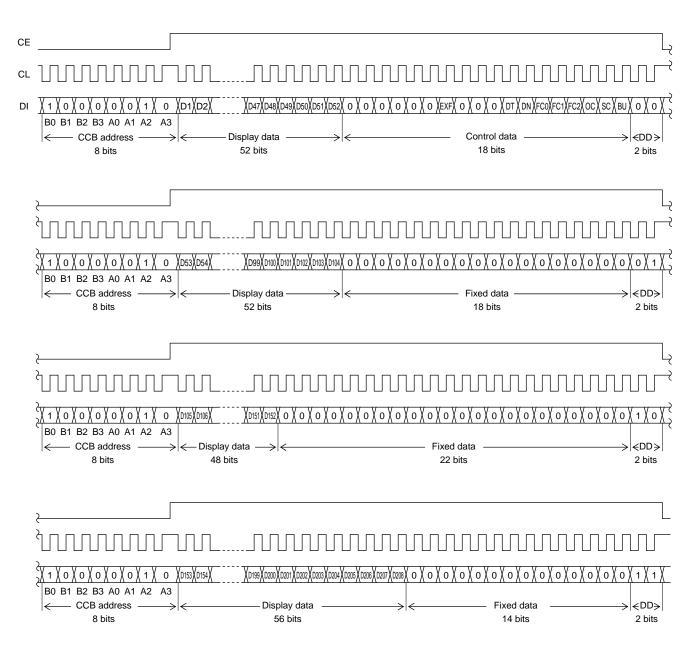

# 2. 1/3 duty(1) When CL is stopped at the low level

Note: DD is the direction data.

(2) When CL is stopped at the high level

Note: DD is the direction data.

- CCB address ..... "41H"

- D1 to D208 ..... Display data

- EXF ...... Ratio of dividing frequency in external clock operating mode setting control data

- DT ..... 1/4-duty drive or 1/3-duty drive switching control data

- DN ..... The number of the maximum display segments setting control data

- FC0 to FC2 ..... Common/segment output waveform frame frequency control data

- OC ...... Internal oscillator operating mode/external clock operating mode switching control data

- SC ..... Segment on/off (off waveform output) control data

- BU ..... Normal mode/power-saving mode control data

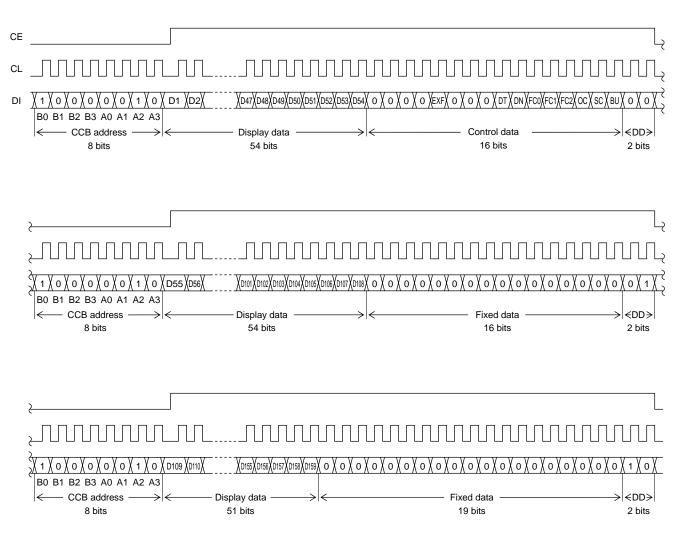

#### Serial Data Transfer Example

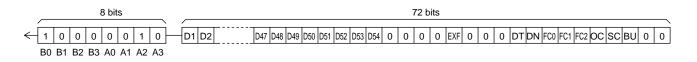

1. 1/4 duty

• When 153 or more segments are used

All 320 bits (include CCB address) of serial data must be sent.

| 8 bits                                                                                                                                                                            | 72 bits                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| ← 1 0 0 0 0 0 1 0 D1 D2<br>B0 B1 B2 B3 A0 A1 A2 A3                                                                                                                                |                                                                                           |

| 1         0         0         0         0         1         0         D53         D54           B0         B1         B2         B3         A0         A1         A2         A3   |                                                                                           |

| 1         0         0         0         0         1         0         D105         D106           B0         B1         B2         B3         A0         A1         A2         A3 | D151 D152 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                           |

| 1         0         0         0         0         1         0         D153         D154           B0         B1         B2         B3         A0         A1         A2         A3 | D199 D200 D201 D202 D203 D204 D205 D206 D207 D208 O O O O O O O O O O O O O O O O O O I I |

• When fewer than 153 segments are used

One of 80, 160 and 240 bits of serial data must be sent, depending on the number of segments to be used. However, the serial data shown below (the D1 to D52 display data, the control data and DD="00") must always be sent.

| 8 bits                  | 72 bits                                                                      |   |

|-------------------------|------------------------------------------------------------------------------|---|

|                         |                                                                              |   |

| ← 1 0 0 0 0 0 1 0 D1 D2 | D47 D48 D49 D50 D51 D52 0 0 0 0 0 0 EXF 0 0 0 DT DN FC0 FC1 FC2 OC SC BU 0 C | ) |

| B0 B1 B2 B3 A0 A1 A2 A3 |                                                                              |   |

#### 2. 1/3 duty

• When 109 or more segments are used All 240 bits (include CCB address) of serial data must be sent.

| 8 bits                                       |           | 72 bits                                                        |

|----------------------------------------------|-----------|----------------------------------------------------------------|

| ← 1 0 0 0 0 0 1 0<br>B0 B1 B2 B3 A0 A1 A2 A3 | -D1 D2    |                                                                |

| 1 0 0 0 0 0 1 0<br>B0 B1 B2 B3 A0 A1 A2 A3   | — D55 D56 |                                                                |

| 1 0 0 0 0 0 1 0<br>B0 B1 B2 B3 A0 A1 A2 A3   |           | D155 D156 D157 D158 D159 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 |

• When fewer than 109 segments are used Either 80 or 160 bits of serial data must be sent, depending on the number of segments to be used. However, the serial data shown below (the D1 to D54 display data, the control data and DD="00") must always be sent.

#### **Control Data Functions**

(1) EXF ... Ratio of dividing frequency in external clock operating mode setting control data

This control data sets the ratio of dividing frequency of the external clock which input into the OSCI pad, when the external clock operating mode (OC="1") is set. However, this data is effective only when external clock operating mode (OC="1") is set. The frame frequency is adjustable by setting EXF, FC0 to FC2 and OC.

| EXF | Ratio of dividing frequency in external clock operating mode |

|-----|--------------------------------------------------------------|

| 0   | f <sub>CK</sub> / 8                                          |

| 1   | fск                                                          |

(2) DT  $\dots$  1/4-duty drive or 1/3-duty drive switching control data

| ) | <i>D</i> D I 1/4-duty drive of 1/3-duty drive switching control data   |              |                 |  |  |  |  |  |

|---|------------------------------------------------------------------------|--------------|-----------------|--|--|--|--|--|

|   | This control data bit selects either 1/4-duty drive or 1/3-duty drive. |              |                 |  |  |  |  |  |

|   | DT                                                                     | Drive scheme | S51 pad's state |  |  |  |  |  |

|   |                                                                        |              |                 |  |  |  |  |  |

| 0 | 1/4-duty drive | Low (V <sub>SS</sub> ) level output |

|---|----------------|-------------------------------------|

| 1 | 1/3-duty drive | S51 (segment output)                |

#### (3) DN ... The number of the maximum display segments setting control data

This control data bit sets the number of the maximum display segments.

| DN | The number of the max | kimum display segments | Pad's state            |                        |  |

|----|-----------------------|------------------------|------------------------|------------------------|--|

| DN | 1/4 duty              | 1/3 duty               | S52                    | S53                    |  |

| 0  | Up to 200 segments    | Up to 153 segments     | "L" (V <sub>SS</sub> ) | "L" (V <sub>SS</sub> ) |  |

| 1  | Up to 208 segments    | Up to 159 segments     | S52 (segment output)   | S53 (segment output)   |  |

(Note) S53 pad outputs VSS level in external clock operating mode.

#### (4) FC0 to FC2 ... Common/segment output waveform frame frequency control data

These control data bits set the frame frequency of the common and segment output waveforms. The frame frequency is adjustable by setting EXF, FC0 to FC2 and OC.

| C   | Control dat | a   |                                                                                      | Frame frequency fo[Hz]                                                                                       |                                                                                                             |  |  |  |

|-----|-------------|-----|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--|--|--|

| FC0 | FC1         | FC2 | Internal oscillator operating mode<br>(The control data OC="0",<br>fosc=300[kHz]typ) | External clock operating mode<br>(The control data<br>OC="1", EXF="0")<br>Case is f <sub>CK</sub> =300[kHz]. | External clock operating mode<br>(The control data<br>OC="1", EXF="1")<br>Case is f <sub>CK</sub> =38[kHz]. |  |  |  |

| 0   | 0           | 0   | fosc/6144 =48.8[Hz]typ                                                               | f <sub>CK</sub> /6144 =48.8[Hz]                                                                              | f <sub>CK</sub> /768 =49.5[Hz]                                                                              |  |  |  |

| 0   | 0           | 1   | fosc/4608 =65.1[Hz]typ                                                               | f <sub>CK</sub> /4608 =65.1[Hz]                                                                              | f <sub>CK</sub> /576 =66.0[Hz]                                                                              |  |  |  |

| 0   | 1           | 0   | fosc/3072 =97.7[Hz]typ                                                               | f <sub>CK</sub> /3072 =97.7[Hz]                                                                              | f <sub>CK</sub> /384 =99.0[Hz]                                                                              |  |  |  |

| 0   | 1           | 1   | fosc/2304 =130.2[Hz]typ                                                              | f <sub>CK</sub> /2304 =130.2[Hz]                                                                             | f <sub>CK</sub> /288 =131.9[Hz]                                                                             |  |  |  |

| 1   | 0           | 0   | fosc/1536 =195.3[Hz]typ                                                              | f <sub>CK</sub> /1536 =195.3[Hz]                                                                             | f <sub>CK</sub> /192 =197.9[Hz]                                                                             |  |  |  |

| 1   | 0           | 1   | fosc/1152 =260.4[Hz]typ                                                              | f <sub>CK</sub> /1152 =260.4[Hz]                                                                             | f <sub>CK</sub> /144 =263.9[Hz]                                                                             |  |  |  |

| 1   | 1           | 0   | fosc/768 =390.6[Hz]typ                                                               | f <sub>CK</sub> /768 =390.6[Hz]                                                                              | f <sub>CK</sub> /96 =395.8[Hz]                                                                              |  |  |  |

| 1   | 1           | 1   | fosc/3072 =97.7[Hz]typ                                                               | f <sub>CK</sub> /3072 =97.7[Hz]                                                                              | f <sub>CK</sub> /384 =99.0[Hz]                                                                              |  |  |  |

(5) OC ... Internal oscillator operating mode/external clock operating mode switching control data

This control data bit selects either the internal oscillator operating mode or external clock operating mode.

| OC | Fundamental clock operating mode   | S53 pad's state                     |

|----|------------------------------------|-------------------------------------|

| 0  | Internal oscillator operating mode | S53 (segment output)                |

| 1  | External clock operating mode      | Low (V <sub>SS</sub> ) level output |

(6) SC ... Segment on/off (off waveform output) control data

This control data bit controls the on/off (off waveform output) state of all the segments.

| SC | Display state                                 |  |  |  |  |

|----|-----------------------------------------------|--|--|--|--|

| 0  | On                                            |  |  |  |  |

| 1  | Off of all the segments (off waveform output) |  |  |  |  |

(7) BU ... Normal mode/power-saving mode control data

This control data bit selects either normal mode or power-saving mode.

| BU | Mode                                                                                                                                                                                                                                                                                                                                              |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0  | Normal mode                                                                                                                                                                                                                                                                                                                                       |

| 1  | Power-saving mode<br>All of the common and segment output pads output the V <sub>SS</sub> level.<br>In this mode, the internal oscillator circuit stops oscillation if the IC is in the internal oscillator operating mode<br>(OC=0), and the IC stops receiving external clock signals if the IC is in the external clock operating mode (OC=1). |

| Output pad | COM1 | COM2 | COM3 | COM4 | Output pad | COM1 | COM2 | COM3 | COM4 |

|------------|------|------|------|------|------------|------|------|------|------|

| S1         | D1   | D2   | D3   | D4   | S28        | D109 | D110 | D111 | D112 |

| S2         | D5   | D6   | D7   | D8   | S29        | D113 | D114 | D115 | D116 |

| S3         | D9   | D10  | D11  | D12  | S30        | D117 | D118 | D119 | D120 |

| S4         | D13  | D14  | D15  | D16  | S31        | D121 | D122 | D123 | D124 |

| S5         | D17  | D18  | D19  | D20  | S32        | D125 | D126 | D127 | D128 |

| S6         | D21  | D22  | D23  | D24  | S33        | D129 | D130 | D131 | D132 |

| S7         | D25  | D26  | D27  | D28  | S34        | D133 | D134 | D135 | D136 |

| S8         | D29  | D30  | D31  | D32  | S35        | D137 | D138 | D139 | D140 |

| S9         | D33  | D34  | D35  | D36  | S36        | D141 | D142 | D143 | D144 |

| S10        | D37  | D38  | D39  | D40  | \$37       | D145 | D146 | D147 | D148 |

| S11        | D41  | D42  | D43  | D44  | S38        | D149 | D150 | D151 | D152 |

| S12        | D45  | D46  | D47  | D48  | S39        | D153 | D154 | D155 | D156 |

| S13        | D49  | D50  | D51  | D52  | S40        | D157 | D158 | D159 | D160 |

| S14        | D53  | D54  | D55  | D56  | S41        | D161 | D162 | D163 | D164 |

| S15        | D57  | D58  | D59  | D60  | S42        | D165 | D166 | D167 | D168 |

| S16        | D61  | D62  | D63  | D64  | S43        | D169 | D170 | D171 | D172 |

| S17        | D65  | D66  | D67  | D68  | S44        | D173 | D174 | D175 | D176 |

| S18        | D69  | D70  | D71  | D72  | S45        | D177 | D178 | D179 | D180 |

| S19        | D73  | D74  | D75  | D76  | S46        | D181 | D182 | D183 | D184 |

| S20        | D77  | D78  | D79  | D80  | S47        | D185 | D186 | D187 | D188 |

| S21        | D81  | D82  | D83  | D84  | S48        | D189 | D190 | D191 | D192 |

| S22        | D85  | D86  | D87  | D88  | S49        | D193 | D194 | D195 | D196 |

| S23        | D89  | D90  | D91  | D92  | S50        | D197 | D198 | D199 | D200 |

| S24        | D93  | D94  | D95  | D96  | S51        | -    | -    | -    | -    |

| S25        | D97  | D98  | D99  | D100 | S52        | D201 | D202 | D203 | D204 |

| S26        | D101 | D102 | D103 | D104 | S53        | D205 | D206 | D207 | D208 |

| S27        | D105 | D106 | D107 | D108 |            |      |      |      |      |

#### Display Data and Output Pad Correspondence (1/4 Duty)

(Note) In external clock operating mode, S53 pad outputs V<sub>SS</sub> level. When DN is "0", S52 pad and S53 pad output V<sub>SS</sub> level. When duty is 1/4, S51 pad outputs V<sub>SS</sub> level.

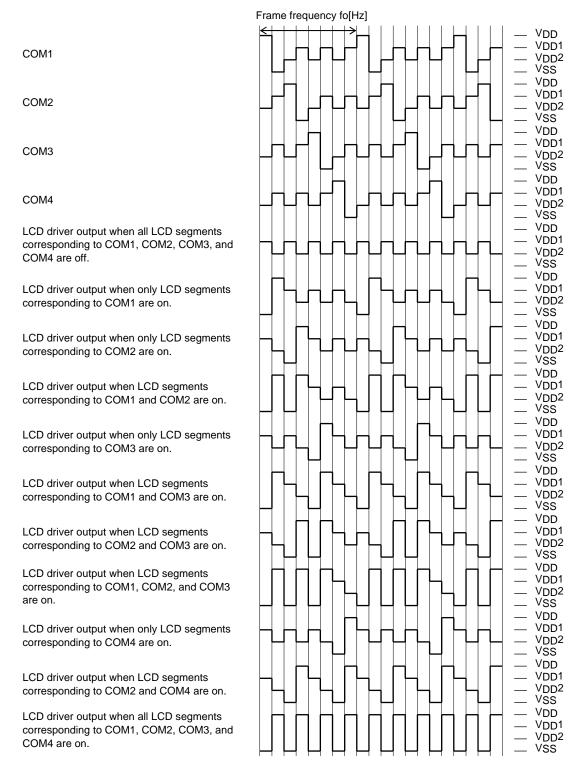

For example, the table below lists the output states for the S21 output pad.

|     | Displa | ay data |     | Output and (2011) state                                               |  |  |  |

|-----|--------|---------|-----|-----------------------------------------------------------------------|--|--|--|

| D81 | D82    | D83     | D84 | Output pad (S21) state                                                |  |  |  |

| 0   | 0      | 0       | 0   | The LCD segments corresponding to COM1, COM2, COM3, and COM4 are off. |  |  |  |

| 0   | 0      | 0       | 1   | The LCD segment corresponding to COM4 is on.                          |  |  |  |

| 0   | 0      | 1       | 0   | The LCD segment corresponding to COM3 is on.                          |  |  |  |

| 0   | 0      | 1       | 1   | The LCD segments corresponding to COM3 and COM4 are on.               |  |  |  |

| 0   | 1      | 0       | 0   | The LCD segment corresponding to COM2 is on.                          |  |  |  |

| 0   | 1      | 0       | 1   | The LCD segments corresponding to COM2 and COM4 are on.               |  |  |  |

| 0   | 1      | 1       | 0   | The LCD segments corresponding to COM2 and COM3 are on.               |  |  |  |

| 0   | 1      | 1       | 1   | The LCD segments corresponding to COM2, COM3, and COM4 are on.        |  |  |  |

| 1   | 0      | 0       | 0   | The LCD segment corresponding to COM1 is on.                          |  |  |  |

| 1   | 0      | 0       | 1   | The LCD segments corresponding to COM1 and COM4 are on.               |  |  |  |

| 1   | 0      | 1       | 0   | The LCD segments corresponding to COM1 and COM3 are on.               |  |  |  |

| 1   | 0      | 1       | 1   | The LCD segments corresponding to COM1, COM3, and COM4 are on.        |  |  |  |

| 1   | 1      | 0       | 0   | The LCD segments corresponding to COM1 and COM2 are on.               |  |  |  |

| 1   | 1      | 0       | 1   | The LCD segments corresponding to COM1, COM2, and COM4 are on.        |  |  |  |

| 1   | 1      | 1       | 0   | The LCD segments corresponding to COM1, COM2, and COM3 are on.        |  |  |  |

| 1   | 1      | 1       | 1   | The LCD segments corresponding to COM1, COM2, COM3, and COM4 are on.  |  |  |  |

| splay Data | and Outp | ut Pad Co | orrespon | aence | e (1/3 Duty) | -    | -    |     |

|------------|----------|-----------|----------|-------|--------------|------|------|-----|

| Output pad | COM1     | COM2      | COM3     |       | Output pad   | COM1 | COM2 | CON |

| S1         | D1       | D2        | D3       |       | S28          | D82  | D83  | D84 |

| S2         | D4       | D5        | D6       |       | S29          | D85  | D86  | D8  |

| S3         | D7       | D8        | D9       |       | S30          | D88  | D89  | D9  |

| S4         | D10      | D11       | D12      |       | S31          | D91  | D92  | D9  |

| S5         | D13      | D14       | D15      |       | S32          | D94  | D95  | D9  |

| S6         | D16      | D17       | D18      |       | S33          | D97  | D98  | D9  |

| S7         | D19      | D20       | D21      |       | S34          | D100 | D101 | D10 |

| S8         | D22      | D23       | D24      |       | S35          | D103 | D104 | D10 |

| S9         | D25      | D26       | D27      |       | S36          | D106 | D107 | D10 |

| S10        | D28      | D29       | D30      |       | S37          | D109 | D110 | D1  |

| S11        | D31      | D32       | D33      |       | S38          | D112 | D113 | D1  |

| S12        | D34      | D35       | D36      |       | S39          | D115 | D116 | D1  |

| S13        | D37      | D38       | D39      |       | S40          | D118 | D119 | D12 |

| S14        | D40      | D41       | D42      |       | S41          | D121 | D122 | D1: |

| S15        | D43      | D44       | D45      |       | S42          | D124 | D125 | D12 |

| S16        | D46      | D47       | D48      |       | S43          | D127 | D128 | D12 |

| S17        | D49      | D50       | D51      |       | S44          | D130 | D131 | D1  |

| S18        | D52      | D53       | D54      |       | S45          | D133 | D134 | D13 |

| S19        | D55      | D56       | D57      |       | S46          | D136 | D137 | D1  |

| S20        | D58      | D59       | D60      |       | S47          | D139 | D140 | D1  |

| S21        | D61      | D62       | D63      |       | S48          | D142 | D143 | D1  |

| S22        | D64      | D65       | D66      |       | S49          | D145 | D146 | D1  |

| S23        | D67      | D68       | D69      |       | S50          | D148 | D149 | D1  |

| S24        | D70      | D71       | D72      |       | S51          | D151 | D152 | D1: |

| S25        | D73      | D74       | D75      |       | S52          | D154 | D155 | D1: |

| S26        | D76      | D77       | D78      |       | S53          | D157 | D158 | D1: |

| S27        | D79      | D80       | D81      |       |              |      |      |     |

#### Display Data and Output Pad Correspondence (1/3 Duty)

(Note) In external clock operating mode, S53 pad outputs V<sub>SS</sub> level. When DN is "0", S52 pad and S53 pad output V<sub>SS</sub> level.

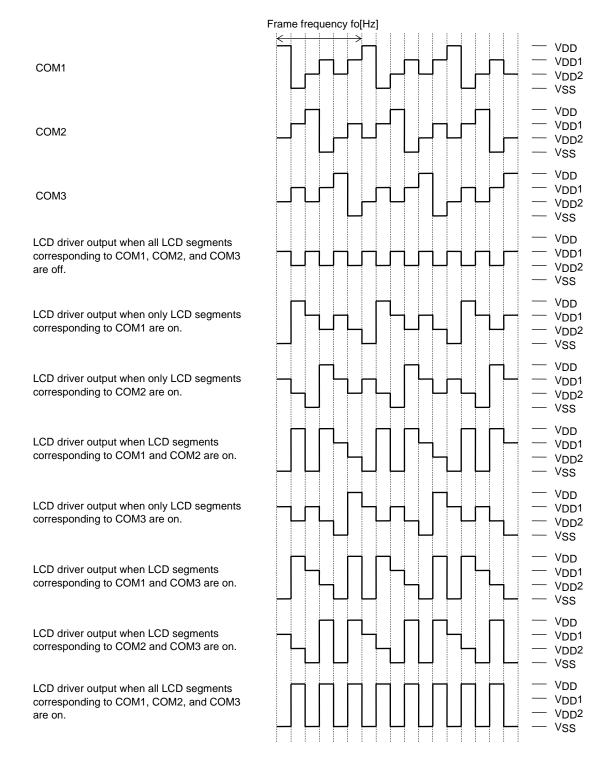

For example, the table below lists the output states for the S21 output pad.

|     | Display data |     | Output pod (S24) state                                          |  |  |  |

|-----|--------------|-----|-----------------------------------------------------------------|--|--|--|

| D61 | D62          | D63 | Output pad (S21) state                                          |  |  |  |

| 0   | 0            | 0   | The LCD segments corresponding to COM1, COM2, and COM3 are off. |  |  |  |

| 0   | 0            | 1   | The LCD segment corresponding to COM3 is on.                    |  |  |  |

| 0   | 1            | 0   | The LCD segment corresponding to COM2 is on.                    |  |  |  |

| 0   | 1            | 1   | The LCD segments corresponding to COM2 and COM3 are on.         |  |  |  |

| 1   | 0            | 0   | The LCD segment corresponding to COM1 is on.                    |  |  |  |

| 1   | 0            | 1   | The LCD segments corresponding to COM1 and COM3 are on.         |  |  |  |

| 1   | 1            | 0   | The LCD segments corresponding to COM1 and COM2 are on.         |  |  |  |

| 1   | 1            | 1   | The LCD segments corresponding to COM1, COM2, and COM3 are on.  |  |  |  |

#### Output Waveforms (1/4-Duty 1/3-Bias Drive Scheme)

(Note) The frame frequency fo[Hz] is adjustable by setting control data (EXF, FC0 to FC2 and OC). (See "Control Data Functions" for details)

#### **Output Waveforms (1/3-Duty 1/3-Bias Drive Scheme)**

(Note) The frame frequency fo[Hz] is adjustable by setting control data (EXF, FC0 to FC2 and OC). (See "Control Data Functions" for details)

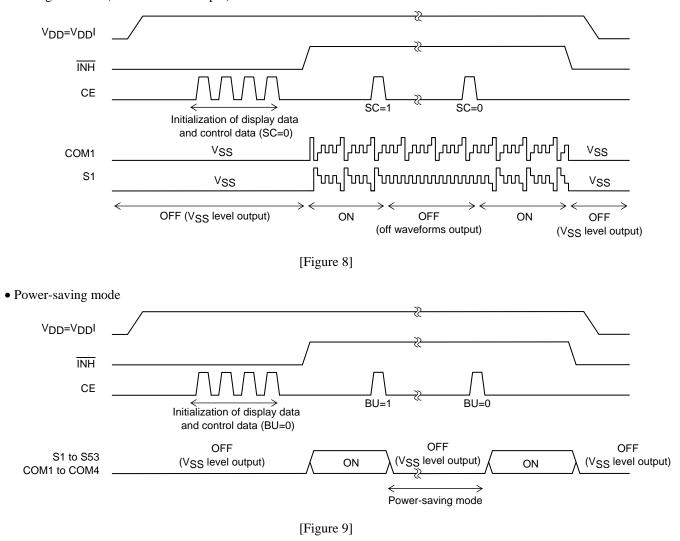

## Display Control and the INH Pad

Since the LSI internal data (1/4 duty : the display data D1 to D208 and the control data, 1/3 duty : the display data D1 to D159 and the control data) is undefined when power is first applied. Applications should set the INH pad low at the same time as power is applied to turn off the display (This sets the S1 to S53 and COM1 to COM4 pads the V<sub>SS</sub> level.) and during this period send serial data from the controller. The controller should then set the INH pad high after the data transfer has completed. This procedure prevents meaningless display at power on. VDD and VDDI are connected with the same power supply. The timing of turn on and turn off for VDD and VDDI should be same time. (See from Figure 5 to Figure 8)

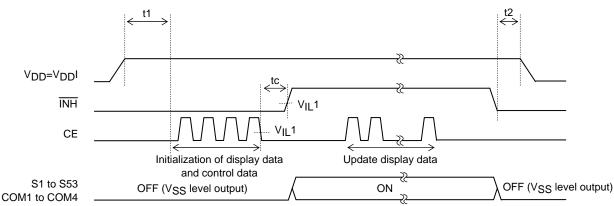

• 1/4 duty

(Note) The wait time (t1) which power supply turn on should be 1ms or more.

The discharge time (t2) of LCD panel's electric charge should be decided the optimum value according to the characteristic of the LCD panel.

The switching time (tc) of  $\overline{INH}$  should be 10µs or more.

#### [Figure 5]

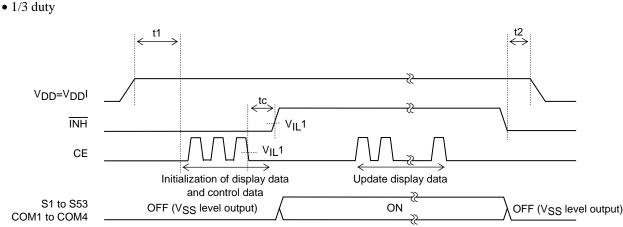

(Note) The wait time (t1) which power supply turn on should be 1ms or more.

The discharge time (t2) of LCD panel's electric charge should be decided the optimum value according to the characteristic of the LCD panel.

The switching time (tc) of INH should be 10µs or more.

[Figure 6]

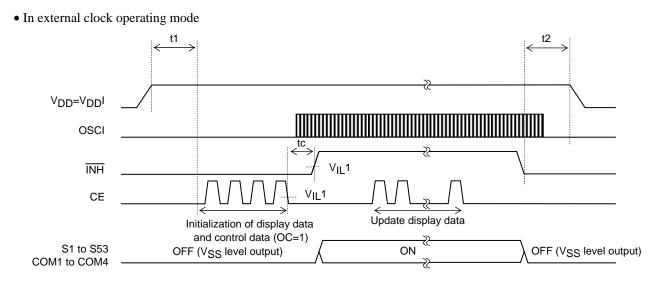

(Note) The wait time (t1) which power supply turn on should be 1ms or more.

The discharge time (t2) of LCD panel's electric charge should be decided the optimum value according to the characteristic of the LCD panel.

The switching time (tc) of  $\overline{\text{INH}}$  should be 10µs or more.

OSCI pad should be input an external clock at INH is high level.

[Figure 7]

• All segments off (off waveforms output)

#### Notes on Controller Transfer of Display Data

When using the LC450029PKB in 1/4 duty, applications transfer the display data (D1 to D208) in four operations, and in 1/3 duty, they transfer the display data (D1 to D159) in three operations. In either case, applications should transfer all of the display data within 30ms to maintain the quality of displayed image.

About peripheral circuit of the input pad

(1) Processing of unused OSCI pad

When OSCI pad is not to be used, select the internal oscillator operating mode (control data OC="0"), and OSCI pad is connected to GND.

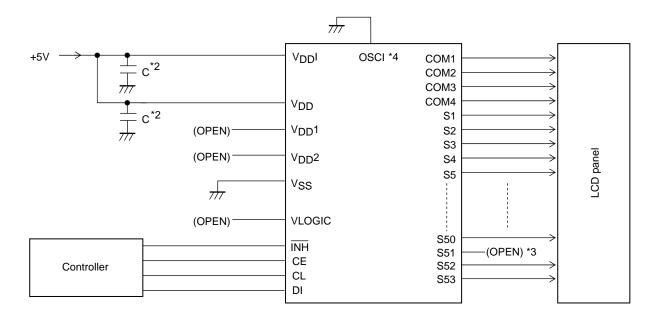

#### Sample Applications Circuit 1

1/4 duty, Display data (D1 to D208), Internal oscillator operating mode

#### **Sample Applications Circuit 2**

1/4 duty, Display data (D1 to D204), External clock operating mode

- \*2 Connect capacitors between a power supply line and GND for noise removal and power supply stabilization. Determine the value of a capacitor, after an actual circuit board estimates.

- \*3 In 1/4 duty, S51 pad outputs VSS level.

- \*4 When OSCI pad is not to be used, select the internal oscillator operating mode (control data OC="0"), and OSCI pad is connected to GND.

- \*5 In external clock operating mode, S53 pad outputs VSS level.

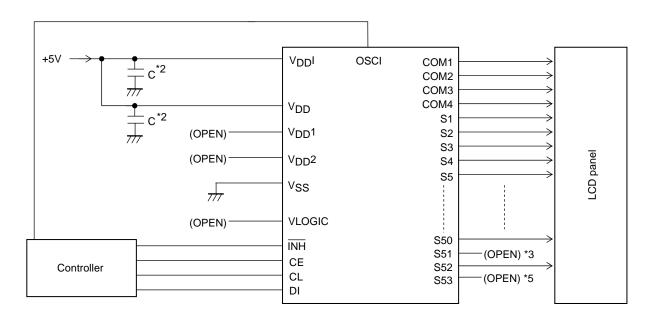

# Sample Applications Circuit 3

1/3 duty, Display data (D1 to D159), Internal oscillator operating mode

\*2 Connect capacitors between a power supply line and GND for noise removal and power supply stabilization. Determine the value of a capacitor, after an actual circuit board estimates.

$^{*}6$  In 1/3 duty, COM4 pad outputs  $V_{\ensuremath{SS}}$  level.

#### The Notes on Use

Important things for stability operation of IC are shown as follows. The contents indicated below do not guarantee IC operation and the characteristic. Moreover, the example of an application circuit written in these specifications is for explaining internal operation and usage. Therefore, please perform the design in consideration of the specification of operation and terms and conditions in the actual LCD panel.

(1) The design of power supply

All power supply pads are connected to the power supply, and do not set open.

(2) ITO (Indium Tin Oxide) wiring

By designing the wire of power supply ( $V_{DD}$ ,  $V_{DDI}$ ,  $V_{SS}$ ) wide and short, make the parasitic resistance of ITO wiring into the minimum.

- (3) Signal wiring and connection The DUMMY pad does not connect to anywhere, and sets open.

- (4) Processing of unused input pad

For CMOS process, if an input pad is in open state, operation of IC may become unstable, or unnecessary power supply current may flow through it. Please be sure to connect the empty pad of a logic input to  $V_{SS}$ .

(5) The measure against shading

The optical irradiation to IC causes the mis-operation of IC. When IC is implemented, take the measures against shading about the surface, back and side of IC.

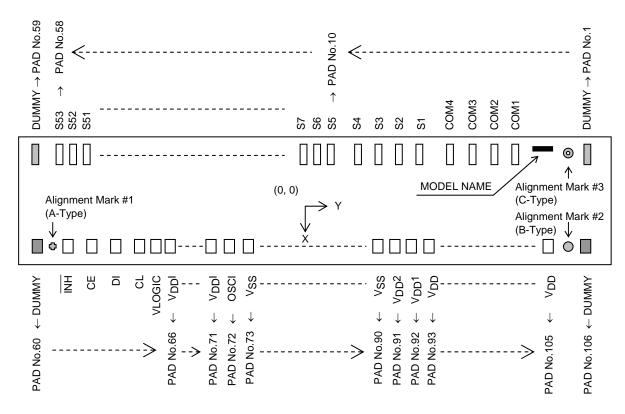

• PAD Locations (Bump Side View)

- Chip dimensions (X, Y, S are based on the dicing center.)

X=1.00mm Y=4.08mm S=4.08mm<sup>2</sup> Wafer thickness=400μm (typ)

- Au Bump dimensions (typ)

|                     |                                            | Size   |        |         |  |  |  |

|---------------------|--------------------------------------------|--------|--------|---------|--|--|--|

| Item                | PAD No.                                    | X [μm] | Υ [μm] | S [μm²] |  |  |  |

| Dump Size           | 1 to 59                                    | 108    | 27     | 2916    |  |  |  |

| Bump Size           | 60 to 106                                  | 68     | 42     | 2856    |  |  |  |

| Min. Duran Ditak    | 10 to 58                                   | 5      | -      |         |  |  |  |

| Min. Bump Pitch     | 1 to 9, 59 to 106                          |        | -      |         |  |  |  |

|                     | 10 to 58, 66 to 71,<br>73 to 90, 93 to 105 | 2      | -      |         |  |  |  |

| Min. Bump Clearance | 1 to 9, 59 to 65, 72,<br>91 to 92, 106     | -      |        | -       |  |  |  |

| Bump Height         | All pads                                   | 1      | 7      | -       |  |  |  |

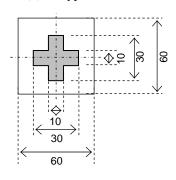

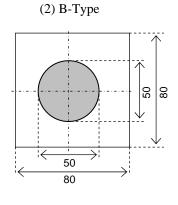

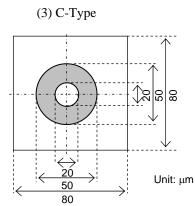

#### • Alignment marks

(1) A-Type

#### • Center coordinates of PADs

(All x/y coordinates represent the position of the center of each PAD)

| (All ) | x/y coordin | ates represe | ent the posit | ion |     | e center of e     | ach PAD | )     | _ |     |                   |      |      |

|--------|-------------|--------------|---------------|-----|-----|-------------------|---------|-------|---|-----|-------------------|------|------|

| PAD    | PAD         | Х            | Y             |     | PAD | PAD               | Х       | Y     |   | PAD | PAD               | Х    | Y    |

| No.    | Name        | [µm]         | [µm]          | -   | No. | Name              | [µm]    | [µm]  |   | No. | Name              | [µm] | [µm] |

| 1      | DUMMY       | -380         | 1950          |     | 41  | S36               | -380    | -943  |   | 81  | VSS               | 400  | 10   |

| 2      | COM1        | -380         | 1369          |     | 42  | S37               | -380    | -993  |   | 82  | VSS               | 400  | 75   |

| 3      | COM2        | -380         | 1276          |     | 43  | S38               | -380    | -1043 |   | 83  | V <sub>SS</sub>   | 400  | 140  |

| 4      | COM3        | -380         | 1183          |     | 44  | S39               | -380    | -1093 |   | 84  | VSS               | 400  | 205  |

| 5      | COM4        | -380         | 1090          |     | 45  | S40               | -380    | -1143 | _ | 85  | V <sub>SS</sub>   | 400  | 270  |

| 6      | S1          | -380         | 932           |     | 46  | S41               | -380    | -1193 |   | 86  | VSS               | 400  | 335  |

| 7      | S2          | -380         | 856           |     | 47  | S42               | -380    | -1243 |   | 87  | VSS               | 400  | 400  |

| 8      | S3          | -380         | 780           |     | 48  | S43               | -380    | -1293 |   | 88  | V <sub>SS</sub>   | 400  | 465  |

| 9      | S4          | -380         | 704           |     | 49  | S44               | -380    | -1343 |   | 89  | V <sub>SS</sub>   | 400  | 530  |

| 10     | S5          | -380         | 607           |     | 50  | S45               | -380    | -1393 |   | 90  | VSS               | 400  | 595  |

| 11     | S6          | -380         | 557           |     | 51  | S46               | -380    | -1443 |   | 91  | V <sub>DD</sub> 2 | 400  | 668  |

| 12     | S7          | -380         | 507           |     | 52  | S47               | -380    | -1493 |   | 92  | V <sub>DD</sub> 1 | 400  | 739  |

| 13     | S8          | -380         | 457           |     | 53  | S48               | -380    | -1543 |   | 93  | V <sub>DD</sub>   | 400  | 811  |

| 14     | S9          | -380         | 407           |     | 54  | S49               | -380    | -1593 |   | 94  | V <sub>DD</sub>   | 400  | 876  |

| 15     | S10         | -380         | 357           |     | 55  | S50               | -380    | -1643 |   | 95  | V <sub>DD</sub>   | 400  | 941  |

| 16     | S11         | -380         | 307           |     | 56  | S51               | -380    | -1693 |   | 96  | V <sub>DD</sub>   | 400  | 1006 |

| 17     | S12         | -380         | 257           |     | 57  | S52               | -380    | -1743 |   | 97  | V <sub>DD</sub>   | 400  | 1071 |

| 18     | S13         | -380         | 207           |     | 58  | S53               | -380    | -1793 |   | 98  | V <sub>DD</sub>   | 400  | 1136 |

| 19     | S14         | -380         | 157           |     | 59  | DUMMY             | -380    | -1950 |   | 99  | V <sub>DD</sub>   | 400  | 1201 |

| 20     | S15         | -380         | 107           |     | 60  | DUMMY             | 400     | -1943 |   | 100 | V <sub>DD</sub>   | 400  | 1266 |

| 21     | S16         | -380         | 57            |     | 61  | ĪNH               | 400     | -1665 |   | 101 | V <sub>DD</sub>   | 400  | 1331 |

| 22     | S17         | -380         | 7             |     | 62  | CE                | 400     | -1525 |   | 102 | V <sub>DD</sub>   | 400  | 1396 |

| 23     | S18         | -380         | -43           |     | 63  | DI                | 400     | -1385 |   | 103 | V <sub>DD</sub>   | 400  | 1461 |

| 24     | S19         | -380         | -93           |     | 64  | CL                | 400     | -1245 |   | 104 | V <sub>DD</sub>   | 400  | 1526 |

| 25     | S20         | -380         | -143          |     | 65  | VLOGIC            | 400     | -1161 |   | 105 | V <sub>DD</sub>   | 400  | 1591 |

| 26     | S21         | -380         | -193          |     | 66  | VDDI              | 400     | -1071 |   | 106 | DUMMY             | 400  | 1943 |

| 27     | S22         | -380         | -243          |     | 67  | VDDI              | 400     | -1006 | _ |     |                   |      | I    |

| 28     | S23         | -380         | -293          |     | 68  | V <sub>DD</sub> I | 400     | -941  |   |     |                   |      |      |

| 29     | S24         | -380         | -343          |     | 69  | V <sub>DD</sub> I | 400     | -876  |   |     |                   |      |      |

| 30     | S25         | -380         | -393          |     | 70  | V <sub>DD</sub> I | 400     | -811  |   |     |                   |      |      |

| 31     | S26         | -380         | -443          |     | 71  | V <sub>DD</sub> I | 400     | -746  |   |     |                   |      |      |

| 32     | S27         | -380         | -493          |     | 72  | OSCI              | 400     | -650  |   |     |                   |      |      |

| 33     | S28         | -380         | -543          |     | 73  | V <sub>SS</sub>   | 400     | -510  |   |     |                   |      |      |

| 34     | S29         | -380         | -593          |     | 74  | V <sub>SS</sub>   | 400     | -445  |   |     |                   |      |      |

| 35     | S30         | -380         | -643          |     | 75  | V <sub>SS</sub>   | 400     | -380  |   |     |                   |      |      |

| 36     | S31         | -380         | -693          | ╞   | 76  | V <sub>SS</sub>   | 400     | -315  |   |     |                   |      |      |

| 37     | \$32        | -380         | -743          | ┢   | 77  | V <sub>SS</sub>   | 400     | -250  |   |     |                   |      |      |

| 38     | S33         | -380         | -793          | ╞   | 78  | V <sub>SS</sub>   | 400     | -185  |   |     |                   |      |      |

| 39     | S34         | -380         | -843          | ╞   | 79  | V <sub>SS</sub>   | 400     | -120  |   |     |                   |      |      |

| 40     | S35         | -380         | -893          | ╞   | 80  | V <sub>SS</sub>   | 400     | -55   |   |     |                   |      |      |

| L      |             |              |               | L   |     | - 35              |         |       |   |     |                   |      |      |

• Center coordinates of alignment marks

(All x/y coordinates represent the position of the center of each alignment mark)

| Alignment mark | TYPE | X [μm] | Υ [μm] |

|----------------|------|--------|--------|

| 1              | А    | 400    | -1800  |

| 2              | В    | 400    | 1790   |

| 3              | С    | -380   | 1800   |

#### **ORDERING INFORMATION**

| Device         | Package            | Shipping (Qty / Packing) |

|----------------|--------------------|--------------------------|

| LC450029PKB-XT | Wafer<br>(Pb-Free) | 1 / Waffle Pack          |

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the existing on a manufactur of the part. ON Semiconductor products and explexes, and reasonable attor