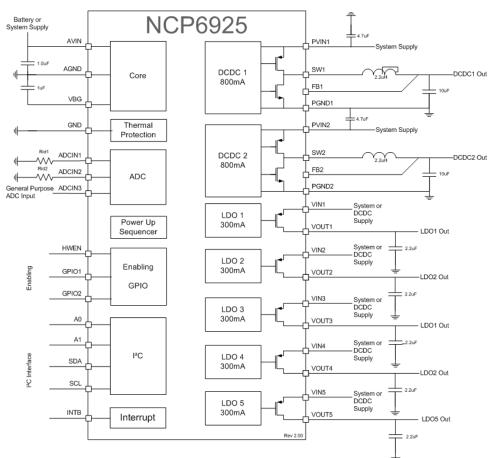

# 7-Channel PMIC with2 DC-DC Converters,5 LDOs and a Triple Input10 Bits ADC

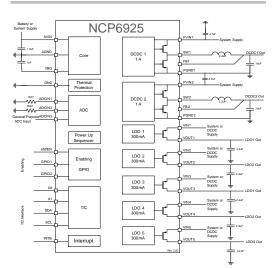

The NCP6925 integrated circuit is part of the ON Semiconductor mini power management IC family (PMIC). It is optimized to supply battery powered portable application sub–systems such as camera function, microprocessors. This device integrates 2 high efficiency 1 A step–down DC–DC converters, 5 low dropout (LDO) voltage regulators and a triple input 10 bits ADC in a WLCSP36 2.36 x 2.36 mm package.

#### Features

- 2 DC–DC Converters (3 MHz,  $1 2.2 \mu$ H / 10  $\mu$ F, 1 A)

- Peak Efficiency 95%

- Programmable Output Voltage from 0.6 V to 3.3 V by 12.5 mV Steps

- 5 Low Noise Low Drop Out Regulators (2.2 µF, 300 mA)

- Programmable Output Voltage from 0.8 V to 3.5 V by 25 mV Steps

- 50 μVrms Typical Low Output Noise

- Triple Input 10 Bits ADC

- Dual Resistor Measurement Mode

- General Purpose Mode

- Control

- Fully Programmable through a 400 kHz / 3.4 MHz I<sup>2</sup>C with Pin Selectable I<sup>2</sup>C Address and Interrupt Output

- General Purpose I/O Pins that can be Used as Internal / External Regulator Enable Pins or Internal Sequences Triggered Input

- Flexible Power-up and Down Sequences Programmable by I<sup>2</sup>C

- 140 µA Very Low Quiescent Current at No Load

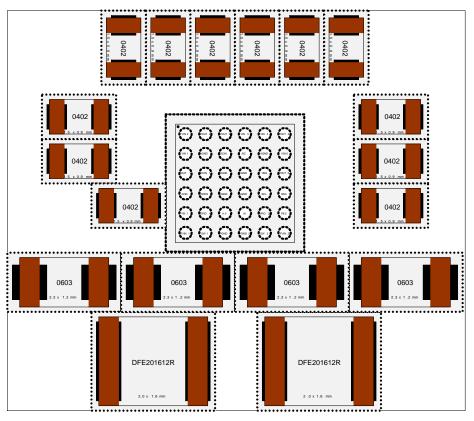

- Small Footprint: 2.36 x 2.36 mm WLCSP 0.4 mm Pitch

# **Typical Applications**

- Cellular Phones, Tablets

- Digital Cameras

# **ON Semiconductor®**

www.onsemi.com

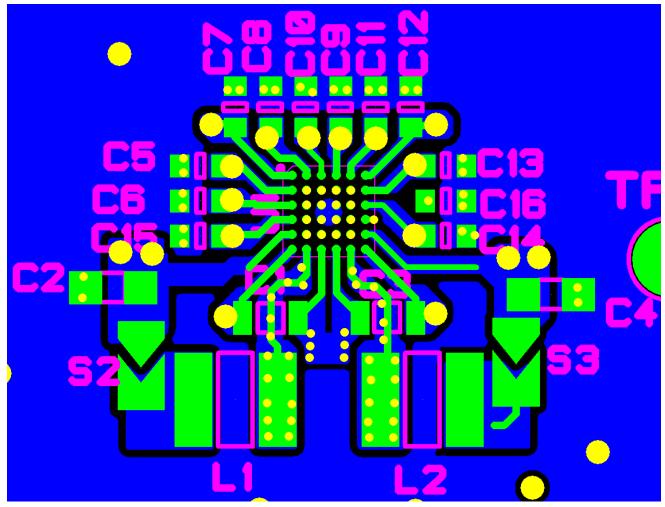

Figure 1. Application Schematic

# **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 42 of this data sheet.

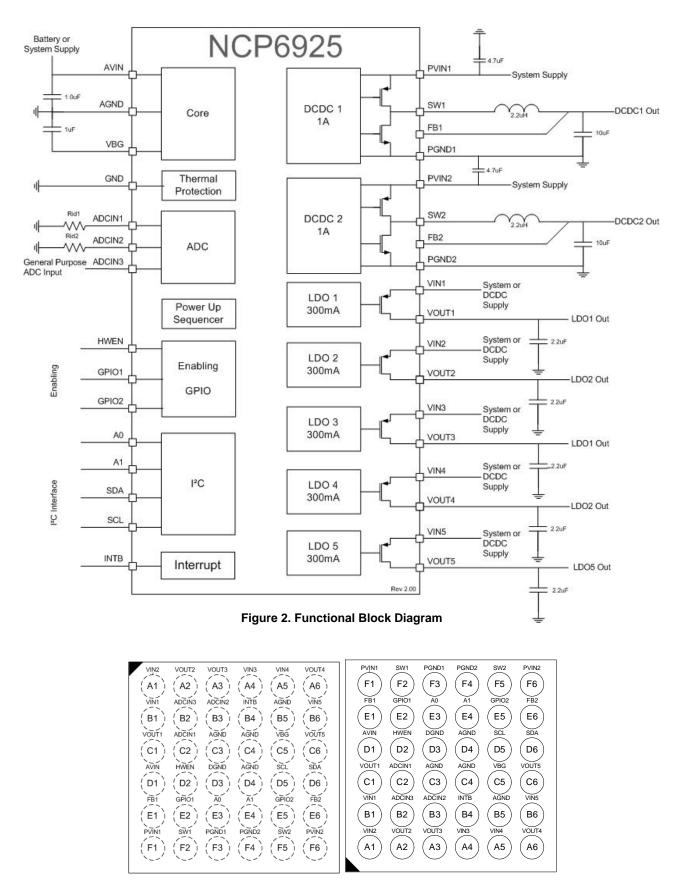

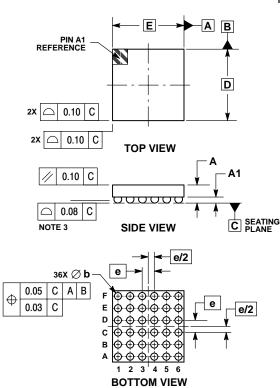

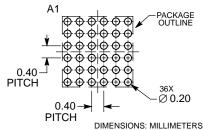

Figure 3. Pin Out Description (Top and Bottom Views)

#### Table 1. PIN FUNCTION DESCRIPTION

| Pin               | Name      | Туре                    | Description                                                                                                                                                                                                    |

|-------------------|-----------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SUPPLY            |           |                         |                                                                                                                                                                                                                |

| D1                | AVIN      | Analog Input            | Analog Supply. This pin is the device analog and digital supply. A 1.0 $\mu F$ ceramic capacitor or larger must bypass this input to ground. This capacitor should be placed as close as possible to this pin. |

| B5, C3,<br>C4, D4 | AGND      | Analog Ground           | Analog Ground. Analog and digital modules ground. Must be connected to the system ground.                                                                                                                      |

| D3                | DGND      | Digital Ground          | Digital Ground. Analog and digital modules ground. Must be connected to the system ground.                                                                                                                     |

| C5                | VBG       | Analog Output           | Reference voltage for analog internal block. This pin requires a 100 nF up to 1 $\mu\text{F}$ decoupling capacitor.                                                                                            |

| CONTROL           | AND SERIA | L INTERFACE             | •                                                                                                                                                                                                              |

| D2                | HWEN      | Digital Input           | Hardware Enable. Active high will enable the part. There is an internal pull down resistor on this pin.                                                                                                        |

| D5                | SCL       | Digital Input           | I <sup>2</sup> C interface Clock line                                                                                                                                                                          |

| D6                | SDA       | Digital<br>Input/Output | I <sup>2</sup> C interface Bi-directional Data line.                                                                                                                                                           |

| B4                | INTB      | Digital Output          | Interrupt open drain output                                                                                                                                                                                    |

| E3                | A0        | Digital Input           | I <sup>2</sup> C selection input                                                                                                                                                                               |

| E4                | A1        | Digital Input           | I <sup>2</sup> C selection input                                                                                                                                                                               |

| E2                | GPIO1     | Digital<br>Input/Output | General purpose input / output                                                                                                                                                                                 |

| E5                | GPIO2     | Digital<br>Input/Output | General purpose input / output                                                                                                                                                                                 |

#### DCDC CONVERTERS

| F1 | PVIN1 | Power Input  | DCDC1 Power Supply. This pin must be decoupled to ground by a 4.7 $\mu F$ ceramic capacitor. This capacitor should be placed as close as possible to this pin.                                                                                               |

|----|-------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F2 | SW1   | Power Output | DCDC1 Switch Power. This pin connects the power transistors to one end of the inductor. Typical application uses 1.0 – 2.2 $\mu$ H inductor; refer to application section for more information.                                                              |

| E1 | FB1   | Analog Input | DCDC1 Feedback Voltage. This pin is the input to the error amplifier and must be connected to the output capacitor.                                                                                                                                          |

| F3 | PGND1 | Power Ground | DCDC1 Power Ground. This pin is the power ground and carries the high switching current. A high quality ground must be provided to prevent noise spikes. A local ground plane is re-<br>commended to avoid high-density current flow in a limited PCB track. |

| F6 | PVIN2 | Power Input  | DCDC2 Power Supply. This pin must be decoupled to ground by a 4.7 $\mu F$ ceramic capacitor. This capacitor should be placed as close as possible to this pin.                                                                                               |

| F5 | SW2   | Power Output | DCDC2 Switch Power. This pin connects the power transistors to one end of the inductor. Typical application uses 1.0 – 2.2 $\mu$ H inductor; refer to application section for more information.                                                              |

| E6 | FB2   | Analog Input | DCDC2 Feedback Voltage. This pin is the input to the error amplifier and must be connected to the output capacitor.                                                                                                                                          |

| F4 | PGND2 | Power Ground | DCDC1 Power Ground. This pin is the power ground and carries the high switching current. A high quality ground must be provided to prevent noise spikes. A local ground plane is recommended to avoid high-density current flow in a limited PCB track.      |

#### LDO REGULATORS

| B1 | VIN1  | Power Input  | LDO1 Power Supply.                                                           |

|----|-------|--------------|------------------------------------------------------------------------------|

| C1 | VOUT1 | Power Output | LDO1 Output Power. This pin requires a 1 – 2.2 $\mu F$ decoupling capacitor. |

| A1 | VIN2  | Power Input  | LDO2 Power Supply.                                                           |

| A2 | VOUT2 | Power Output | LDO2 Output Power. This pin requires a 1 – 2.2 $\mu F$ decoupling capacitor. |

| A4 | VIN3  | Power Input  | LDO3 Power Supply                                                            |

#### Table 1. PIN FUNCTION DESCRIPTION

|       |                                | Description                                                                   |  |  |  |

|-------|--------------------------------|-------------------------------------------------------------------------------|--|--|--|

| ATORS |                                |                                                                               |  |  |  |

| VOUT3 | Power Output                   | LDO3 Output Power. This pin requires a 1 – 2.2 $\mu F$ decoupling capacitor.  |  |  |  |

| VIN4  | Power Input                    | LDO4 Power Supply                                                             |  |  |  |

| VOUT4 | Power Output                   | LDO4 Output Power. This pin requires a 1 – 2.2 $\mu F$ decoupling capacitor.  |  |  |  |

| VIN5  | Power Input                    | LDO5 Power Supply.                                                            |  |  |  |

| VOUT5 | Power Output                   | LDO5 Output Power. This pin requires a 1 – 2.2 $\mu F$ decoupling capacitor.  |  |  |  |

|       | VOUT3<br>VIN4<br>VOUT4<br>VIN5 | VOUT3 Power Output   VIN4 Power Input   VOUT4 Power Output   VIN5 Power Input |  |  |  |

ADC

| C2 | ADCIN1 | Analog Input | 10 bits ADC input 1. |

|----|--------|--------------|----------------------|

| B3 | ADCIN2 | Analog Input | 10 bits ADC input 2. |

| B2 | ADCIN3 | Analog Input | 10 bits ADC input 3. |

#### Table 2. MAXIMUM RATINGS (Note 1)

| Rating                                          | Symbol                             | Value                                   | Unit    |

|-------------------------------------------------|------------------------------------|-----------------------------------------|---------|

| Analog and power pins:                          | V <sub>A</sub>                     | -0.3 to +6.0                            | V       |

| Digital pins:<br>Input Voltage<br>Input Current | V <sub>DG</sub><br>I <sub>DG</sub> | -0.3 to V <sub>A</sub> +0.3 ≤ 6.0<br>10 | V<br>mA |

| Storage Temperature Range                       | T <sub>STG</sub>                   | –65 to +150                             | °C      |

| Maximum Junction Temperature                    | T <sub>JMAX</sub>                  | -40 to +150                             | °C      |

| Moisture Sensitivity                            | MSL                                | Level 1                                 |         |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. All voltages are related to AGND.

2. ESDrated to the following:

Human Body Model (HBM) ±2.0 kV per JEDEC standard: JESD22-A114.

Machine Model (MM) ±150 V per JEDEC standard: JESD22-A115.

3. Latch up Current per JEDEC standard: JESD78 class II.

4. Moisture Sensitivity Level (MSL): 1 per IPC/JEDEC standard: J-STD-020A.

# Table 3. RECOMMENDED OPERATING CONDITIONS

| Symbol                | Parameter                                | Conditions           | Min | Тур     | Max  | Unit |

|-----------------------|------------------------------------------|----------------------|-----|---------|------|------|

| $AV_{IN}$ , $PV_{IN}$ | Analog and Power Supply                  |                      | 2.5 |         | 5.5  | V    |

| LDO <sub>VIN</sub>    | LDO Input Voltage range                  |                      | 1.7 |         | 5.5  | V    |

| T <sub>A</sub>        | Ambient Temperature Range                |                      | -40 | 25      | +85  | °C   |

| TJ                    | Junction Temperature Range               |                      | -40 | 25      | +125 | °C   |

| Raja                  | Thermal Resistance Junction to Ambient   |                      | -   | 40      | _    | °C/W |

| PD                    | Power Dissipation Rating                 | $T_A \le 85^\circ C$ | -   | 1       | -    | W    |

|                       |                                          | $T_A = 40^{\circ}C$  | -   | 2.1     | -    | W    |

| L                     | Inductor for DC to DC converters         |                      | -   | 1 – 2.2 | -    | μH   |

| Со                    | Output Capacitor for DC to DC Converters |                      | -   | 10      | -    | μF   |

|                       | Output Capacitors for LDO                |                      | -   | 1 – 2.2 | -    | μF   |

| Cin                   | Input Capacitor for DC to DC Converters  |                      | -   | 4.7     | -    | μF   |

5. Refer to the Application Information section of this data sheet for more details.

6. The thermal shutdown set to 150°C (typical) avoids potential irreversible damage on the device due to power dissipation.

7. The R<sub>0JA</sub> is dependent of the PCB heat dissipation. Board used to drive this data was a NCP6925EVB board. It is a multilayer board with 1–ounce internal power and ground planes and 2–ounce copper traces on top and bottom of the board.

8. The maximum power dissipation (P<sub>D</sub>) is dependent by input voltage, maximum output current and external components selected.

$$\mathsf{R}_{\theta \mathsf{J} \mathsf{A}} = \frac{\mathsf{125} - \mathsf{T}_{\mathsf{A}}}{\mathsf{P}_{\mathsf{D}}}$$

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

**Table 4. ELECTRICAL CHARACTERISTICS** Min & Max Limits apply for  $T_A = -40^{\circ}$ C to +85°C unless otherwise specified. AV<sub>IN</sub> = PV<sub>IN1</sub> = PV<sub>IN2</sub> = V<sub>IN1</sub> = V<sub>IN2</sub> = V<sub>IN3</sub> = V<sub>IN3</sub> = V<sub>IN5</sub> = 3.6 V (Unless otherwise noted). DCDC1 = 1.05 V, DCDC2 = 1.2 V, LDO1&2&3 = 2.85 V, LDO4&5 = 1.8 V. Typical values are referenced to  $T_A = +25^{\circ}$ C and default configuration (Note 10)

| Symbol             | Parameter                                                            | Conditions                                                                                         | Min | Тур | Max | Unit |

|--------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| SUPPLY CU          | RRENT: Pins AV <sub>IN</sub> – PV <sub>IN1</sub> – PV <sub>IN1</sub> | $v_{1} - v_{1N1} - v_{1N2} - v_{1N3} - v_{1N4} - v_{1N5}$                                          |     |     | -   |      |

| Ι <sub>Q</sub>     | Operating quiescent current                                          | DCDC1&2 on, no load, no switching LDOs off                                                         | -   | 65  | -   | μΑ   |

|                    |                                                                      | DCDC1&2 on, no load, no switching LDOs on, no load $T_A = up \text{ to } +85^{\circ}\text{C}$      | -   | 140 | -   |      |

|                    |                                                                      | DCDC1&2 Off<br>LDOs on, no load<br>$T_A = up \text{ to } +85 \text{ °C}$                           | -   | 45  | -   |      |

| I <sub>SLEEP</sub> | Sleep mode current                                                   | HWEN pin on<br>All DC to DC and LDOs off<br>$V_{IN} = 2.5 V$ to 5.5 V<br>$T_A =$ up to +85°C       | -   | 7.5 | -   | μΑ   |

| I <sub>OFF</sub>   | Shutdown current                                                     | All DCDCs and LDOs off<br>HWEN pin = off<br>$I^2C$ interface disabled<br>$V_{IN} = 2.5 V$ to 5.5 V | -   | 0.3 | 2   | μΑ   |

#### **DCDC1&2 STEP DOWN CONVERTERS**

| PVIN                 | Input Voltage Range               |                                                                       | 2.5   | -                                          | 5.5                                               | V    |

|----------------------|-----------------------------------|-----------------------------------------------------------------------|-------|--------------------------------------------|---------------------------------------------------|------|

|                      | Output Voltage Range              |                                                                       | 0.600 | -                                          | 3.3                                               | V    |

|                      | Programming Granularity           |                                                                       | -     | 12.5                                       | -                                                 | mV   |

| I <sub>OUTMAX</sub>  | Maximum Output Current            |                                                                       | 1     | -                                          | -                                                 | А    |

| $\Delta V_{OUT}$     | Output Voltage DC Error           | I <sub>OUT</sub> = 300 mA                                             | –1    | 0                                          | 1                                                 | %    |

| F <sub>SW</sub>      | Switching Frequency               |                                                                       | 2.7   | -                                          | 3.3                                               | MHz  |

| R <sub>ONHS</sub>    | P-Channel MOSFET On Resistance    | From PVIN pins to SW pins<br>PV <sub>IN</sub> = 3.6 V                 | -     | 180                                        | -                                                 | mΩ   |

| R <sub>ONLS</sub>    | N-Channel MOSFET On Resistance    | From SW pins to PGND pins $PV_{IN} = 3.6 V$                           | -     | 78                                         | -                                                 | mΩ   |

| I <sub>PK</sub>      | Peak Inductor Current             | $2.5 \text{ V} \leq \text{PV}_{\text{IN}} \leq 5.5 \text{ V}$         | 1.3   | 1.6                                        | 1.9                                               | А    |

|                      | Load Regulation                   | I <sub>OUT</sub> from 300 mA to I <sub>OUTMAX</sub>                   | -     | 5                                          | -                                                 | mV/A |

|                      | Line Regulation                   | $I_{OUT} = 300\text{mA}$<br>2.5 V $\leq$ PV <sub>IN</sub> $\leq$ 5.5V | -     | 0                                          | 3.3<br>-<br>1<br>3.3<br>-<br>1<br>3.3<br>-<br>1.9 | mV   |

| D                    | Maximum Duty Cycle                |                                                                       | -     | 100                                        | -                                                 | %    |

| t <sub>START</sub>   | Soft-Start Time                   |                                                                       | -     | 850                                        | -                                                 | μS   |

| R <sub>DISDCDC</sub> | DCDC Active Output Discharge      |                                                                       | -     | 7                                          | -                                                 | Ω    |

| U <sub>VP_BUCK</sub> | Under voltage threshold detection |                                                                       | -     | V <sub>OUT_BU</sub><br><sub>СК</sub> х 0.9 | -                                                 | V    |

01 TO LDO5 LOW DROP OUT REGULATORS

VIN Input voltage range

9. Devices that use non-standard supply voltages which do not conform to the intent I<sup>2</sup>C bus system levels must relate their input levels to the  $V_{DD}$  voltage to which the pull-up resistors  $R_P$  are connected.

1.7

V

5.5

10. Refer to the Application Information section of this data sheet for more details.

11. Guaranteed by design and characterized.

Table 4. ELECTRICAL CHARACTERISTICS Min & Max Limits apply for T<sub>A</sub> = -40°C to +85°C unless otherwise specified. AV<sub>IN</sub> =  $PV_{IN1} = PV_{IN2} = V_{IN1} = V_{IN2} = V_{IN3} = V_{IN4} = V_{IN5} = 3.6 V (Unless otherwise noted). DCDC1 = 1.05 V, DCDC2 = 1.2 V, LDO1&2&3 = 2.85 V, LDO4&5 = 1.8 V. Typical values are referenced to T<sub>A</sub> = +25°C and default configuration (Note 10)$

| Symbol              | Parameter                         | Conditions                                                                                                                               | Min | Тур                                         | Max  | Unit |

|---------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------------|------|------|

| LDO1 TO LI          | 005 LOW DROP OUT REGULATORS       |                                                                                                                                          |     |                                             |      |      |

| V <sub>OUT</sub>    | Output Voltage Range              |                                                                                                                                          | 0.8 | -                                           | 3.50 | V    |

|                     | Programming Granularity           |                                                                                                                                          | -   | 25                                          | -    | mV   |

| I <sub>OUTMAX</sub> | Maximum Output Current            |                                                                                                                                          | 300 | -                                           | -    | mA   |

| I <sub>LIM</sub>    | Current limitation                | (Note 11)                                                                                                                                | 360 | -                                           | 700  | mA   |

| I <sub>SC</sub>     | Short Circuit Protection          | Foldback current                                                                                                                         | -   | 180                                         | -    | mA   |

| t <sub>START</sub>  | Soft-Start Time                   | Vout = 1.8 V<br>Vout = 2.85 V                                                                                                            | -   | 110<br>160                                  | -    | μs   |

| $\Delta V_{OUT}$    | Output Voltage Accuracy DC        | I <sub>OUT</sub> = 300 mA                                                                                                                | -2  | V <sub>NOM</sub>                            | +2   | %    |

|                     | Load Regulation                   | I <sub>OUT</sub> = 0 mA to 300 mA                                                                                                        | -   | 0.4                                         | -    | %    |

|                     | Line Regulation                   | V <sub>IN</sub> = 2.5 V to 5.5 V<br>V <sub>OUT</sub> = 1.8 V, I <sub>OUT</sub> = 300 mA                                                  | -   | 0.3                                         | -    | %    |

| V <sub>DROP</sub>   | Dropout Voltage                   | $    I_{OUT} = 300 \text{ mA} \\ V_{OUT} = V_{NOM} - 2\%, V_{NOM} = 1.8 \text{ V} \\ V_{OUT} = V_{NOM} - 2\%, V_{NOM} = 2.85 \text{ V} $ |     | 300<br>170                                  | -    | mV   |

| PSRR                | Ripple Rejection                  | F = 10 kHz<br>V <sub>OUT</sub> = 2.8 V, I <sub>OUT</sub> = 100 mA (Note 11)                                                              | -   | -50                                         | _    | dB   |

| Noise               |                                   | 100 Hz $\rightarrow$ 100 kHz,<br>V <sub>OUT</sub> = 2.8 V, I <sub>OUT</sub> = 100 mA (Note 11)                                           | -   | 50                                          | _    | μV   |

| R <sub>DISLDO</sub> | LDO Active Output Discharge       |                                                                                                                                          | -   | 25                                          | _    | Ω    |

| $U_{VP\_LDO}$       | Under voltage threshold detection |                                                                                                                                          | -   | V <sub>OUT_LD</sub><br><sub>O</sub> x 0.875 | -    | V    |

#### ADC

| Reference voltage | Bandgap x 2                | -    | 2.4   | -     | V   |

|-------------------|----------------------------|------|-------|-------|-----|

| Input Range       | From zero to full scale    | 0    | -     | 2.390 | V   |

| Resolution        |                            | _    | 2.344 | -     | mV  |

| Offset error      |                            | -1   | -     | +1    | LSB |

| Gain error        | % of the FS                | -    | ±0.5  | -     | %   |

| INL               | Integral non-linearity     | -1.5 | -     | +1.5  | LSB |

| DNL               | Differential non-linearity | -1.5 | -     | +1.5  | LSB |

#### HWEN, A0, A1

| V <sub>IH</sub> | Positive Going Input High Voltage<br>Threshold | 1.1 | -   | -   | V  |

|-----------------|------------------------------------------------|-----|-----|-----|----|

| V <sub>IL</sub> | Negative Going Input Low Voltage<br>Threshold  | -   | _   | 0.4 | V  |

| I <sub>PD</sub> | Pull–Down (input bias current)                 | _   | 0.1 | 1.0 | μΑ |

#### GPIO1, GPIO2

| V <sub>IH</sub> Positive Going Input High Voltage<br>Threshold | 1 | 1.1 | - | - | V |

|----------------------------------------------------------------|---|-----|---|---|---|

|----------------------------------------------------------------|---|-----|---|---|---|

9. Devices that use non-standard supply voltages which do not conform to the intent  $I^2C$  bus system levels must relate their input levels to the V<sub>DD</sub> voltage to which the pull-up resistors R<sub>P</sub> are connected.

Refer to the Application Information section of this data sheet for more details.

Guaranteed by design and characterized.

**Table 4. ELECTRICAL CHARACTERISTICS** Min & Max Limits apply for  $T_A = -40^{\circ}$ C to +85°C unless otherwise specified. AV<sub>IN</sub> = PV<sub>IN1</sub> = PV<sub>IN2</sub> = V<sub>IN1</sub> = V<sub>IN2</sub> = V<sub>IN3</sub> = V<sub>IN3</sub> = V<sub>IN5</sub> = 3.6 V (Unless otherwise noted). DCDC1 = 1.05 V, DCDC2 = 1.2 V, LDO1&2&3 = 2.85 V, LDO4&5 = 1.8 V. Typical values are referenced to  $T_A = +25^{\circ}$ C and default configuration (Note 10)

| Symbol              | Parameter                                     | Conditions               | Min                        | Тур | Max  | Unit |

|---------------------|-----------------------------------------------|--------------------------|----------------------------|-----|------|------|

| GPIO1, GPI          | 02                                            |                          | -                          | -   |      |      |

| $V_{IL}$            | Negative Going Input Low Voltage<br>Threshold |                          | -                          | -   | 0.4  | V    |

| V <sub>OH</sub>     | High Level Output Voltage                     | $I_{OH} = -1 \text{ mA}$ | AV <sub>IN</sub> –<br>0.45 | -   | -    | V    |

| V <sub>OL</sub>     | Low Level Output Voltage                      | I <sub>OH</sub> = 1 mA   | -                          | -   | 0.45 | V    |

| <sup>2</sup> C      |                                               |                          | -                          | •   | -    |      |

| V <sub>I2CINT</sub> | High level at SCL/SDA line                    | (Note 11)                | -                          | -   | 5.0  | V    |

| 17                  | CCL_CDA low input voltage                     | CCL CDA nin (Note 11)    |                            |     | 0.5  | 17   |

|   | 1201111            | -                                |                                    |                              |   |     |     |

|---|--------------------|----------------------------------|------------------------------------|------------------------------|---|-----|-----|

|   | V <sub>I2CIL</sub> | SCL, SDA low input voltage       | SCL, SDA pin (Note 11)             | -                            | _ | 0.5 | V   |

|   | V <sub>I2CIH</sub> | SCL, SDA high input voltage      | SCL, SDA pin (Note 11)             | 0.8 x<br>V <sub>I2CINT</sub> | _ | _   | V   |

|   | V <sub>I2COL</sub> | SCL, SDA low output voltage      | I <sub>SINK</sub> = 3 mA (Note 11) | -                            | _ | 0.4 | V   |

| ſ | F <sub>SCL</sub>   | I <sup>2</sup> C clock frequency | (Note 11)                          | -                            | - | 3.4 | MHz |

TOTAL DEVICE

| V <sub>UVLO</sub>    | Under Voltage Lockout            | V <sub>IN</sub> falling | -  | -   | 2.3 | V  |

|----------------------|----------------------------------|-------------------------|----|-----|-----|----|

| V <sub>UVLOH</sub>   | Under Voltage Lockout Hysteresis | V <sub>IN</sub> rising  | 60 | 130 | 200 | mV |

| T <sub>dlysys</sub>  | Initialization time at power on  |                         | _  | 2   | -   | ms |

| T <sub>SD</sub>      | Thermal Shut Down Protection     | (Note 11)               | -  | 150 | -   | °C |

| T <sub>WARNING</sub> | Warning Rising Edge              | (Note 11)               | _  | 135 | -   | °C |

| T <sub>SDHYS</sub>   | Thermal Shut Down Hysteresis     | (Note 11)               | _  | 35  | -   | °C |

9. Devices that use non-standard supply voltages which do not conform to the intent  $I^2C$  bus system levels must relate their input levels to the V<sub>DD</sub> voltage to which the pull-up resistors R<sub>P</sub> are connected.

10. Refer to the Application Information section of this data sheet for more details.

11. Guaranteed by design and characterized.

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

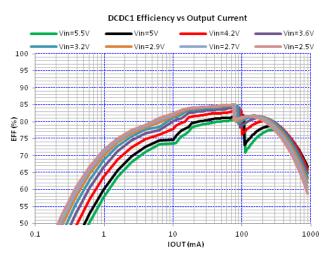

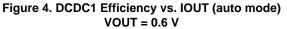

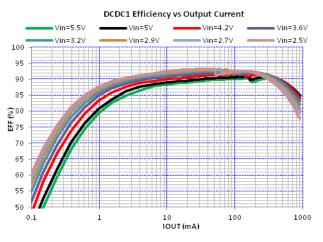

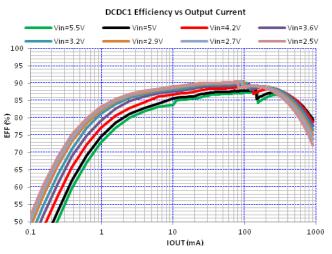

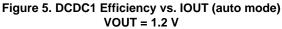

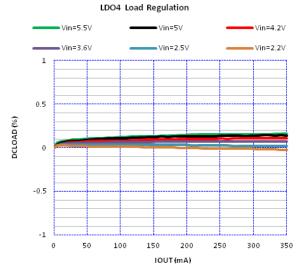

# **TYPICAL OPERATING CHARACTERISTICS**

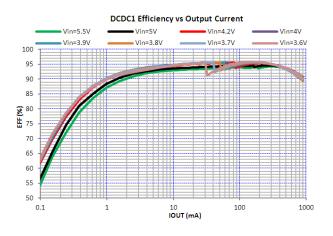

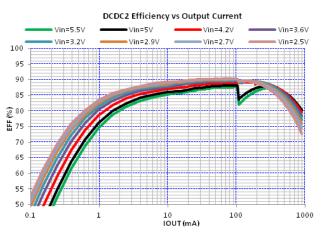

$\begin{array}{l} {\sf AV}_{{\sf IN}} = {\sf PV}_{{\sf IN1}} = {\sf PV}_{{\sf IN2}} = {\sf V}_{{\sf INLDOx}} = 3.6 \; {\sf V} \; ({\sf Unless \; otherwise \; noted}). \; {\sf T}_{\sf J} = +25^{\circ}{\sf C}, \; {\sf DCDC1} = 1.25 \; {\sf V}, \; {\sf DCDC2} = 1.85 \; {\sf V}, \; {\sf LDO1\&3} = 2.80 \; {\sf V}, \\ {\sf LDO3\&4} = 1.80 \; {\sf V}, \; {\sf C}_{{\sf LDO}} = 2.2 \; {\sf \mu}{\sf F} \; 0603, \; {\sf L}_{{\sf DCDC}} = 2.2 \; {\sf \mu}{\sf H} \; ({\sf DFE201612R-H-2R2N}) - {\sf C}_{{\sf DCDC}} = 10 \; {\sf \mu}{\sf F} \; 0603. \end{array}$

Figure 6. DCDC1 Efficiency vs. IOUT (auto mode) VOUT = 1.8 V

Figure 7. DCDC1 Efficiency vs. IOUT (auto mode) VOUT = 3.3 V

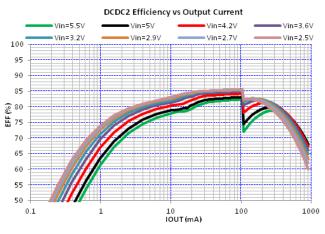

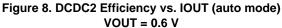

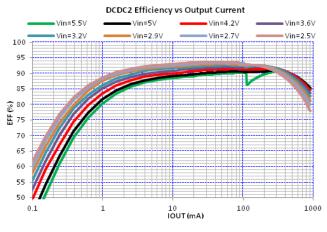

# **TYPICAL OPERATING CHARACTERISTICS**

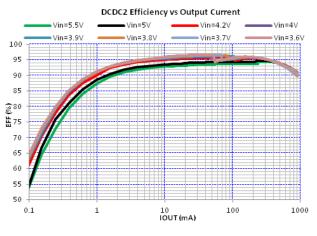

$\begin{array}{l} {\sf AV}_{{\sf IN}} = {\sf PV}_{{\sf IN1}} = {\sf PV}_{{\sf IN2}} = {\sf V}_{{\sf INLDOX}} = 3.6 \; {\sf V} \; ({\sf Unless \; otherwise \; noted}). \; {\sf T}_{\sf J} = +25^{\circ}{\sf C}, \; {\sf DCDC1} = 1.25 \; {\sf V}, \; {\sf DCDC2} = 1.85 \; {\sf V}, \; {\sf LDO1\&3} = 2.80 \; {\sf V}, \\ {\sf LDO3\&4} = 1.80 \; {\sf V}, \; {\sf C}_{{\sf LDO}} = 2.2 \; {\sf \mu}{\sf F} \; 0603, \; {\sf L}_{{\sf DCDC}} = 2.2 \; {\sf \mu}{\sf H} \; ({\sf DFE201612R-H-2R2N}) - {\sf C}_{{\sf DCDC}} = 10 \; {\sf \mu}{\sf F} \; 0603. \end{array}$

Figure 10. DCDC2 Efficiency vs. IOUT (auto mode) VOUT = 1.8 V

Figure 9. DCDC2 Efficiency vs. IOUT (auto mode) VOUT = 1.2 V

Figure 11. DCDC2 Efficiency vs. IOUT (auto mode) VOUT = 3.3 V

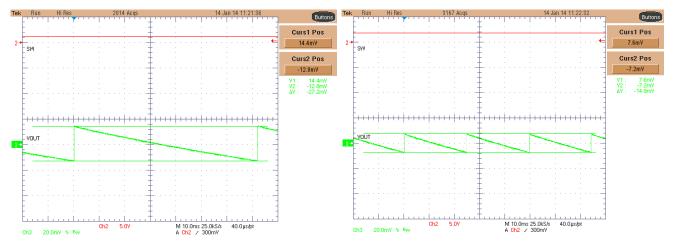

# **TYPICAL OPERATING CHARACTERISTICS**

$AV_{IN} = PV_{IN1} = PV_{IN2} = V_{INLDOx} = 3.6 \text{ V} \text{ (Unless otherwise noted)}. T_{J} = +25^{\circ}\text{C}, \text{ DCDC1} = 1.25 \text{ V}, \text{ DCDC2} = 1.85 \text{ V}, \text{ LDO1&3} = 2.80 \text{ V}, \text{ LDO3&4} = 1.80 \text{ V}, \text{ C}_{\text{LDO}} = 2.2 \text{ } \mu\text{F} \text{ 0603}, \text{ L}_{\text{DCDC}} = 2.2 \text{ } \mu\text{H} \text{ (DFE201612R} - \text{H} - 2\text{R2N}) - \text{C}_{\text{DCDC}} = 10 \text{ } \mu\text{F} \text{ 0603}.$

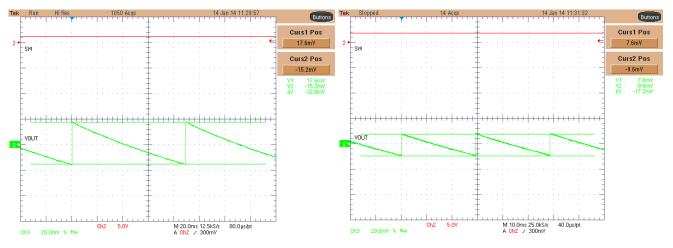

Figure 12. DCDC1 Ripple Voltage in PFM Mode  $(V_{IN} = 3.6V - V_{OUT} = 1.2 V - No load)$

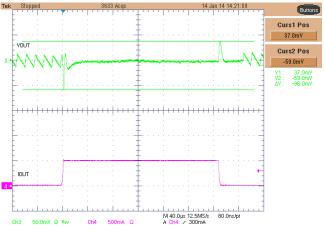

Figure 15. DCDC2 Ripple Voltage in PFM Mode ( $V_{IN}$  = 3.6 V -  $V_{OUT}$  = 1.8 V - No load)

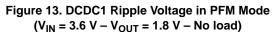

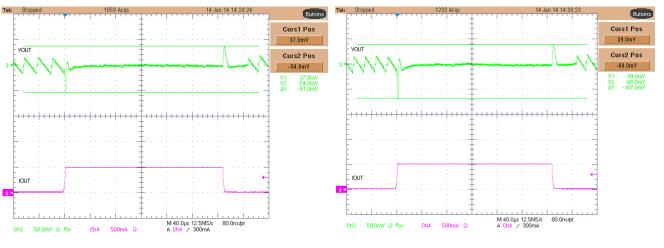

# **TYPICAL OPERATING CHARACTERISTICS**

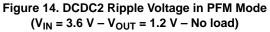

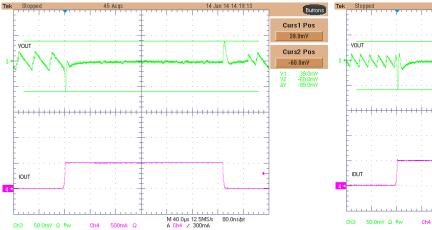

$AV_{IN} = PV_{IN1} = PV_{IN2} = V_{INLDOX} = 3.6 \text{ V} \text{ (Unless otherwise noted)}. T_{J} = +25^{\circ}\text{C}, \text{ DCDC1} = 1.25 \text{ V}, \text{ DCDC2} = 1.85 \text{ V}, \text{ LDO1&3} = 2.80 \text{ V}, \text{ LDO3&4} = 1.80 \text{ V}, \text{ C}_{\text{LDO}} = 2.2 \text{ } \mu\text{F} \text{ } 0603, \text{ } \text{L}_{\text{DCDC}} = 2.2 \text{ } \mu\text{H} \text{ } (\text{DFE201612R} - \text{H} - 2\text{R2N}) - \text{C}_{\text{DCDC}} = 10 \text{ } \mu\text{F} \text{ } 0603.$

Figure 16. DCDC1 Load Transient Response (PWM Mode,  $V_{IN} = 3.6 V - V_{OUT} = 1.2 V$ )

Figure 17. DCDC1 Load Transient Response (PWM Mode,  $V_{IN}$  = 3.6 V –  $V_{OUT}$  = 1.8 V)

Figure 18. DCDC2 Load Transient Response (PWM Mode,  $V_{IN}$  = 3.6 V –  $V_{OUT}$  = 1.2 V)

Figure 19. DCDC2 Load Transient Response (PWM Mode,  $V_{IN} = 3.6 V - V_{OUT} = 1.8 V$ )

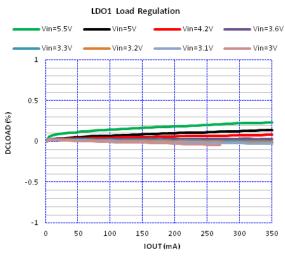

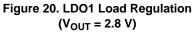

# **TYPICAL OPERATING CHARACTERISTICS**

$AV_{IN} = PV_{IN1} = PV_{IN2} = V_{INLDOx} = 3.6 \text{ V} \text{ (Unless otherwise noted)}. T_{J} = +25^{\circ}\text{C}, \text{ DCDC1} = 1.25 \text{ V}, \text{ DCDC2} = 1.85 \text{ V}, \text{ LDO1&3} = 2.80 \text{ V}, \text{ LDO3&4} = 1.80 \text{ V}, \text{ C}_{\text{LDO}} = 2.2 \text{ } \mu\text{F} \text{ } 0603, \text{ } L_{\text{DCDC}} = 2.2 \text{ } \mu\text{H} \text{ } (\text{DFE201612R} - \text{H} - 2\text{R2N}) - \text{C}_{\text{DCDC}} = 10 \text{ } \mu\text{F} \text{ } 0603.$

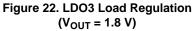

Figure 21. LDO2 Load Regulation (V<sub>OUT</sub> = 2.8 V)

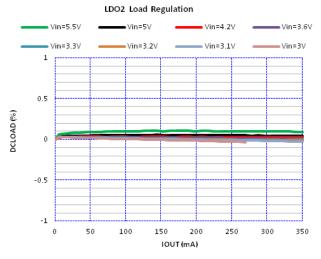

Figure 23. LDO4 Load Regulation  $(V_{OUT} = 1.8 \text{ V})$

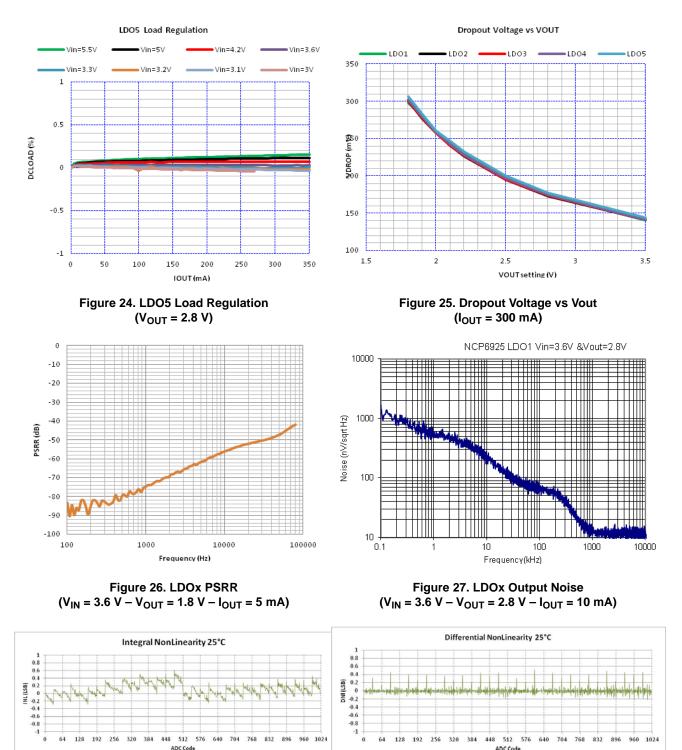

# **TYPICAL OPERATING CHARACTERISTICS**

$\begin{array}{l} {\sf AV}_{{\sf IN}} = {\sf PV}_{{\sf IN1}} = {\sf PV}_{{\sf IN2}} = {\sf V}_{{\sf INLDOx}} = 3.6 \; {\sf V} \; ({\sf Unless \; otherwise \; noted}). \; {\sf T}_{\sf J} = +25^{\circ}{\sf C}, \; {\sf DCDC1} = 1.25 \; {\sf V}, \; {\sf DCDC2} = 1.85 \; {\sf V}, \; {\sf LDO1\&3} = 2.80 \; {\sf V}, \\ {\sf LDO3\&4} = 1.80 \; {\sf V}, \; {\sf C}_{{\sf LDO}} = 2.2 \; {\sf \mu}{\sf F} \; 0603, \; {\sf L}_{{\sf DCDC}} = 2.2 \; {\sf \mu}{\sf H} \; ({\sf DFE201612R-H-2R2N}) - {\sf C}_{{\sf DCDC}} = 10 \; {\sf \mu}{\sf F} \; 0603. \end{array}$

Figure 28. ADC INL

Figure 29. ADC DNL

#### DETAILED OPERATING DESCRIPTION

#### **General Description**

The NCP6925 mini power management integrated circuit is optimized to supply different sub systems of battery powered portable applications. The IC can be supplied directly from the latest technology single cell batteries such as Lithium–Polymer as well as from triple alkaline cells. Alternatively, the IC can be supplied from a pre–regulated supply rail in case of multi–cell or main powered applications.

It integrates two switched mode DCDC converters and five low dropout linear regulators. The IC is widely programmable through an I<sup>2</sup>C interface and includes low level IO signaling. An analog core provides the necessary references for the IC while a digital core ensures proper control.

The output voltage range, current capabilities and performance of the switched mode DCDC converters are well suited to supply the different peripherals in the system as well as to supply processor cores. For PWM operation, the converters run on a local 3 MHz clock. A low power PFM mode is provided that ensures that even at low loads high efficiency can be obtained. All the switching components are integrated including the compensation networks and synchronous rectifier. Only a small sized  $1-2.2 \,\mu$ H inductor and 10  $\mu$ F bypass capacitor are required for typical applications.

The general purpose low dropout regulators can be used to supply the lower power rails in the application. To improve the overall application standby current, the bias current of these regulators are made very low. The regulators have their own input supply pin to be able to connect them independently to either the system supply voltage or to the output of the DCDC converter in the application. The regulators are bypassed with a small size  $1 - 2.2 \,\mu\text{F}$  capacitor.

The feature can be controlled through the I<sup>2</sup>C interface. In addition to this bus, digital control pins including hardware enable (HWEN), two general purpose inputs / outputs (GPIOx) and interrupt (INTB) are provided.

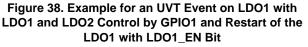

The 10 bits triple input analog to digital converter checks and store the resistor value placed on ADCIN1 and ADCIN2. It is used to store the ID of the external module which help to have the right configuration for each converter.

#### **Under Voltage Lockout**

The core does not operate for voltages below the Under Voltage Lock Out (UVLO) level. Below the UVLO threshold, all internal circuitry (both analog and digital) is held in reset.

NCP6925 operation is guaranteed down to UVLO when battery voltage is dropping off. To avoid erratic on / off behaviour, a typical 130 mV hysteresis is implemented. When an UVLO event occurs and the AV<sub>IN</sub> voltage recovers, NCP6925 is initialized in its default state.

#### **Thermal Shutdown**

The thermal capabilities of the device can be exceeded due to the output power capabilities of the on chip step down converters and low drop out regulators. A thermal protection circuit is therefore implemented to prevent the part from being damaged. This protection circuit is only activated when the core is in active mode (at least one output channel is enabled). During thermal shutdown, all outputs of the NCP6925 are off.

When the NCP6925 returns from thermal shutdown mode, it can re-start in three different configurations depending on REARM[1:0] bits:

- If REARM[1:0] = 00, NCP6925 re-starts with default register values,

- If REARM[1:0] = 01 NCP6925 re-starts with register values set prior to thermal shutdown,

- Finally if REARM[1:0] = 10, NCP6925 does not re-start automatically, a toggle of HWEN or CHx\_EN[] or SEQx\_CTRL[] is needed.

In addition, a thermal warning is implemented which can inform the processor through an interrupt (if not masked) that NCP6925 is close to its thermal shutdown so that preventive measurement can be taken by software.

#### **Active Output Discharge**

To prevent any disturbances on the power–up sequence, a quick active output discharge is done during the start–up sequence for all output channels.

When the IC is turned off through HWEN pin (or ENx bits) or AVIN drops down below UVLO threshold, no shut down sequence is expected, all supplies are disabled and outputs discharged simultaneously.

# Enabling / Disabling

The HWEN pin controls the device start up without enabling the output of the converters. If HWEN is raised, this starts the internal circuitry. By default all the converters are off. If HWEN is made low, device enters in shutdown mode and all regulators are turned off. Regulators can also be turned off with the dedicated register. A built–in pull–down resistor disables the device if this pin is left unconnected.

When HWEN is high, the different power rails can be independently enabled / disabled by writing the appropriate bit in the ENABLE register.

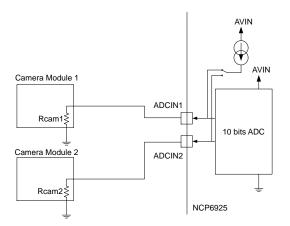

When HWEN is low, NCP6925 is in power down mode and I<sup>2</sup>C will return NACK to any request. After HWEN transition from low to high, initialization sequence and ADC 1&2 read will be performed. During this sequence is performed, I<sup>2</sup>C will NACK any request too. I<sup>2</sup>C will be accessible after sequence and ADC completion are completed.

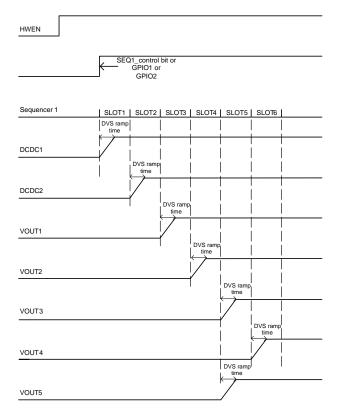

# Power Up / Down Sequence and HWEN

Power up and power down sequence can be program and controlled with the dedicated register (BUCKx\_SEQ[7:0], LD012\_SEQ[7:0], LD034\_SEQ[7:0], LD05\_SEQ[3:0], CHx\_SEQ[7:0], SEQ1\_PROG[7:0], SEQ2\_PROG[7:0]). SEQx\_CTRL[1:0] set the power-up or shut down. Converters can also be turned on and off independently with the CHx\_EN[6:0] register.

When a shutdown is required during a power–up, it will be valid and start when the power–up is finished.

Any changes in BUCKx\_SEQ[7:0], LDO12\_SEQ[7:0], LDO34\_SEQ[7:0], LDO5\_SEQ[3:0] during a power–up or shutdown is not valid and will not modify the NCP6925 setting.

# Figure 30.

Example for Sequencer 1 with DCDC1 assign to SLOT1, DCDC2 assign to SLOT2, VOUT1 assign to SLOT3, VOUT2 assign to SLOT4, VOUT3 assign to SLOT5, VOUT4 assign to SLOT6, VOUT5 assign to SLOT5

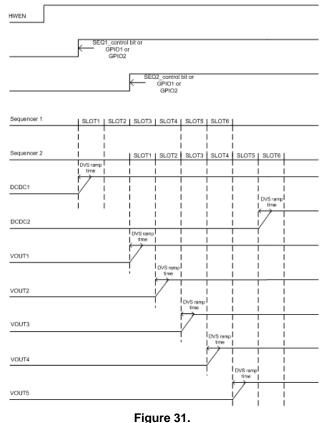

# Slot Period and DCDC Soft Start Time Setting

(details Table 35)

SEQ\_SPEED[1:0] defines the slot period of the 2 sequences. The DCDC soft start time selection is linked to the slot period as the setting is also done with SEQ\_SPEED[1:0].

Any changes in SEQ\_SPEED[1:0] during a power-up or shut down sequence is valid only when the sequence is finished.

Example for Sequencer 1 and Sequencer 2 with DCDC1 assign to SLOT1 SEQ1, DCDC2 assign to SLOT6 SEQ2, VOUT1 assign to SLOT1 SEQ2, VOUT2 assign to SLOT2 SEQ2, VOUT3 assign to SLOT5 SEQ1, VOUT4 assign to SLOT6 SEQ1, VOUT5 assign to SLOT5 SEQ2

CHx\_SEQ = 0000

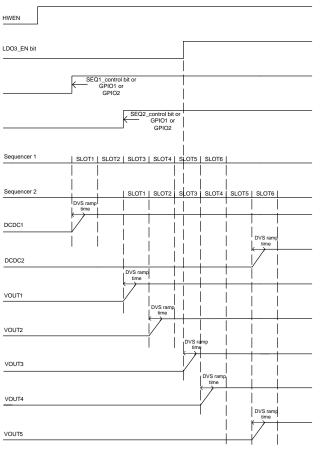

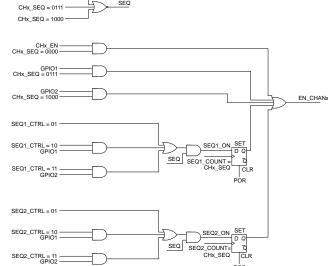

Figure 33. Logic Diagram of Power Up / Power Down

Figure 32.

Example of turn on sequence with DCDC1 assign to SLOT1 SEQ1, DCDC2 assign to SLOT6 SEQ2, VOUT1 assign to SLOT1 SEQ2, VOUT2 assign to SLOT2 SEQ2, VOUT3 control with LDO3\_EN bit, VOUT4 assign to SLOT6 SEQ1, VOUT5 assign to SLOT6 SEQ2

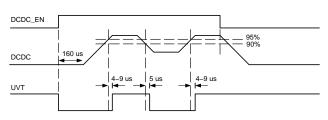

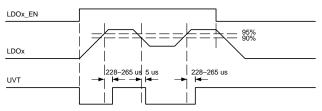

# DCDC Step Down Converter and LDO's Under Voltage Threshold

To indicate that the output of an output channel is established and that the level does not go below 0.875 x Vout\_set, a UVT bit is available for each output channel.

The UVT bit is high when the channel is off and goes low when enabling the channel. Once the output voltage reaches the expected output level, the UVT bit becomes high again.

When during operation the output gets below the expected level (87.5% for the LDOs or 90% for the DCDCs) the UVT bit goes low which indicates a power failure. When the voltage rises again above 87.5% for the LDOs or 90% for the DCDCs the UVT bit goes high again.

Figure 34. DCDCx Channel Internal UVT Bit

Figure 35. LDOx Channel Internal UVT Bit

#### Interrupt

The interrupt controller continuously monitors internal interrupt sources, generating an interrupt signal when a system status change is detected (dual edge monitoring). The interrupt sources include:

| Interrupt<br>Sources | Description                         |  |

|----------------------|-------------------------------------|--|

| UVT_DCDC1            | DCDC1 Under Voltage Threshold       |  |

| UVT_DCDC2            | DCDC2 Under Voltage Threshold       |  |

| UVT_LDO1             | LDO1 Under Voltage Threshold        |  |

| UVT_LDO2             | LDO2 Under Voltage Threshold        |  |

| UVT_LDO3             | LDO3 Under Voltage Threshold        |  |

| UVT_LDO4             | LDO4 Under Voltage Threshold        |  |

| UVT_LDO5             | LDO5 Under Voltage Threshold        |  |

| UVLO                 | UVLO state                          |  |

| IDCDC1               | DCDC1 Converter Output Over Current |  |

| IDCDC2               | DCDC2 Converter Output Over Current |  |

| ILDO1                | LDO1 Output Over Current            |  |

| ILDO2                | LDO2 Output Over Current            |  |

| ILDO3                | LDO3 Output Over Current            |  |

| ILDO4                | LDO4 Output Over Current            |  |

| ILDO5                | LDO5 Output Over Current            |  |

| ADC_EOC              | ADC End Of Conversion               |  |

| WNRG                 | Thermal Warning                     |  |

| TSD                  | Thermal Shutdown                    |  |

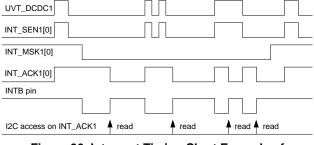

Individual bits generating interrupts will be set to 1 in the INT ACK1/INT ACK2/INT ACK3 registers (I<sup>2</sup>C read only registers), indicating the interrupt source. INT\_ACK1/INT\_ACK2/INT\_ACK3 registers are automatically I<sup>2</sup>C reset by read. an INT\_SEN1/INT\_SEN2/INT\_SEN3 registers (read only registers) contain real time indicators of interrupt sources.

All interrupt sources can be masked by writing registers INT\_MSK1/INT\_MSK2/INT\_MSK3. Masked sources will never generate an interrupt request on INTB pin.

The INTB pin is an open drain output. A non masked interrupt request will result in the INTB pin being driven low.

When the host reads the

INT\_ACK1/INT\_ACK2/INT\_ACK3 registers the INTB pin is released to high impedance and the interrupt registers INT\_ACK1/INT\_ACK2/INT\_ACK3 are cleared.

Below figure shows how DCDC1 converter power good produces interrupt on INTB pin with INT\_SEN1/INT\_MSK1/INT\_ACK1 and an I<sup>2</sup>C read access (assuming no other interrupt happens during this read period).

Figure 36. Interrupt Timing Chart Example of PG\_DCDC1

INT\_MSK1, INT\_MSK2 and INT\_MSK3 registers are set to disable INTB feature by default during power-up.

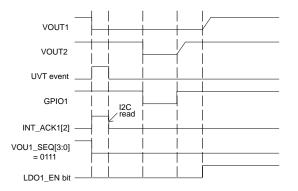

In case the interruption is flagged due to an under voltage threshold detection or an output over current detection, the regulator which failed will be turned off.

The regulator can be turn on again only after the INT\_ACK1/INT\_ACK2/INT\_ACK3 registers are cleared by reading these registers.

# Errors

The events which are considered as an error and flag the interrupt pin are:

- Under Voltage Threshold of DCDC1

- Under Voltage Threshold of DCDC2

- Under Voltage Threshold of LDO1

- Under Voltage Threshold of LDO2

- Under Voltage Threshold of LDO3

- Under Voltage Threshold of LDO4

- Under Voltage Threshold of LDO5

- Over Current Protection for DCDC1

- Over Current Protection for DCDC2

- Over Current Protection for LDO1

- Over Current Protection for LDO2

- Over Current Protection for LDO3

- Over Current Protection for LDO4

- Over Current Protection for LDO5

- Under Voltage Lock Out

- Thermal Shutdown

- Thermal Shutdown Warning

The errors need to be activated with the registers INT\_MASK1/INTMASK2/INT\_MASK3.

To recover from the error mode and release the part, the registers INT\_ACK1/INT\_ACK2/INT\_ACK3 has to be read.

• Thermal Shutdown error : When a thermal shutdown event occurs, the part goes in shutdown mode. It recovers in the mode define with the 2 bits REARM[1:0]. By default NCP6925 recovers with a new power up sequence with no reset of the I<sup>2</sup>C registers. This error is master and independent of the functionality of the interruption register. The user can choose the flag the INT pin and INT\_ACK3 register with the register INT\_MSK3.

- Thermal shutdown warning : When a TSD warning event occurs, the INT pin and the INT\_ACK3 register are flagged. The user has to read the register INT\_ACK3 to recover. This error need to be activated with the registers INT\_MASK3. By default this error is masked.

- Under Voltage Lockout : When an under voltage lock out event occurs, the part goes in shutdown mode. It recovers in its default state. This error is master and independent of the functionality of the interruption register. The user can choose to flag the INT pin and INT\_ACK1 register with the register INT\_MSK1.

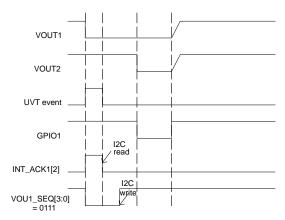

- Under Voltage Threshold on CHx: when this event occurs, the corresponding regulator is turned off. The values of CHx\_SEQ[3:0] is reset to 0000 and CHx\_EN is reset to 0 and the INTB pin is pulled high. This error is linked to the interruption register. By default this error is activated.

- Over Current Protection on CHx: when this event occurs, the corresponding regulator is turned off. The values of CHx\_SEQ[3:0] is reset to 0000 and CHx\_EN is reset to 0 and the INTB pin is pulled high. This error is linked to the interruption register. By default this error is activated.

#### Figure 37. Example for an UVT Event on LDO1 with LDO1 and LDO2 Control by GPIO1

# GPIOs

2 GPIOs are available and can be configured with GPIO\_CONTROL1[] and GPIO\_CONTROL2[] register.

GPIO\_READ[1:0] bits store the logic level when the pins are set as input.

GPIOx\_EN\_RD bit set the pin as an input (1) or output (0).

GPIOx[1:0] bits set the logic level (HiZ, low, high) when the pins are set as output.

The GPIOs can also enable or disable one or multiple regulators when it is set as an input and configured in the CHx\_SEQ register.

The turn-on or shut down sequence can also be started by a GPIO when it is set as an input and configured in the SEQx\_CTRL[1:0] bits.

#### **DCDC Step Down Converters**

The DCDC converters are synchronous rectifier type with both high side and low side integrated switches. Neither external transistor nor diodes are required for proper operation. Feedback and compensation network are also fully integrated.

The DCDC converters can operate in two different modes: PWM and PFM. The transition between PWM/PFM modes can occur automatically or the switcher can be placed in forced PWM mode by I<sup>2</sup>C programming.

# PWM (Pulse Width Modulation) Operating Mode

In medium and high load conditions, DCDC converters operates in PWM mode from a fixed 3MHz clock and adapts its duty cycle to regulate the desired output voltage. In this mode, the inductor current is in CCM (Continuous Current Mode) and the voltage is regulated by PWM. The internal N–MOS switch operates as synchronous rectifier and is driven complementary to the P–MOS switch. In CCM the lower (N–MOS switch) in a synchronous converter provides a lower voltage drop than the diode in an asynchronous converter, which provides less loss and higher efficiency.

#### PFM (Pulse Frequency Modulation) Operating Mode

In order to save power and improve efficiency at low loads the DCDC converters operate in PFM mode as the inductor drops into DCM (Discontinuous Current Mode). The upper FET on time is kept constant and the switching frequency is variable. Output voltage is regulated by varying the switching frequency which becomes proportional to loading current. As it does in PWM mode, the internal N–MOSFET operates as synchronous rectifier after each P–MOSFET on–pulse with very small negative current limit. When load increases and current in inductor becomes continuous again, the controller automatically turns back to PWM fixed frequency mode.

#### Forced PWM

The DCDC converters can be programmed to only use PWM and disable the transition to PFM if so desired.

### Inductor Peak Current Limitation

During normal operation, peak current limitation will monitor and limit the current through the inductor. This current limitation is particularly useful when size and/or height constrains inductor power

#### Soft Start

A soft start is provided to limit inrush currents when enabling the converter. After enabling and internal delays elapsed, the DC to DC converter output will gradually ramp up to the programmed voltage.

#### **Triple Input 10 Bits ADC**

The triple input 10 bits has 2 different mode:

During power–up, ADC converts the ADCIN1 and ADCIN2 in the EXTID register.

When HWEN is set, the ADC automatically converts the 2 inputs and then it is turned off. It could be used for applications which need to detect and store in a register the external accessory id when the battery is plugged.

Figure 39. Example for the Detection of 2 External Camera Modules

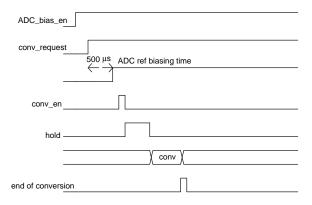

#### Figure 40. Timing of the 2 Conversion when AVIN is Plugged

When the part is turn on, the 3 inputs of the ADC can be used as a general purpose ADC by setting the ADC\_CONF register. Result can be read in the ADC\_READ\_INPUT register.

#### Figure 41. Timing of a Conversion in the General Purpose Mode

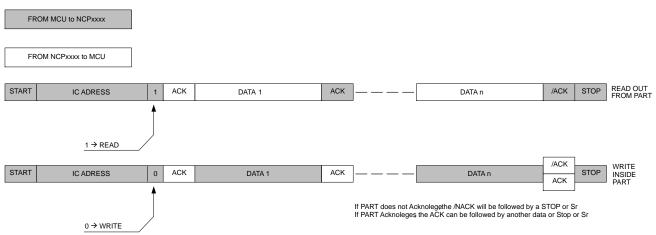

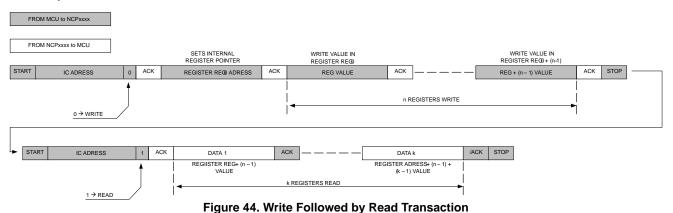

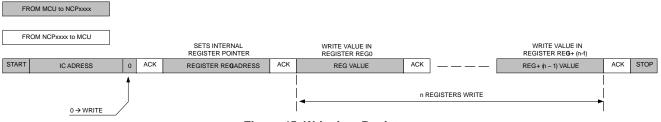

# I<sup>2</sup>C COMPATIBLE INTERFACE

NCP6925 can support a subset of I<sup>2</sup>C protocol, below are detailed introduction for I<sup>2</sup>C programming.

# I<sup>2</sup>C Communication Description

ON Semiconductor communication protocol is a subset of I<sup>2</sup>C protocol.

The first byte transmitted is the Chip address (with LSB bit sets to 1 for a read operation, or sets to 0 for a Write operation). Then the following data will be:

- In case of a Write operation, the register address (@REG) we want to write in followed by the data we will write in the chip. The writing process is incremental. So the first data will be written in @REG, the second one in @REG + 1 .... The data are optional.

- In case of read operation, the NCP6925 will output the data out from the last register that has been accessed by the last write operation. Like writing process, reading process is an incremental process.

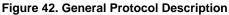

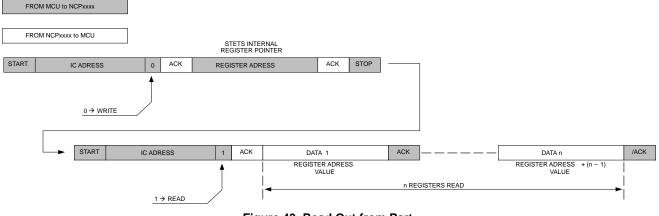

# **Read Out from Part**

The Master will first make a "Pseudo Write" transaction with no data to set the internal address register. Then, a stop then start or a Repeated Start will initiate the read transaction from the register address the initial write transaction has set:

# Figure 43. Read Out from Part

The first WRITE sequence will set the internal pointer on the register we want access to. Then the read transaction will start at the address the write transaction has initiated.

#### Transaction with Real Write then Read: With Stop Then Start

#### Write in Part

Write operation will be achieved by only one transaction. After chip address, the MCU first data will be the internal register we want access to, then following data will be the data we want to write in Reg, Reg + 1, Reg + 2, ..., Reg + n.

#### Write n Registers:

Figure 45. Write in n Registers

# I<sup>2</sup>C Address

NCP6925 has 4 selectable I<sup>2</sup>C address (see below table A7~A1), NCP6925 supports 7-bit address only.

0

|   | A1    |       |   | A0    |  | Hex   |   |

|---|-------|-------|---|-------|--|-------|---|

|   | 0     |       |   | 0     |  | \$50  |   |

|   | 0     |       |   | 1     |  |       |   |

|   | 1     |       | 0 |       |  | \$52  |   |

|   | 1     |       |   | 1     |  | \$53  |   |

| Т | Bit 4 | Bit 3 | 3 | Bit 2 |  | Bit 1 | Т |

0

A1

Bit 0

A0

R/W

\_

# Table 6. NCP6925 I<sup>2</sup>C Address

NOTE: Other addresses are available upon request.

Bit 5

0

#### **Register Map**

Bit 6

1

Following register map describes I²C registers.Registers can be:Read only registerRRead only registerRCRead then ClearRWRead and Write registerRWMRead, Write and can be modified by the ICReservedAddress is reserved and register is not physically designedSpareAddress is reserved and register is physically designed

1

| Address      | Register Name   | Туре | Default | Function                                               |

|--------------|-----------------|------|---------|--------------------------------------------------------|

| \$00         | CHIP_REV        | R    | \$00    | Chip revision                                          |

| \$01         | EXT_ID          | R    | \$00    | External ID resistor identification                    |

| \$02         | BUCK1_PROG      | RW   | \$00    | DCDC1 setting                                          |

| \$03         | BUCK2_PROG      | RW   | \$00    | DCDC2 setting                                          |

| \$04         | BUCKx_PROG      | RW   | \$00    | DCDC 1 and 2 setting                                   |

| \$05         | LDO1_VOUT       | RW   | \$00    | LDO1 output voltage setting                            |

| \$06         | LDO2_VOUT       | RW   | \$00    | LDO2 output voltage setting                            |

| \$07         | LDO3_VOUT       | RW   | \$00    | LDO3 output voltage setting                            |

| \$08         | LDO4_VOUT       | RW   | \$00    | LDO4 output voltage setting                            |

| \$09         | LDO5_VOUT       | RW   | \$00    | LDO5 output voltage setting                            |

| \$0A         | -               | -    | _       | -                                                      |

| \$0B         | CHx_EN          | RW   | \$00    | Channel enable register                                |

| \$0C         | BUCKx_SEQ       | RW   | \$00    | DCDC 1 and 2 sequencer assignment                      |

| \$0D         | LDO12_SEQ       | RW   | \$00    | LDO 1 and 2 sequencer assignment                       |

| \$0E         | LDO34_SEQ       | RW   | \$00    | LDO 3 and 4 sequencer assignment                       |

| \$0F         | LDO5_SEQ        | RW   | \$00    | LDO 5 sequencer assignment                             |

| \$10         | SEQ1_PROG       | RW   | \$00    | Sequencer 1 setting                                    |

| \$11         | SEQ2_PROG       | RW   | \$00    | Sequencer 2 setting                                    |

| \$12         | GPIO_CONTROL1   | RW   | \$00    | GPIO 1 and 2 read register                             |

| \$13         | GPIO_CONTROL2   | RW   | \$00    | GPIO1 and 2 setting register                           |

| \$14 to \$1F | -               | -    | _       | Reserved for future use                                |

| \$20         | ADC_CONF        | RW   | \$00    | ADC configuration register                             |

| \$21         | ADC_READ_INPUT  | RW   | \$00    | ADC read input register (bits 2 to 9)                  |

| \$22         | ADC_READ_INPUT2 | RW   | \$00    | ADC read input register 2 (bits 0 to 1)                |

| \$23         | INT_ACK1        | RC   | \$00    | Interrupt 1 register (dual edge)                       |

| \$24         | INT_ACK2        | RC   | \$00    | Interrupt 2 register (rising edge and dual edge)       |

| \$25         | INT_ACK3        | RC   | \$00    | Interrupt 3 register (rising edge and dual edge)       |

| \$26         | INT_SEN1        | R    | \$00    | Sense 1 register (real time status)                    |

| \$27         | INT_SEN2        | R    | \$00    | Sense 2 register (real time status)                    |

| \$28         | INT_SEN3        | R    | \$00    | Sense 3 register (real time status)                    |

| \$29         | INT_MASK1       | RW   | \$FF    | Mask 1 register to enable or disable interrupt sources |

| \$2A         | INT_MASK2       | RW   | \$7F    | Mask 2 register to enable or disable interrupt sources |

| \$2B         | INT_MASK3       | RW   | \$06    | Mask 3 register to enable or disable interrupt sources |

| \$2C         | REARM           | RW   | \$01    | TSD rearm register setting                             |

| \$2D         | DIS             | RW   | \$7F    | Active output discharge register                       |

| \$2E to \$3F | -               | -    | _       | Reserved for future use                                |

| 0x00 | Bit 7                   | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |  |

|------|-------------------------|-------|-------|-------|-------|-------|-------|-------|--|--|--|

| Name | CHIP_REV[7:0]           |       |       |       |       |       |       |       |  |  |  |

| Mode | R                       |       |       |       |       |       |       |       |  |  |  |

| Init | 0                       | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |  |

| 0x01 | Bit 7                   | Bit 6 | Bit 2 | Bit 1 | Bit 0 |       |       |       |  |  |  |

| Name | EXTID2[4:0] EXTID1[4:0] |       |       |       |       |       |       |       |  |  |  |

| Mode |            |       | R         |       |              |        | R             |               |

|------|------------|-------|-----------|-------|--------------|--------|---------------|---------------|

| Init | 0          | 0     | 0         | 0     | 0            | 0      | 0             | 0             |

| 0x02 | Bit 7      | Bit 6 | Bit 5     | Bit 4 | Bit 3        | Bit 2  | Bit 1         | Bit 0         |

| Name | BUCK1_AUTO |       | I         | E     | BUCK1_VOUT[6 | :0]    |               |               |

| Mode | RW         |       |           |       | RW           |        |               |               |

| Init | 0          | 0     | 0         | 0     | 0            | 0      | 0             | 0             |

| 0x03 | Bit 7      | Bit 6 | Bit 5     | Bit 4 | Bit 3        | Bit 2  | Bit 1         | Bit 0         |

| Name | BUCK2_AUTO |       |           | E     | BUCK2_VOUT[6 | :0]    |               |               |

| Mode | RW         |       |           |       | RW           |        |               |               |

| Init | 0          | 0     | 0         | 0     | 0            | 0      | 0             | 0             |

| 0x04 | Bit 7      | Bit 6 | Bit 5     | Bit 4 | Bit 3        | Bit 2  | Bit 1         | Bit 0         |

| Name |            |       |           |       |              |        | BUCK2_VOUT[7] | BUCK1_VOUT[7] |

| Mode |            |       |           |       |              |        | RW            | RW            |

| Init |            |       |           |       |              |        | 0             | 0             |

| 0x05 | Bit 7      | Bit 6 | Bit 5     | Bit 4 | Bit 3        | Bit 2  | Bit 1         | Bit 0         |

| Name |            |       |           |       | LDO1_VOUT[6: | )]     |               |               |

| Mode |            |       |           |       | RW           |        |               |               |

| Init |            | 0     | 0         | 0     | 0            | 0      | 0             | 0             |

| 0x06 | Bit 7      | Bit 6 | Bit 5     | Bit 4 | Bit 3        | Bit 2  | Bit 1         | Bit 0         |

| Name |            |       |           |       | LDO2_VOUT[6: | )]     |               |               |

| Mode |            |       |           |       | RW           |        |               |               |

| Init |            | 0     | 0         | 0     | 0            | 0      | 0             | 0             |

| 0x07 | Bit 7      | Bit 6 | Bit 5     | Bit 4 | Bit 3        | Bit 2  | Bit 1         | Bit 0         |

| Name |            |       |           |       | LDO3_VOUT[6: | )]     |               |               |

| Mode |            |       |           |       | RW           |        |               |               |

| Init |            | 0     | 0         | 0     | 0            | 0      | 0             | 0             |

| 0x08 | Bit 7      | Bit 6 | Bit 5     | Bit 4 | Bit 3        | Bit 2  | Bit 1         | Bit 0         |

| Name |            |       |           |       | LDO4_VOUT[6: | <br>)] |               |               |

| Mode |            |       |           |       | RW           |        |               |               |

| Init |            | 0     | 0         | 0     | 0            | 0      | 0             | 0             |

| 0x09 | Bit 7      | Bit 6 | Bit 5     | Bit 4 | Bit 3        | Bit 2  | Bit 1         | Bit 0         |

| Name |            |       | •         | •     | LDO5_VOUT[6: | D]     | •             |               |

| Mode |            |       |           |       | RW           |        |               |               |

| Init |            | 0     | 0         | 0     | 0            | 0      | 0             | 0             |

| 0x0A | Bit 7      | Bit 6 | Bit 5     | Bit 4 | Bit 3        | Bit 2  | Bit 1         | Bit 0         |

| Name |            |       |           |       |              |        |               |               |

| Mode |            |       |           | 1     |              |        |               |               |

| Init |            |       |           |       |              |        |               |               |

| 0x0B | Bit 7      | Bit 6 | Bit 5     | Bit 4 | Bit 3        | Bit 2  | Bit 1         | Bit 0         |

| Name |            |       |           |       | CHx_EN[6:0]  |        |               |               |

| Mode |            |       |           |       | RW           |        |               |               |

| Init |            | 0     | 0         | 0     | 0            | 0      | 0             | 0             |

| 0x0C | Bit 7      | Bit 6 | Bit 5     | Bit 4 | Bit 3        | Bit 2  | Bit 1         | Bit 0         |

| Name | 1          | BUCK2 | _SEQ[3:0] | 1     | 1            | BUCK1  | _SEQ[3:0]     |               |

| Mode |          | R            | W            |              |              | R            | W             |               |  |

|------|----------|--------------|--------------|--------------|--------------|--------------|---------------|---------------|--|

| Init | 0        | 0            | 0            | 0            | 0            | 0            | 0             | 0             |  |

| 0x0D | Bit 7    | Bit 6        | Bit 5        | Bit 4        | Bit 3        | Bit 2        | Bit 1         | Bit 0         |  |

| Name |          | LDO2_S       | SEQ[3:0]     |              |              | LDO1_S       | SEQ[3:0]      | 1             |  |

| Mode |          | R            | W            |              | RW           |              |               |               |  |

| Init | 0        | 0            | 0            | 0            | 0            | 0            | 0             | 0             |  |

| 0x0E | Bit 7    | Bit 6        | Bit 5        | Bit 4        | Bit 3        | Bit 2        | Bit 1         | Bit 0         |  |

| Name |          | LDO4_S       | EQ[3:0]      |              |              | LDO3_S       | SEQ[3:0]      | 1             |  |

| Mode |          | R            | W            |              |              | R            | W             |               |  |

| Init | 0        | 0            | 0            | 0            | 0            | 0            | 0             | 0             |  |

| 0x0F | Bit 7    | Bit 6        | Bit 5        | Bit 4        | Bit 3        | Bit 2        | Bit 1         | Bit 0         |  |

| Name |          |              |              |              |              | LDO5_S       | SEQ[3:0]      |               |  |

| Mode |          |              |              |              |              | R            | W             |               |  |

| Init |          |              |              |              | 0            | 0            | 0             | 0             |  |

| 0x10 | Bit 7    | Bit 6        | Bit 5        | Bit 4        | Bit 3        | Bit 2        | Bit 1         | Bit 0         |  |

| Name | SEQ_SP   | EED[1:0]     | SEQ1_C       | TRL[1:0]     | SEQ1_ON      | S            | EQ1_COUNT[2   | :0]           |  |

| Mode | R        | W            | R            | W            | R            |              | R             |               |  |

| Init | 0        | 0            | 0            | 0            | 0            | 0            | 0             | 0             |  |

| 0x11 | Bit 7    | Bit 6        | Bit 5        | Bit 4        | Bit 3        | Bit 2        | Bit 1         | Bit 0         |  |

| Name |          |              | SEQ2_C       | TRL[1:0]     | SEQ2_ON      | S            | EQ2_COUNT[2   | :0]           |  |

| Mode |          |              | R            | W            | R            |              | R             |               |  |

| Init |          |              | 0            | 0            | 0            | 0            | 0             | 0             |  |

| 0x12 | Bit 7    | Bit 6        | Bit 5        | Bit 4        | Bit 3        | Bit 2        | Bit 1         | Bit 0         |  |

| Name |          |              |              |              |              |              | GPIO_R        | EAD[1:0]      |  |

| Mode |          |              |              |              |              |              |               | R             |  |

| Init |          |              |              |              |              |              | 0             | 0             |  |

| 0x13 | Bit 7    | Bit 6        | Bit 5        | Bit 4        | Bit 3        | Bit 2        | Bit 1         | Bit 0         |  |

| Name |          | GPIO         | 2[1:0]       | GPIO2_EN_RD  |              | GPIC         | 01[1:0]       | GPIO1_EN_RD   |  |

| Mode |          | R            | W            | RW           |              | R            | W             | RW            |  |

| Init |          | 0            | 0            | 0            |              | 0            | 0             | 0             |  |

| 0x20 | Bit 7    | Bit 6        | Bit 5        | Bit 4        | Bit 3        | Bit 2        | Bit 1         | Bit 0         |  |

| Name |          | ADC_HOLD[2:0 | ]            | ADC_CS_DIS   | ADC_CH       | IAN[1:0]     | ADC_REQ       | ADC_EN        |  |

| Mode |          | RW           |              | RW           | R            | W            | RW            | RW            |  |

| Init | 1        | 1            | 0            | 0            | 0            | 0            | 0             | 0             |  |

| 0x21 | Bit 7    | Bit 6        | Bit 5        | Bit 4        | Bit 3        | Bit 2        | Bit 1         | Bit 0         |  |

| Name |          |              |              | ADC_READ     | _INPUT[7:0]  |              |               |               |  |

| Mode |          |              |              | F            | 8            |              |               |               |  |

| Init | 0        | 0            | 0            | 0            | 0            | 0            | 0             | 0             |  |

| 0x22 | Bit 7    | Bit 6        | Bit 5        | Bit 4        | Bit 3        | Bit 2        | Bit 1         | Bit 0         |  |

| Name |          |              |              |              |              |              | ADC_READ      | _INPUT2[1:0]  |  |

| Mode |          |              |              |              |              |              |               | R             |  |

| Init |          |              |              |              |              |              | 0             | 0             |  |

| 0x23 | Bit 7    | Bit 6        | Bit 5        | Bit 4        | Bit 3        | Bit 2        | Bit 1         | Bit 0         |  |

| Name | ACK_UVLO | ACK_UVP_LDO5 | ACK_UVP_LDO4 | ACK_UVP_LDO3 | ACK_UVP_LDO2 | ACK_UVP_LDO1 | ACK_UVP_DCDC2 | ACK_UVP_DCDC1 |  |

| Mode |           |               |                | R            | C            |           |                  |               |

|------|-----------|---------------|----------------|--------------|--------------|-----------|------------------|---------------|

| Init | 0         | 0             | 0              | 0            | 0            | 0         | 0                | 0             |

| 0x24 | Bit 7     | Bit 6         | Bit 5          | Bit 4        | Bit 3        | Bit 2     | Bit 1            | Bit 0         |

| Name |           | ACK_ILDO5     | ACK_ILDO4      | ACK_ILDO3    | ACK_ILDO2    | ACK_ILDO1 | ACK_IDCDC2       | ACK_IDCDC'    |

| Mode |           |               |                |              | RC           |           |                  |               |

| Init |           | 0             | 0              | 0            | 0            | 0         | 0                | 0             |

| 0x25 | Bit 7     | Bit 6         | Bit 5          | Bit 4        | Bit 3        | Bit 2     | Bit 1            | Bit 0         |

| Name |           |               |                |              |              | ACK_TSD   | ACK_WRNG         | ACK_ADCEOC    |

| Mode |           |               |                |              |              |           | RC               |               |

| Init |           |               |                |              |              | 0         | 0                | 0             |

| 0x26 | Bit 7     | Bit 6         | Bit 5          | Bit 4        | Bit 3        | Bit 2     | Bit 1            | Bit 0         |

| Name | SEN_UVLO  | SEN_UVP_LDO5  | SEN_UVP_LDO4   | SEN_UVP_LDO3 | SEN_UVP_LDO2 |           | SEN_UVP_DCDC2    |               |

| Mode | 02.107.20 | 02.1011 _2000 | 02.1011 _22001 |              | R            |           | 02.1.2011 _00002 | 02.1011 _0000 |

| Init | 0         | 0             | 0              | 0            | 0            | 0         | 0                | 0             |

| 0x27 | Bit 7     | Bit 6         | Bit 5          | Bit 4        | Bit 3        | Bit 2     | Bit 1            | Bit 0         |

| Name |           | SEN_ILDO5     | SEN_ILDO4      | SEN_ILDO3    | SEN_ILDO2    | SEN_ILDO1 | SEN_IDCDC2       |               |

| Mode |           | SEN_IEDOS     | SEN_IEDO4      | SEN_IEDOS    | R            | SEN_ILDOT |                  |               |

| Init |           | 0             | 0              | 0            | 0            | 0         | 0                | 0             |

| 0x28 | Bit 7     | Bit 6         | Bit 5          | Bit 4        | Bit 3        | Bit 2     | Bit 1            | Bit 0         |

| Name |           | Bit 0         | BILS           | BIL 4        | BIL 3        |           | SEN_TSD          | SEN_WRNG      |

| Mode |           |               |                |              |              |           | SEN_TOD          | _             |

| Init |           |               |                |              |              |           | 0                | 0             |

| 0x29 | Bit 7     | Bit 6         | Bit 5          | Bit 4        | Bit 3        | Bit 2     | Bit 1            | Bit 0         |

| Name | MSK_UVLO  | MSK_UVP_LDO5  | MSK_UVP_LDO4   | MSK_UVP_LDO3 | MSK_UVP_LDO2 |           | MSK_UVP_DCDC2    |               |

| Mode |           |               |                | IR           | W            |           |                  |               |

| Init | 1         | 1             | 1              | 1            | 1            | 1         | 1                | 1             |

| 0x2A | Bit 7     | Bit 6         | Bit 5          | Bit 4        | Bit 3        | Bit 2     | Bit 1            | Bit 0         |

| Name |           | MSK_ILDO5     | MSK_ILDO4      | MSK_ILDO3    | MSK_ILDO2    | MSK_ILDO1 | MSK_IDCDC2       | MSK_IDCDC     |

| Mode |           |               |                |              | RW           |           |                  | 1             |

| Init |           | 1             | 1              | 1            | 1            | 1         | 1                | 1             |

| 0x2B | Bit 7     | Bit 6         | Bit 5          | Bit 4        | Bit 3        | Bit 2     | Bit 1            | Bit 0         |

| Name |           |               |                |              |              | MSK_TSD   | MSK_WRNG         | MSK_ADCEOC    |

| Mode |           |               |                |              |              |           | RW               |               |

| Init |           |               |                |              |              | 1         | 1                | 0             |

| 0x2C | Bit 7     | Bit 6         | Bit 5          | Bit 4        | Bit 3        | Bit 2     | Bit 1            | Bit 0         |

| Name |           |               |                |              |              |           | REAR             | M[1:0]        |

| Mode |           |               |                |              |              |           | R                | W             |