ON Semiconductor®

http://onsemi.com

# 5W Power Amplifier with Very Few External Parts for Car Radio and Car Stereo

#### Overview

The LA4425PV is a 5W power amplifier with very few external parts. Encapsulated in a surface mount package [SSOP44K (275 mil)], it is designed for operation without a heat sink. Only two external parts (Only IN/OUT coupling capacitors). Almost no evaluation, adjustment and check of its functions as a power IC required, enabling control to be simplified and set patterns to be further miniaturized.

#### **Functions**

- Wide operation supply range  $\rightarrow$  5 to 16V

- On-chip protection:

- Over-voltage protection

- Thermal protection

- Output D.C. short protection .

- On-chip pop noise reducing circuit

## **Specifications**

**Maximum Ratings** at  $Ta = 25^{\circ}C$

| Parameter                    | Symbol                | Conditions                        | Ratings     | Unit |

|------------------------------|-----------------------|-----------------------------------|-------------|------|

| Maximum supply voltage       | V <sub>CC</sub> max   | $Rg = 0\Omega$                    | 18          | V    |

| Surge maximum supply voltage | V <sub>CC</sub> surge | Giant pulse 200ms                 | 50          | V    |

|                              |                       | Rise time 1ms                     |             |      |

| Maximum output current       | IO peak               |                                   | 3.3         | Α    |

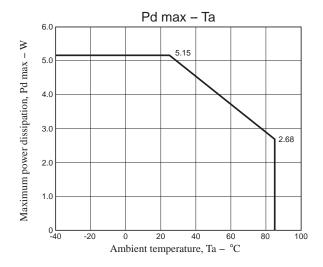

| Allowable power dissipation  | Pd max                | When mounted on the specified PCB | 5.15        | W    |

| Operating temperature        | Topr                  |                                   | -40 to +85  | °C   |

| Storage temperature          | Tstg                  |                                   | -40 to +150 | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

# **Operating Conditions** at Ta = 25°C,

| Parameter                       | Symbol             | Conditions                                 | Ratings | Unit |

|---------------------------------|--------------------|--------------------------------------------|---------|------|

| Recommended supply voltage      | VCC                |                                            | 13.2    | V    |

| Recommended load resistance     | $R_L$              |                                            | 4       | Ω    |

| Operating voltage range         | V <sub>CC</sub> op |                                            | 5 to 16 | V    |

| Operating load resistance range | R <sub>L</sub> op  | Under conditions where maximum ratings are | 2 to 8  | Ω    |

|                                 |                    | not exceeded                               |         |      |

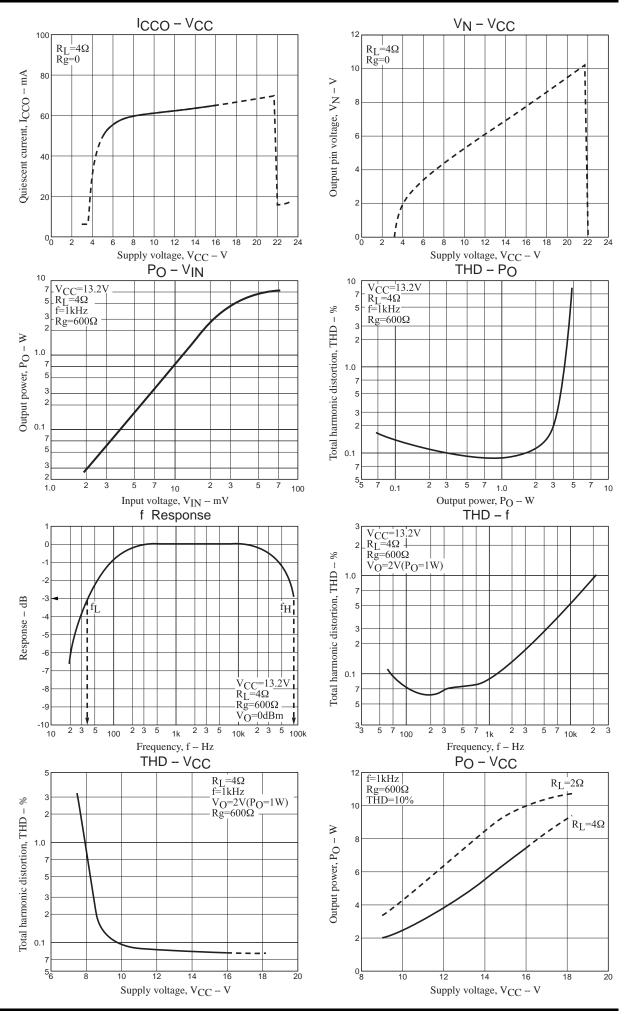

# $\textbf{Electrical Characteristics} \ \ \text{at Ta} = 25^{\circ}\text{C}, \ \ V_{CC} = 13.2\text{V}, \ R_L = 4\Omega, \ f = 1 \ \text{kHz}, \ R_g = 600\Omega, \ Specified \ board/specified \ circuit$

| Parameter                 | Course has l      | Symbol Conditions                                                     |     | Ratings |     |      |

|---------------------------|-------------------|-----------------------------------------------------------------------|-----|---------|-----|------|

|                           | Symbol            |                                                                       | min | typ     | max | Unit |

| Quiescent current         | Icco              |                                                                       |     | 65      | 130 | mA   |

| Voltage gain              | V <sub>G</sub>    | V <sub>O</sub> = 0dBm                                                 | 43  | 45      | 47  | dB   |

| Output power              | P <sub>O</sub> 1  | 13.2 V / 4Ω, THD = 10%                                                |     | 5       |     | W    |

|                           | P <sub>O</sub> 2  | 14.4 V / 4Ω, THD = 10%                                                | 5   | 6       |     | W    |

| Total harmonic distortion | THD               | V <sub>O</sub> = 2Vrms                                                |     | 0.1     | 1.0 | %    |

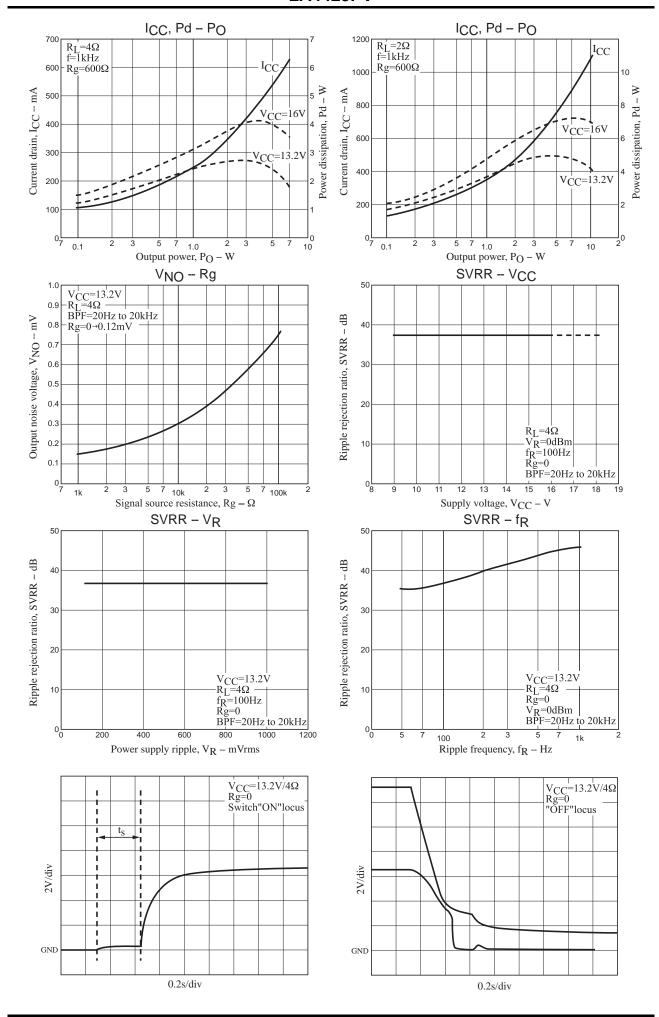

| Output noise voltage      | V <sub>NO</sub>   | Rg = $0\Omega$ , BPF = 20 Hz to 20 kHz                                |     | 0.15    | 0.5 | mV   |

| Ripple rejection ratio    | SVRR1             | Rg = $0\Omega$ , BPF = 20 Hz to 20 kHz<br>$V_R$ = 0dBm, $f_R$ = 100Hz | 30  | 40      |     | dB   |

|                           | SVRR2             | Rg = $0\Omega$ , BPF = 20 Hz to 20 kHz<br>$V_R$ = 0dBm, $f_R$ = 1kHz  |     | 47      |     | dB   |

| Over-voltage attack       | V <sub>CC</sub> X | $Rg = 0\Omega$                                                        |     | 21.5    |     | V    |

| Starting time             | t <sub>S</sub>    |                                                                       |     | 0.35    |     | s    |

| Input resistance          | R <sub>IN</sub>   |                                                                       |     | 50      |     | kΩ   |

| Roll-off frequency        | fL                |                                                                       |     | 40      |     | Hz   |

|                           | fH                |                                                                       |     | 90      |     | kHz  |

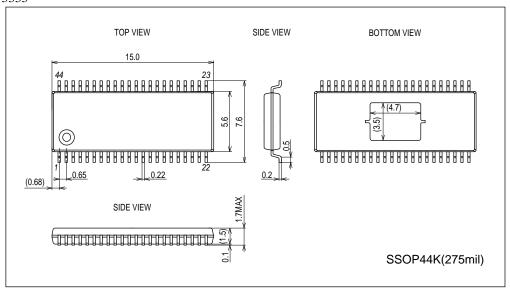

# **Package Dimensions**

unit: mm (typ)

3333

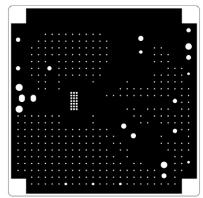

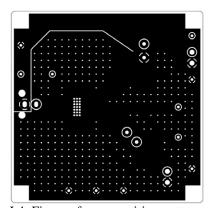

Board specifications of the Pdmax - Ta measurement (LA4425PV specified PCB)

Size:  $70 \text{mm} \times 70 \text{mm} \times 1.6 \text{mm}^3$  (Four layer boards) Copper foil thickness:  $L1/L4=18 \mu \text{m}$ ,  $L2/L3=35 \mu \text{m}$ Materials: FR-4 (Glass cloth matrix epoxy resin)

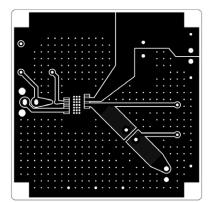

L1: Figure of copper wiring pattern

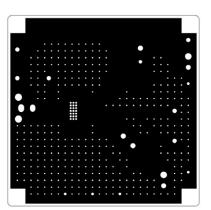

L3: Figure of copper wiring pattern

L2: Figure of copper wiring pattern

L4: Figure of copper wiring pattern

#### Notes:

The data for the case with the exposed die-pad substrate mounted shows the values when 95% or more of the Exposed Die-Pad is wet.

- 1. For the set design, employ the derating design with sufficient margin.

- 2. Stresses to be derated include the voltage, current, junction temperature, power loss, and mechanical stresses such as vibration, impact, and tension.

Accordingly, the design must ensure these stresses to be as low or small as possible.

The guideline for ordinary derating is shown below:

- (1) Maximum value 80% or less for the voltage ratings

- (2) Maximum value 80% or less for the current ratings

- (3) Maximum value 80% or less for the temperature ratings

- 3. After the set has been designed, be sure to verify the design with the actual product. Confirm the solder joint state and verify also the reliability of solder joint for the Exposed Die-Pad, etc. Any void or deterioration, if observed in the solder joint of these parts, causes deteriorated thermal conduction, possibly resulting in thermal destruction of IC.

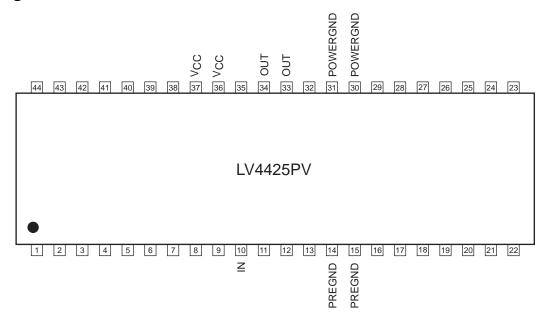

# **Pin Assignment**

- Connect exposed die pad on the back side to GND with a large pattern.

- Pins whose names are not given next to the pin numbers are all "NC pins" that are not connected to the chip inside the package, and they must not be used as relay pins.

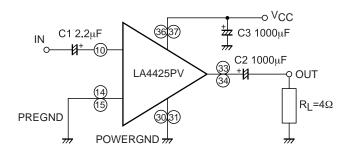

# **Application Circuit Example**

- On-chip overvoltage protection

- On-chip thermal protection

- On-chip pop noise reducing circuit

- On-chip output D.C. short protection

Pin Voltage at  $V_{CC} = 13.2V$

| Characteristics                  | Input                         | Pre GND | Power GND | Output                          | V <sub>CC</sub>             |

|----------------------------------|-------------------------------|---------|-----------|---------------------------------|-----------------------------|

| Pin No.                          | 10                            | 14, 15  | 30, 31    | 33, 34                          | 36, 37                      |

| Pin voltage<br>(reference value) | (≈ 2V <sub>BE</sub> )<br>1.4V | 0V      | 0V        | (≈ 1/2V <sub>CC</sub> )<br>6.5V | (V <sub>CC</sub> )<br>13.2V |

#### **IC Usage Notes**

#### Maximum ratings

If the IC is used in the vicinity of the maximum ratings, even a slight variation in conditions may cause the maximum ratings to be exceeded, thereby leading to a breakdown.

#### • Printed circuit board

When drawing the printed circuit pattern, refer to the sample printed circuit pattern. Be careful not to form a feedback loop between input and output.

Always use both pins of the Pre GND, Power GND, OUT and VCC when designing the layout.

#### • Exposed Die-Pad

The exposed die pad on the back side of the IC must be connected to GND with a large pattern surface area.

#### • Load Resistance and Misoperation

It should be noted that when  $R_L < 2\Omega$  and  $V_{CC}$  is high, and the switch is turned "ON" when setting is for a signal (THD = 10%), the ground detector (current × voltage Schmitt circuit) operates momentarily.

#### • Starting Time (t<sub>S</sub>)

This is set at 0.35sec/typ, but it can be made shorter by making input capacitor Ci smaller, or longer by making it larger.

#### • Pop noise

The pop noise prevention circuit operates to reduce pop until Rg reaches  $50k\Omega$ . However, if Rg is left open, the charging route of input capacitor Ci is lost, so the pop noise reduction circuit stops operating and click noises become louder.

#### • VG/OSC

The voltage gain is fixed at 45dB inside the IC. It is impossible to change it externally.

Phase compensation capacitors (350pF/total) are connected between individual stages inside the IC, and the open loop gain is low. In addition, the upper and lower drives are made equivalent so that final stage current gain is adjusted, providing a measure against unwanted high-frequency parasitic oscillation peculiar to power IC's.

#### BTL Connection

Connection is impossible with IC alone.

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equa