# Transceiver for KNX Twisted Pair Networks

### Introduction

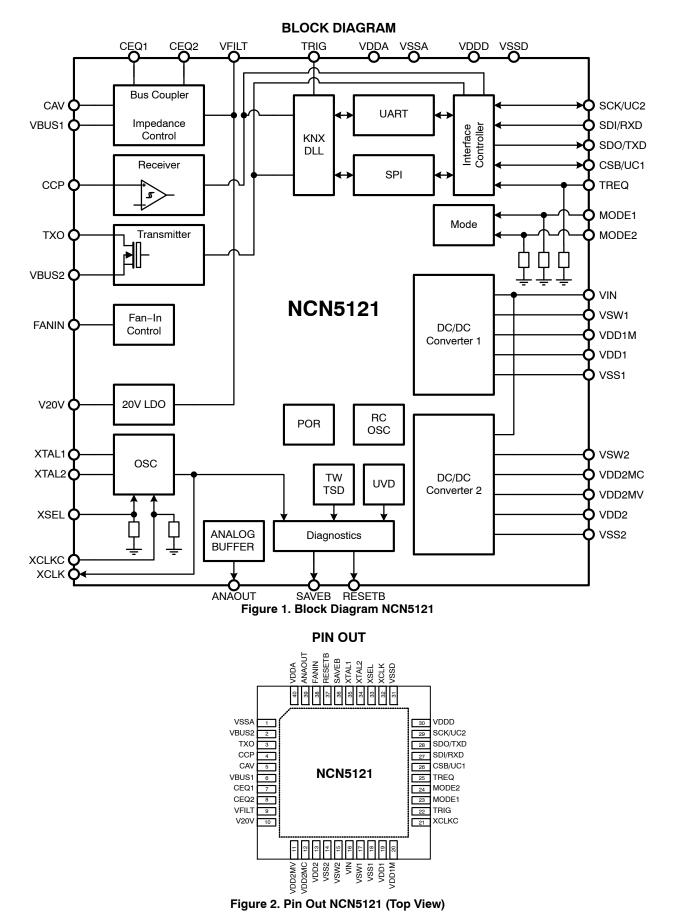

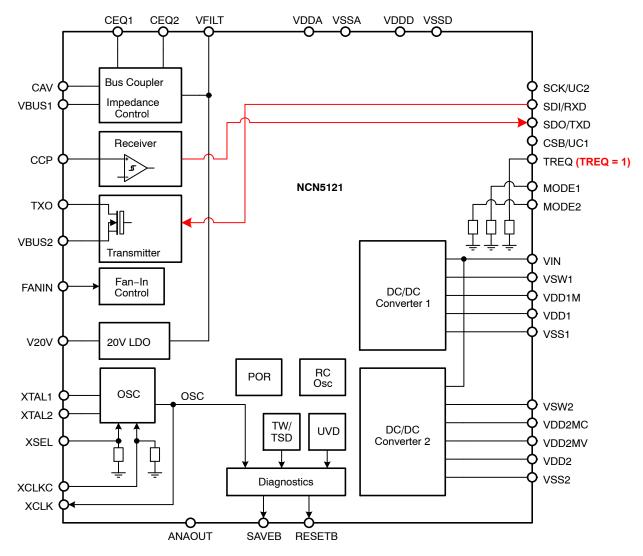

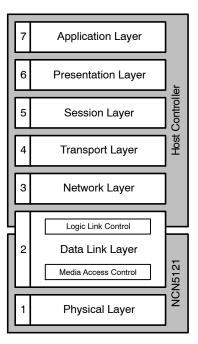

NCN5121 is a receiver-transmitter IC suitable for use in KNX twisted pair networks (KNX TP1-256). It supports the connection of actuators, sensors, microcontrollers, switches or other applications in a building network.

NCN5121 handles the transmission and reception of data on the bus. It generates from the unregulated bus voltage stabilized voltages for its own power needs as well as to power external devices, for example, a microcontroller.

NCN5121 assures safe coupling to and decoupling from the bus. Bus monitoring warns the external microcontroller in case of loss of power so that critical data can be stored in time.

### **Key Features**

- 9600 baud KNX Communication Speed

- Supervision of KNX Bus Voltage and Current

- Supports Bus Current Consumption up to 24 mA

- High Efficient DC–DC Converters

- 3.3 V Fixed

- 1.2 V to 21 V Selectable

- Control and Monitoring of Power Regulators

- Linear 20 V Regulator

- Buffering of Sent Data Frames (Extended Frames Supported)

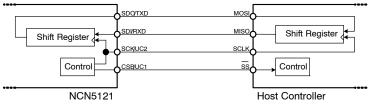

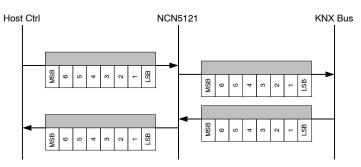

- Selectable UART or SPI Interface to Host Controller

- Selectable UART and SPI baud Rate to Host Controller

- Optional CRC on UART to the Host

- Optional Received Frame-end with MARKER Service

- Optional Direct Analog Signaling to Host

- Operates with Industry Standard Low Cost 16 MHz Quartz

- Generates Clock of 8 or 16 MHz for External Devices

- Auto Acknowledge (optional)

- Auto Polling (optional)

- Temperature Monitoring

- Extended Operating Temperature Range -40°C to +105°C

- These Devices are Pb-Free and are RoHS Compliant

# **ON Semiconductor®**

www.onsemi.com

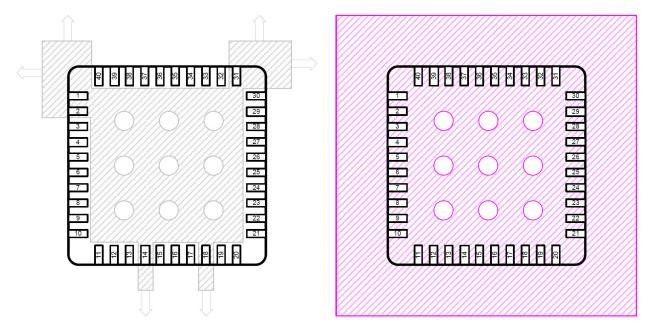

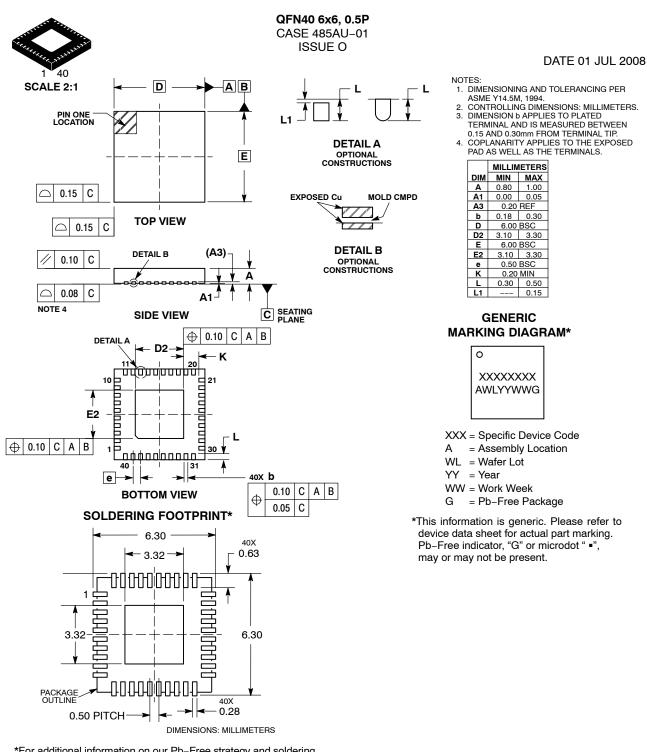

QFN40 MN SUFFIX CASE 485AU

### MARKING DIAGRAM

A = Assembly Location

- WL = Wafer Lot

- YY = Year

- WW = Work Week

- G = Pb-Free Package

### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 57 of this data sheet.

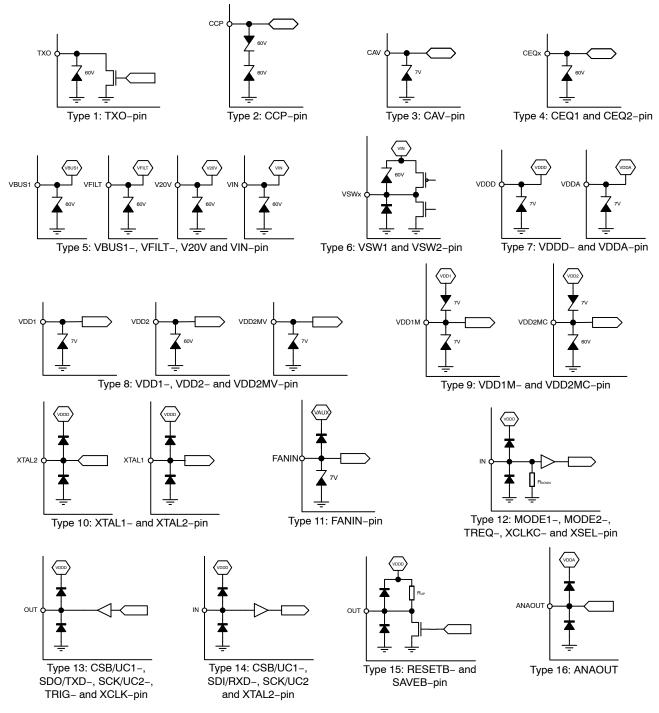

## **PIN DESCRIPTION**

### Table 1. PIN LIST AND DESCRIPTION

| Name Pin Descripti |    | Description                                                                                             | Туре                               | Equivalent<br>Schematic |

|--------------------|----|---------------------------------------------------------------------------------------------------------|------------------------------------|-------------------------|

| VSSA               | 1  | Analog Supply Voltage Ground                                                                            | Supply                             |                         |

| VBUS2              | 2  | Ground for KNX Transmitter                                                                              | Supply                             |                         |

| TX0                | 3  | KNX Transmitter Output                                                                                  | Analog Output                      | Type 1                  |

| CCP                | 4  | AC coupling external capacitor connection                                                               | Analog I/O                         | Type 2                  |

| CAV                | 5  | Capacitor connection to average bus DC voltage                                                          | Analog I/O                         | Туре 3                  |

| VBUS1              | 6  | KNX power supply input                                                                                  | Supply                             | Type 5                  |

| CEQ1               | 7  | Capacitor connection 1 for defining equalization pulse                                                  | Analog I/O                         | Type 4                  |

| CEQ2               | 8  | Capacitor connection 2 for defining equalization pulse                                                  | Analog I/O                         | Type 4                  |

| VFILT              | 9  | Filtered bus voltage                                                                                    | Supply                             | Type 5                  |

| V20V               | 10 | 20V supply output                                                                                       | Supply                             | Type 5                  |

| VDD2MV             | 11 | Voltage monitor of Voltage Regulator 2                                                                  | Analog Input                       | Type 8                  |

| VDD2MC             | 12 | Current monitor input 1 of Voltage Regulator 2                                                          | Analog Input                       | Туре 9                  |

| VDD2               | 13 | Current monitor input 2 of Voltage Regulator 2                                                          | Analog Input                       | Type 8                  |

| VSS2               | 14 | Voltage Regulator 2 Ground                                                                              | Supply                             |                         |

| VSW2               | 15 | Switch output of Voltage Regulator 2                                                                    | Analog Output                      | Type 6                  |

| VIN                | 16 | Voltage Regulator 1 and 2 Power Supply Input                                                            | Supply                             | Type 5                  |

| VSW1               | 17 | Switch output of Voltage Regulator 1                                                                    | Analog Output                      | Type 6                  |

| VSS1               | 18 | Voltage Regulator 1 Ground                                                                              | Supply                             |                         |

| VDD1               | 19 | Current Input 2 and Voltage Monitor Input of Voltage Regulator 1                                        | Analog Input                       | Type 8                  |

| VDD1M              | 20 | Current Monitor Input 1 of Voltage Monitor 1                                                            | Analog Input                       | Type 9                  |

| XCLKC              | 21 | Clock Frequency Configure                                                                               | Digital Input                      | Type 12                 |

| TRIG               | 22 | Transmission Trigger Output                                                                             | Digital Output                     | Type 13                 |

| MODE1              | 23 | Mode Selection Input 1                                                                                  | Digital Input                      | Type 12                 |

| MODE2              | 24 | Mode Selection Input 2                                                                                  | Digital Input                      | Type 12                 |

| TREQ               | 25 | Transmit Request Input                                                                                  | Digital Input                      | Type 12                 |

| CSB/UC1            | 26 | Chip Select Output (SPI) or Configuration Input (UART)<br>or 20 V LDO Disable (Analog Mode)             | Digital Output or<br>Digital Input | Type 13 or 1            |

| SDI/RXD            | 27 | Serial Data Input (SPI) or Receive Input (UART)                                                         | Digital Input                      | Type 14                 |

| SDO/TXD            | 28 | Serial Data Output (SPI) or Transmit Output (UART)                                                      | Digital Output                     | Type 13                 |

| SCK/UC2            | 29 | Serial Clock Output (SPI) or Configuration Input (UART)<br>or Voltage Regulator 2 Disable (Analog Mode) | Digital Output or<br>Digital Input | Type 13 or 1            |

| VDDD               | 30 | Digital Supply Voltage Input                                                                            | Supply                             | Type 7                  |

| VSSD               | 31 | Digital Supply Voltage Ground                                                                           | Supply                             |                         |

| XCLK               | 32 | Oscillator Clock Output                                                                                 | Digital Output                     | Type 13                 |

| XSEL               | 33 | Clock Selection (Quartz or Digital Clock)                                                               | Digital Input                      | Type 12                 |

| XTAL2              | 34 | Clock Generator Output (Quartz) or Input (Digital Clock)                                                | Analog Output or<br>Digital Input  | Type 10 or 1            |

| XTAL1              | 35 | Clock Generator Input (Quartz)                                                                          | Analog Input                       | Type 10                 |

| SAVEB              | 36 | Save Signal (open drain with pull-up)                                                                   | Digital Output                     | Type 15                 |

| RESETB             | 37 | Reset Signal (open drain with pull–up)                                                                  | Digital Output                     | Type 15                 |

| FANIN              | 38 | Fan-In Input                                                                                            | Digital Input                      | Type 11                 |

| ANAOUT             | 39 | Analog Signal Output                                                                                    | Analog Output                      | Type 16                 |

| VDDA               | 40 | Analog Supply Voltage Input                                                                             | Supply                             | Type 7                  |

NOTE: Type of CSB/UC1 and SCK/UC2 is depending on status MODE1 – MODE2 pin

Type of XTAL1 and XTAL2 pin is depending on status XSEL pin.

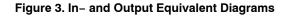

### **EQUIVALENT SCHEMATICS**

Following figure gives the equivalent schematics of the user relevant inputs and outputs. The diagrams are simplified representations of the circuits used.

NOTE: Type of CSB/UC1 and SCK/UC2 is depending on status MODE1 – MODE2 pin Type of XTAL1 and XTAL2 pin is depending on status XSEL pin.

### **ELECTRICAL SPECIFICATION**

### Table 2. ABSOLUTE MAXIMUM RATINGS (Notes 1 and 2)

| Symbol              | Parameter                                                                                                                     | Min   | Max   | Unit |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------|-------|-------|------|

| V <sub>TXO</sub>    | KNX Transmitter Output Voltage                                                                                                | -0.3  | +45   | V    |

| I <sub>TXO</sub>    | KNX Transmitter Output Current (Note 3)                                                                                       | -     | 250   | mA   |

| V <sub>CCP</sub>    | Voltage on CCP-pin                                                                                                            | -10.5 | +14.5 | V    |

| V <sub>CAV</sub>    | Voltage on CAV-pin                                                                                                            | -0.3  | +3.6  | V    |

| V <sub>BUS1</sub>   | Voltage on VBUS1-pin                                                                                                          | -0.3  | +45   | V    |

| V <sub>ANAOUT</sub> | Voltage on ANAOUT pin                                                                                                         | -0.3  | +3.6  | V    |

| I <sub>BUS1</sub>   | Current Consumption VBUS1-pin                                                                                                 | 0     | 120   | mA   |

| V <sub>CEQ</sub>    | Voltage on pins CEQ1 and CEQ2                                                                                                 | -0.3  | +45   | V    |

| V <sub>FILT</sub>   | Voltage on VFILT-pin                                                                                                          | -0.3  | +45   | V    |

| V <sub>20V</sub>    | Voltage on V20V-pin                                                                                                           | -0.3  | +25   | V    |

| V <sub>DD2MV</sub>  | Voltage on VDD2MV-pin                                                                                                         | -0.3  | +3.6  | V    |

| V <sub>DD2MC</sub>  | Voltage on VDD2MC-pin                                                                                                         | -0.3  | +45   | V    |

| V <sub>DD2</sub>    | Voltage on VDD2-pin                                                                                                           | -0.3  | +45   | V    |

| V <sub>SW</sub>     | Voltage on VSW1- and VSW2-pin                                                                                                 | -0.3  | +45   | V    |

| V <sub>IN</sub>     | Voltage on VIN-pin                                                                                                            | -0.3  | +45   | V    |

| V <sub>DD1</sub>    | Voltage on VDD1-pin                                                                                                           | -0.3  | +3.6  | V    |

| V <sub>DD1M</sub>   | Voltage on VDD1M-pin                                                                                                          | -0.3  | +3.6  | V    |

| V <sub>DIG</sub>    | Voltage on pins MODE1, MODE2, TREQ, CSB/UC1, SDI/TXD, SDO/RXD, SCK/<br>UC2, XCLK, XSEL, SAVEB, RESETB, XCLKC, TRIG, and FANIN | -0.3  | +3.6  | V    |

| V <sub>DD</sub>     | Voltage on VDDD- and VDDA-pin                                                                                                 | -0.3  | +3.6  | V    |

| V <sub>XTAL</sub>   | Voltage on XTAL1- and XTAL2-pin                                                                                               | -0.3  | +3.6  | V    |

| T <sub>ST</sub>     | Storage temperature                                                                                                           | -55   | +150  | °C   |

| TJ                  | Junction Temperature (Note 4)                                                                                                 | -40   | +155  | °C   |

| V <sub>HBM</sub>    | Human Body Model electronic discharge immunity (Note 5)                                                                       | -2    | +2    | kV   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Convention: currents flowing in the circuit are defined as positive.

2. VBUS2, VSS1, VSS2, VSSA and VSSD form the common ground. They are hard connected to the PCB ground layer.

3. Room temperature, 27  $\Omega$  shunt resistor for transmitter, 250 mA over temperature range.

Normal performance within the limitations is guaranteed up to the Thermal Warning level. Between Thermal Warning and Thermal Shutdown temporary loss of function or degradation of performance (which ceases after the disturbance ceases) is possible.

5. According to JEDEC JESD22-A114.

### **Recommend Operation Conditions**

Operating ranges define the limits for functional operation and parametric characteristics of the device. Note that the functionality of the chip outside these operating ranges is not guaranteed. Operating outside the recommended operating ranges for extended periods of time may affect device reliability.

### **Table 3. OPERATING RANGES**

| Symbol             | Parameter                                                                            | Min      | Max   | Unit |

|--------------------|--------------------------------------------------------------------------------------|----------|-------|------|

| V <sub>BUS1</sub>  | VBUS1 Voltage (Note 6)                                                               | +20      | +33   | V    |

| V <sub>DD</sub>    | Digital and Analog Supply Voltage (VDDD- and VDDA-pin)                               | +3.13    | +3.47 | V    |

| V <sub>IN</sub>    | Input Voltage DC-DC Converter 1 and 2                                                | (Note 7) | +33   | V    |

| V <sub>CCP</sub>   | Input Voltage at CCP-pin                                                             | -10.5    | +14.5 | V    |

| V <sub>CAV</sub>   | Input Voltage at CAV-pin                                                             | 0        | +3.3  | V    |

| V <sub>DD1</sub>   | Input Voltage on VDD1-pin                                                            | +3.13    | +3.47 | V    |

| V <sub>DD1M</sub>  | Input Voltage on VDD1M-pin                                                           | +3.13    | +3.57 | V    |

| V <sub>DD2</sub>   | Input Voltage on VDD2-pin                                                            | +1.2     | +21   | V    |

| V <sub>DD2MC</sub> | Input Voltage on VDD2MC-pin                                                          | +1.2     | +21.1 | V    |

| V <sub>DD2MV</sub> | Input Voltage on VDD2MV-pin                                                          | +1.2     | VDD   | V    |

| V <sub>DIG</sub>   | Input Voltage on pins MODE1, MODE2, TREQ, CSB/UC1, SDI/RXD, SCK/UC2, XCLKC, and XSEL | 0        | VDD   | V    |

| V <sub>FANIN</sub> | Input Voltage on FANIN-pin                                                           | 0        | 3.6   | V    |

| f <sub>clk</sub>   | Clock Frequency External Quartz                                                      | 16       |       | MHz  |

| T <sub>A</sub>     | Ambient Temperature                                                                  | -40      | +105  | °C   |

| TJ                 | Junction Temperature (Note 8)                                                        | -40      | +125  | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.6. Voltage indicates DC value. With equalization pulse bus voltage must be between 11 V and 45 V.

7. Minimum operating voltage on VIN-pin should be at least 1 V larger than the highest value of VDD1 and VDD2.

8. Higher junction temperature can result in reduced lifetime.

**Table 4. DC PARAMETERS** The DC parameters are given for a device operating within the Recommended Operating Conditions

unless otherwise specified. Convention: currents flowing in the circuit are defined as positive.

| Symbol                          | Pin(s)   | Parameter                                                            | <b>Remark/Test Conditions</b>                                                                                                                    | Min  | Тур  | Max  | Unit |

|---------------------------------|----------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| POWER SUPP                      | PLY      | •                                                                    | •                                                                                                                                                |      | •    |      |      |

| V <sub>BUS1</sub>               | VBUS1    | Bus DC voltage                                                       | Excluding active and equalization pulse                                                                                                          | 20   | -    | 33   | V    |

| I <sub>BUS1_Int</sub>           |          | Bus Current Consumption                                              | VBUS = 30 V, IBUS = 10 mA,<br>DC2, V20V disabled, no crystal<br>or clock                                                                         | -    | 2.00 | 2.70 | mA   |

|                                 |          | Bus Current Consumption                                              | VBUS = 20 V, IBUS = 20 mA                                                                                                                        | -    | 3.20 | 4.10 |      |

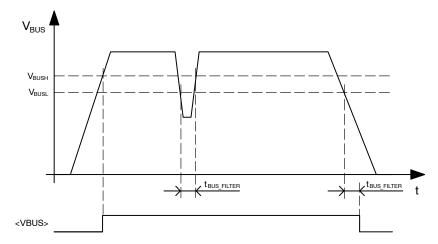

| V <sub>BUSH</sub>               |          | Undervoltage release level                                           | V <sub>BUS1</sub> rising, see Figure 4                                                                                                           | 17.1 | 18.0 | 18.9 | V    |

| V <sub>BUSL</sub>               |          | Undervoltage trigger level                                           | V <sub>BUS1</sub> falling, see Figure 4                                                                                                          | 15.9 | 16.8 | 17.7 | V    |

| V <sub>BUS_Hyst</sub>           |          | Undervoltage hysteresis                                              |                                                                                                                                                  | 0.6  | -    | -    | V    |

| V <sub>DDD</sub>                | VDDD     | Digital Power Supply                                                 |                                                                                                                                                  | 3.13 | 3.3  | 3.47 | V    |

| V <sub>DDA</sub>                | VDDA     | Analog Power Supply                                                  |                                                                                                                                                  | 3.13 | 3.3  | 3.47 | V    |

| V <sub>AUX</sub>                |          | Auxiliary Supply                                                     | Internal supply, for info only                                                                                                                   | 2.8  | 3.3  | 3.6  | V    |

| KNX BUS CO                      | UPLER    |                                                                      |                                                                                                                                                  |      |      |      |      |

| $\Delta I_{coupler} / \Delta t$ | VBUS1    | Bus Coupler Current Slope                                            | FANIN floating, V <sub>FILT</sub> > V <sub>FILTH</sub>                                                                                           | -    | 0.40 | 0.50 | A/s  |

|                                 |          | Limitation                                                           | FANIN = 0, V <sub>FILT</sub> > V <sub>FILTH</sub>                                                                                                | -    | 0.80 | 1.00 | A/s  |

| I <sub>coupler_lim,</sub>       | VBUS1    | Bus Coupler Startup Current                                          | FANIN floating, V <sub>FILT</sub> > V <sub>FILTH</sub>                                                                                           | 20.0 | 25.0 | 30.0 | mA   |

| startup                         |          | Limitation                                                           | FANIN = 0, V <sub>FILT</sub> > V <sub>FILTH</sub>                                                                                                | 40.0 | 50.0 | 60.0 | mA   |

| I <sub>coupler_lim</sub>        | VBUS1    | Bus Coupler Current Limitation                                       | FANIN floating, V <sub>FILT</sub> > V <sub>FILTH</sub>                                                                                           | 10.6 | 11.4 | 12.0 | mA   |

|                                 |          |                                                                      | FANIN = 0, V <sub>FILT</sub> > V <sub>FILTH</sub>                                                                                                | 20.5 | 22.3 | 24.0 | mA   |

| V <sub>coupler_drop</sub>       | VBUS1,   | Coupler Voltage Drop                                                 | I <sub>BUS1</sub> = 10 mA                                                                                                                        | -    | 1.72 | 2.32 | V    |

|                                 | VFILT    | (V <sub>coupler_drop</sub> = V <sub>BUS1</sub> – V <sub>FILT</sub> ) | I <sub>BUS1</sub> = 20 mA                                                                                                                        | -    | 2.34 | 2.80 | V    |

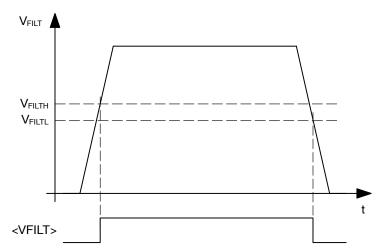

| V <sub>FILTH</sub>              | VFILT    | Undervoltage release level                                           | V <sub>FILT</sub> rising, see Figure 5                                                                                                           | 10.1 | 10.6 | 11.2 | V    |

| V <sub>FILTL</sub>              |          | Undervoltage trigger level                                           | V <sub>FILT</sub> falling, see Figure 5                                                                                                          | 8.4  | 8.9  | 9.4  | V    |

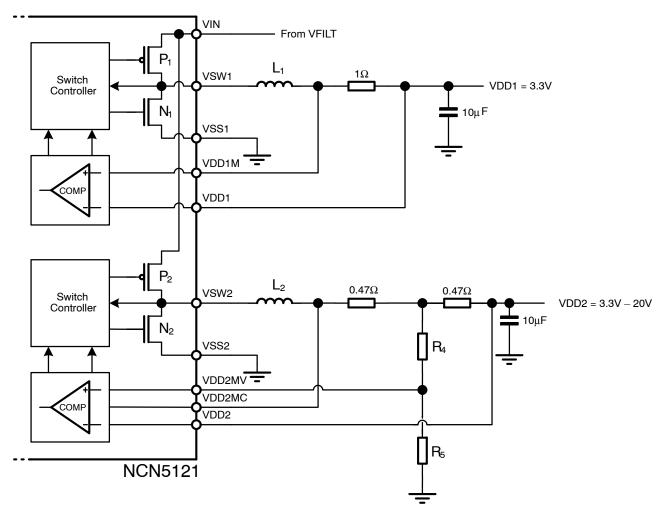

| FIXED DC-DC                     | CONVERTE | R                                                                    |                                                                                                                                                  | -    |      |      |      |

| V <sub>IN</sub>                 | VIN      | Input Voltage                                                        |                                                                                                                                                  | 4.47 | -    | 33   | V    |

| V <sub>DD1</sub>                | VDD1     | Output Voltage                                                       |                                                                                                                                                  | 3.13 | 3.3  | 3.47 | V    |

| V <sub>DD1_rip</sub>            |          | Output Voltage Ripple                                                | $V_{IN}$ = 25 V, I <sub>DD1</sub> = 40 mA,<br>L1 = 220 µH                                                                                        | -    | 40   | -    | mV   |

| I <sub>DD1_lim</sub>            |          | Overcurrent Threshold                                                | $R_2 = 1 \Omega$ , see Figure 13                                                                                                                 | -100 | -    | -200 | mA   |

| ባVDD1                           |          | Power Efficiency<br>(DC Converter Only)                              | $\begin{array}{l} V_{in} = 25 \; V, \; I_{DD1} = 35 \; mA, \\ L_1 = 220 \; \mu H \; (1.26 \; \Omega \; ESR), \\ see \; Figure \; 12 \end{array}$ |      | 90   | -    | %    |

| R <sub>DS(on)_p1</sub>          |          | R <sub>DS(on)</sub> of power switch                                  | See Figure 18                                                                                                                                    | -    | -    | 9    | Ω    |

| R <sub>DS(on)_n1</sub>          |          | R <sub>DS(on)</sub> of flyback switch                                | See Figure 18                                                                                                                                    | -    | -    | 4    | Ω    |

| V <sub>DD1M</sub>               | VDD1M    | Input voltage VDD1M-pin                                              |                                                                                                                                                  | -    | -    | 3.57 | V    |

| Table 4. DC PARAMETERS The DC parameters are given for a device operating within the Recommended Operating Conditions |

|-----------------------------------------------------------------------------------------------------------------------|

| unless otherwise specified. Convention: currents flowing in the circuit are defined as positive.                      |

| Symbol                              | Pin(s)       | Parameter                               | <b>Remark/Test Conditions</b>                                                                                   | Min                     | Тур                       | Max              | Unit |

|-------------------------------------|--------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------|---------------------------|------------------|------|

| ADJUSTABL                           | E DC-DC CONV | ERTER                                   |                                                                                                                 |                         |                           |                  |      |

| $V_{IN}$                            | VIN          | Input Voltage                           |                                                                                                                 | V <sub>DD2</sub><br>+ 1 | _                         | 33               | V    |

| V <sub>DD2</sub>                    | VDD2         | Output Voltage                          | $V_{IN} \ge V_{DD2}$                                                                                            | 1.2                     | -                         | 21               | V    |

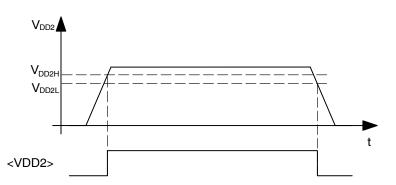

| V <sub>DD2H</sub>                   |              | Undervoltage release level              | V <sub>DD2</sub> rising, see Figure 6                                                                           | -                       | 0.9 x<br>V <sub>DD2</sub> | -                | V    |

| V <sub>DD2L</sub>                   |              | Undervoltage trigger level              | $V_{DD2}$ falling, see Figure 6                                                                                 | -                       | 0.8 x<br>V <sub>DD2</sub> | -                | V    |

| V <sub>DD2_rip</sub>                |              | Output Voltage Ripple                   | $\begin{array}{l} V_{IN} = 25 \; V,  V_{DD2} = 3.3 \; V, \\ I_{DD2} = 40 \; mA,  L2 = 220 \; \mu H \end{array}$ | -                       | 40                        | -                | mV   |

| I <sub>DD2_lim</sub>                |              | Overcurrent Threshold                   | $R_3 = 1 \Omega$ , see Figure 13                                                                                | -100                    | -                         | -250             | mA   |

| η <sub>VDD2</sub>                   |              | Power Efficiency<br>(DC Converter Only) | $V_{in}$ = 25 V, $V_{DD2}$ = 3.3 V,<br>$I_{DD2}$ = 35 mA, $L_2$ = 220 μH<br>(1.26 Ω ESR), see Figure 13         | -                       | 90                        | -                | %    |

| R <sub>DS(on)_p2</sub>              |              | R <sub>DS(on)</sub> of power switch     | See Figure 18                                                                                                   | -                       | -                         | 8                | Ω    |

| R <sub>DS(on)_n2</sub>              |              | R <sub>DS(on)</sub> of flyback switch   | See Figure 18                                                                                                   | -                       | -                         | 4                | Ω    |

| V <sub>DD2M</sub>                   | VDD2MC       | Input voltage VDD2MC-pin                |                                                                                                                 | -                       | -                         | 21.1             | V    |

| R <sub>VDD2M</sub>                  | VDD2MV       | Input Resistance VDD2MV-pin             |                                                                                                                 | 1                       | -                         | -                | MΩ   |

| I <sub>leak,vsw2</sub>              |              | Half-bridge leakage                     |                                                                                                                 | -                       | -                         | 20               | μA   |

| V20V REGU                           | LATOR        |                                         |                                                                                                                 |                         |                           |                  |      |

| V <sub>20V</sub>                    | V20V         | V20V Output Voltage                     | $I_{20V} < I_{20V\_lim}, V_{FILT} \ge 21 \text{ V}$                                                             | 18                      | 20                        | 22               | V    |

| $\Delta {\rm I}_{\rm 20V, \; STEP}$ |              | V20V Output Current                     | FANIN floating                                                                                                  | -                       | 1.25                      | -                | mA   |

|                                     |              | Limitation Step                         | FANIN = 0                                                                                                       | -                       | 2.50                      | -                | mA   |

| I <sub>20V_lim</sub>                |              | V20V Output Current Limitation          | FANIN floating                                                                                                  | 6                       | 7.5                       | 9                | mA   |

|                                     |              | (for V20VCLIMIT[2:0] = 100)             | FANIN = 0                                                                                                       | 12                      | 15                        | 18               | mA   |

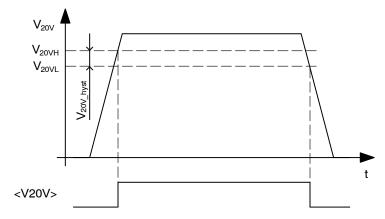

| V <sub>20VH</sub>                   |              | V20V Undervoltage release<br>level      | $V_{20V}$ rising, see Figure 7                                                                                  | 14.2                    | 15.0                      | 15.8             | V    |

| V <sub>20VL</sub>                   |              | V20V Undervoltage trigger<br>level      | $V_{20V}$ falling, see Figure 7                                                                                 | 13.2                    | 14.0                      | 14.8             | V    |

| V <sub>20V_hyst</sub>               |              | V20V Undervoltage hysteresis            | $V_{20V\_hyst} = V_{20VH} - V_{20VL}$                                                                           | -                       | 1.0                       | -                | V    |

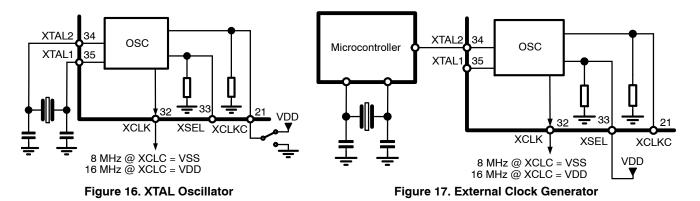

| XTAL OSCIL                          | LATOR        |                                         |                                                                                                                 |                         |                           |                  |      |

| V <sub>XTAL</sub>                   | XTAL1, XTAL2 | Voltage on XTAL-pin                     |                                                                                                                 | -                       | -                         | V <sub>DDD</sub> | V    |

| FAN-IN CON                          | ITROL        |                                         |                                                                                                                 |                         |                           |                  |      |

| I <sub>pu,fanin</sub>               | FANIN        | Pull-Up Current FANIN-pin               | FANIN shorted to GND,<br>Pull-up connected to V <sub>AUX</sub>                                                  | 10                      | 20                        | 40               | μA   |

Table 4. DC PARAMETERS

The DC parameters are given for a device operating within the Recommended Operating Conditions

unless otherwise specified.

Convention: currents flowing in the circuit are defined as positive.

| Symbol              | Pin(s)                                    | Parameter                                                                                            | <b>Remark/Test Conditions</b>              | Min                        | Тур   | Max              | Unit |

|---------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------|----------------------------|-------|------------------|------|

| DIGITAL INP         | UTS                                       |                                                                                                      |                                            |                            |       |                  | -    |

| V <sub>IL</sub>     | SCK/UC2,<br>SDI/RXD,                      | Logic Low Threshold                                                                                  |                                            | 0                          | -     | 0.7              | V    |

| V <sub>IH</sub>     | CSB/UC1,<br>TREQ,                         | Logic High Threshold                                                                                 |                                            |                            | -     | V <sub>DDD</sub> | V    |

| R <sub>DOWN</sub>   | MODE1,<br>MODE2,<br>XSEL, XCLKC,<br>XTAL2 | Internal Pull-Down Resistor SCK/UC2-, SDI/RXD- and CSB/UC1 pin excluded. Only valid in Normal State. |                                            | 5                          | 10    | 28               | kΩ   |

| DIGITAL OU          | TPUTS                                     |                                                                                                      | •                                          | -                          |       | •                |      |

| V <sub>OL</sub>     | SCK/UC2,                                  | Logic low output level                                                                               |                                            | 0                          | -     | 0.4              | V    |

| V <sub>OH</sub>     | SDO/TXD,<br>CSB/UC1,<br>XCLK, TRIG        | Logic high output level                                                                              |                                            | V <sub>DDD</sub> -<br>0.45 | -     | V <sub>DDD</sub> | V    |

| ۱ <sub>L</sub>      | SCK/UC2,<br>XCLK, TRIG                    | Load Current                                                                                         |                                            | -                          | -     | 8                | mA   |

|                     | SDO/TXD,<br>CSB/UC1                       |                                                                                                      |                                            | -                          | -     | 4                | mA   |

| V <sub>OL</sub>     | SAVEB,                                    | Logic low level open drain                                                                           | I <sub>OL</sub> = 4 mA                     | -                          | -     | 0.4              | V    |

| R <sub>up</sub>     | RESETB                                    | Internal Pull-up Resistor                                                                            |                                            | 20                         | 40    | 80               | kΩ   |

| ANALOG OU           | ITPUT                                     |                                                                                                      |                                            |                            |       |                  |      |

| PV <sub>BUS</sub>   | ANAOUT                                    | Analog output division ratio for V <sub>BUS</sub>                                                    |                                            | 0.067                      | 0.071 | 0.075            | -    |

| PV <sub>FILT</sub>  |                                           | Analog output division ratio for                                                                     | V <sub>FILT</sub>                          | 0.071                      | 0.075 | 0.079            | -    |

| PV <sub>20V</sub>   |                                           | Analog output division ratio for                                                                     | V <sub>20V</sub>                           | 0.086                      | 0.091 | 0.096            | -    |

| PV <sub>DDA</sub>   |                                           | Analog output division ratio for                                                                     | V <sub>DDA</sub>                           | 0.438                      | 0.462 | 0.485            | -    |

| PV <sub>DD2</sub>   |                                           | Analog output division ratio for                                                                     | V <sub>DD2MV</sub>                         | 0.950                      | 1.000 | 1.050            | -    |

| PI <sub>BUS</sub>   |                                           | Analog output conversion ratio                                                                       | for I <sub>BUS</sub>                       | 14.0                       | 20.9  | 28.8             | V/A  |

| PTJ                 |                                           | Analog output conversion ratio                                                                       | for T <sub>junction</sub>                  | -                          | -4    | -                | mV/K |

| VTJ <sub>OFF</sub>  |                                           | Analog output offset for Tjunctic                                                                    | <sub>on</sub> at 300K                      | -                          | 1.309 | -                | V    |

| V <sub>OFF</sub>    |                                           | Analog output offset voltage                                                                         |                                            | -12                        | -     | 12               | mV   |

| t <sub>SW,ANA</sub> |                                           | Time between writing Analog (<br>ANAOUT voltage (<1 nF capa                                          |                                            | -                          | 33    | -                | μs   |

| TEMPERATU           | JRE MONITOR                               |                                                                                                      |                                            |                            |       |                  | -    |

| T <sub>TW</sub>     |                                           | Thermal Warning                                                                                      | Rising temperature<br>See Figure 8         | 105                        | 115   | 125              | °C   |

| T <sub>TSD</sub>    |                                           | Thermal shutdown                                                                                     | Rising temperature<br>See Figure 8         | 130                        | 140   | 150              | °C   |

| T <sub>Hyst</sub>   |                                           | Thermal Hysteresis                                                                                   | See Figure 8                               | 5                          | 11    | 15               | °C   |

| $\Delta T$          |                                           | Delta $T_{TSD}$ and $T_{TW}$                                                                         | See Figure 8                               | -                          | 21.7  | -                | °C   |

| PACKAGE T           | HERMAL RESIS                              | TANCE VALUE                                                                                          |                                            |                            |       |                  |      |

| R <sub>θ</sub> ,ja  |                                           | Thermal Resistance<br>Junction-to-Ambient                                                            | Simulated Conform<br>JEDEC JESD-51, (2S2P) | -                          | 30    | -                | K/W  |

|                     |                                           |                                                                                                      | Simulated Conform<br>JEDEC JESD-51, (1S0P) | -                          | 60    | -                | K/W  |

| R <sub>θ</sub> ,jp  |                                           | Thermal Resistance<br>Junction-to-Exposed Pad                                                        |                                            | -                          | 0.95  | _                | K/W  |

Table 5. AC PARAMETERS

The AC parameters are given for a device operating within the Recommended Operating Conditions

unless otherwise specified.

Image: Condition of Condit

|                                                                                                 | Pin(s)            | Parameter                                                                                                                                                                                                                                 | <b>Remark/Test Conditions</b>                                                                                                                                                                 | Min                                                                                                                     | Тур                                                                                            | Max                                    | Unit                 |

|-------------------------------------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------|----------------------|

| POWER SUP                                                                                       | PLY               |                                                                                                                                                                                                                                           |                                                                                                                                                                                               |                                                                                                                         |                                                                                                |                                        |                      |

| t <sub>BUS_FILTER</sub>                                                                         | VBUS1             | VBUS1 filter time                                                                                                                                                                                                                         | See Figure 4                                                                                                                                                                                  | -                                                                                                                       | 2                                                                                              | -                                      | ms                   |

| FIXED DC-D                                                                                      | C CONVERTER       |                                                                                                                                                                                                                                           |                                                                                                                                                                                               |                                                                                                                         |                                                                                                |                                        | -                    |

| t <sub>VSW1_rise</sub>                                                                          | VSW1              | Rising slope at VSW1-pin                                                                                                                                                                                                                  |                                                                                                                                                                                               | -                                                                                                                       | 0.45                                                                                           | -                                      | V/ns                 |

| t <sub>VSW1_fall</sub>                                                                          |                   | Falling slope at VSW1-pin                                                                                                                                                                                                                 |                                                                                                                                                                                               | -                                                                                                                       | 0.6                                                                                            | -                                      | V/ns                 |

| ADJUSTABL                                                                                       | E DC-DC CONV      | ERTER                                                                                                                                                                                                                                     |                                                                                                                                                                                               |                                                                                                                         |                                                                                                |                                        |                      |

| t <sub>VSW2_rise</sub>                                                                          | VSW2              | Rising slope at VSW2-pin                                                                                                                                                                                                                  |                                                                                                                                                                                               | -                                                                                                                       | 0.45                                                                                           | -                                      | V/ns                 |

| t <sub>VSW2_fall</sub>                                                                          |                   | Falling slope at VSW2-pin                                                                                                                                                                                                                 |                                                                                                                                                                                               | -                                                                                                                       | 0.6                                                                                            | -                                      | V/ns                 |

| XTAL OSCIL                                                                                      | LATOR             |                                                                                                                                                                                                                                           |                                                                                                                                                                                               |                                                                                                                         |                                                                                                |                                        | -                    |

| <b>f</b> XTAL                                                                                   | XTAL1, XTAL2      | XTAL Oscillator Frequency                                                                                                                                                                                                                 |                                                                                                                                                                                               | -                                                                                                                       | 16                                                                                             | -                                      | MHz                  |

| WATCHDOG                                                                                        |                   | •                                                                                                                                                                                                                                         |                                                                                                                                                                                               |                                                                                                                         |                                                                                                |                                        |                      |

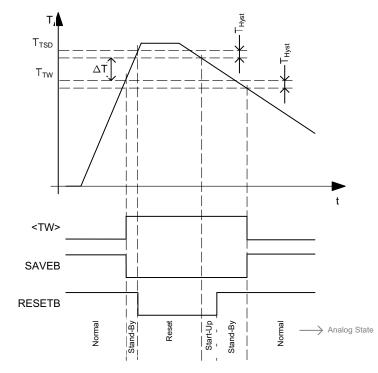

| t <sub>WDPR</sub>                                                                               |                   | Prohibited Watchdog<br>Acknowledge Delay                                                                                                                                                                                                  | See Watchdog, p22                                                                                                                                                                             | 2                                                                                                                       | -                                                                                              | 33                                     | ms                   |

| t <sub>WDTO</sub>                                                                               |                   | Watchdog Timeout Interval                                                                                                                                                                                                                 | Selectable over UART or SPI                                                                                                                                                                   | 33                                                                                                                      | -                                                                                              | 524                                    | ms                   |

| t <sub>WDTO_acc</sub>                                                                           |                   | Watchdog Timeout Interval<br>Accuracy                                                                                                                                                                                                     |                                                                                                                                                                                               |                                                                                                                         | =Xtal ad                                                                                       | ccuracy                                | •                    |

| t <sub>WDRD</sub>                                                                               |                   | Watchdog Reset Delay                                                                                                                                                                                                                      |                                                                                                                                                                                               | _                                                                                                                       | 0                                                                                              | -                                      | ns                   |

| t <sub>RESET</sub>                                                                              |                   | Reset Duration                                                                                                                                                                                                                            |                                                                                                                                                                                               | -                                                                                                                       | 8                                                                                              | _                                      | μs                   |

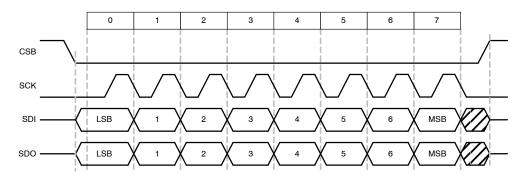

| MASTER SE                                                                                       | RIAL PERIPHER     | AL INTERFACE (MASTER SP                                                                                                                                                                                                                   | I)                                                                                                                                                                                            |                                                                                                                         |                                                                                                |                                        | -                    |

|                                                                                                 |                   |                                                                                                                                                                                                                                           | SPI Baudrate depending on                                                                                                                                                                     |                                                                                                                         |                                                                                                |                                        |                      |

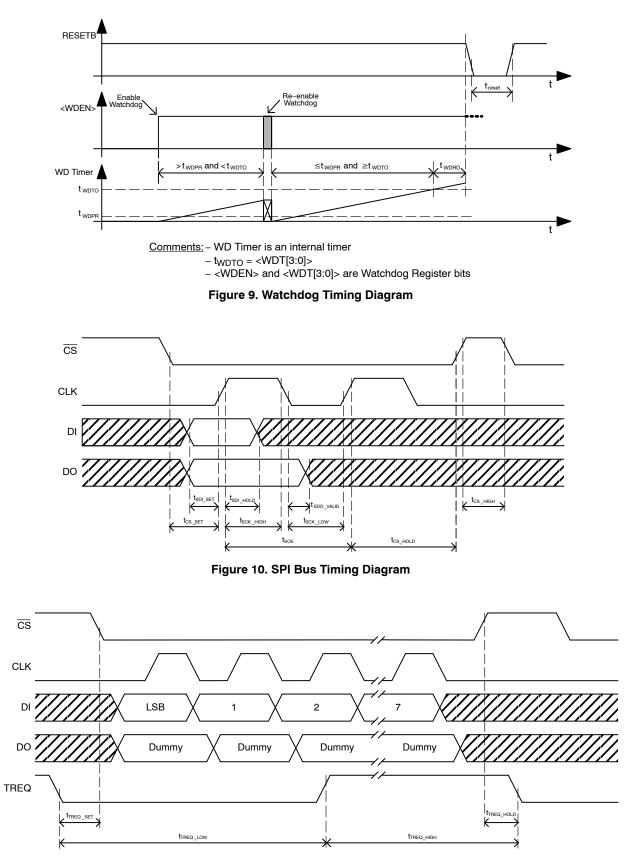

| t <sub>sck</sub>                                                                                | SCK               | SPI Clock period                                                                                                                                                                                                                          |                                                                                                                                                                                               | -                                                                                                                       | 2                                                                                              | -                                      | μs                   |

| t <sub>sck</sub>                                                                                | SCK               | SPI Clock period                                                                                                                                                                                                                          | configuration input bits (see<br>Interface Mode, p26). Tolerance                                                                                                                              | -                                                                                                                       | 2<br>8                                                                                         | -                                      | μs<br>μs             |

| t <sub>sck</sub><br>t <sub>SCK_HIGH</sub>                                                       | SCK               | SPI Clock period<br>SPI Clock high time                                                                                                                                                                                                   | configuration input bits (see<br>Interface Mode, p26). Tolerance<br>is equal to Xtal oscillator                                                                                               |                                                                                                                         |                                                                                                |                                        | •                    |

|                                                                                                 | SCK               |                                                                                                                                                                                                                                           | configuration input bits (see<br>Interface Mode, p26). Tolerance                                                                                                                              | -                                                                                                                       | 8                                                                                              |                                        | •                    |

| t <sub>SCK_HIGH</sub>                                                                           | SCK               | SPI Clock high time                                                                                                                                                                                                                       | configuration input bits (see<br>Interface Mode, p26). Tolerance<br>is equal to Xtal oscillator<br>tolerance.                                                                                 | -                                                                                                                       | 8<br>t <sub>SCK</sub> / 2                                                                      |                                        | •                    |

| t <sub>SCK_HIGH</sub><br>t <sub>SCK_LOW</sub>                                                   |                   | SPI Clock high time<br>SPI Clock low time                                                                                                                                                                                                 | configuration input bits (see<br>Interface Mode, p26). Tolerance<br>is equal to Xtal oscillator<br>tolerance.                                                                                 | -                                                                                                                       | 8<br>t <sub>SCK</sub> / 2<br>t <sub>SCK</sub> / 2                                              | -                                      | μs                   |

| <sup>t</sup> SCK_HIGH<br><sup>t</sup> SCK_LOW<br><sup>t</sup> SDI_SET                           |                   | SPI Clock high time<br>SPI Clock low time<br>SPI Data Input setup time                                                                                                                                                                    | configuration input bits (see<br>Interface Mode, p26). Tolerance<br>is equal to Xtal oscillator<br>tolerance.                                                                                 | -<br>-<br>-<br>125                                                                                                      | 8<br>t <sub>SCK</sub> / 2<br>t <sub>SCK</sub> / 2                                              | -                                      | μs<br>ns             |

| tsck_High<br>tsck_Low<br>tsDI_SET<br>tsDI_HOLD                                                  | SDI               | SPI Clock high time<br>SPI Clock low time<br>SPI Data Input setup time<br>SPI Data Input hold time                                                                                                                                        | configuration input bits (see<br>Interface Mode, p26). Tolerance<br>is equal to Xtal oscillator<br>tolerance.<br>See also Figure 10                                                           | -<br>-<br>125<br>125                                                                                                    | 8<br>t <sub>SCK</sub> /2<br>t <sub>SCK</sub> /2<br>-<br>-                                      |                                        | μs<br>ns<br>ns       |

| tsck_high<br>tsck_low<br>tsdi_set<br>tsdi_hold<br>tsdo_valid                                    | SDI<br>SDO        | SPI Clock high time<br>SPI Clock low time<br>SPI Data Input setup time<br>SPI Data Input hold time<br>SPI Data Output valid time                                                                                                          | configuration input bits (see<br>Interface Mode, p26). Tolerance<br>is equal to Xtal oscillator<br>tolerance.<br>See also Figure 10<br>C <sub>L</sub> = 20 pF, See Figure 10                  | -<br>-<br>125<br>125<br>-<br>0.5 x                                                                                      | 8<br>t <sub>SCK</sub> / 2<br>t <sub>SCK</sub> / 2<br>-<br>-                                    |                                        | μs<br>ns<br>ns       |

| tsck_high<br>tsck_low<br>tsdi_set<br>tsdi_hold<br>tsdo_valid<br>tcs_high                        | SDI<br>SDO        | SPI Clock high time<br>SPI Clock low time<br>SPI Data Input setup time<br>SPI Data Input hold time<br>SPI Data Output valid time<br>SPI Chip Select high time                                                                             | configuration input bits (see<br>Interface Mode, p26). Tolerance<br>is equal to Xtal oscillator<br>tolerance.<br>See also Figure 10<br>C <sub>L</sub> = 20 pF, See Figure 10                  | -<br>-<br>125<br>125<br>-<br>0.5 x<br>t <sub>SCK</sub><br>0.5 x                                                         | 8<br>t <sub>SCK</sub> /2<br>t <sub>SCK</sub> /2<br>-<br>-<br>-<br>-                            |                                        | μs<br>ns<br>ns       |

| tsck_high<br>tsck_low<br>tsdi_set<br>tsdi_hold<br>tsdo_valid<br>tcs_high<br>tcs_set             | SDI<br>SDO        | SPI Clock high time<br>SPI Clock low time<br>SPI Data Input setup time<br>SPI Data Input hold time<br>SPI Data Output valid time<br>SPI Chip Select high time<br>SPI Chip Select setup time                                               | configuration input bits (see<br>Interface Mode, p26). Tolerance<br>is equal to Xtal oscillator<br>tolerance.<br>See also Figure 10<br>C <sub>L</sub> = 20 pF, See Figure 10                  | -<br>-<br>125<br>125<br>-<br>0.5 x<br>t <sub>SCK</sub><br>0.5 x<br>t <sub>SCK</sub>                                     | 8<br>t <sub>SCK</sub> / 2<br>t <sub>SCK</sub> / 2<br>-<br>-<br>-<br>-<br>-                     |                                        | μs<br>ns<br>ns       |

| tsck_high<br>tsck_low<br>tsdi_set<br>tsdi_hold<br>tsdo_valid<br>tcs_high<br>tcs_set<br>tcs_hold | SDI<br>SDO<br>CSB | SPI Clock high time<br>SPI Clock low time<br>SPI Data Input setup time<br>SPI Data Input hold time<br>SPI Data Output valid time<br>SPI Chip Select high time<br>SPI Chip Select setup time<br>SPI Chip Select hold time                  | configuration input bits (see<br>Interface Mode, p26). Tolerance<br>is equal to Xtal oscillator<br>tolerance.<br>See also Figure 10<br>C <sub>L</sub> = 20 pF, See Figure 10<br>See Figure 10 | -<br>-<br>125<br>125<br>-<br>0.5 x<br>t <sub>SCK</sub><br>0.5 x<br>t <sub>SCK</sub><br>0.5 x<br>t <sub>SCK</sub>        | 8<br>t <sub>SCK</sub> / 2<br>t <sub>SCK</sub> / 2<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-      | -<br>-<br>-<br>-<br>100<br>-<br>-<br>- | μs<br>ns<br>ns<br>ns |

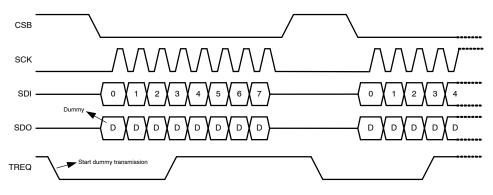

| tsck_HiGH<br>tsck_Low<br>tsDI_SET<br>tsDI_HOLD<br>tsDO_VALID<br>tcs_HIGH<br>tcs_SET<br>tcs_HOLD | SDI<br>SDO<br>CSB | SPI Clock high time<br>SPI Clock low time<br>SPI Data Input setup time<br>SPI Data Input hold time<br>SPI Data Output valid time<br>SPI Chip Select high time<br>SPI Chip Select setup time<br>SPI Chip Select hold time<br>TREQ low time | configuration input bits (see<br>Interface Mode, p26). Tolerance<br>is equal to Xtal oscillator<br>tolerance.<br>See also Figure 10<br>C <sub>L</sub> = 20 pF, See Figure 10<br>See Figure 10 | -<br>-<br>125<br>125<br>-<br>0.5 х<br>t <sub>SCK</sub><br>0.5 х<br>t <sub>SCK</sub><br>0.5 х<br>t <sub>SCK</sub><br>125 | 8<br>t <sub>SCK</sub> / 2<br>t <sub>SCK</sub> / 2<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>- | -<br>-<br>-<br>100<br>-<br>-<br>-<br>- | ns<br>ns<br>ns<br>ns |

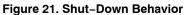

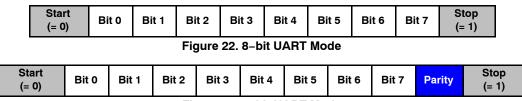

| f <sub>UART</sub> | TXD, RXD | UART Interface Baudrate | Baudrate depending on<br>configuration input pins (see<br>Interface Mode, p26). | - | 19200 | - | Baud |

|-------------------|----------|-------------------------|---------------------------------------------------------------------------------|---|-------|---|------|

|                   |          |                         | Tolerance is equal to tolerance<br>of Xtal oscillator tolerance.                | - | 38400 | - | Baud |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

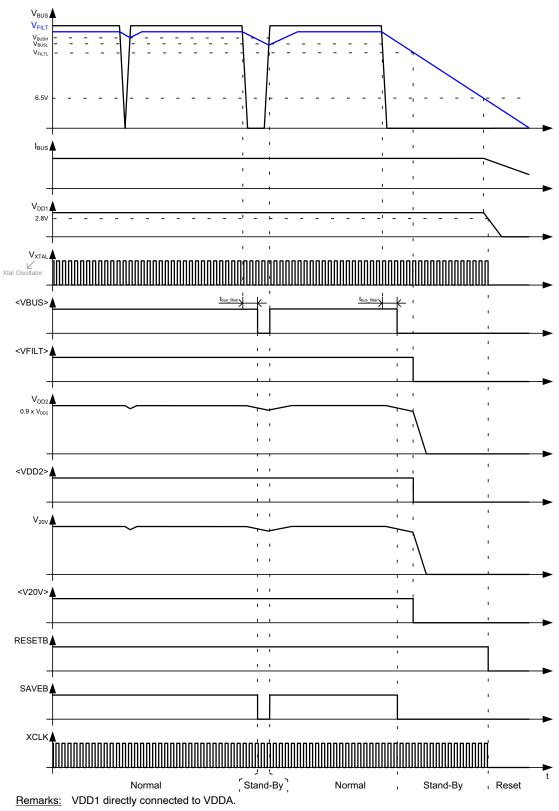

Comments: </BUS> is an internal signal which can be verified with the Internal State Service

Figure 4. Bus Voltage Undervoltage Threshold

Comments: </FILT> is an internal signal which can be verified with the Internal State Service

Figure 5. VFILT Undervoltage Threshold

Comments: <VDD2> is an internal signal which can be verified with the Internal State Service

Figure 6. VDD2 Undervoltage Thresholds

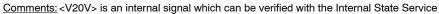

<u>Remarks:</u> - <TW> is an internal signal which can be verified with the System State Service. - No SPI/UART communication possible when RESETB is low!

- It's assumed all voltage supplies are within their operating condition.

Figure 8. Temperature Monitoring Levels

Figure 11. TREQ Timing Diagram

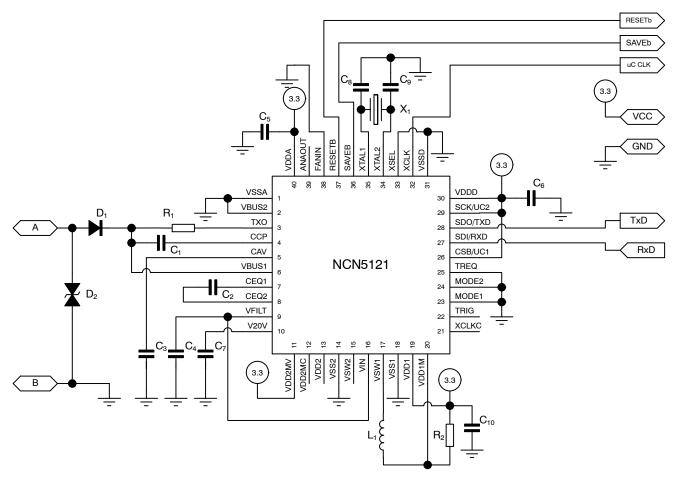

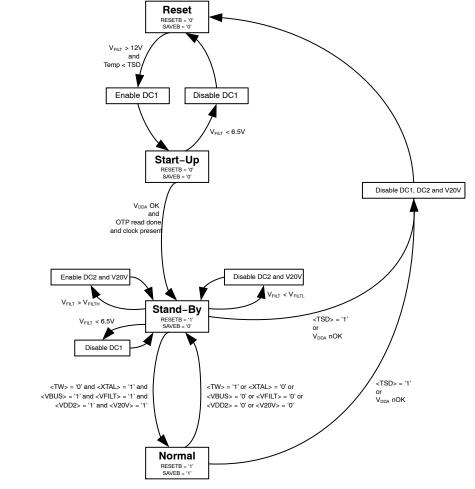

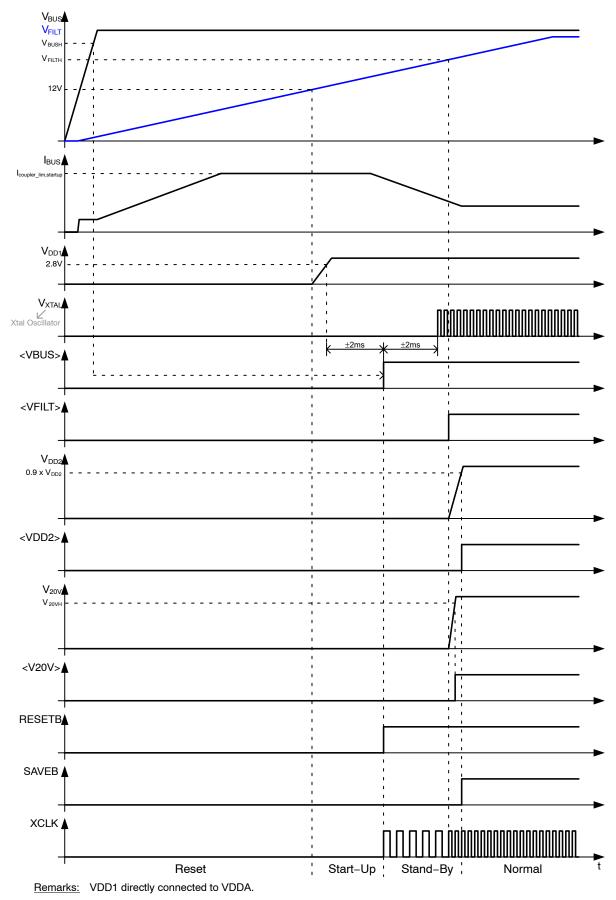

# **TYPICAL APPLICATION SCHEMATICS**

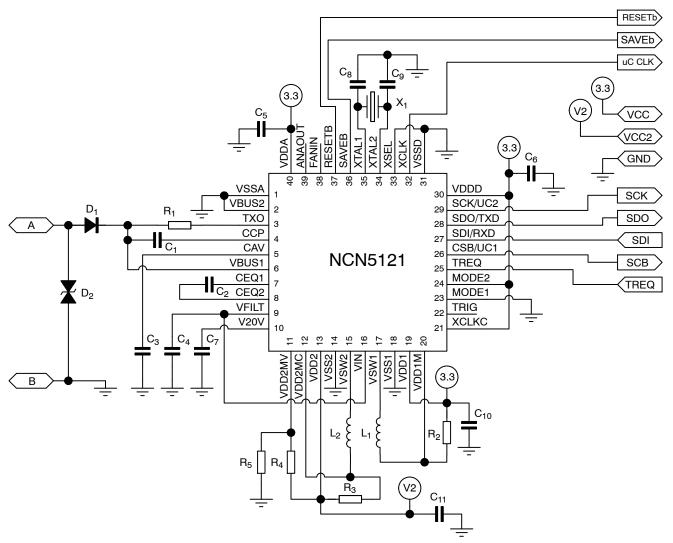

Figure 12. Typical Application Schematic, 8-bit UART Mode (38400 bps), Single Supply, 20 mA Bus Current Limit and 1 mA/ms Bus Current Slopes, 8 MHz Microcontroller Clock Signal

# **TYPICAL APPLICATION SCHEMATICS**

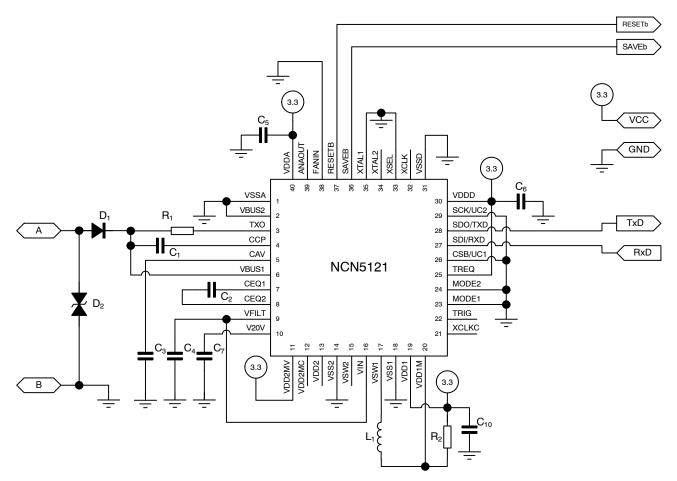

Figure 13. Typical Application Schematic, SPI (500 kbps), Dual Supply, 10 mA Bus Current Limit and 0.5 mA/ms Bus Current Slopes, 16 MHz Clock for Microcontroller

# **TYPICAL APPLICATION SCHEMATICS**

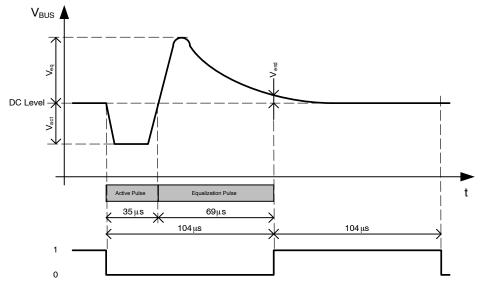

Figure 14. Typical Application Schematic, Analog Mode, Single Supply, 20 mA Bus Current Limit and 1.0 mA/ms Bus Current Slopes, 8 MHz Clock Signal for Microcontroller

| Comp.                           | Function                            | Min  | Тур      | Max  | Unit | Remarks                            | Notes         |

|---------------------------------|-------------------------------------|------|----------|------|------|------------------------------------|---------------|

| C <sub>1</sub>                  | AC coupling capacitor               | 42.3 | 47       | 51.7 | nF   | 50 V, Ceramic                      | 9             |

| C <sub>2</sub>                  | Equalization capacitor              | 198  | 220      | 242  | nF   | 50 V, Ceramic                      | 9             |

| C <sub>3</sub>                  | Capacitor to average bus DC voltage | 80   | 100      | 120  | nF   | 50 V, Ceramic                      | 9             |

| C <sub>4</sub>                  | Storage and filter capacitor VFILT  | 80   | 100      | 4000 | μF   | 35 V                               | 9, 16         |

| C <sub>5</sub>                  | VDDA HF rejection capacitor         | 80   | 100      | -    | nF   | 6.3 V, Ceramic                     |               |

| C <sub>6</sub>                  | VDDD HF rejection capacitor         | 80   | 100      | -    | nF   | 6.3 V, Ceramic                     |               |

| C <sub>7</sub>                  | Load Capacitor V20V                 | -    | 1        | -    | μF   | 35 V, Ceramic, ESR < 2 $\Omega$    | 14,<br>15, 16 |

| C <sub>8</sub> , C <sub>9</sub> | Parallel capacitor X-tal            | 8    | 10       | 12   | pF   | 6.3 V, Ceramic                     | 10            |

| C <sub>10</sub>                 | Load capacitor VDD1                 | 8    | 10       |      | μF   | 6.3 V, Ceramic, ESR < 0.1 $\Omega$ |               |

| C <sub>11</sub>                 | Load capacitor VDD2                 | 8    | 10       |      | μF   | Ceramic, ESR < 0.1 $\Omega$        | 11            |