## L99PM72GXP

# Advanced power management system IC with embedded LIN and high speed CAN transceiver supporting CAN Partial Networking

Datasheet - production data

#### **Features**

- Two 5 V voltage regulators for microcontroller and peripheral supply

- No electrolytic capacitor required on regulator outputs

- Ultra low quiescent current in standby modes

- Programmable reset generator for power-on and undervoltage

- Configurable window watchdog and fail safe output

- LIN 2.1 compliant (SAEJ2602 compatible) transceiver

- Advanced high speed CAN transceiver (ISO 11898-2/-5 and SAE J2284 compliant) with local failure and bus failure diagnosis and selective wake-up functionality according to ISO 11898-6

- Complete 3 channel contact monitoring interface with programmable cyclic sense functionality

- Programmable periodic system wake-up feature

- ST SPI interface for mode control and diagnosis

- 5 fully protected high-side drivers with internal 4-channel PWM generator

- · 2 low-side drivers with active Zener clamping

- 4 Internal PWM timers

- 2 operational amplifiers with rail-to-rail outputs (V<sub>S</sub>) and low voltage inputs

- Temperature warning and thermal shutdown

## **Applications**

Automotive ECU's such as door zone and body control modules description

### **Description**

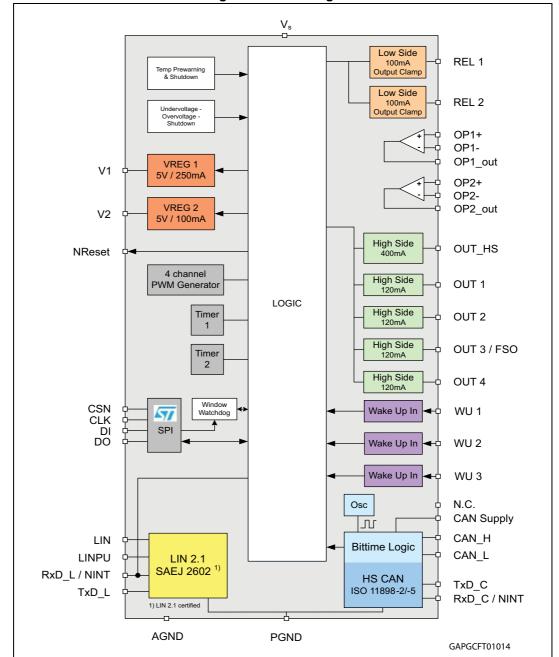

The L99PM72GXP is a power management system IC providing electronic control units with enhanced system power supply functionality including various standby modes as well as LIN and HS CAN physical communication layers. It contains two low drop voltage regulators to supply the system microcontroller and external peripheral loads such as sensors and provides enhanced system standby functionality with programmable local and remote wake up capability.

In addition, five high-side drivers, two low-side drivers and two operational amplifiers increase the system integration level.

The ST standard SPI Interface (3.0) allows control and diagnosis of the device and enables generic software development.

**Table 1. Device summary**

| Package     | Order code |               |  |

|-------------|------------|---------------|--|

| rackage     | Tube       | Tape and reel |  |

| PowerSSO-36 | L99PM72GXP | L99PM72GXPTR  |  |

April 2014 DocID024767 Rev 4 1/129

Contents L99PM72GXP

## **Contents**

| 1 | Bloc | k diagra | am and pin description                                                  | 10 |

|---|------|----------|-------------------------------------------------------------------------|----|

| 2 | Deta | iled des | scription                                                               | 13 |

|   | 2.1  | Voltage  | e regulators                                                            | 13 |

|   |      | 2.1.1    | Voltage regulator: V <sub>1</sub>                                       | 13 |

|   |      | 2.1.2    | Voltage regulator: V <sub>2</sub>                                       | 13 |

|   |      | 2.1.3    | Increased output current capability for voltage regulator $V_2 \ \dots$ | 14 |

|   |      | 2.1.4    | Voltage regulator failure                                               | 16 |

|   |      | 2.1.5    | Voltage regulator behavior                                              | 17 |

|   | 2.2  | Operat   | ting modes                                                              | 17 |

|   |      | 2.2.1    | Active Mode                                                             | 17 |

|   |      | 2.2.2    | Flash Mode                                                              | 17 |

|   |      | 2.2.3    | SW-Debug Mode                                                           | 18 |

|   |      | 2.2.4    | V <sub>1_standby</sub> mode                                             | 18 |

|   |      | 2.2.5    | Interrupt                                                               | 19 |

|   |      | 2.2.6    | V <sub>Bat_standby</sub> mode                                           | 20 |

|   |      | 2.2.7    | Wake up from Standby Modes                                              | 20 |

|   |      | 2.2.8    | Wake up inputs                                                          | 21 |

|   |      | 2.2.9    | Cyclic contact supply                                                   | 22 |

|   |      | 2.2.10   | Timer interrupt / wake-up of microcontroller by timer                   | 22 |

|   | 2.3  | Function | onal overview (truth table)                                             | 22 |

|   | 2.4  | Config   | urable window watchdog                                                  | 24 |

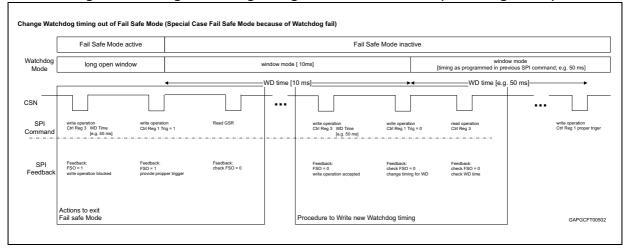

|   |      | 2.4.1    | Change watchdog timing                                                  | 26 |

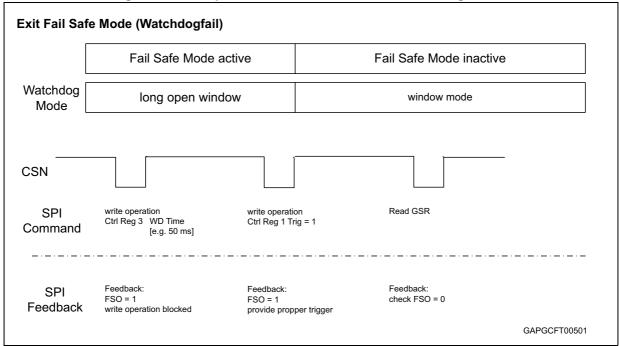

|   | 2.5  | Fail Sa  | ıfe Mode                                                                | 28 |

|   |      | 2.5.1    | Single failures                                                         | 28 |

|   |      | 2.5.2    | Multiple failures – entering forced V <sub>Bat_standby</sub> Mode       | 30 |

|   | 2.6  | Reset    | output (NRESET)                                                         | 31 |

|   | 2.7  | Operat   | tional amplifiers                                                       | 31 |

|   | 2.8  | LIN Bu   | ıs Interface                                                            | 32 |

|   |      | 2.8.1    | Error handling                                                          |    |

|   |      | 2.8.2    | Wake up (from LIN)                                                      |    |

|   |      | 2.8.3    | LIN Pull-Up                                                             |    |

|   | 2.9  | High s   | peed CAN bus transceiver                                                | 34 |

|   |      |          |                                                                         |    |

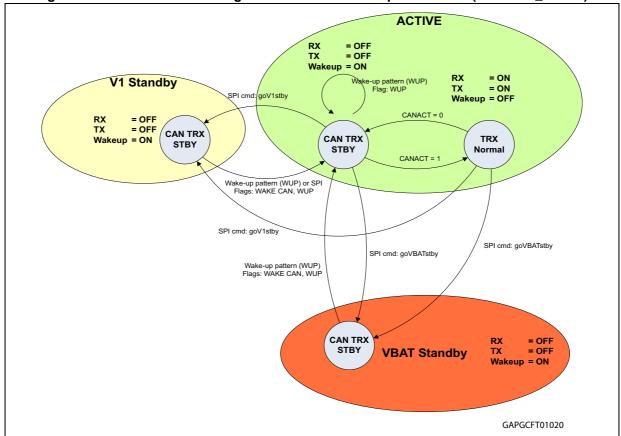

|   |            | 2.9.1                                                                                                         | CAN transceiver operating modes                                                                                                                                                                                                                                          | 35                                                 |

|---|------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

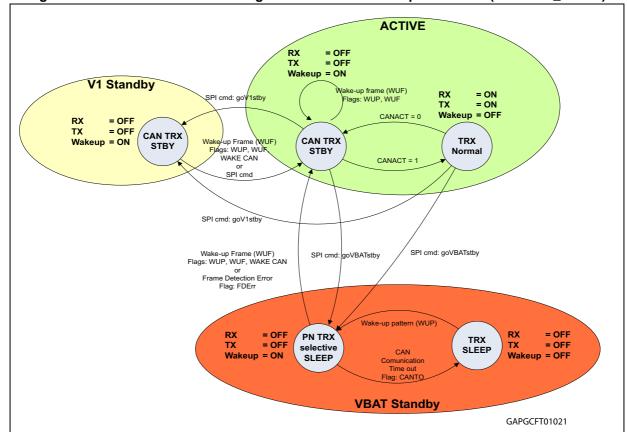

|   |            | 2.9.2                                                                                                         | Sequence for enabling selective wakeup                                                                                                                                                                                                                                   | 37                                                 |

|   |            | 2.9.3                                                                                                         | CAN error handling                                                                                                                                                                                                                                                       | 37                                                 |

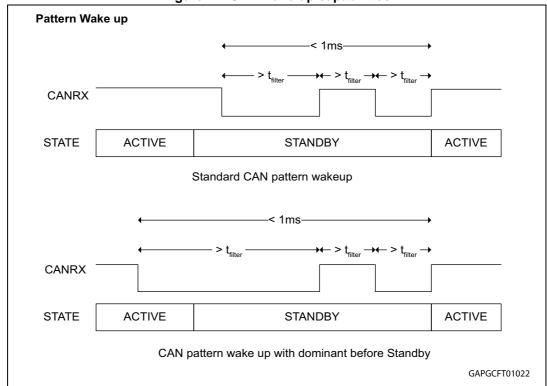

|   |            | 2.9.4                                                                                                         | Wake up by CAN                                                                                                                                                                                                                                                           | 38                                                 |

|   |            | 2.9.5                                                                                                         | CAN receive only mode                                                                                                                                                                                                                                                    | 40                                                 |

|   |            | 2.9.6                                                                                                         | CAN looping mode                                                                                                                                                                                                                                                         | 40                                                 |

|   | 2.10       | Serial I                                                                                                      | Peripheral Interface (ST SPI Standard 3.0)                                                                                                                                                                                                                               | 40                                                 |

| 3 | Prote      | ection a                                                                                                      | and diagnosis                                                                                                                                                                                                                                                            | 42                                                 |

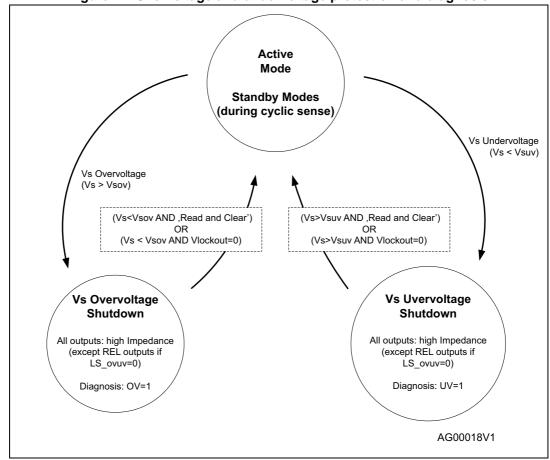

|   | 3.1        | Power                                                                                                         | supply fail                                                                                                                                                                                                                                                              | 42                                                 |

|   |            | 3.1.1                                                                                                         | V <sub>S</sub> overvoltage                                                                                                                                                                                                                                               | 42                                                 |

|   |            | 3.1.2                                                                                                         | V <sub>S</sub> undervoltage                                                                                                                                                                                                                                              | 42                                                 |

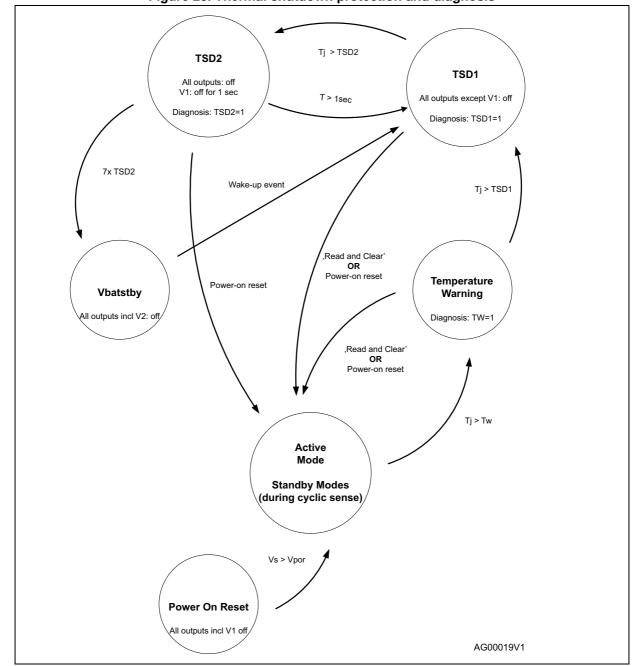

|   | 3.2        | Tempe                                                                                                         | erature warning and thermal shut-down                                                                                                                                                                                                                                    | 44                                                 |

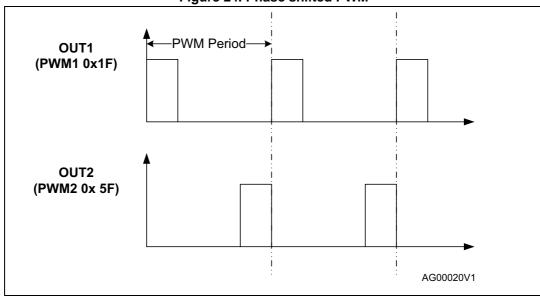

|   | 3.3        | High si                                                                                                       | ide driver outputs                                                                                                                                                                                                                                                       | 45                                                 |

|   | 3.4        | _                                                                                                             | de driver outputs REL1, REL2                                                                                                                                                                                                                                             |                                                    |

|   | 3.5        |                                                                                                               | agnosis                                                                                                                                                                                                                                                                  |                                                    |

|   |            |                                                                                                               |                                                                                                                                                                                                                                                                          | 4.0                                                |

| 4 | Туріс      | al appl                                                                                                       | lication                                                                                                                                                                                                                                                                 | 48                                                 |

| 5 | Elect      | rical sp                                                                                                      | pecifications                                                                                                                                                                                                                                                            | 49                                                 |

|   | 5.1        | Absolu                                                                                                        | ıte maximum ratings                                                                                                                                                                                                                                                      | 49                                                 |

|   |            |                                                                                                               |                                                                                                                                                                                                                                                                          | F0                                                 |

|   | 5.2        | ESD p                                                                                                         | rotection                                                                                                                                                                                                                                                                | 50                                                 |

|   | 5.2<br>5.3 | •                                                                                                             | al data                                                                                                                                                                                                                                                                  |                                                    |

|   |            | Therm                                                                                                         |                                                                                                                                                                                                                                                                          | 50                                                 |

|   | 5.3        | Therm                                                                                                         | al data                                                                                                                                                                                                                                                                  | 50<br>52                                           |

|   | 5.3        | Therma<br>Packag<br>5.4.1                                                                                     | al datage and PCB thermal data                                                                                                                                                                                                                                           | 50<br>52                                           |

|   | 5.3<br>5.4 | Therma<br>Packag<br>5.4.1                                                                                     | al data ge and PCB thermal data PowerSSO-36 thermal data                                                                                                                                                                                                                 | 50<br>52<br>52                                     |

|   | 5.3<br>5.4 | Therma<br>Packaç<br>5.4.1<br>Electric                                                                         | al data  ge and PCB thermal data  PowerSSO-36 thermal data  cal characteristics                                                                                                                                                                                          | 50<br>52<br>52<br>55                               |

|   | 5.3<br>5.4 | Therma<br>Packag<br>5.4.1<br>Electric<br>5.5.1                                                                | al data                                                                                                                                                                                                                                                                  | 50<br>52<br>52<br>55<br>56                         |

|   | 5.3<br>5.4 | Therma<br>Packag<br>5.4.1<br>Electric<br>5.5.1<br>5.5.2                                                       | al data                                                                                                                                                                                                                                                                  | 50<br>52<br>55<br>55<br>56                         |

|   | 5.3<br>5.4 | Therma<br>Packag<br>5.4.1<br>Electric<br>5.5.1<br>5.5.2<br>5.5.3                                              | al data  ge and PCB thermal data  PowerSSO-36 thermal data  cal characteristics  Supply and supply monitoring  Oscillator  Power-on reset (V <sub>S</sub> )                                                                                                              | 50<br>52<br>55<br>55<br>56                         |

|   | 5.3<br>5.4 | Therma<br>Packag<br>5.4.1<br>Electric<br>5.5.1<br>5.5.2<br>5.5.3<br>5.5.4                                     | al data  ge and PCB thermal data  PowerSSO-36 thermal data  cal characteristics  Supply and supply monitoring  Oscillator  Power-on reset (V <sub>S</sub> )  Voltage regulator V <sub>1</sub>                                                                            | 50<br>52<br>55<br>55<br>56<br>56                   |

|   | 5.3<br>5.4 | Therma<br>Packag<br>5.4.1<br>Electric<br>5.5.1<br>5.5.2<br>5.5.3<br>5.5.4<br>5.5.5                            | al data  ge and PCB thermal data  PowerSSO-36 thermal data  cal characteristics  Supply and supply monitoring  Oscillator  Power-on reset (V <sub>S</sub> )  Voltage regulator V <sub>1</sub> Voltage regulator V <sub>2</sub>                                           | 50<br>52<br>55<br>56<br>56<br>56<br>57             |

|   | 5.3<br>5.4 | Therma<br>Packag<br>5.4.1<br>Electric<br>5.5.1<br>5.5.2<br>5.5.3<br>5.5.4<br>5.5.5<br>5.5.6                   | al data  ge and PCB thermal data  PowerSSO-36 thermal data  cal characteristics  Supply and supply monitoring  Oscillator  Power-on reset (V <sub>S</sub> )  Voltage regulator V <sub>1</sub> Voltage regulator V <sub>2</sub> Reset output                              | 50<br>52<br>55<br>56<br>56<br>56<br>57<br>58       |

|   | 5.3<br>5.4 | Therma<br>Packag<br>5.4.1<br>Electric<br>5.5.1<br>5.5.2<br>5.5.3<br>5.5.4<br>5.5.5<br>5.5.6<br>5.5.7          | al data  ge and PCB thermal data  PowerSSO-36 thermal data  cal characteristics  Supply and supply monitoring  Oscillator  Power-on reset (V <sub>S</sub> )  Voltage regulator V <sub>1</sub> Voltage regulator V <sub>2</sub> Reset output  Watchdog                    | 50<br>52<br>55<br>56<br>56<br>56<br>57<br>58<br>58 |

|   | 5.3<br>5.4 | Therma<br>Packag<br>5.4.1<br>Electric<br>5.5.1<br>5.5.2<br>5.5.3<br>5.5.4<br>5.5.5<br>5.5.6<br>5.5.7<br>5.5.8 | al data  ge and PCB thermal data  PowerSSO-36 thermal data  cal characteristics  Supply and supply monitoring  Oscillator  Power-on reset (V <sub>S</sub> )  Voltage regulator V <sub>1</sub> Voltage regulator V <sub>2</sub> Reset output  Watchdog  High side outputs | 50<br>52<br>55<br>56<br>56<br>57<br>58<br>58<br>60 |

|   |       | 5.5.11                               | High speed CAN transceiver                                                                                                                                                           |

|---|-------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |       | 5.5.12                               | LIN transceiver                                                                                                                                                                      |

|   |       | 5.5.13                               | Operational amplifier                                                                                                                                                                |

|   |       | 5.5.14                               | SPI71                                                                                                                                                                                |

|   |       | 5.5.15                               | Inputs TxDC and TxDL for Flash Mode                                                                                                                                                  |

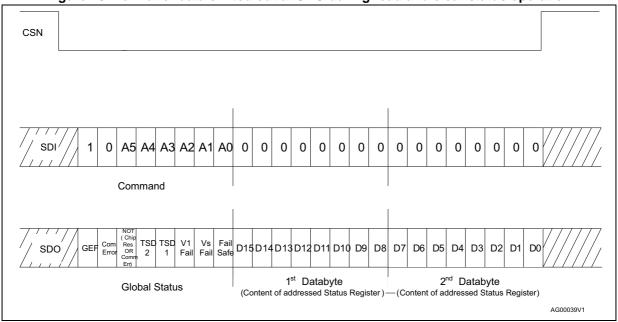

| 6 | ST SF | ગ                                    |                                                                                                                                                                                      |

|   | 6.1   | SPI com                              | nmunication flow                                                                                                                                                                     |

|   |       | 6.1.1                                | General description                                                                                                                                                                  |

|   |       | 6.1.2                                | Operating code definition                                                                                                                                                            |

|   |       | 6.1.3                                | Global Status Register                                                                                                                                                               |

|   |       | 6.1.4                                | Configuration register                                                                                                                                                               |

|   |       | 6.1.5                                | Address mapping                                                                                                                                                                      |

|   |       | 6.1.6                                | Write operation                                                                                                                                                                      |

|   |       | 6.1.7                                | Format of data shifted out at SDO during Write cycle                                                                                                                                 |

|   |       | 6.1.8                                | Read operation82                                                                                                                                                                     |

|   |       | 6.1.9                                | Format of data shifted out at SDO during Read cycle                                                                                                                                  |

|   |       | 6.1.10                               | Read and Clear Status Operation84                                                                                                                                                    |

|   |       | 6.1.11                               | Read device information85                                                                                                                                                            |

|   | 6.2   | SPI regi                             | sters                                                                                                                                                                                |

|   |       | 6.2.1                                | Overview command byte                                                                                                                                                                |

|   |       | 6.2.2                                | Overview control register                                                                                                                                                            |

|   |       | 6.2.3                                | Control Register 1                                                                                                                                                                   |

|   |       | 6.2.4                                | Control Register 2                                                                                                                                                                   |

|   |       | 6.2.5                                | Control Register 396                                                                                                                                                                 |

|   |       | 6.2.6                                | Control Register 4                                                                                                                                                                   |

|   |       | 6.2.7                                | Control Register 5                                                                                                                                                                   |

|   |       | 6.2.8                                | Control Register 6                                                                                                                                                                   |

|   |       | 6.2.9                                | Control Register 7                                                                                                                                                                   |

|   |       | 6.2.10                               | Control Register 8                                                                                                                                                                   |

|   |       |                                      |                                                                                                                                                                                      |

|   |       | 6.2.11                               | Control Register 9                                                                                                                                                                   |

|   |       | 6.2.11<br>6.2.12                     | -                                                                                                                                                                                    |

|   |       |                                      | Control Register 9                                                                                                                                                                   |

|   |       | 6.2.12                               | Control Register 9                                                                                                                                                                   |

|   |       | 6.2.12<br>6.2.13                     | Control Register 9       107         Control Register 10       108         Control Register 11       108                                                                             |

|   |       | 6.2.12<br>6.2.13<br>6.2.14           | Control Register 9       107         Control Register 10       108         Control Register 11       108         Control Register 12       109                                       |

|   |       | 6.2.12<br>6.2.13<br>6.2.14<br>6.2.15 | Control Register 9       107         Control Register 10       108         Control Register 11       108         Control Register 12       109         Control Register 13       109 |

| R | Revi | sion his | story                    | 128 |

|---|------|----------|--------------------------|-----|

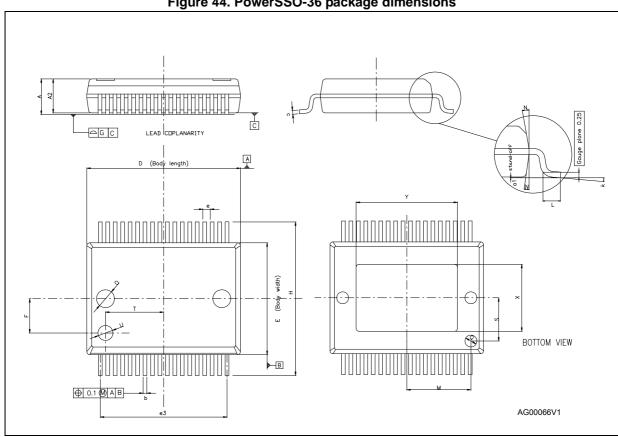

|   | 7.2  | Powers   | SSO-36 mechanical data   | 126 |

|   | 7.1  | ECOPA    | ACK <sup>®</sup>         | 126 |

| 7 | Pack | J        | ormation                 |     |

|   |      |          |                          |     |

|   |      | 6.2.27   | Status Register 5        | 125 |

|   |      | 6.2.26   | Status Register 4        | 123 |

|   |      | 6.2.25   | Status Register 3        | 121 |

|   |      | 6.2.24   | Status Register 2        | 120 |

|   |      | 6.2.23   | Status Register 1        | 118 |

|   |      | 6.2.22   | Global status register   | 117 |

|   |      | 6.2.21   | Overview status register | 116 |

|   |      | 6.2.20   | Control Register 35      | 115 |

|   |      | 6.2.19   | Control Register 34      | 114 |

|   |      | 6.2.18   | Control Register 16      | 112 |

|   |      |          |                          |     |

List of tables L99PM72GXP

## List of tables

| Table 1.  | Device summary                                   | . 1 |

|-----------|--------------------------------------------------|-----|

| Table 2.  | Pin definitions and functions                    | 11  |

| Table 3.  | CAN wake-up signalization                        | 19  |

| Table 4.  | Wake up from Standby Modes                       | 20  |

| Table 5.  | Functional overview (truth table)                | 22  |

| Table 6.  | Fail-Safe conditions and exit modes              | 29  |

| Table 7.  | Persisting fail safe conditions and exit modes   | 31  |

| Table 8.  | PWM configuration for high-side outputs          | 45  |

| Table 9.  | Absolute maximum ratings                         | 49  |

| Table 10. | ESD protection                                   | 50  |

| Table 11. | Operating junction temperature                   | 50  |

| Table 12. | Temperature warning and thermal shutdown         | 50  |

| Table 13. | Thermal parameter                                | 54  |

| Table 14. | Supply and supply monitoring                     |     |

| Table 15. | Oscillator                                       |     |

| Table 16. | Power-on reset (V <sub>S</sub> )                 |     |

| Table 17. | Voltage regulator V <sub>1</sub>                 | 56  |

| Table 18. | Voltage regulator V <sub>2</sub>                 | 57  |

| Table 19. | Reset output                                     |     |

| Table 20. | Watchdog                                         | 58  |

| Table 21. | Output (OUT_HS)                                  |     |

| Table 22. | Outputs (OUT14)                                  |     |

| Table 23. | Relay drivers                                    |     |

| Table 24. | Wake-up inputs                                   |     |

| Table 25. | CAN communication operating range                |     |

| Table 26. | CAN transmit data input: pin TxDC                | 62  |

| Table 27. | CAN receive data output: pin RxDC                |     |

| Table 28. | CAN transmitter and receiver: pins CANH and CANL |     |

| Table 29. | CAN transceiver timing                           |     |

| Table 30. | LIN transmit data input: pin TxD                 |     |

| Table 31. | LIN receive data output: pin RxD                 |     |

| Table 32. | LIN transmitter and receiver: pin LIN            |     |

| Table 33. | LIN transceiver timing                           |     |

| Table 34. | LIN pull-up: pin LINPU                           |     |

| Table 35. | Operational amplifier                            |     |

| Table 36. | Input: CSN                                       |     |

| Table 37. | Inputs: CLK, DI                                  |     |

| Table 38. | DI timing                                        |     |

| Table 39. | Output: DO                                       |     |

| Table 40. | DO timing                                        |     |

| Table 41. | CSN timing                                       |     |

| Table 42. | RXDL/NINT, RXDC/NINT timing                      |     |

| Table 43. | Inputs: TxDC and TxDL for Flash Mode             |     |

| Table 44. | Command Byte                                     |     |

| Table 45. | Operating code definition                        |     |

| Table 46. | Global status register                           |     |

| Table 47. | Configuration register                           |     |

| Table 48. | Address mapping                                  | 80  |

57

L99PM72GXP List of tables

| Table 49.              | Write command format: command byte                                                     |    |

|------------------------|----------------------------------------------------------------------------------------|----|

| Table 50.              | Write command format: data byte 1                                                      | 81 |

| Table 51.              | Write command format: data byte 2                                                      | 81 |

| Table 52.              | Format of data shifted out at SDO during write cycle: global status register           |    |

| Table 53.              | Format of data shifted out at SDO during write cycle: data byte 1                      |    |

| Table 54.              | Format of data shifted out at SDO during write cycle: data byte 2                      |    |

| Table 55.              | Read command format: command byte                                                      |    |

| Table 56.              | Read command format: data byte 1                                                       |    |

| Table 57.              | Read command format: data byte 2                                                       |    |

| Table 58.              | Format of data shifted out at SDO during read cycle: global status register            |    |

| Table 59.              | Format of data shifted out at SDO during read cycle: data byte 1                       |    |

| Table 60.              | Format of data shifted out at SDO during read cycle: data byte 2                       |    |

| Table 61.              | Read and clear status command format: command byte                                     |    |

| Table 62.              | Read and clear status command format: data byte 1                                      |    |

| Table 63.              | Read and clear status command format: data byte 2                                      |    |

| Table 64.              | Format of data shifted out at SDO during read and clear status: global status register |    |

| Table 65.              | Format of data shifted out at SDO during read and clear status: data byte 1            |    |

| Table 66.              | Format of data shifted out at SDO during read and clear status: data byte 2            |    |

| Table 67.              | Read device information                                                                |    |

| Table 68.              | ID-header                                                                              |    |

| Table 69.              | Family identifier                                                                      |    |

| Table 70.              | Silicon version identifier                                                             |    |

| Table 71.              | SPI-frame-ID                                                                           |    |

| Table 72.              | SPI register: command byte                                                             |    |

| Table 73.              | SPI register: mode selection                                                           |    |

| Table 74.              | SPI register: CTRL register selection                                                  |    |

| Table 75.              | SPI register: STAT register selection                                                  |    |

| Table 76.              | Overview of control register data bytes                                                |    |

| Table 77.              | Control register 1: command and data bytes                                             |    |

| Table 78.              | Control register 1, data bytes                                                         |    |

| Table 79.              | Control register 1, bits                                                               |    |

| Table 80.              | Control register 2: command and data bytes                                             |    |

| Table 81.              | Control register 2, data bytes                                                         |    |

| Table 82.              | Control register 2, bits                                                               |    |

| Table 83.              | Control register 3: command and data bytes                                             |    |

| Table 84.              | Control register 3, data bytes                                                         |    |

| Table 85.<br>Table 86. | Control register 3, bits                                                               |    |

| Table 87.              |                                                                                        |    |

| Table 87.              | Control register 4, data bytes                                                         |    |

| Table 89.              | Control register 5: command and data bytes                                             |    |

| Table 99.              | Control register 5, data bytes                                                         |    |

| Table 90.              | Control register 5, bits                                                               |    |

| Table 92.              | Control register 6: command and data bytes                                             |    |

| Table 93.              | Control register 6, data bytes                                                         |    |

| Table 94.              | Control register 6, bits                                                               |    |

| Table 95.              | Control register 7: command and data bytes                                             |    |

| Table 95.              | Control register 7, data bytes                                                         |    |

| Table 97.              | Control register 7, bits                                                               |    |

| Table 98.              | Control register 8: command and data bytes                                             |    |

| Table 99.              | Control register 8, data bytes                                                         |    |

| Table 100.             | Control register 8, bits                                                               |    |

|                        |                                                                                        |    |

DocID024767 Rev 4

7/129

List of tables L99PM72GXP

| Table 101. | Control register 9: command and data bytes  |       |

|------------|---------------------------------------------|-------|

| Table 102. | Control register 9, data bytes              |       |

| Table 103. | Control register 9, bits                    |       |

| Table 104. | Control register 10: command and data bytes | . 108 |

| Table 105. | Control register 10, data bytes             |       |

| Table 106. | Control register 10, bits                   | . 108 |

| Table 107. | Control register 11: command and data bytes | . 108 |

| Table 108. | Control register 11, data bytes             | . 108 |

| Table 109. | Control register 11, bits                   | . 108 |

| Table 110. | Control register 12: command and data bytes | . 109 |

| Table 111. | Control register 12, data bytes             | . 109 |

| Table 112. | Control register 12, bits                   | . 109 |

| Table 113. | Control register 13: command and data bytes | . 109 |

| Table 114. | Control register 13, data bytes             | . 109 |

| Table 115. | Control register 13, bits                   | . 109 |

| Table 116. | Control register 14: command and data bytes | . 110 |

| Table 117. | Control register 14, data bytes             | . 110 |

| Table 118. | Control register 14, bits                   |       |

| Table 119. | Control register 15: command and data bytes | . 111 |

| Table 120. | Control register 15, data bytes             |       |

| Table 121. | Control register 15, bits                   |       |

| Table 122. | Control register 16: command and data bytes |       |

| Table 123. | Control register 16, data bytes             |       |

| Table 124. | Control register 16, bits                   |       |

| Table 125. | Control register 34: command and data bytes |       |

| Table 126. | Control register 34, data bytes             |       |

| Table 127. | Control register 34, bits                   |       |

| Table 128. | Control register 35: command and data bytes |       |

| Table 129. | Control register 35, data bytes             |       |

| Table 130. | Control register 35, bits                   |       |

| Table 131. | Overview of status register data bytes      |       |

| Table 132. | Global status register                      |       |

| Table 133. | Status register 1: command and data bytes   | . 118 |

| Table 134. | Status register 1, data bytes               |       |

| Table 135. | Status register 1, bits                     |       |

| Table 136. | Status register 2: command and data bytes   |       |

| Table 137. | Status register 2, data bytes               | . 120 |

| Table 138. | Status register 2, bits                     | . 120 |

| Table 139. | Status register 3: command and data bytes   | . 121 |

| Table 140. | Status register 3, data bytes               | . 121 |

| Table 141. | Status register 3, bits                     | . 121 |

| Table 142. | Status register 4: command and data bytes   |       |

| Table 143. | Status register 4, data bytes               | . 123 |

| Table 144. | Status register 4, bits                     | . 123 |

| Table 145. | Status register 5: command and data bytes   | . 125 |

| Table 146. | Status register 5, data bytes               | . 125 |

| Table 147. | Status register 5, bits                     | . 125 |

| Table 148. | PowerSSO-36 mechanical data                 | . 127 |

| Table 149. | Document revision history                   | . 128 |

L99PM72GXP List of figures

## List of figures

| Figure 1.  | Block diagram                                                                             | 10 |

|------------|-------------------------------------------------------------------------------------------|----|

| Figure 2.  | Pin connection (top view)                                                                 |    |

| Figure 3.  | Voltage source with external PNP                                                          |    |

| Figure 4.  | Voltage source with external PNP and current limitation                                   | 14 |

| Figure 5.  | Voltage source with external NPN                                                          |    |

| Figure 6.  | Voltage source with external NPN and current limitation                                   |    |

| Figure 7.  | Voltage regulator behaviour and diagnosis during supply voltage ramp-up / ramp-down       |    |

| J          | conditions                                                                                | 17 |

| Figure 8.  | Sequence to enter and exit SW Debug Mode                                                  |    |

| Figure 9.  | Main operating modes                                                                      |    |

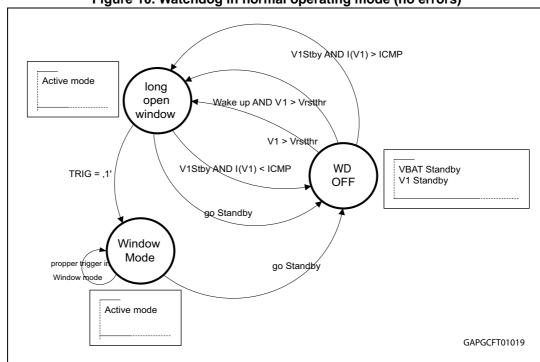

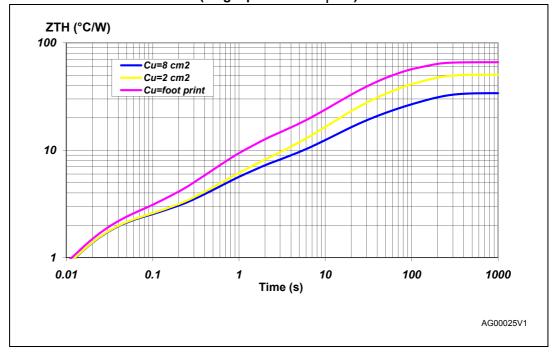

| Figure 10. | Watchdog in normal operating mode (no errors)                                             |    |

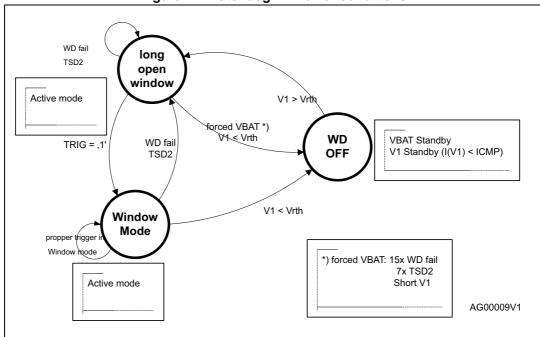

| Figure 11. | Watchdog with error conditions                                                            |    |

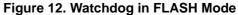

| Figure 12. | Watchdog in FLASH Mode                                                                    |    |

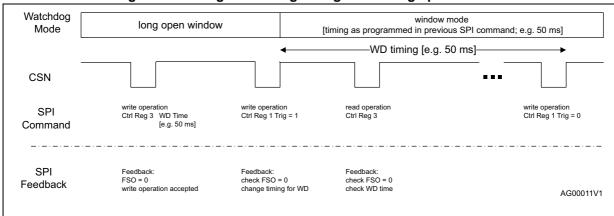

| Figure 13. | Change watchdog timing within long open window                                            |    |

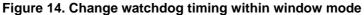

| Figure 14. | Change watchdog timing within window mode                                                 |    |

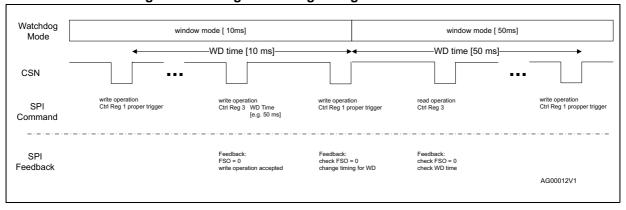

| Figure 15. | General procedure to change watchdog timing out of Fail safe mode                         |    |

| Figure 16. | Change watchdog timing out of Fail safe mode (Watchdog failure)                           |    |

| Figure 17. | Example: exit Fail-Safe mode from Watchdog failure                                        |    |

| Figure 18. | Master node configuration using LIN_PU (optional)                                         |    |

| Figure 19. | Transceiver state diagram if selective wake-up is disabled (CR16 SW_EN = 0)               |    |

| Figure 20. | CAN transceiver state diagram if selective wake-up is enabled (CR16 SW_EN = 1)            |    |

| Figure 21. | CAN wake up capabilities                                                                  |    |

| Figure 22. | Overvoltage and undervoltage protection and diagnosis                                     | 43 |

| Figure 23. | Thermal shutdown protection and diagnosis                                                 | 44 |

| Figure 24. | Phase shifted PWM                                                                         | 46 |

| Figure 25. | Typical application diagram                                                               | 48 |

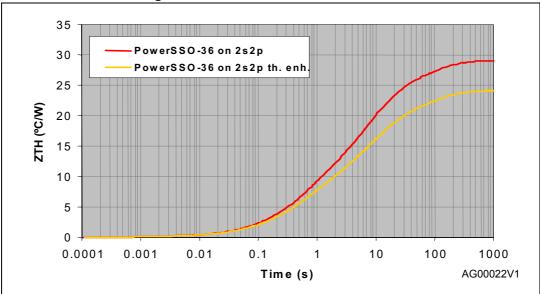

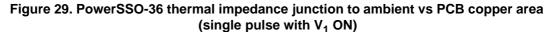

| Figure 26. | Thermal data of PowerSSO-36                                                               | 51 |

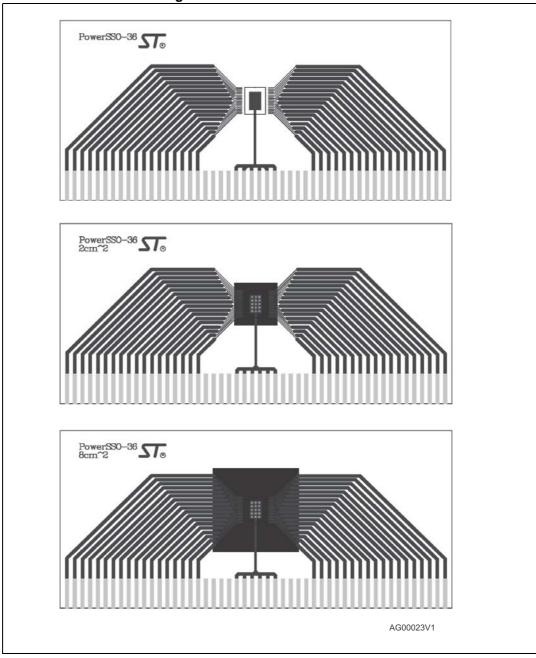

| Figure 27. | PowerSSO-36 PC board                                                                      |    |

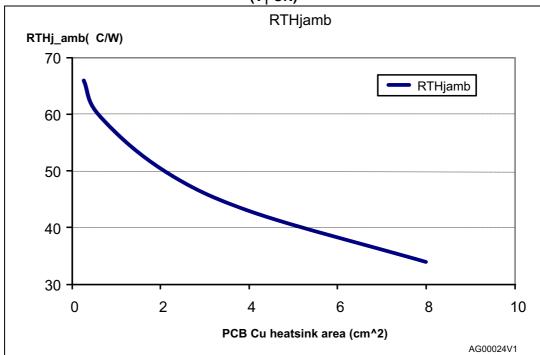

| Figure 28. | PowerSSO-36 thermal resistance junction to ambient vs PCB copper area (V <sub>1</sub> ON) | 53 |

| Figure 29. | PowerSSO-36 thermal impedance junction to ambient vs PCB copper area (single pulse        |    |

|            | with $V_1$ ON)                                                                            |    |

| Figure 30. | PowerSSO-36 thermal fitting model (V <sub>1</sub> ON)                                     |    |

| Figure 31. | Watchdog timing (long, early, late and safe window)                                       |    |

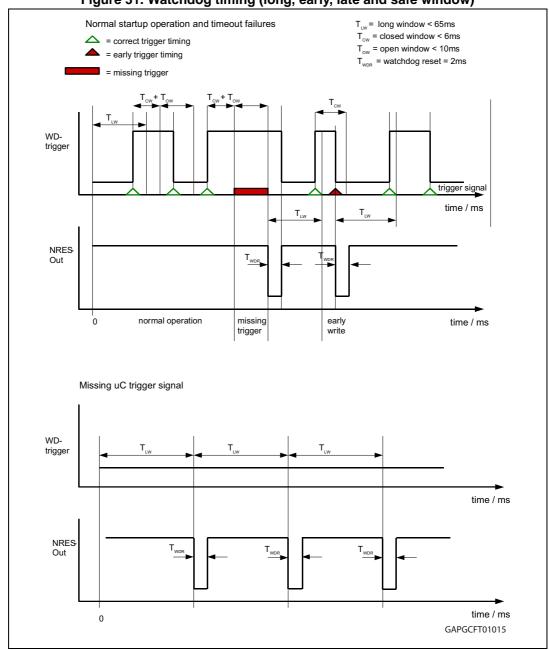

| Figure 32. | Watchdog early, late and safe windows                                                     |    |

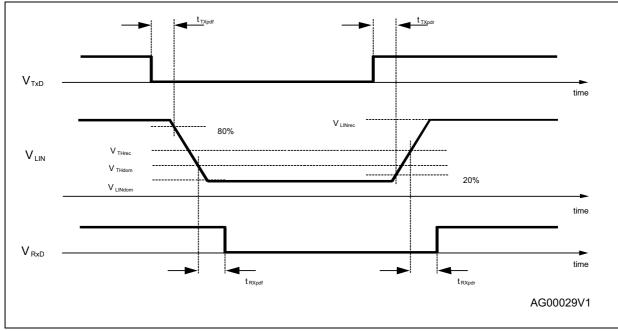

| Figure 33. | LIN transmit, receive timing                                                              |    |

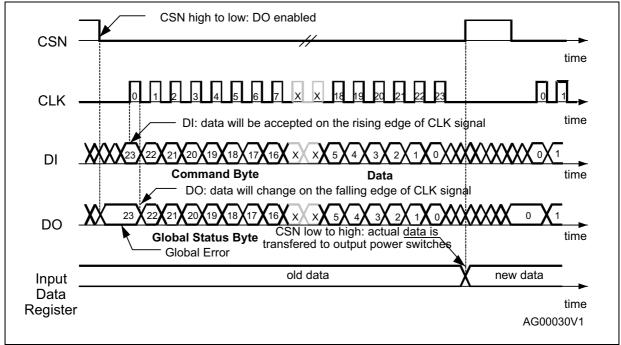

| Figure 34. | SPI - transfer timing diagram                                                             |    |

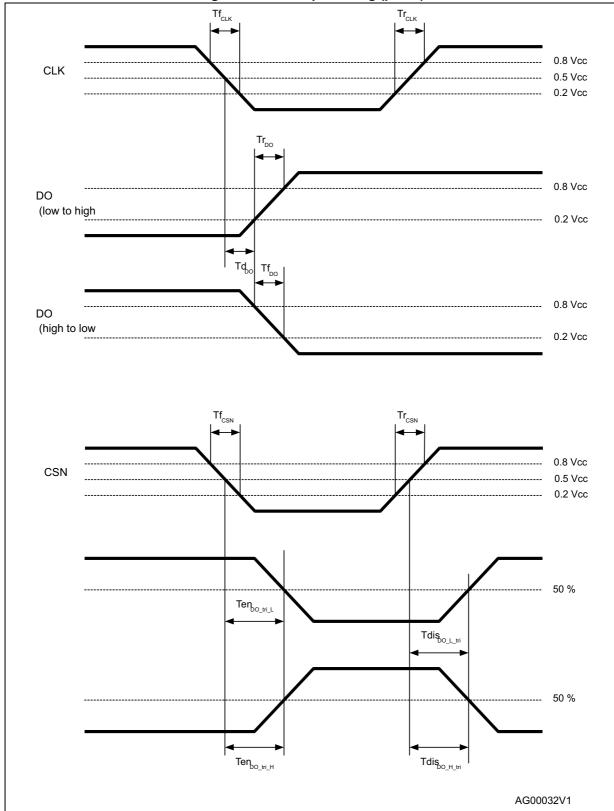

| Figure 35. | SPI input timing                                                                          |    |

| Figure 36. | SPI output timing (part 1)                                                                |    |

| Figure 37. | SPI CSN - output timing                                                                   |    |

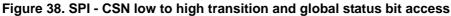

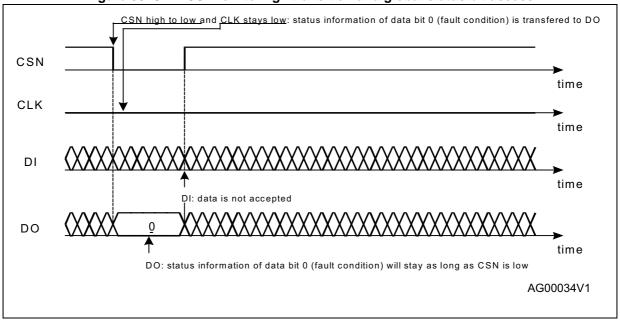

| Figure 38. | SPI - CSN low to high transition and global status bit access                             |    |

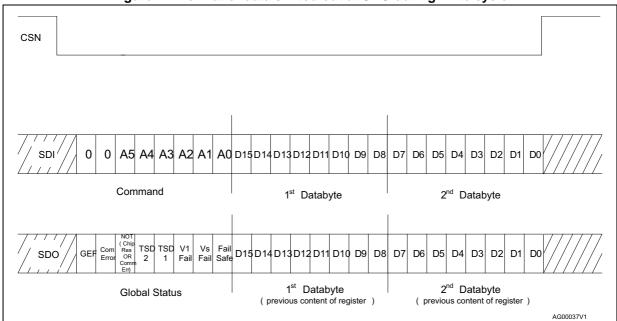

| Figure 39. | Read configuration register                                                               |    |

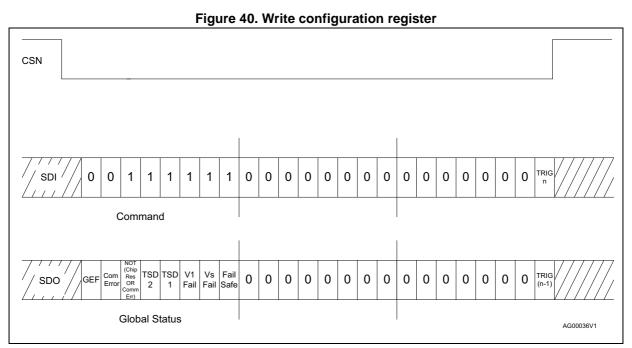

| Figure 40. | Write configuration register                                                              |    |

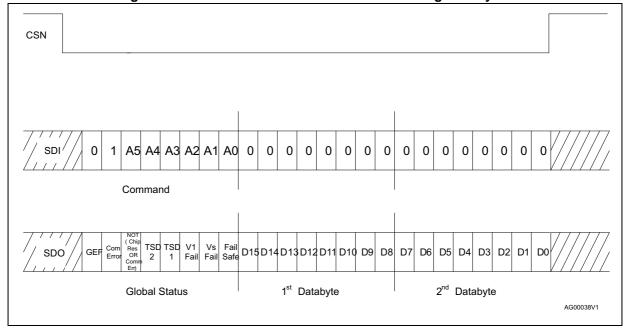

| Figure 41. | Format of data shifted out at SDO during write cycle                                      |    |

| Figure 42. | Format of data shifted out at SDO during read cycle                                       |    |

| Figure 43. | Format of data shifted out at SDO during read and clear status operation                  |    |

| Figure 44. | PowerSSO-36 package dimensions                                                            | 26 |

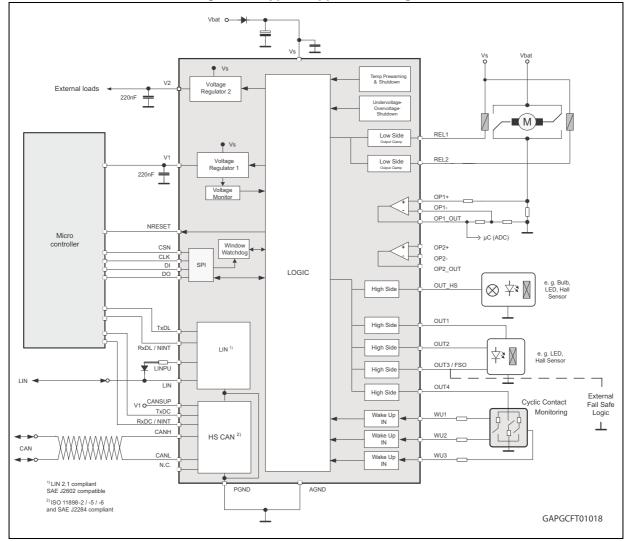

## 1 Block diagram and pin description

Figure 1. Block diagram

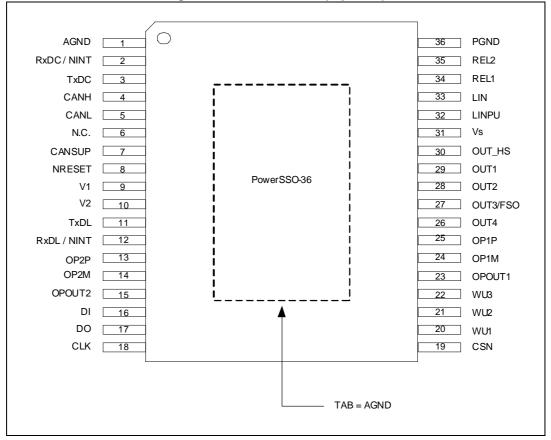

Table 2. Pin definitions and functions

| Pin  | Symbol    | Function                                                                                                                                                                |

|------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | AGND      | Analog ground                                                                                                                                                           |

| 2    | RxDC/NINT | RxDC -> CAN receive data output NINT -> indicates remote CAN wake-up events in Active Mode (transceiver in TRX_STBY; CAN_ACT = 0)                                       |

| 3    | TxDC      | CAN transmit data Input                                                                                                                                                 |

| 4    | CANH      | CAN high level voltage I/O                                                                                                                                              |

| 5    | CANL      | CAN low level voltage I/O                                                                                                                                               |

| 6    | N.C.      | TBC                                                                                                                                                                     |

| 7    | CANSUP    | CAN supply input; to allow external CAN supply from $V_1$ or $V_2$ regulator.                                                                                           |

| 8    | NRESET    | NRESET output to microcontroller; Internal pull-up of typ. 100 K $\Omega$ (reset state = LOW)                                                                           |

| 9    | V1        | Voltage regulator 1 output: 5 V supply e.g. micro controller, CAN transceiver                                                                                           |

| 10   | V2        | Voltage regulator 2 output: 5 V supply for external loads (IR receiver, potentiometer, sensors) or CAN transceiver. V <sub>2</sub> is protected against reverse supply. |

| 11   | TxDL      | LIN transmit data input                                                                                                                                                 |

| 12   | RxDL/NINT | RxDL -> LIN receive data output NINT -> indicates local/remote wake-up events except CAN wake-up in Active Mode provides a programmable timer interrupt signal          |

| 13   | OP2+      | Non inverting input of operational amplifier 2                                                                                                                          |

| 14   | OP2-      | Inverting input of operational amplifier 2                                                                                                                              |

| 15   | OP2_OUT   | Output of operational amplifier 2                                                                                                                                       |

| 16   | DI        | SPI: serial data input                                                                                                                                                  |

| 17   | DO        | SPI: serial data output                                                                                                                                                 |

| 18   | CLK       | SPI: serial clock input                                                                                                                                                 |

| 19   | CSN       | SPI: chip select not input                                                                                                                                              |

| 2022 | WU13      | Wake-up Inputs 13: Input pins for static or cyclic monitoring of external contacts                                                                                      |

| 23   | OP1_OUT   | Output of operational amplifier 1                                                                                                                                       |

| 24   | OP1-      | Inverting input of operational amplifier 1                                                                                                                              |

| 25   | OP1+      | Non inverting input of operational amplifier 1                                                                                                                          |

| 26   | OUT4      | High side driver output (7 $\Omega$ , typ)                                                                                                                              |

| 27   | OUT3/FSO  | Configurable as:  - High-side driver output (7Ω, typ)  - Fail safe output pin (default)                                                                                 |

| 28   | OUT2      | High side driver output (7 $\Omega$ , typ)                                                                                                                              |

| 29   | OUT1      | High side driver output (7 $\Omega$ , typ)                                                                                                                              |

| 30   | OUT_HS    | High side driver (1 $\Omega$ , typ)                                                                                                                                     |

DocID024767 Rev 4

11/129

Table 2. Pin definitions and functions (continued)

| Pin | Symbol | Function                                                                   |  |  |  |

|-----|--------|----------------------------------------------------------------------------|--|--|--|

| 31  | Vs     | Power supply voltage                                                       |  |  |  |

| 32  | LINPU  | High side driver output to switch off LIN master pull up resistor          |  |  |  |

| 33  | LIN    | LIN bus line                                                               |  |  |  |

| 34  | REL1   | Low side driver output (2 $\Omega$ typ)                                    |  |  |  |

| 35  | REL2   | Low side driver output (2 $\Omega$ typ)                                    |  |  |  |

| 36  | PGND   | Power ground (REL1/2, LIN and CAN GND), to be connected to AGND externally |  |  |  |

Figure 2. Pin connection (top view)

57

## 2 Detailed description

### 2.1 Voltage regulators

The L99PM72GXP contains two independent and fully protected low drop voltage regulators, which are designed for very fast transient response and do not require electrolytic output capacitors for stability.

The output voltage is stable with ceramic load capacitors ≥ 220 nF.

#### 2.1.1 Voltage regulator: V<sub>1</sub>

The  $V_1$  voltage regulator provides 5 V supply voltage and up to 250 mA continuous load current and is mainly intended for supply of the system microcontroller. The  $V_1$  regulator is embedded in the power management and Fail\_safe functionality of the device and operates according to the selected operating mode.

It can be used to supply the internal HS CAN Transceiver via the CANSUP pin externally. In case of a short circuit condition on the CAN bus, the output current of the transmitter is limited to 100 mA and the transceiver is turned off in order to ensure continued supply of the microcontroller.

In addition the regulator  $V_1$  drives the L99PM72GXP internal 5 V loads. The voltage regulator is protected against overload and overtemperature. An external reverse current protection has to be provided by the application circuitry to prevent the input capacitor from being discharged by negative transients or low input voltage. Current limitation of the regulator ensures fast charge of external bypass capacitors. The output voltage is stable for ceramic load capacitors  $\geq$  220 nF.

If the device temperature exceeds the TSD1 threshold, all outputs (OUTx, RELx, V2, LIN) are deactivated except  $V_1$ . Hence the micro controller has the possibility for interaction or error logging. In case of exceeding TSD2 threshold (TSD2 > TSD1), also  $V_1$  is deactivated (see *Figure 23: Thermal shutdown protection and diagnosis*). A timer is started and the voltage regulator is deactivated for  $t_{TSD} = 1$  sec. During this time, all other wakeup sources (CAN, LIN, WU1...3 and wake up of  $\mu$ C by timer) are disabled. After 1 sec, the voltage regulator tries to restart automatically. If the restart fails 7 times, within one minute, without clearing and thermal shutdown condition still exists, the L99PM72GXP enters the Forced  $V_{Bat\ standby}$  Mode.

In case of short to GND at " $V_1$ " after initial turn on ( $V_1 < 2 \text{ V}$  for  $t > t_{V1 \text{ short}}$ ) the L99PM72GXP enters the Forced  $V_{Bat\_standby}$  Mode. Reactivation (wake-up) of the device can be achieved with signals from CAN, LIN, WU1..3 or periodic wake by timer.

### 2.1.2 Voltage regulator: V<sub>2</sub>

The voltage regulator  $V_2$  can supply additional 5 V loads (e.g. logic components or the integrated HS CAN transceiver or external loads such as sensors or potentiometers. The maximum continuous load current is 100 mA. The regulator is protected against:

- Overload

- Overtemperature

- Short circuit (short to ground and battery supply voltage)

- Reverse biasing

DocID024767 Rev 4 13/129

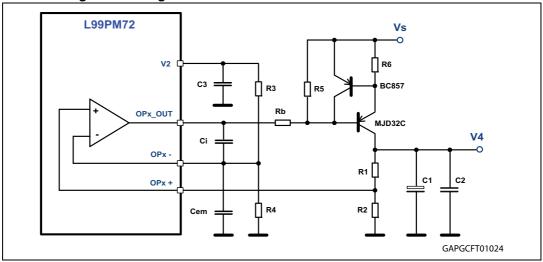

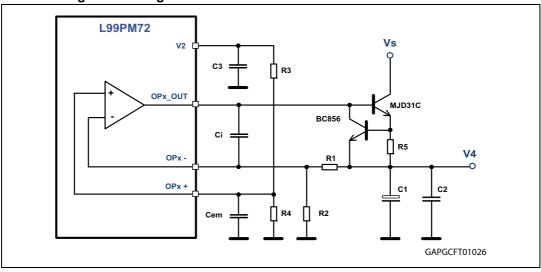

## 2.1.3 Increased output current capability for voltage regulator V<sub>2</sub>

For applications, which require high output currents, the output current capability of the regulator can be increased my means of the integrated operational amplifiers and an external pass transistor.

L99PM72

Vs

OPX OPX OPX PR

OPX PR

OPX PR

OPX PR

GAPGCFT01023

Figure 3. Voltage source with external PNP

Figure 4. Voltage source with external PNP and current limitation

*Figure 3* shows a possible configuration with a PNP pass element using Voltage Regulator 2 to provide the voltage reference for the regulated output voltage V3.

The  $V_S$  operating range for this circuit is 5.5 V to 18 V. It is important respect the input common mode range specified for the operational amplifiers.

The output voltage V3 can be calculated using the following formula (for R3 = R4):

$$V_3 = \frac{V_2}{2} \cdot \frac{R_1 + R_2}{R_2} [V]$$

577

The circuit in *Figure 4* provides additional current limitation using an additional PNP transistor and R6, which allows setting the current limit.

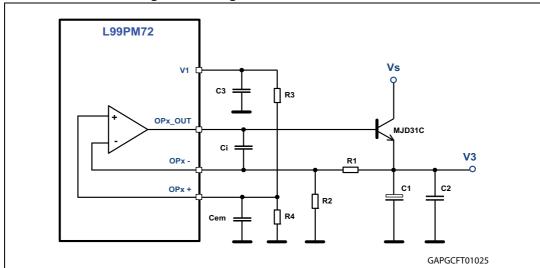

Figure 5. Voltage source with external NPN

Figure 6. Voltage source with external NPN and current limitation

Figure 5 shows a possible configuration with an NPN pass element using Voltage Regulator 2 to provide the voltage reference for the regulated output voltage V3. This circuit requires fewer components compared to the configuration in Figure 3 but has a limited  $V_S$  operating range (6 V to 18 V).

The output voltage V3 can be calculated using the following formula (for R3 = R4):

$$V_3 = \frac{V_2}{2} \cdot \frac{R_1 + R_2}{R_2} [V]$$

The circuit in *Figure 6* provides additional current limitation using an additional NPN transistor and R5 which allows setting the current limit.

577

DocID024767 Rev 4

Alternatively, Voltage Regulator 1 can be used to provide the 5 V reference for this topology. However, the additional current consumption through R3 and R4 has to be considered in  $V_{1\ standby}$  Mode.

#### 2.1.4 Voltage regulator failure

The V<sub>1</sub> and V<sub>2</sub> regulator output voltages are monitored.

In case of a drop below the  $V_1$ ,  $V_2$  - fail thresholds ( $V_{1,2}$  < 2 V, typ for t > 2  $\mu$ s), the  $V_{1,2}$  -fail bits are latched. The fail bits can be cleared by a dedicated SPI command.

#### Short to ground detection

If 4 ms after turn on of the regulator the  $V_{1,2}$  voltage is below the  $V_{1,2}$  fail thresholds, (independent for  $V_{1,2}$ ), the L99PM72GXP identifies a short circuit condition at the related regulator output and the regulator are switched off.

In case of  $V_1$  short to GND failure the device enters  $V_{Bat\_standby}$  mode automatically. Bits Forced VBAT TSD2/SHTV1 and  $V_1$  fail were set.

In case of a  $V_2$  short to GND failure the  $V_2$  short and  $V_2$  fail bit is set.

If the output voltage of the corresponding regulator once exceeded the  $V_{1,2\_fail}$  thresholds the short to ground detection is disabled. If a short to ground condition occurs the regulator outputs switch of due to Thermal shutdown ( $V_1$  at TSD2;  $V_2$  at TSD1).

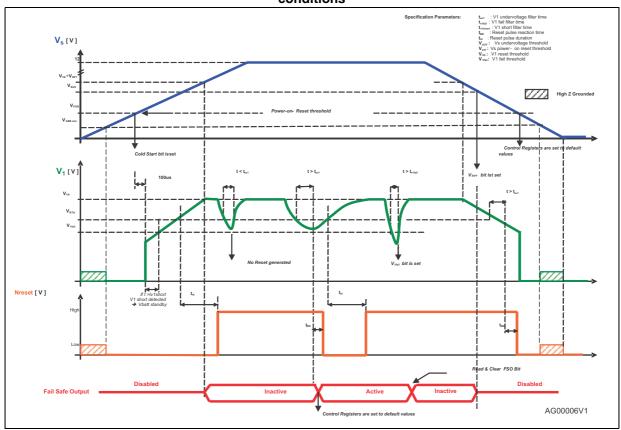

### 2.1.5 Voltage regulator behavior

Figure 7. Voltage regulator behaviour and diagnosis during supply voltage ramp-up / ramp-down conditions

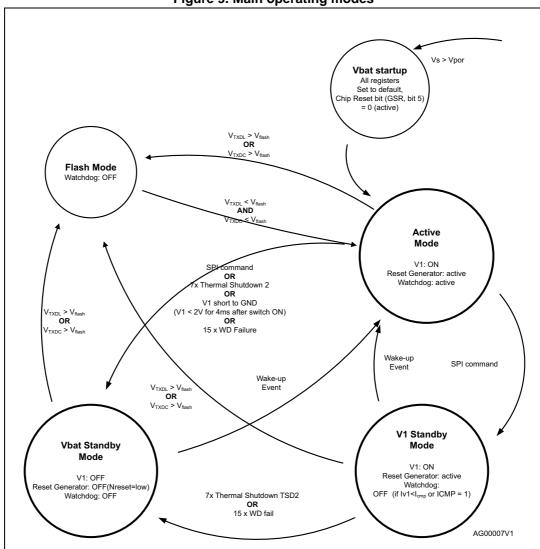

## 2.2 Operating modes

The L99PM72GXP can be operated in 4 different operating modes:

- Active

- FLASH

- V<sub>1\_standby</sub>

- V<sub>Bat\_standby</sub>

A cyclic monitoring of wake-up inputs and a periodic interrupt / wake-up by timer is available in standby modes.

#### 2.2.1 Active Mode

All functions are available and the device is controlled by the ST SPI Interface.

#### 2.2.2 Flash Mode

To program the system microcontroller via LIN or HS CAN bus signals, the device can be operated in LIN Flash Mode or CAN Flash Mode where the internal watchdog is disabled.

DocID024767 Rev 4 17/129

All other device features in Flash Mode are available as in Active Mode.

CAN Transmitter and CAN Receiver are enabled in CAN Flash Mode by default.

A transition from Flash Modes to V<sub>1</sub> standby or V<sub>bat</sub> standby is not possible.

The modes can be entered by applying an external voltage at the respective pin:

- V<sub>TxDL</sub> ≥ V<sub>flash</sub> (CAN Flash Mode)

- V<sub>TxDC</sub> ≥ V<sub>flash</sub> (LIN Flash Mode)

At exit from Flash Modes ( $V_{TxD} < V_{flash}$ ) no NRESET pulse is generated and the watchdog starts with a long open window.

Note:

Setting both TxDL and TxDC to high voltage levels ( $> V_{flash}$ ) is not allowed Communication at the respective TxD pin is not possible

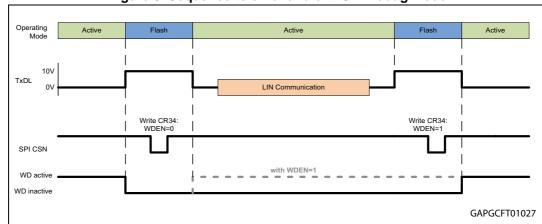

#### 2.2.3 SW-Debug Mode

To allow software debugging, the watchdog can be deactivated by setting CR34: WDEN = 0.

Write access to this bit is only possible during CAN Flash Mode in order to prevent accidental deactivation of the watchdog. After setting the WDEN bit the CAN Flash Mode can be left ( $V_{TxDL} < V_{Flash}$ ) and the Watchdog remains deactivated (see *Figure 8*)

In SW-Debug Mode, the full device functionality is available.

Figure 8. Sequence to enter and exit SW Debug Mode

## 2.2.4 V<sub>1\_standby</sub> mode

The transition from Active Mode to V<sub>1</sub> standby mode is controlled by SPI.

To supply the micro controller in a low power mode, the voltage regulator 1 ( $V_1$ ) remains active. In order to reduce the current consumption, the regulator goes in low current mode as soon as the supply current of the microcontroller goes below the  $I_{CMP}$  current threshold. At this transition, the L99PM72GXP also deactivates the internal watchdog.

Relay outputs, LIN and CAN Transmitters are switched off in  $V_{1\_standby}$  Mode. High side outputs and the  $V_{2}$  regulator remain in the configuration programmed prior to the standby command.

DocID024767 Rev 4

A cyclic supply of external contacts and a synchronized monitoring of the contact state can be activated and configured by SPI.

In  $V_{1\_standby}$  mode various wake-up sources can be individually programmed. Each wake-up event puts the device into Active Mode and forces the RxDL/NINT pin to a low level indicating the wake-up condition to the microcontroller.

After Power ON Reset (POR) all wake up sources are activated by default except the periodic interrupt / wake timer.

With the interrupt timer the micro controller can be forced from 'stop' to 'run' after a programmable period. The RxDL/NINT pin is forced low after the timer is elapsed. The L99PM72GXP enters active mode and is awaiting a valid watchdog trigger.

Both internal timers can be used for this feature.

The interrupt timer (TINT) at pin RxDL/NINT is only available in V<sub>1 standby</sub> mode.

Note:

Inputs TxDL, TxDC must be at recessive (high) level and CSN must be at high level or at high impedance in order to achieve minimum standby current in  $V_{1\_standby}$  Mode. Inputs DI and CLK must be at GND or at high impedance to achieve minimum standby current in  $V_{1\_standby}$  Mode.

#### 2.2.5 Interrupt

The interrupt signal (linked to RxDL/NINT) indicates a wake-up event from  $V_{1\_standby}$  mode. In case of a wake-up by Wake-up Inputs, activity on LIN or CAN, SPI access or Timer-Interrupt the RxDL/NINT pin is pulled low for  $t = t_{interrupt}$ .

If the CAN transceiver is deactivated during Active Mode (CAN\_ACT = 0), a WUP (SWEN = 0) or a WUF (SWEN = 1) generates an interrupt at RxDC/NINT to signalize CAN communication on the bus to the microcontroller.

In case of a CAN communication timeout an interrupt at RxDC /NINT is generated and the CAN TO flag is set.

In case of  $V_{1\_standby}$  mode and  $(I_{V1} > I_{CMP})$ , the device remains in standby mode, the  $V_{1}$  regulator switches to high current mode and the watchdog starts. No Interrupt signal is generated.

| Operating mode         | Event                     | Wake-up<br>transition to<br>active | Status flag                   | Interrupt | Transceiver state |

|------------------------|---------------------------|------------------------------------|-------------------------------|-----------|-------------------|

| Active                 | WUP or WUF <sup>(1)</sup> | Not applicable                     | Wake_CAN WUP<br>or<br>WUP/WUF | RxDC      | TRX_STBY          |

|                        | CAN timeout               |                                    | CAN_TO                        | RxDC      | TRX_STBY          |

| V <sub>1_standby</sub> | WUP or WUF <sup>(1)</sup> | Yes                                | Wake_CAN WUP<br>or<br>WUP/WUF | RxDL      | TRX_STBY          |

|                        | CAN timeout               | No                                 | CAN_TO                        | RxDC      | TRX_STBY          |

Table 3. CAN wake-up signalization

| Operating mode           | Event                            | Wake-up<br>transition to<br>active | Status flag         | Interrupt      | Transceiver state |

|--------------------------|----------------------------------|------------------------------------|---------------------|----------------|-------------------|

| V                        | WUP or<br>WUP/WUF <sup>(2)</sup> | Yes                                | Wake_CAN<br>WUP/WUF | Not applicable | TRX_STBY          |

| V <sub>bat_standby</sub> | CAN timeout                      | Transition to TRX_SLEEP            | CAN_TO              |                | TRX_SLEEP         |

Table 3. CAN wake-up signalization (continued)

- 1. SW\_EN = 0:

- wake-up according ISO 11898-5 (WUP)— Flags: Wake\_CAN, WUP

- SW\_EN = 1:

- wake-up according ISO 11898-6 (on WUP/WUF combination)

Flags: Wake\_CAN, WUP, WUF (the WUP flag is set only if the received WUF also contained a WUP)

- 2. SW EN = 0:

- wake-up according ISO 11898-5 (on WUP)— Flags: Wake\_CAN, WUP

- SW\_EN = 1:

- wake-up according ISO 11898-6 (on WUP/WUF combination)

After the reception of a wake-up pattern (WUP) the CAN Enhanced Voltage Biasing is turned on until a CAN timeout is detected

- Flags: Wake\_CAN, WUP, WUF

#### 2.2.6 V<sub>Bat standby</sub> mode

The transition from Active Mode to V<sub>Bat standby</sub> mode is initiated by an SPI command.

In  $V_{Bat\ standby}$  Mode, the  $V_1$  voltage regulator, relay outputs, LIN and CAN Transmitters are switched off. High side Outputs and the V<sub>2</sub> Regulator remain in the configuration programmed prior to the standby command.

In  $V_{Bat\_standby}$  mode the current consumption of the L99PM72GXP is reduced to a minimum level.

An NRESET pulse is generated upon wake-up from  $V_{\text{bat standby}}$  Mode.

Note:

Inputs TXDL, TXDC and CSN must be terminated to GND in  $V_{bat\_standby}$  to achieve minimum standby current.

This can be achieved with the internal ESD protection diodes of the microcontroller (microcontroller is not supplied in this mode;  $V_1$  is pulled to GND).

#### 2.2.7 Wake up from Standby Modes

A wake-up from standby mode switches the device to active mode. This can be initiated by one or more of the following events:

Table 4. Wake up from Standby Modes

| Wake up source          | Description                                                          |  |  |

|-------------------------|----------------------------------------------------------------------|--|--|

| LIN bus activity        | Can be disabled by SPI                                               |  |  |

| CAN bus activity        | Can be disabled by SPI<br>Selective Wake-up can be configured by SPI |  |  |

| Level change of WU1 - 3 | Can be individually configured or disabled by SPI                    |  |  |

| Wake up source                           | Description                                                                                                                                                                                                                                                                                                            |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I <sub>V1</sub> > I <sub>CMP</sub>       | Device remains in $V_{1\_standby}$ mode but watchdog is enabled (If $I_{CMP} = 0$ ) and the $V_1$ regulator goes into High Current Mode (Increased Current Consumption). No interrupt is generated.                                                                                                                    |

| Timer Interrupt / Wake up of μC by TIMER | programmable by SPI  - V <sub>1_standby</sub> Mode: device wakes up and Interrupt signal is generated at RxDL/NINT when programmable timeout has elapsed  - V <sub>Bat_standby</sub> Mode: device wakes up, V <sub>1</sub> regulator is turned on and NRESET signal is generated when programmable timeout has elapsed |

| SPI Access                               | Always active (except in V <sub>Bat_standby</sub> mode)  Wake up event: CSN is low and first rising edge on CLK                                                                                                                                                                                                        |

Table 4. Wake up from Standby Modes (continued)

To prevent the system from a deadlock condition (no wake up possible) a configuration where the periodic timer interrupt and wake up by LIN and HS CAN are disabled, is not allowed. The default configuration is entered for all wake-up sources in case of such an invalid setting.

All wake-up events from  $V_{1\_standby}$  mode (except  $I_{V1} > I_{CMP}$ ) are indicated to the microcontroller by a low-pulse (duration: 56 µs) at RxDL/NINT or RxDC/NINT (see *Table 3: CAN wake-up signalization*)

Wake-up from V<sub>1\_standby</sub> by SPI Access might be used to check the interrupt service handler.

#### 2.2.8 Wake up inputs

The de-bounced digital inputs WU1...WU3 can be used to wake up the L99PM72GXP from standby modes. These inputs are sensitive to any level transition (positive and negative edge)

For static contact monitoring, a filter time of 64µs is implemented at WU1-3. The filter is started when the input voltage passes the specified threshold.

In addition to the continuous sensing (static contact monitoring) at the wake up inputs, a cyclic sense functionality is implemented. This feature allows periodical activation of the wake-up inputs to read the status of the external contacts. The periodical activation can be linked to Timer 1 or Timer 2 (see Section 2.2.9). The input signal is filtered with a filter time of 16 µs after a programmable delay (80 µs or 800 µs) according to the configured Timer On-time. A wake-up is processed if the status has changed versus the previous cycle.

The Outputs OUT\_HS and OUT1-4 can be used to supply the external contacts with the timer setting according to the cyclic monitoring of the wake-up inputs.

If the wake-up inputs are configured for cyclic sense mode the input filter timing and input filter delay (*WUx\_filt* in control register 2) must correspond to the setting of the High Side Output which supplies the external contact switches (OUTx in control register 0).

In Standby Mode, the inputs WU1-3 are SPI configurable for pull-up or pull-down current source configuration according to the setup of the external. In active mode the inputs have a pull down resistor.

In Active Mode, the input status can be read by SPI (Status Register 2). Static sense should be configured (Control Register 2) before the read operation is started (In cyclic sense

DocID024767 Rev 4 21/129

configuration, the input status is updated according to the cyclic sense timing; therefore, reading the input status in this mode may not reflect the actual status).

#### 2.2.9 Cyclic contact supply

In  $V_{1\_standby}$  and  $V_{Bat\_standby}$  modes, any high side driver output (OUT1..4, OUTHS) can be used to periodically supply external contacts.

The timing is selectable by SPI

Timer 1: period is X s. The on-time is 10 ms resp. 20 ms: with  $X \in \{1, 2, 3, 4s\}$