# STHVDAC-253M

# Antenna tuning circuit

Datasheet - production data

#### **Features**

- Dedicated ASIC to control BST tunable capacitances

- Operation compliant with cellular systems requirements

- Integrated boost converter with 3 programmable outputs (from 0 to 25 V)

- Low power consumption

- MIPI RFFE serial interface 1.8 V

- Available in WLCSP for stand-alone or SiP module integration

- RF tunable passive implementation in mobile phones to optimize the radiated performances

# Application

- Cellular antenna tunable matching network in multi-band GSM/WCDMA mobile phone

- Compatible with open loop antenna tuner applications

## **Description**

The ST BST capacitance controller STHVDAC-253M is a high voltage digital to analog converter (DAC), specifically designed to control and meet the wide tuning bias voltage requirement of the BST tunable capacitances.

It provides 3 independent high voltage outputs, thus having the capability to control 3 different capacitances. It is fully controlled through a RFFE serial interface.

BST capacitances are tunable capacitances intended for use in mobile phone application, and dedicated to RF tunable applications. These tunable capacitances are controlled through a bias voltage ranging from 0 to 25 V. The implementation of BST tunable capacitance in mobile phones enables significant improvement in terms of radiated performances, making the performance almost insensitive to the external environment.

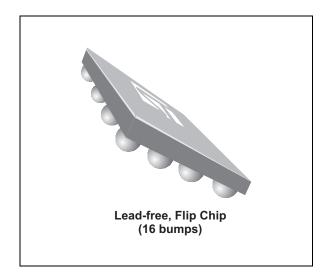

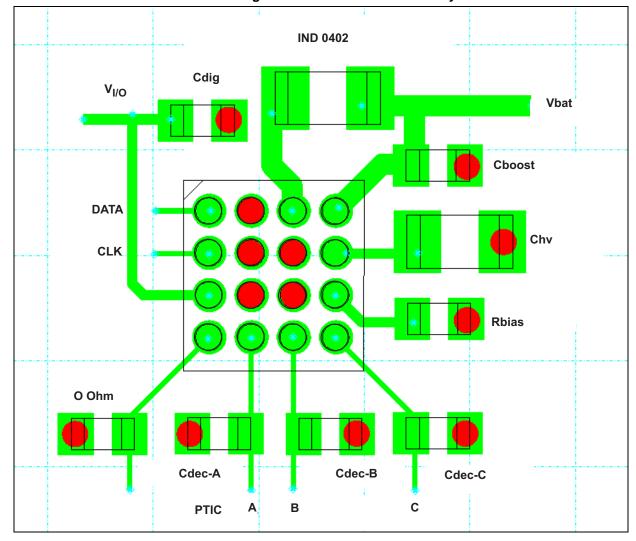

Figure 1. Pin configuration bumps side view

# **Contents**

| 1 | Electrical characteristics |                                                  |  |  |  |  |  |

|---|----------------------------|--------------------------------------------------|--|--|--|--|--|

| 2 | Func                       | tional block diagram                             |  |  |  |  |  |

| 3 | Theo                       | ory of operation                                 |  |  |  |  |  |

|   | 3.1                        | HVDAC output voltages 6                          |  |  |  |  |  |

|   | 3.2                        | Operating modes                                  |  |  |  |  |  |

|   | 3.3                        | Device reset                                     |  |  |  |  |  |

|   | 3.4                        | RFFE serial interface                            |  |  |  |  |  |

|   | 3.5                        | RFFE register and write command sequence 9       |  |  |  |  |  |

|   | 3.6                        | RFFE serial interface extended mode 9            |  |  |  |  |  |

|   | 3.7                        | RFFE serial interface brodcast capability        |  |  |  |  |  |

|   | 3.8                        | Power-up / down sequence                         |  |  |  |  |  |

|   | 3.9                        | Power supply sequencing                          |  |  |  |  |  |

|   | 3.10                       | Trigger Mode11                                   |  |  |  |  |  |

|   |                            | 3.10.1 Trigger mode enabled:                     |  |  |  |  |  |

|   |                            | 3.10.2 Trigger mode disabled (default mode):     |  |  |  |  |  |

|   | 3.11                       | Settling time                                    |  |  |  |  |  |

|   | 3.12                       | Operation with 1 to 3 tunable capacitor          |  |  |  |  |  |

| 4 | Regi                       | sters table                                      |  |  |  |  |  |

|   | 4.1                        | RFFE interface-register content description      |  |  |  |  |  |

|   | 4.2                        | RFFE interface, command and data frame structure |  |  |  |  |  |

|   | 4.3                        | Changing USID                                    |  |  |  |  |  |

|   | 4.4                        | Serial interface specification                   |  |  |  |  |  |

| 5 | Appl                       | ication schematic                                |  |  |  |  |  |

| 6 | Pack                       | age information                                  |  |  |  |  |  |

| 7 | Orde                       | ring information                                 |  |  |  |  |  |

| 8 | Revi                       | sion history25                                   |  |  |  |  |  |

# 1 Electrical characteristics

Table 1. Absolute maximum ratings (limiting value)

| Symbol                 | Parameter                                   | Rating            | Unit |

|------------------------|---------------------------------------------|-------------------|------|

| AV <sub>DD</sub>       | Analog supply voltage                       | -0.3 to +5.5      | V    |

| VIO                    | Digital supply voltage                      | -0.3 to +3.3      | V    |

| V <sub>I/O</sub>       | Input voltage logic lines (DATA, CLK, CS)   | -0.5 to VIO + 0.5 | V    |

| V <sub>ESD (HBM)</sub> | Human body model, JESD22-A114-B, All I/O    | 2                 | kV   |

| V <sub>ESD (CDM)</sub> | Charge device model, JESD22-C101-C, All I/O | 500               | V    |

| T <sub>stg</sub>       | Storage temperature range                   | -55 to +150       | °C   |

| T <sub>j</sub>         | Maximum junction temperature                | 150               | °C   |

Table 2. Recommended operating conditions

| Symbol              | Parameter                                      |                      | Unit |                        |       |

|---------------------|------------------------------------------------|----------------------|------|------------------------|-------|

| Cymbol              | T diameter                                     | Min.                 | Тур. | Max.                   | Oille |

| T <sub>AMB_oP</sub> | Operating ambient temperature                  | -30                  | -    | +85                    | °C    |

| AV <sub>DD</sub>    | Analog supply voltage                          | 2.3                  | -    | 5                      | V     |

| V <sub>I/O</sub>    | Digital supply voltage                         | 1.65                 | -    | 1.95                   | V     |

| V <sub>IH</sub>     | Input voltage logic level HIGH (DATA, CLK, CS) | 0.7*V <sub>I/O</sub> | -    | V <sub>I/O</sub> + 0.3 | V     |

| V <sub>IL</sub>     | Input voltage logic level LOW (DATA, CLK, CS)  | -0.3                 | -    | 0.35*V <sub>I/O</sub>  | V     |

Electrical characteristics STHVDAC-253M

Table 3. High voltage DAC output characteristics

| Condition       | Conditions: AV <sub>DD</sub> from 2.5 to 5 V, VIO from 1.65 to 1.95 V, T <sub>amb</sub> from -30 °C to +85 °C, OUTA-C, unless otherwise specified |                                              |      |      |      |                   |  |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------|------|------|-------------------|--|--|--|--|

| Symbol          | Parameter                                                                                                                                         | Conditions                                   | Min. | Тур. | Max  | Unit              |  |  |  |  |

| Shutdown n      | node                                                                                                                                              |                                              |      | 1    |      |                   |  |  |  |  |

| R <sub>PD</sub> | OUTA-OUTC set in pull down mode                                                                                                                   |                                              |      |      | 500  | Ω                 |  |  |  |  |

| Active mode     | 9                                                                                                                                                 |                                              |      |      |      |                   |  |  |  |  |

| V <sub>OH</sub> | OUTA-OUTC maximum output voltage                                                                                                                  | DAC = 7Fh, I <sub>LOAD</sub> < 1 μA          | 24   |      |      | V                 |  |  |  |  |

| V <sub>OL</sub> | OUTA-OUTC minimum output voltage                                                                                                                  | DAC = 01h, I <sub>LOAD</sub> < 1 μA          |      |      | 1    | V                 |  |  |  |  |

|                 |                                                                                                                                                   | 7 bits DAC 01h to 3Ch range (< 6V)           |      | 100  |      | mV                |  |  |  |  |

| Resolution      | Voltage resolution / OUTA, OUTC                                                                                                                   | 7 bits DAC, 3Dh to 48h range<br>( 6 V-8,4 V) |      | 200  |      | mV                |  |  |  |  |

|                 |                                                                                                                                                   | 7 bits DAC, 49h to 7Fh range ( (>8,4 V)      |      | 300  |      | mV                |  |  |  |  |

| ERROR           |                                                                                                                                                   | V <sub>OUT</sub> 2 to 25 V                   | -3.5 |      | +3.5 | %V <sub>OUT</sub> |  |  |  |  |

| I <sub>sc</sub> | Over current protection                                                                                                                           | Any DAC output                               |      |      | 50   | mA                |  |  |  |  |

4/27 DocID025735 Rev 1

**Table 4. DC characteristics**

Conditions: AV<sub>DD</sub> 3.3 V, V<sub>IO</sub> from 1.65 to 1.95 V,  $T_{amb}$  from -30 °C to +85 °C,  $L_{BOOST}$  = 15  $\mu H$  unless otherwise specified

|                                                  |                                                             | unless other            | wise specified                          |      |      |                  |      |

|--------------------------------------------------|-------------------------------------------------------------|-------------------------|-----------------------------------------|------|------|------------------|------|

| Symbol                                           | Parameter                                                   |                         | Conditions                              | Min. | Тур. | Max.             | Unit |

|                                                  |                                                             | Low power mode          | Low power mode or shutdown              |      |      |                  |      |

| I <sub>LBOOST</sub>                              |                                                             |                         | Active mode, 1 output steady state 2 V  |      | 130  |                  |      |

|                                                  | Boost inductor supply current:<br>L = 15 µA                 | I <sub>LBOOST_SS2</sub> | Active mode, 3outputs steady state 2 V  |      | 300  | 570              | μA   |

|                                                  | AV <sub>DD</sub> = 3.3 V                                    |                         | Active mode, 1 output steady state 20 V |      | 150  |                  |      |

|                                                  |                                                             | ILBOOST_SS20            | Active mode, 3outputs steady state 20 V |      | 370  | 750              |      |

|                                                  |                                                             | Low power mode          |                                         | 1.35 | 4    |                  |      |

|                                                  | AV <sub>DD</sub> supply current<br>AV <sub>DD</sub> = 3.3 V |                         | Active mode, 1 output steady state 2 V  |      | 590  | 670              |      |

| I <sub>AVDD</sub>                                |                                                             | I <sub>AVDD_SS2</sub>   | Active mode, 3outputs steady state 2 V  |      | 700  | 780              | μA   |

|                                                  |                                                             |                         | Active mode, 1 output steady state 20 V |      | 590  | 670              |      |

|                                                  |                                                             | I <sub>AVDD_</sub> SS2  | Active mode, 3outputs steady state 20 V |      | 700  | 780              |      |

|                                                  |                                                             | Low power mode          |                                         |      | 1.8  | 4                |      |

| I <sub>vio</sub> V <sub>dig</sub> supply current |                                                             | ,                       |                                         |      |      | 40<br>315<br>585 | μA   |

| I <sub>IH</sub>                                  | Input current logic level high                              | DATA, CLK, SELS         | SID pins                                | -1   |      | 1                | μA   |

| I <sub>IL</sub>                                  | Input current logic level LOW                               | DATA, CLK , SEL         | SID pins                                | -1   |      | 1                | μA   |

| V <sub>IORST</sub>                               | V <sub>IO</sub> low threshold                               |                         |                                         |      |      | 0.2              | V    |

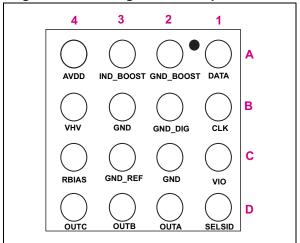

#### Functional block diagram 2

Figure 2. HVDAC functional block diagram

Table 5. Signal descriptions

| Pin number | Pin name          | Description                        |

|------------|-------------------|------------------------------------|

| A1         | DATA              | RFFE interface / serial DATA       |

| A2         | GND_BOOST         | Power ground for BOOST             |

| A3         | IND_BOOST         | Boost inductance                   |

| A4         | AV <sub>DD</sub>  | Analog supply                      |

| B1         | CLK               | RFFE interface / serial clock      |

| B2         | GND_DIG           | Ground reference                   |

| В3         | GND               | Tie to GND plane on PCB            |

| B4         | V <sub>HV</sub>   | Boost high voltage output          |

| C1         | V <sub>IO</sub>   | RFFE interface / Serial I/O supply |

| C2         | GND               | Tie to GND plane on PCB            |

| C3         | GND_REF           | Ground reference                   |

| C4         | R <sub>bias</sub> | Biasing reference resistance       |

| D1         | SELSID            | RFFE interface / SELSID            |

| D2         | OUTA              | High voltage output A              |

| D3         | OUTB              | High voltage output B              |

| D4         | OUTC              | High voltage output C              |

5//

6/27 DocID025735 Rev 1

## 3 Theory of operation

### 3.1 HVDAC output voltages

The HVDAC outputs are directly controlled by programming the 7-bit DAC (DAC A, DAC B and DAC C) through the RFFE serial interface.

The DAC stages are driven from a reference voltage, generating an analog output voltage driving a high voltage amplifier supplied from the boost converter (see HVDAC block diagram - *Figure 2*).

The HVDAC output voltages are scaled from 0 to 25 V, with 128 steps. The device resolution is automatically adjusted depending on the voltage output range so that it will match the CV curve of tunable BST capacitors.

From 0 to 6 V the resolution is 100 mV, from 6 V to 8.4 V the resolution is 200 mV, from 8.4 V to 25 V the resolution is 300 mV.

If DAC value is set to 00 h, then the corresponding output is directly connected to GND through a pull-down resistor (500  $\Omega$ ). See *Table 6* for DAC settings correspondence table.

DEC HEX BIN Volts DEC HEX BIN Volts DEC HEX BIN Volts 1.9 3.8 0.56 3.9 0.56 2.1 0.56 2.2 4.1 2.3 0.57 4.2 0.58 2.4 2B 4.3 0.62 2.5 4.4 0.7 1A 2.6 2D 4.5 0.8 1B 2.7 2F 4.6 0.9 1C 2.8 4.7 Α 1D 2.9 4.8 В 1.1 1E 4.9 C 1.2 1F 3.1 D 1.3 3.2 5.1 3.3 Ε 1.4 5.2 F 1.5 3.4 5.3 3.5 5.4 1.6 1.7 3.6 5.5 1.8 3.7 5.6 5.7 11.1 18.3

Table 6. DAC settings correspondence table

DocID025735 Rev 1

7/27

Theory of operation STHVDAC-253M

Table 6. DAC settings correspondence table

| DEC | HEX | BIN      | Volts | DEC | HEX | BIN      | Volts | DEC | HEX | BIN      | Volts |

|-----|-----|----------|-------|-----|-----|----------|-------|-----|-----|----------|-------|

| 58  | 3A  | 00111010 | 5.8   | 82  | 52  | 01010010 | 11.4  | 106 | 6A  | 01101010 | 18.6  |

| 59  | 3B  | 00111011 | 5.9   | 83  | 53  | 01010011 | 11.7  | 107 | 6B  | 01101011 | 18.9  |

| 60  | 3C  | 00111100 | 6     | 84  | 54  | 01010100 | 12    | 108 | 6C  | 01101100 | 19.2  |

| 61  | 3D  | 00111101 | 6.2   | 85  | 55  | 01010101 | 12.3  | 109 | 6D  | 01101101 | 19.5  |

| 62  | 3E  | 00111110 | 6.4   | 86  | 56  | 01010110 | 12.6  | 110 | 6E  | 01101110 | 19,8  |

| 63  | 3F  | 00111111 | 6.6   | 87  | 57  | 01010111 | 12.9  | 111 | 6F  | 01101111 | 20.1  |

| 64  | 40  | 01000000 | 6.8   | 88  | 58  | 01011000 | 13.2  | 112 | 70  | 01110000 | 20.4  |

| 65  | 41  | 01000001 | 7     | 89  | 59  | 01011001 | 13.5  | 113 | 71  | 01110001 | 20.7  |

| 66  | 42  | 01000010 | 7.2   | 90  | 5A  | 01011010 | 13.8  | 114 | 72  | 01110010 | 21    |

| 67  | 43  | 01000011 | 7.4   | 91  | 5B  | 01011011 | 14.1  | 115 | 73  | 01110011 | 21.3  |

| 68  | 44  | 01000100 | 7.6   | 92  | 5C  | 01011100 | 14.4  | 116 | 74  | 01110100 | 21.6  |

| 69  | 45  | 01000101 | 7.8   | 93  | 5D  | 01011101 | 14.7  | 117 | 75  | 01110101 | 21.9  |

| 70  | 46  | 01000110 | 8     | 94  | 5E  | 01011110 | 15    | 118 | 76  | 01110110 | 22.2  |

| 71  | 47  | 01000111 | 8.2   | 95  | 5F  | 01011111 | 15.3  | 119 | 77  | 01110111 | 22.5  |

| 72  | 48  | 01001000 | 8.4   | 96  | 60  | 01100000 | 15.6  | 120 | 78  | 01111000 | 22.8  |

| 73  | 49  | 01001001 | 8.7   | 97  | 61  | 01100001 | 15.9  | 121 | 79  | 01111001 | 23.1  |

| 74  | 4A  | 01001010 | 9     | 98  | 62  | 01100010 | 16.2  | 122 | 7A  | 01111010 | 23.4  |

| 75  | 4B  | 01001011 | 9.3   | 99  | 63  | 01100011 | 16.5  | 123 | 7B  | 01111011 | 23.7  |

| 76  | 4C  | 01001100 | 9.6   | 100 | 64  | 01100100 | 16.8  | 124 | 7C  | 01111100 | 24    |

| 77  | 4D  | 01001101 | 9.9   | 101 | 65  | 01100101 | 17.1  | 125 | 7D  | 01111101 | 24.3  |

| 78  | 4E  | 01001110 | 10.2  | 102 | 66  | 01100110 | 17.4  | 126 | 7E  | 01111110 | 24.6  |

| 79  | 4F  | 01001111 | 10.5  | 103 | 67  | 01100111 | 17.7  | 127 | 7F  | 01111111 | 24.9  |

| 80  | 50  | 01010000 | 10.8  | 104 | 68  | 01101000 | 18    |     |     |          |       |

<sup>-</sup> From 0 to 6 V the resolution is 100 mV.

<sup>-</sup> From 6.20 to 8.40 V the resolution is 200 mV.

<sup>-</sup> From 8.70 to 24.90 V the resolution is 300 mV.

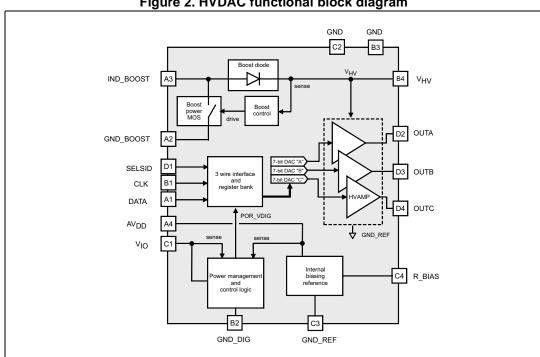

## 3.2 Operating modes

The following operating modes are accessible through the serial interface:

- **Shutdown mode:** The HVDAC is switched off, and all the blocks in the control ASIC are switched off. Power consumption is almost zero in this mode, the DAC outputs are pulled down. The shutdown mode is set by driving VIO to low level.

- Active mode: The HVDAC is switched on and the DAC outputs are fully controlled through the RFFE serial interface. The DAC settings can be dynamically modified and the HV outputs will be adjusted according to the specified timing diagrams. Each DAC can be individually controlled and/or switched off according to application requirements. Boost is active in this mode. The device is directly set into this mode after startup (VIO supply switched on, or power mode bits set to 01b).

- **Low power mode:** The HVDAC is switched OFF except the RFFE interface. This mode is set by driving PWR\_MODE bits to 10b.

Figure 3. HVDAC state diagram

#### 3.3 Device reset

Power-On Reset is implemented on the VIO supply input, ensuring the HVDAC will be reset to default mode once VIO supply line rises above a given threshold  $V_{IORST}$ . This trigger will force all registers to their default value.

Soft Reset is also implemented as defined in the MIPI RFFE specification. Setting PWR\_MODE bits to 01b will force the device to reset all registers to their default value, and switch into active mode.

Theory of operation STHVDAC-253M

#### 3.4 RFFE serial interface

The HVDAC is fully controlled through RFFE serial interface (DATA, VIO, CLK).

This interface is further described in the next sections of this document and is made compliant to the MIPI alliance Specification for RF Front End control Interface version 1.10 (26 July 2011)

Sequence Start Condition (SSC): One rising edge followed by falling edge on DATA while CLK remains at logic level low. This is used by the Master to identify the start of a Command frame.

Parity (P): Each frame shall end with a single parity bit. The parity bit shall be driven such that the total number of bits in the frame that are driven to logic level one, including the parity bit, is odd.

Bus Park Cycle (BP): The slave releasing DATA will drive the DATA to logic level zero during the first half of the CLK clock cycle. This is used by the Master as the indication of the end of Frame.

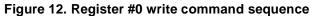

### 3.5 RFFE register and write command sequence

Register #0 is a specific register that can be programmed without sending the register address. Output C is associated to Register #0 so that when there is only one tunable capacitor to control a simple register#0 write command is sufficient. Please refer to *Figure 12* for Register #0 Write sequence. The Sequence Starts with an Start Sequence command (SSC) followed by the Register #0 Write Command frame containing the slave address, a logic one and a seven bit word to be written to Register #0.

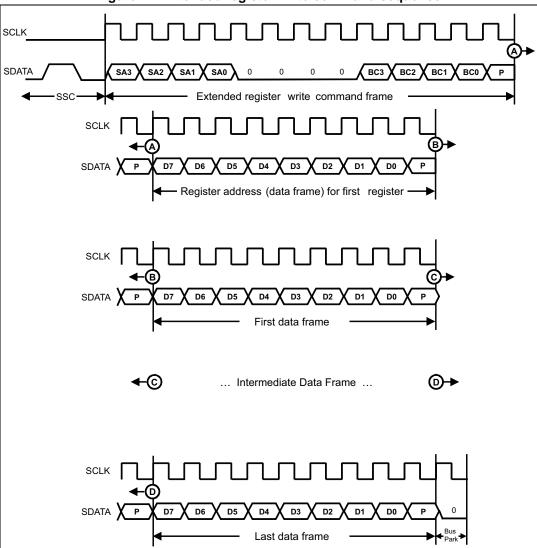

### 3.6 RFFE serial interface extended mode

All the registers in the device can be addressed in extended mode, by sending appropriate command sequences as per MIPI RFFE specification (see *Figure 11*).

# 3.7 RFFE serial interface broadcast capability

Registers 27 to 31 can be addressed in broadcast mode, by sending appropriate command sequences as per MIPI RFFE specification.

STHVDAC-253M Theory of operation

### 3.8 Power-up / down sequence

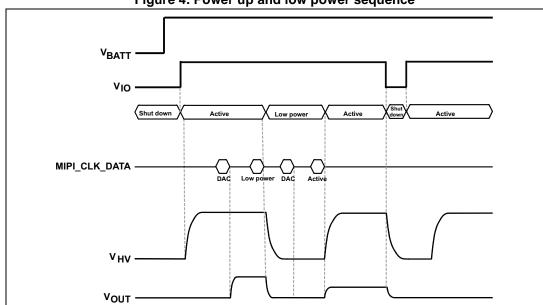

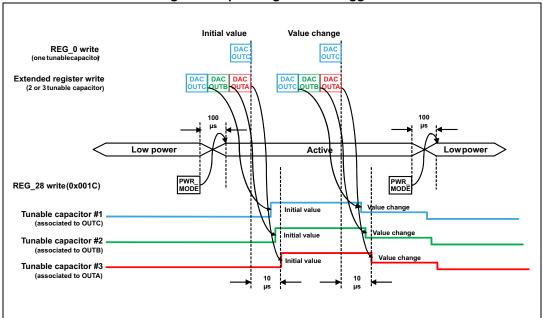

*Table 7* and *Figure 4* describe the HVDAC settling time requirements and recommended timing diagrams.

Switching from shutdown to active mode is triggered by setting VIO to high level.

Switching from active to low power mode will occur by setting PWR\_MODE bits to 10b in register 28.

Switching from low power to active mode will occur by setting power mode bits to 01b in register 28

Following active mode command (from Shutdown or from Low power), the HVDAC will be operational after  $T_{active}$  (typ. 100  $\mu$ s). Once in Active mode, a settling time of 10  $\mu$ s typical ( $T_{set}$ ) is required following each DAC command in active mode. During this settling time the HVDAC output voltages will vary from the initial to the updated DAC command.

Figure 4. Power up and low power sequence

# 3.9 Power supply sequencing

It is assumed that the  $AV_{DD}$  input will be directly supplied from the battery and will then be the first ON.

VIO should then be switched as described in previous sections.

Theory of operation STHVDAC-253M

### 3.10 Trigger Mode

To meet precise timing requirements and avoid RFFE interface traffic congestion at critical timing, trigger mode has been implemented in the RFFE interface.

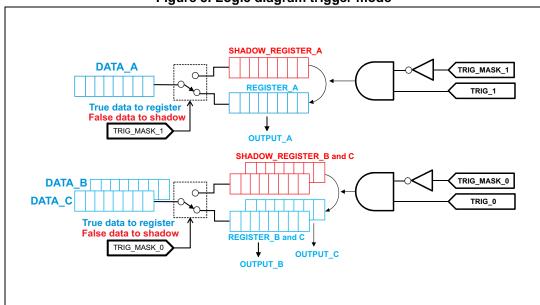

Two triggers (TRIG0 and TRIG1) are available and can be controlled through the RFFE interface.

Registers 0 and 1 (DAC C and DAC B) are associated to TRIG0, and register 2 (DAC A) is associated to TRIG1. Each trigger can be activated independently.

#### 3.10.1 Trigger mode enabled:

The different triggers are enabled unsetting corresponding trigger mask bits in register 28.

In this case, once in ACTIVE mode, the following sequence must be followed to control the HVDAC outputs:

Send any valid register 0/1/2 write command sequence. The new register values will be temporarily stored in shadow registers.

Send a register28 write command sequence, setting trigger bits and keeping Trigger mask bits low. The shadow registers will be loaded to destination registers and this will trigger the corresponding DAC outputs to their new values (see *Figure 5*).

### 3.10.2 Trigger mode disabled (default mode):

The different triggers are disabled setting corresponding trigger mask bits in register 28.

In this case, any valid register write command sequence is directly loaded to the destination register, directly triggering the corresponding DAC output to its new value.

The following logic diagram illustrates the trigger mode function. By default the trigger mode is disable and the data are directly sent to the register in order to change the outputs without Trigger.

Figure 5. Logic diagram trigger mode

577

STHVDAC-253M Theory of operation

# 3.11 Settling time

The ST HVDAC will set the bias voltage of the tuner within 10µs typical after

- Bus Park (BP) of register28 write sequence data frame if trigger mode is enabled

- Bus Park (BP) of register 0/1/2/3 write sequence data frame if trigger mode is disabled

Table 7. Timing

| Condition           | Conditions: AV <sub>DD</sub> from 2.3 to 5 V, VIO from 1.65 to 1.95 V, T <sub>amb</sub> from -30 °C to +85 °C, OUTA-OUTC unless otherwise specified |                                                         |     |            |     |      |  |  |  |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----|------------|-----|------|--|--|--|--|

| Symbol              | Parameter                                                                                                                                           | Condition                                               | min | typ<br>(1) | max | unit |  |  |  |  |

| T <sub>active</sub> | activation time                                                                                                                                     | Activation time from shutdown to active mode            |     | 100        | 300 | μs   |  |  |  |  |

| T <sub>set+</sub>   | Output positive settling time at 95%                                                                                                                | Vout = 2 V to 20 V equivalent load of 15 Kohms and 1 nF |     | 10         | 35  | μs   |  |  |  |  |

| T <sub>set-</sub>   | Output negative settling time at 95%                                                                                                                | Vout = 20 V to 2 V equivalent load of 15 Kohms and 1 nF |     | 10         | 35  | μs   |  |  |  |  |

<sup>1.</sup> Typical value are provided for IND = 15  $\mu$ H

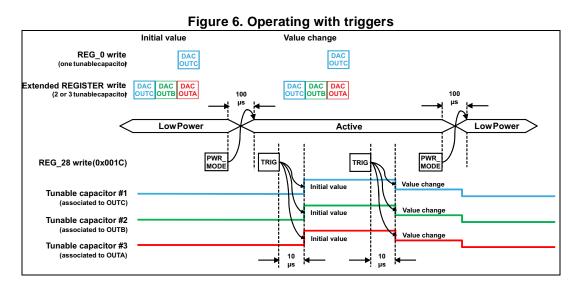

## 3.12 Operation with 1 to 3 tunable capacitors

With triggers:

It is recommended to use trigger so that outputs will be activated by write to REG\_28. In order to use the trigger, it is required to change the TRIG\_MASK to 0.

When only one tunable capacitor is required it is recommended to use the REG\_0 associated to OUTC.

When several tunable capacitors are required it is recommended to use extended register write so that all DAC registers can be programmed with only one command.

The *Figure 6* below represents operation when trigger and extended write are in use.

DocID025735 Rev 1

13/27

Theory of operation STHVDAC-253M

#### Without triggers:

When the TRIG\_MASK are set to 1 (disable) the outputs will change after the DAC are set. When using the extended write all output will changed at the same time.

The Figure 7 below represents operation without trigger and using extended write.

STHVDAC-253M Register table

# 4 Register table

The HVDAC is embedding 8 bits registers. Registers content is described in *Table 8*, and registers default values are provided in *Table 9*.

Table 8. Registers content

| Reg | Address | D7<br>MSB | D6              | D5                                    | D4       | D3    | D2 | D1    | D0<br>LSB | Access<br>type | Triggered |

|-----|---------|-----------|-----------------|---------------------------------------|----------|-------|----|-------|-----------|----------------|-----------|

| 0   | [00000] | 0         |                 | DAC C                                 |          |       |    |       |           |                | TRIG0     |

| 1   | [00001] | 0         |                 |                                       |          | DAC B |    |       |           | RW             | TRIG0     |

| 2   | [00010] | 0         |                 | DAC A                                 |          |       |    |       |           |                | TRIG1     |

| 28  | [11100] | PWR_      | MODE            | MODE Trig Trig Trig TRIG2 TRIG1 TRIG0 |          |       |    | TRIG0 | RW        | no             |           |

| 29  | [11101] |           | Product ID      |                                       |          |       |    |       |           | R              | no        |

| 30  | [11110] |           | Manufacturer ID |                                       |          |       |    |       |           | R              | no        |

| 31  | [11111] | Spa       | are             | Manufact                              | turer ID |       | US | SID   |           | RW             | no        |

Table 9. Registers default values

| Reg | Address | D7                 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|-----|---------|--------------------|----|----|----|----|----|----|----|

| 0   | [00000] | 0                  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 1   | [00001] | 0                  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 2   | [00010] | 0                  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 28  | [11100] | 0                  | 0  | 1  | 1  | 1  | 0  | 0  | 0  |

| 29  | [11101] | (*) <sup>(1)</sup> | 0  | 0  | 0  | 0  | 0  | 1  | 0  |

| 30  | [11110] | 0                  | 0  | 0  | 0  | 0  | 1  | 0  | 0  |

| 31  | [11111] | 0                  | 0  | 0  | 1  | 0  | 1  | 1  | 1  |

<sup>(\*)</sup> Reg #29 - D7 (MSB DEVICE ID) default value is directly tied to SELSID pin. This bit is set to 1 if SELSID pin is tied to VIO, and set to 0 if SELSID pin is tied to GND. This will allow to have two HVDAC with specific product ID on the same mobile phone.

Register table STHVDAC-253M

# 4.1 RFFE interface-register content description

Registers content and control are further described in *Table 10* to *Table 12*.

Table 10. HVDAC mode selection-REG#28

| D7    | D6 | Comments                             |  |  |

|-------|----|--------------------------------------|--|--|

| PWR_I |    |                                      |  |  |

| 0     | 0  | Active mode                          |  |  |

| 0     | 1  | Startup / registers reset to default |  |  |

| 1     | 0  | Low power                            |  |  |

| 1     | 1  | n/a                                  |  |  |

### Table 11. HVDAC trigger control register - REG#28

| D5         | D4         | D3         | D2    | D1    | D0    | comments                                     |

|------------|------------|------------|-------|-------|-------|----------------------------------------------|

| Trig mask2 | Trig mask1 | Trig mask0 | TRIG2 | TRIG1 | TRIG0 |                                              |

| 0          | 0          | 0          | 0     | 0     | 0     | Triggers 2, 1 and 0 are unmasked and disable |

| 0          | 0          | 0          | 1     | 1     | 1     | Triggers 2, 1 and 0 are unmasked and enable  |

| 1          | 1          | 1          | 0     | 0     | 0     | Triggers 2, 1 and 0 are masked (default)     |

### Table 12. HVDAC unique slave identifier control - REG31

| D7 | D6  | D5        | D4          | D3 | D2 | D1  | D0 | comments                                                                                           |

|----|-----|-----------|-------------|----|----|-----|----|----------------------------------------------------------------------------------------------------|

| sp | are | Manufactu | rer_ID[9,8] |    | US | SID |    |                                                                                                    |

| 0  | 0   | 0         | 1           | 0  | 1  | 1   | 1  | default value                                                                                      |

| 0  | 0   | 0         | 1           | х  | х  | х   | х  | USID can be modified by RFFE master, see detailed programming procedure in MIPI RFFE specification |

STHVDAC-253M Register table

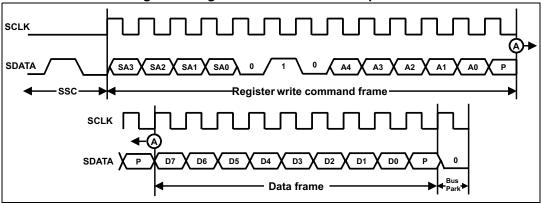

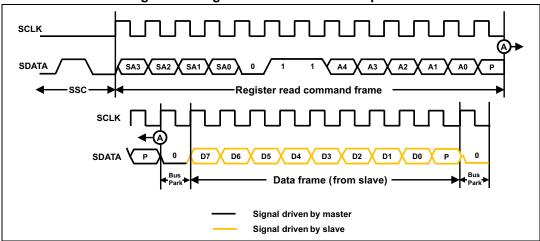

## 4.2 RFFE interface, command and data frame structure

The STHVDAC-253M RFFE interface has been implemented to support the following command sequences:

- Register WRITE

- Register READ

- Extended Register Write

These supported command sequences are described in *Table 13*.

Table 13. Support command sequences

|                         | 0, | (1) |   |      |   | С | Command frame |   |        |      |       |      |             | Data frame |                                   |           |    |  |  |    |    |  |  |  |

|-------------------------|----|-----|---|------|---|---|---------------|---|--------|------|-------|------|-------------|------------|-----------------------------------|-----------|----|--|--|----|----|--|--|--|

| Register<br>write       | 0  | 1   | 0 | USID | 0 | 1 | 0             | F | Reg    | adre | ss [4 | ŀ,0] | P<br>③      | DATA[7,0]  | Р                                 | BP<br>(4) |    |  |  |    |    |  |  |  |

| Register read           | 0  | 1   | 0 | USID | 0 | 1 | 1             | F | Reg    | adre | ss [4 | ŀ,0] | Р           | BP         | DATA<br>[7,0]                     | Р         | BP |  |  |    |    |  |  |  |

| Extended register write | 0  | 1   | 0 | USID | 0 | 0 | 0             | 0 | 0<br>E | (5)  |       | Р    | Adress[7,0] | Р          | Up to 4 bytes of data with parity |           |    |  |  | ty | BP |  |  |  |

- 1. Sequence start condition

- 2. Unique slave identifier

- 3. Parity bit

- 4. Bus park cycle

- 5. Byte count

All frames are required to end with a single parity bit. The parity bit shall be driven such that the total number of bits in the frame that are driven to logic level 1, including the parity bit, is odd. In case the device detects a parity error, the frame is considered not valid and is ignored.

Register table STHVDAC-253M

*Table 14* is showing a typical set of command sequences, to start up and initialize the device, control the HVDAC outputs, and then switch off the device. Command sequences #2,3 & 4 can also be sent at once using an extended mode command sequence.

Table 14. Typical command sequences

|                              |                                       | S | S | С | Command frame |    |     |     |   |     |   |   |                     |   |   |   |   |            |   |   |   |     |     |    |   |   |    |

|------------------------------|---------------------------------------|---|---|---|---------------|----|-----|-----|---|-----|---|---|---------------------|---|---|---|---|------------|---|---|---|-----|-----|----|---|---|----|

| CS#                          | Description                           | 0 | 1 | 0 |               | US | SID | ١   | I | R/V | ı | R | Reg adress<br>[4,0] |   |   | s | Ρ | DATA [7,0] |   |   |   | Р   | ВР  |    |   |   |    |

| 1                            | Write Reg28 - switch to active mode   | 0 | 1 | 0 | 0             | 1  | 1   | 1   | 0 | 1   | 0 | 1 | 1                   | 1 | 0 | 0 | 0 | 0          | 1 | 1 | 1 | 1   | 0   | 0  | 0 | 1 | BP |

|                              |                                       |   |   |   |               |    |     |     |   |     |   |   |                     |   |   |   |   | 0          | 0 | 0 | 0 | 0   | 0   | 0  | 0 | 1 | BP |

| 2 Write Reg0 - program DAC C |                                       | 0 | 1 | 0 | 0             | 1  | 1   | 1   | 0 | 1   | 0 | 0 | 0                   | 0 | 0 | 0 | 1 |            | С | A | С | C · | val | ue |   | Р | BP |

|                              |                                       |   |   |   |               |    |     |     |   |     |   |   |                     |   |   |   |   | 0          | 1 | 1 | 1 | 1   | 1   | 1  | 1 | 0 | BP |

|                              |                                       |   |   |   |               |    |     |     |   |     |   |   |                     |   |   |   |   | 0          | 0 | 0 | 0 | 0   | 0   | 0  | 0 | 1 | BP |

| 3 Write Reg1 - program DAC   |                                       | 0 | 1 | 0 | 0             | 1  | 1   | 1   | 0 | 1   | 0 | 0 | 0                   | 0 | 0 | 1 | 0 |            | С | Α | С | В١  | val | ue |   | Р | BP |

|                              |                                       |   |   |   |               |    |     |     |   |     |   |   |                     |   |   |   |   | 0          | 1 | 1 | 1 | 1   | 1   | 1  | 1 | 0 | BP |

|                              |                                       |   |   |   | 0             |    |     | 1 1 | 0 | 1   | 0 |   |                     |   |   |   |   | 0          | 0 | 0 | 0 | 0   | 0   | 0  | 0 | 1 | BP |

| 4                            | Write Reg2 - program DAC C            | 0 | 1 | 0 |               | 1  | 1   |     |   |     |   | 0 | 0                   | 0 | 1 | 0 | 0 |            | С | A | C | A١  | val | ue |   | Р | BP |

|                              |                                       |   |   |   |               |    |     |     |   |     |   |   |                     |   |   |   |   | 0          | 1 | 1 | 1 | 1   | 1   | 1  | 1 | 0 | BP |

|                              | Back to CS#2 to run in loop mode      |   |   |   |               |    |     |     |   |     |   |   |                     |   |   |   |   |            |   |   |   |     |     |    |   |   |    |

| 5                            | Write Reg28 - switch to shutdown mode | 0 | 1 | 0 | 0             | 1  | 1   | 1   | 0 | 1   | 0 | 1 | 1                   | 1 | 0 | 0 | 0 | 1          | 0 | 1 | 1 | 1   | 0   | 0  | 0 | 1 | ВР |

STHVDAC-253M Register table

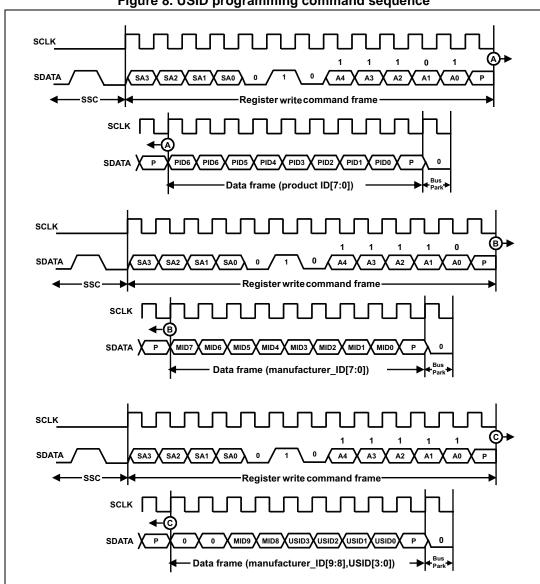

## 4.3 Changing USID

The USID programming method is compliant with MIPI RFFE interface 1.10 (26 July 2011).

This task is achieved writing consecutively registers 29 (Product ID), 30 (Manufacturer ID) and 31 (Manufacturer ID and USID definition).

Note that while reprogramming USID:

- Bits SA3, SA2, SA1 and SA0 remain old USID value.

- Register 29, D7 (MSB) corresponds to pin SELSID logic level

- New USID is defined by the register 30 last four bits.

After the USID reprogramming, SA3, SA2, SA1 and SA0 values correspond to New USID respective values (see *Figure 8*).

Figure 8. USID programming command sequence

DocID025735 Rev 1

19/27

Register table STHVDAC-253M

# 4.4 Serial interface specification

Table 15. Interface specification

| Conditio            | Conditions: AV $_{ m DD}$ from 2.3 to 5 V, VIO from 1.65 to 1.95 V, T $_{ m amb}$ from -30 °C to +85 °C, unless otherwise specified |                                     |       |     |     |      |  |  |  |  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------|-----|-----|------|--|--|--|--|

| Symbol              | Parameter                                                                                                                           | Condition                           | min   | typ | max | unit |  |  |  |  |

| F <sub>CLK</sub>    | Clock frequency                                                                                                                     |                                     |       |     | 26  | MHz  |  |  |  |  |

| T <sub>CLK</sub>    | Clock period                                                                                                                        |                                     | 38,4  |     |     | ns   |  |  |  |  |

| T <sub>HIGH</sub>   | Clock high time                                                                                                                     |                                     | 11,25 |     |     | ns   |  |  |  |  |

| T <sub>LOW</sub>    | Clock low time                                                                                                                      |                                     | 11,25 |     |     | ns   |  |  |  |  |

| TD <sub>setup</sub> | DATA setup time                                                                                                                     | Relative to 30% of CLK failing edge | 1     |     |     | ns   |  |  |  |  |

| TD <sub>hold</sub>  | DATA hold time                                                                                                                      | Relative to 70% of CLK failing edge | 5     |     |     | ns   |  |  |  |  |

| C <sub>CLK</sub>    | CLK pin input capacitance                                                                                                           |                                     |       |     | 5   | pF   |  |  |  |  |

| C <sub>DATA</sub>   | DATA pin input capacitance                                                                                                          |                                     |       |     | 8   | pF   |  |  |  |  |

Figure 9. Register write command sequence

Figure 10. Register read command sequence

20/27 DocID025735 Rev 1

STHVDAC-253M Register table

Figure 11. Extended register write command sequence

#### **Application schematic** 5

VIO STHVDAC MIPI FEM OUT C1\_\_B1\_\_A1 STPTIC C2 B2 A2

Figure 13. Recommended application schematic

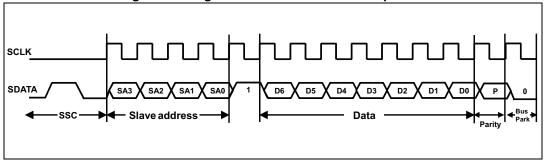

Figure 14. Evaluation board

5/

22/27

Figure 15. Recommended PCB layout

Table 16. Recommended external BOM

| Component          | Description                                    | Nominal value | Package<br>(inch) | Package<br>(mm) | Recommended P/N                                     |

|--------------------|------------------------------------------------|---------------|-------------------|-----------------|-----------------------------------------------------|

| C <sub>boost</sub> | Boost supply capacitor                         | 1 μF          | 0201              | 0603            | AVX: 02016D105MAT2A                                 |

|                    |                                                | 15 µH         | 0603              | 1608            | COILCRAFT: 0603LS-153XGL                            |

| L <sub>boost</sub> | Boost inductance                               | 10 µH         | 0402              | 1005            | Murata: LQW15CN100K10                               |

|                    |                                                | 10 μπ         |                   | 2016            | TDK: VLS2016ET-100M                                 |

| R <sub>bias</sub>  | Reference bias resistor, 1%                    | 110 kΩ        | 0201              | 0603            | Multicomp: MC0.0625W0402                            |

| C <sub>hv</sub>    | C <sub>hv</sub> Boost output capacitance, 50 V |               | 0402              | 1005            | Murata: GRM155R71H223KA12<br>Semco: CL21B223KBCNNNC |

| C <sub>dec</sub>   | Decoupling capacitance, 50 V                   | 100 pF        | 0201              | 0603            | TDK: C0603COG1H101J                                 |

Package information STHVDAC-253M

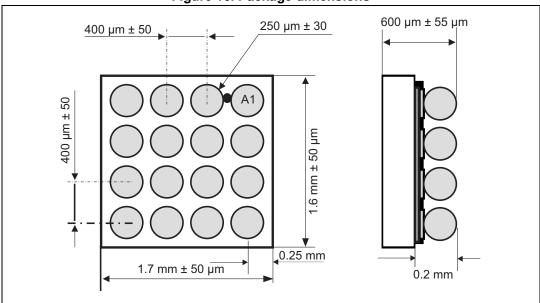

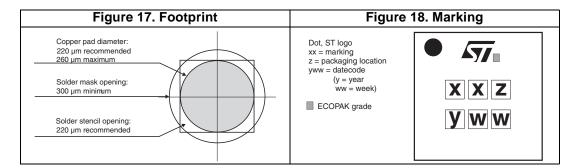

# 6 Package information

- Epoxy meets UL94, V0

- Lead-free package

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: <a href="www.st.com">www.st.com</a>. ECOPACK<sup>®</sup> is an ST trademark.

Figure 16. Package dimensions

**577**

24/27 DocID025735 Rev 1

STHVDAC-253M Package information

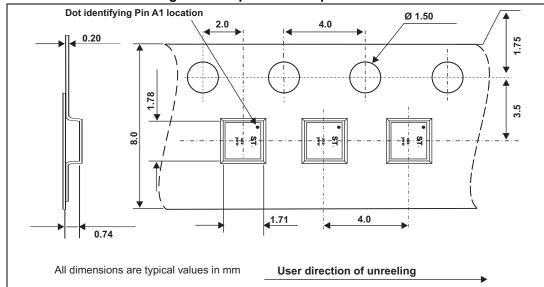

Figure 19. Tape and reel specification

Ordering information STHVDAC-253M

# 7 Ordering information

**Table 17. Ordering information**

| Order code     | code Marking |           | Weight | Base qty | Delivery mode |  |  |

|----------------|--------------|-----------|--------|----------|---------------|--|--|

| STHVDAC-253MF3 | PP           | Flip Chip | 2.7 mg | 5000     | Tape and reel |  |  |

Note:

More information is available in the STMicroelectonics Application note: AN1235: "Flip Chip: Package description and recommendations for use"

# 8 Revision history

Table 18. Document revision history

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 19-Feb-2014 | 1        | Initial release. |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

ST PRODUCTS ARE NOT DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER'S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR "AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL" INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2014 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

DocID025735 Rev 1 27/27