# Automotive monolithic dual 3.5 A step-down switching regulator with LDO

Datasheet - production data

#### **Features**

- AEC-Q100 qualified

- Two step-down synchronous switching voltage regulators with internal power switches:

- Wide operating input voltage range (from 3.3 V to 26 V)

- Output voltage selectable by external divider (feedback voltage at 0.9 V)

- 0.9 V minimum output, maximum output limited by maximum Duty Cycle

- DC/DCs can work in Low Power Mode for reduced current consumption in low output Load

- Internal high-side/ low-side NDMOS

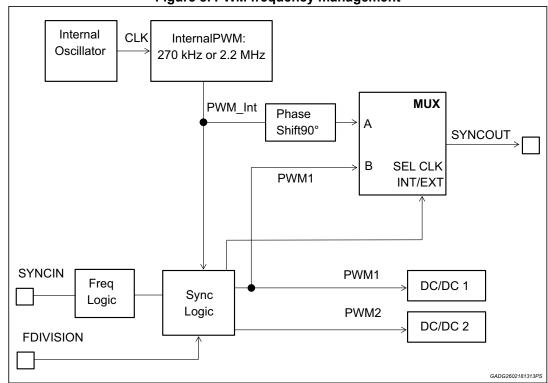

- 270 kHz and 2.2 MHz selectable free-run frequencies

- 125 kHz < f < 2.3 MHz synchronization range at SYNCIN pin

- Programmable current limits at 2 A and 4 A

- Independent hardware enabling pins

- Independent supply inputs

This is information on a product in full production.

- 180° phase shift between outputs

- Synch out 90 ° phase shift vs DC-DC1

- Programmable switching frequency divider by 1, 2, 4, 8 between the two regulators

- The two regulators can be paralleled

- Independent voltage supervisors/power-goods with selectable thresholds through external pin:

- two available thresholds for UV/OV/PG signals: 90-120-95% or 80-110-85% (output voltage percentage)

- · Soft-start, thermal protection

- One standby/linear regulator:

- Output selectable with external resistor divider till 10 V

- Soft start, hardware enable pin

- 250 mA maximum current capability

- Standby operative mode

- Programmable power good thresholds (85% or 95% output voltage percentage)

- Thermal protection

- Microcontroller reset with programmable duration, activated by output under voltage or watchdog fault

- External High Side Driver enable pin

- One integrated window watchdog (5 ms ≤ window ≤ 50 ms, with ± 20% tolerance)

- · Short circuit protected outputs

- Low external components number

- Low EMI

- Thermal shutdown junction temperature 150°C

**Table 1. Device summary**

| Order code | Package            | Packing     |

|------------|--------------------|-------------|

| L5964L-VYY | LQFP64 exp. pad up | Tray        |

| L5964L-VYT | LQFP64 exp. pad up | Tape & Reel |

www.st.com

Contents L5964

## **Contents**

| 1 | Des  | ription                                   | 6          |

|---|------|-------------------------------------------|------------|

| 2 | Pins | description                               | 8          |

|   | 2.1  | LQFP64 pins description                   | 8          |

| 3 | Bloc | diagram1                                  | 2          |

| 4 | App  | cation diagrams                           | 3          |

| 5 | Elec | rical specifications                      | 4          |

|   | 5.1  | Absolute maximum ratings                  | 4          |

|   | 5.2  | Operating voltage                         | 5          |

|   | 5.3  | Thermal data                              |            |

|   | 5.4  | Electrical characteristics                | 6          |

|   | 5.5  | Electrical characteristic curves          | <u>'</u> 1 |

| 6 | Fund | ional description                         | 2          |

|   | 6.1  | Block description                         | 2:         |

|   |      | 6.1.1 Switching regulators                | 22         |

|   |      | 6.1.2 Low drop out (LDO) linear regulator | 23         |

|   | 6.2  | Working modes 2                           | :6         |

|   |      | 6.2.1 Shutdown mode                       | 26         |

|   |      | 6.2.2 Normal mode                         | 26         |

|   |      | 6.2.3 Microcontroller mode                | 28         |

| 7 | Арр  | cation information                        | 6          |

|   | 7.1  | Output inductor (L)                       | 6          |

|   | 7.2  | Output capacitors (C <sub>OUT</sub> )     | 6          |

|   | 7.3  | Input capacitors (C <sub>IN</sub> )       | 7          |

|   | 7.4  | Bootstrap capacitor (C <sub>BS</sub> )    | 8          |

|   | 7.5  | Compensation network                      | 8          |

|   | 7.6  | Power good delay time setting             |            |

|   | 7.7  | Watch dog delay time setting              |            |

|   |      |                                           |            |

| 9 | Revis | sion history                                          | 49   |

|---|-------|-------------------------------------------------------|------|

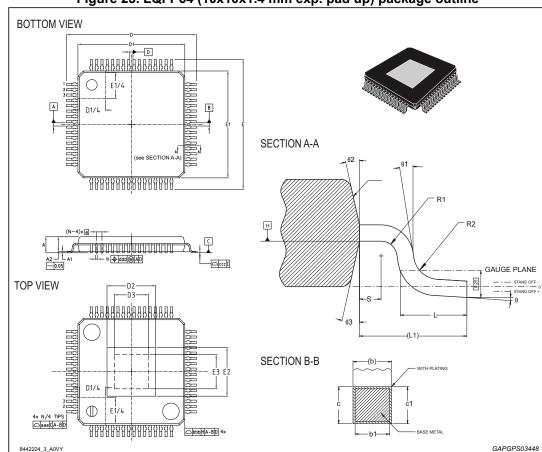

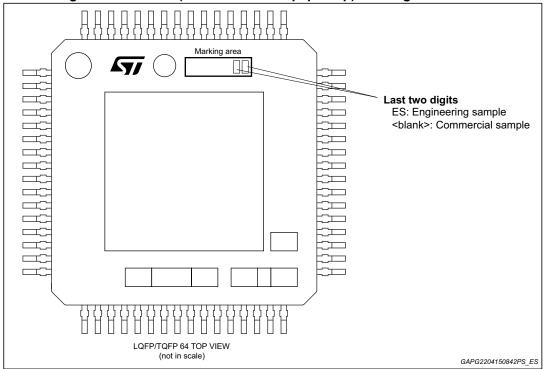

|   | 8.2   | Package marking information                           | 48   |

|   | 8.1   | LQFP64 (10x10x1.4 mm exp. pad up) package information | 45   |

| 8 | Pack  | age information                                       | 45   |

|   | 7.19  | External compensation network                         | 44   |

|   | 7.18  | The modulator gain at f <sub>C</sub>                  |      |

|   | 7.17  | The DC gain of modulator                              | 43   |

|   | 7.16  | The zero of modulator                                 | 43   |

|   | 7.15  | The pole of modulator                                 | 43   |

|   | 7.14  | R <sub>LOAD</sub>                                     | . 43 |

|   | 7.13  | The crossover frequency f <sub>C</sub>                | . 43 |

|   | 7.12  | Duty cycle                                            | 43   |

|   | 7.11  | Output capacitor                                      | 42   |

|   | 7.10  | Inductor                                              | 42   |

|   | 7.9   | Inductor ripple current                               | 42   |

|   | 7.8   | Design step guide                                     | 42   |

|   |       |                                                       |      |

List of tables L5964

## List of tables

| Table 1.  | Device summary                                                                  | 1    |

|-----------|---------------------------------------------------------------------------------|------|

| Table 2.  | LQFP64 pin list                                                                 | 8    |

| Table 3.  | Absolute maximum ratings                                                        | . 14 |

| Table 4.  | Operating voltage                                                               | . 15 |

| Table 5.  | Thermal data (LQFP64)                                                           | . 15 |

| Table 6.  | Electrical characteristics                                                      | . 16 |

| Table 7.  | Relationship between capacitor value at PGDELAY pin and delay duration          | . 27 |

| Table 8.  | 2 presets which can be selected through PGTH12 pin                              | . 27 |

| Table 9.  | Relationship between capacitor value at PGDELAY pin and Reset/Power Up duration | . 30 |

| Table 10. | Fault Management for all regulators in all working modes                        | . 33 |

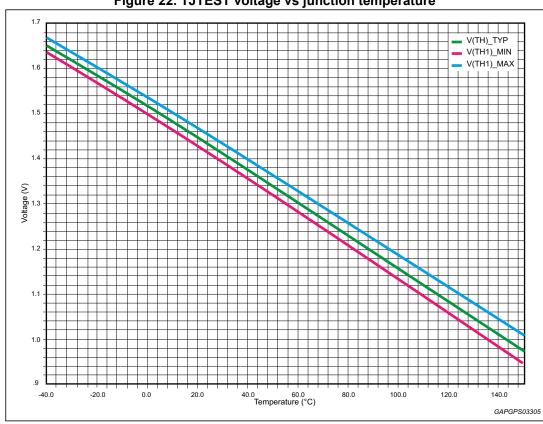

| Table 11. | TJTEST voltage vs junction temperature                                          | . 35 |

| Table 12. | Design process and component selection                                          | . 42 |

| Table 13. | LQFP64 (10x10x1.4 mm exp. pad up) package mechanical data                       | . 46 |

| Table 14  | Document revision history                                                       | 49   |

L5964 List of figures

## List of figures

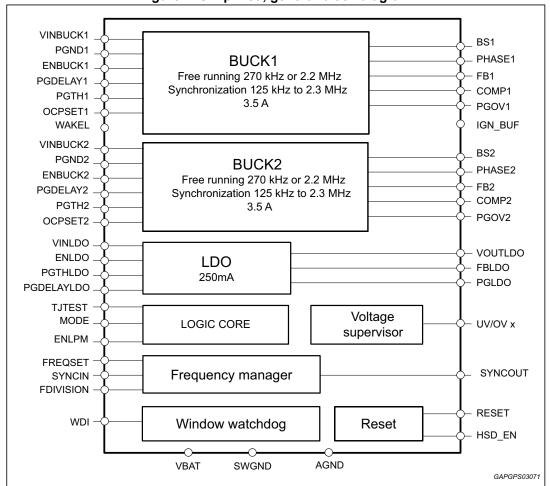

| Figure 1.  | Simplified, general block diagram                                      | /  |

|------------|------------------------------------------------------------------------|----|

| Figure 2.  | LQFP64 pinout (bottom view)                                            | 8  |

| Figure 3.  | Block diagram                                                          | 12 |

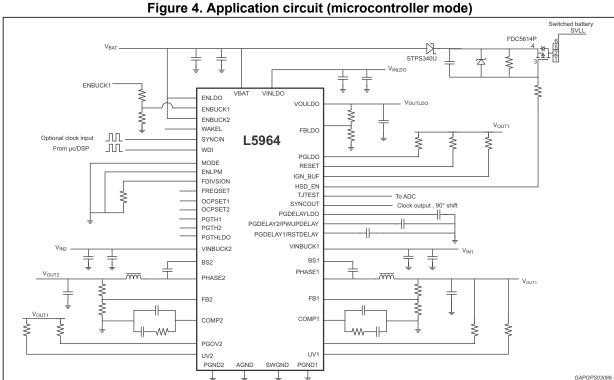

| Figure 4.  | Application circuit (microcontroller mode)                             | 13 |

| Figure 5.  | application circuit for parallel mode                                  | 13 |

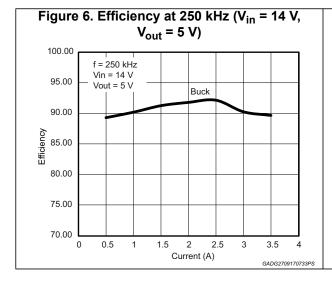

| Figure 6.  | Efficiency at 250 kHz (V <sub>in</sub> = 14 V, V <sub>out</sub> = 5 V) | 21 |

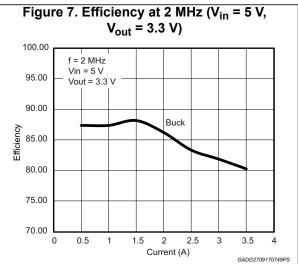

| Figure 7.  | Efficiency at 2 MHz (V <sub>in</sub> = 5 V, V <sub>out</sub> = 3.3 V)  | 21 |

| Figure 8.  | PWM frequency management                                               | 22 |

| Figure 9.  | LDO diagram                                                            | 23 |

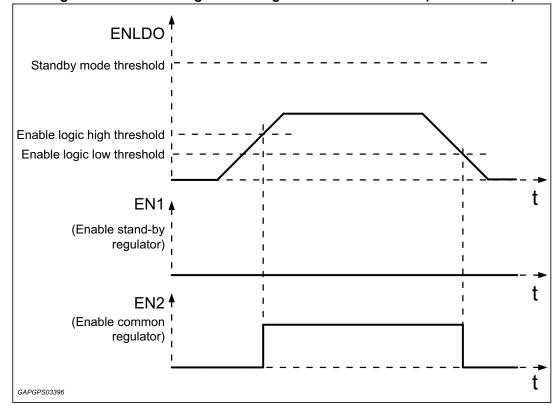

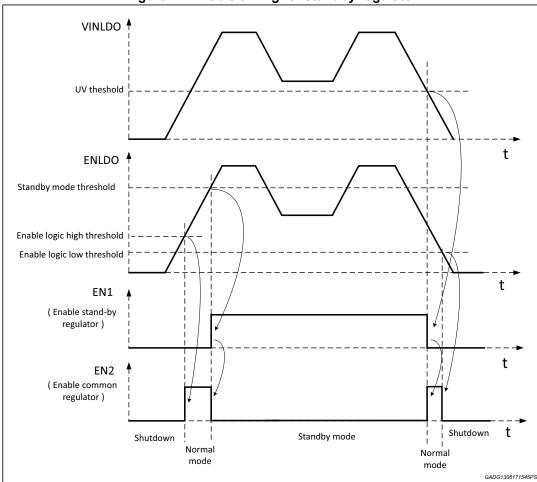

| Figure 10. | Enable timing for LDO regulator in Normal Mode (ENLDO < 5 V)           | 24 |

| Figure 11. | Enable timing for standby regulator                                    | 25 |

| Figure 12. | Shutdown Mode configuration                                            | 26 |

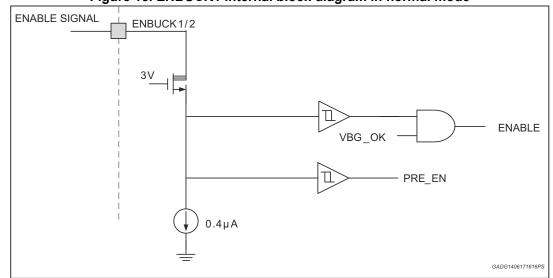

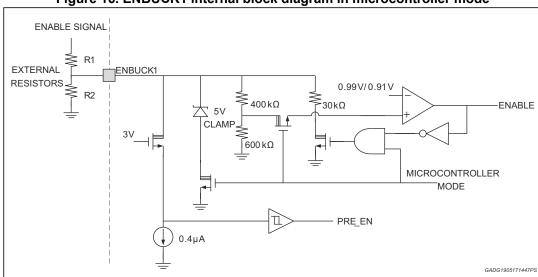

| Figure 13. | ENBUCK1 internal block diagram in normal mode                          |    |

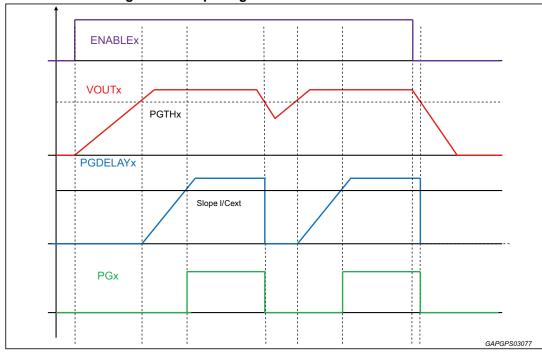

| Figure 14. | Output signals behavior in normal mode                                 | 27 |

| Figure 15. | OV, UV functions                                                       | 28 |

| Figure 16. | ENBUCK1 internal block diagram in microcontroller mode                 | 29 |

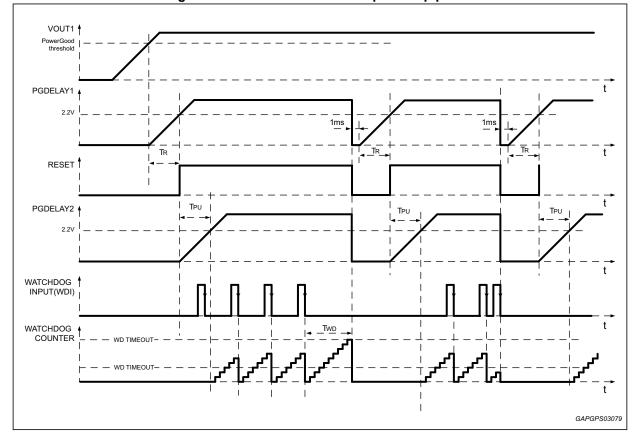

| Figure 17. | Microcontroller mode power up phase                                    | 30 |

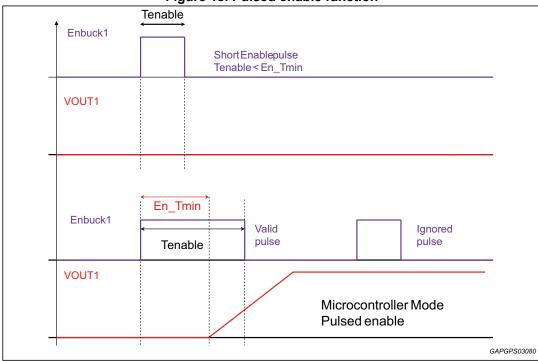

| Figure 18. | Pulsed enable function                                                 | 31 |

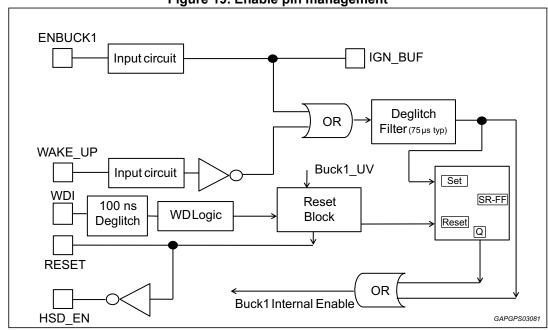

| Figure 19. | Enable pin management                                                  |    |

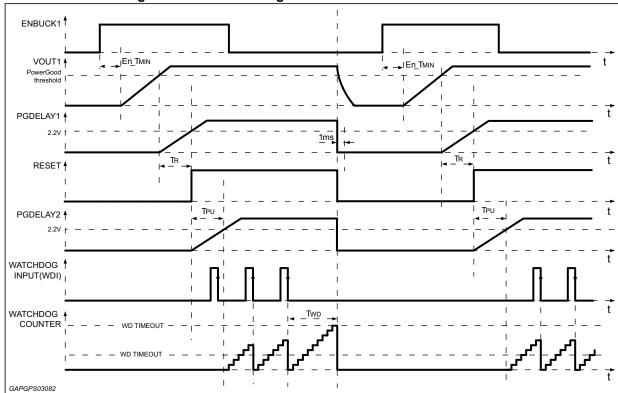

| Figure 20. | WD fail management in microcontroller mode '1'                         | 32 |

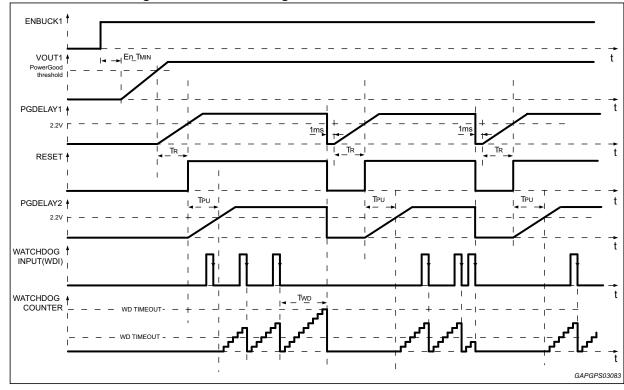

| Figure 21. | WD fail management in microcontroller mode '2'                         | 33 |

| Figure 22. | TJTEST voltage vs junction temperature                                 | 34 |

| Figure 23. | Basic control loop block diagram                                       | 38 |

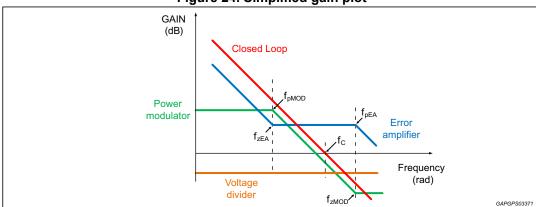

| Figure 24. | Simplified gain plot                                                   | 40 |

| Figure 25. | LQFP64 (10x10x1.4 mm exp. pad up) package outline                      | 45 |

| Figure 26. | LOFP64 (10x10x1.4 mm exp. pad up) marking information                  | 48 |

DS12453 Rev 2 5/50

Description L5964

## 1 Description

L5964 is a dual step-down switching regulator with internal power switches and a low dropout linear/standby regulator, designed for car battery supplied applications. All the regulators have independent supply voltages, enables pins, power goods and thermal protections.

The switching regulators have selectable voltage supervisors and power goods, and selectable current limits. The LDO has power good and fixed current limitation.

The PMIC finds application in different automotive systems, where load dump protection and wide input voltage range are mandatory.

Typically, the regulator connected to the battery works at low frequency, while the one connected to the pre-regulated voltage can make the most of the high frequency operation. In this way the efficiency of the system is improved and the ability of the product to function both as a pre- and post-regulator is exploited.

For the same reason, in applications where both regulators must be connected to a battery, for example when powering a hub consisting of two USB ports, it is recommended to work at the lowest frequency. The linear regulator that remains available can be used to power the controller.

The two DC-DC converters can work in free-run condition, with frequency selectable between two values, 270 kHz or 2.2 MHz, or synchronize themselves to an external clock (SYNCIN pin). They are 180° out of phase, while the synchronization output signal (SYNCOUT pin) is 90° out of phase with the first regulator. The phase shift simplifies the use of two ICs in the same application (4 DC/DCs regulators).

The high operating frequency allowed by the synchronization input helps to reduce AM and FM interferences and grants the use of small and low cost inductors and capacitors.

The two switching regulators can be used in parallel and increase the output current capability up to 7 A.

The L5964 can work in two different modes, normal and microcontroller mode, based on the condition of a hardware pin.

When the microcontroller mode is selected, some pins change functionality. For example, the reset and watchdog functions are available. In this way the PMIC easily manages the power management of a microcontroller.

The availability of power good and enable signals, however, makes easy to manage the system power up sequence even without the presence of a microcontroller, since it is possible to enable a voltage only when the previous voltage is stable and with a precise delay.

The total quiescent current, when both DC/DCs and LDO are disabled, is less than 10 μA.

The product is available in LQFP64 with exposed pad up. This package is able to dissipate power through an external heatsink.

47/

L5964 Description

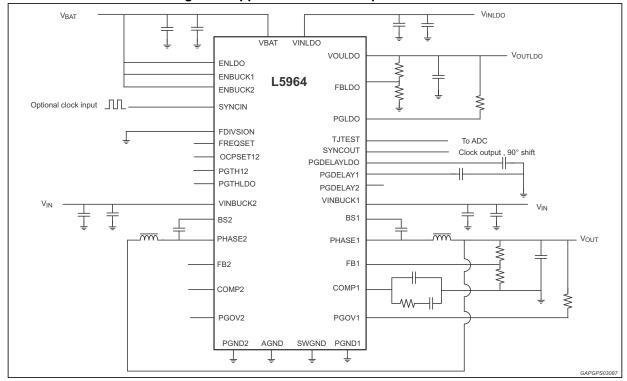

Figure 1. Simplified, general block diagram

Pins description L5964

#### **Pins description** 2

#### LQFP64 pins description 2.1

**PGDELAYLDO** SYNCOUT VOUTLDO SYNCIN ENLDO VINLDO FBLDO MD S. O. 64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 MODE 48 □ SUB PGDELAY2/ 2 47 **AGND PWUPDELAY** 3 COMP2 **PGTHLDO** 46 4 FB2 45 COMP1 5 SWGND1 44 FB1 SWGND2 43 **PGLDO** FDIVISION 42 **TJTEST** SUB 8 41 **FREQSET** LQFP-64 VINBUCK2 9 VINBUCK1 40 VINBUCK2 VINBUCK1 10 39 BS2 11 38 BS<sub>1</sub> 12 PHASE2 PHASE1 37 PHASE2 13 PHASE1 ENBUCK1 35 PGOV1 ENBUCK2 34 PGOV2 15 PGTH1 16 33 OCPSET1 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 BUF PGND2 PGND2 OCPSET2 PGND1

Figure 2. LQFP64 pinout (bottom view)

Table 2. LQFP64 pin list

GN

RESET

| N# | Pin name               | Pin type | Pin description                                                                                                                                                                             |  |

|----|------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1  | MODE                   | IN       | Working mode: Pin floating sets the working Mode to Normal; shorted to AGND sets the Microcontroller Mode.                                                                                  |  |

| 2  | PGDELAY2/<br>PWUPDELAY | IN       | DC/DC2 Power good output delay time adjustable by connecting a capacitor from PGDELAY2 to AGND. In Microcontroller Mode, a capacitor sets the power up delay, from reset to watchdog input. |  |

| 3  | COMP2                  | IN/OUT   | DC/DC2 Error amplifier output for compensation network connection.                                                                                                                          |  |

| 4  | FB2                    | IN/OUT   | DC/DC2 Output feedback. Connected to an error amplifier that compares the feedback voltage to the internal reference voltage.                                                               |  |

8/50 DS12453 Rev 2

GAPG1304151152PS

L5964 Pins description

Table 2. LQFP64 pin list (continued)

| N# | Pin name  | Pin type | Pin description                                                                                                                                                      |  |

|----|-----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 5  | SWGND1    | GROUND   | DC/DC analog blocks ground (Switching ground).                                                                                                                       |  |

| 6  | SWGND2    | GROUND   | DC/DC analog blocks ground (Switching ground).                                                                                                                       |  |

| 7  | FDIVISION | IN       | Frequency divider setting to make DC/DC2 working at a frequency that is 1/1, 1/2, 1/4 or 1/8 of DC/DC1 one. If connected to ground puts the device in Parallel Mode. |  |

| 8  | SUB       | GROUND   | Device substrate ground.                                                                                                                                             |  |

| 9  | VINBUCK2  | SUPPLY   | DC/DC2 power supply connection.                                                                                                                                      |  |

| 10 | VINBUCK2  | SUPPLY   | DC/DC2 power supply connection.                                                                                                                                      |  |

| 11 | BS2       | OUT      | Boot-strap capacitor connection for DC/DC2.                                                                                                                          |  |

| 12 | PHASE2    | OUT      | DC/DC2 power stage output (for external inductor and boot-strap capacitor connection).                                                                               |  |

| 13 | PHASE2    | OUT      | DC/DC2 power stage output (for external inductor and boot-strap capacitor connection).                                                                               |  |

| 14 | ENBUCK1   | IN       | DC/DC1 enable (active high).                                                                                                                                         |  |

| 15 | ENBUCK2   | IN       | DC/DC2 enable (active high).                                                                                                                                         |  |

| 16 | PGTH1     | IN       | Power good threshold setting for DC/DC1. Pin floating sets the threshold to 95% of Vout; shorted to AGND sets the threshold to 85% of Vout.                          |  |

| 17 | PGTH2     | IN       | Power good threshold setting for DC/DC2. Pin floating sets the threshold to 95% of Vout; shorted to AGND sets the threshold to 85% of Vout.                          |  |

| 18 | N.C.      | -        | Not Connected.                                                                                                                                                       |  |

| 19 | PGND2     | GROUND   | Power ground of DC/DC2. Connected to internal low-side source.                                                                                                       |  |

| 20 | PGND2     | GROUND   | Power ground of DC/DC2. Connected to internal low-side source.                                                                                                       |  |

| 21 | RESET     | OUT      | Reset signal to Microprocessor in Microcontroller Mode: in Normal mode is kept in high impedance state. Open-drain output.                                           |  |

| 22 | N.C.      | -        | Not Connected.                                                                                                                                                       |  |

| 23 | IGN_BUF   | OUT      | DC/DC1 status (ON/OFF) echo to Microprocessor in Microcontroller Mode: in Normal Mode is kept in high impedance. Open-drain output.                                  |  |

| 24 | N.C.      | -        | Not Connected.                                                                                                                                                       |  |

| 25 | N.C.      | -        | Not Connected.                                                                                                                                                       |  |

| 26 | UV2       | OUT      | Under-voltage DC/DC2 signal. Open-drain output.                                                                                                                      |  |

| 27 | N.C.      | -        | Not Connected.                                                                                                                                                       |  |

| 28 | UV1       | OUT      | Under-voltage DC/DC1 signal. Open-drain output.                                                                                                                      |  |

| 29 | PGND1     | GROUND   | Power ground of DC/DC1. Connected to internal low-side source.                                                                                                       |  |

| 30 | PGND1     | GROUND   | Power ground of DC/DC1. Connected to internal low-side source.                                                                                                       |  |

| 31 | N.C.      | -        | Not Connected.                                                                                                                                                       |  |

| 32 | OCPSET2   | IN       | Programmable OCP setting for DC/DC2. Pin floating sets the overcurrent threshold to 4A; shorted to AGND sets the threshold to 2 A.                                   |  |

DS12453 Rev 2 9/50

Pins description L5964

Table 2. LQFP64 pin list (continued)

| N# | Pin name | Pin type | Pin description                                                                                                                                |  |

|----|----------|----------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 33 | OCPSET1  | IN       | Programmable OCP setting for DC/DC1. Pin floating sets the overcurrent threshold to 4A; shorted to AGND sets the threshold to 2 A.             |  |

| 34 | PGOV2    | OUT      | Over-voltage DC/DC2 signal. Open-drain output.                                                                                                 |  |

| 35 | PGOV1    | OUT      | Over-voltage DC/DC1 signal. Open-drain output.                                                                                                 |  |

| 36 | PHASE1   | OUT      | DC/DC1 power stage output (for external inductor and boot-strap capacitor connection).                                                         |  |

| 37 | PHASE1   | OUT      | DC/DC1 power stage output (for external inductor and boot-strap capacitor connection).                                                         |  |

| 38 | BS1      | OUT      | Boot-strap capacitor connection for DC/DC1.                                                                                                    |  |

| 39 | VINBUCK1 | SUPPLY   | DC/DC1 power supply connection.                                                                                                                |  |

| 40 | VINBUCK1 | SUPPLY   | DC/DC1 power supply connection.                                                                                                                |  |

| 41 | FREQSET  | IN       | Programmable internal PWM frequency for DC/DC. Pin floating sets the frequency to 2M Hz; shorted to AGND sets the frequency to 250 kHz.        |  |

| 42 | TJTEST   | OUT      | Device junction temperature information.                                                                                                       |  |

| 43 | PGLDO    | OUT      | LDO regulator Power good output. Open-drain output.                                                                                            |  |

| 44 | FB1      | IN/OUT   | DC/DC1 Output feedback. Connected to error amplifier that compares the feedback voltage to the internal reference voltage.                     |  |

| 45 | COMP1    | IN/OUT   | DC/DC1 Error amplifier output for compensation network connection.                                                                             |  |

| 46 | PGTHLDO  | IN       | Power good threshold setting for LDO. Pin floating sets the threshold to 95% of VOUTLDO; shorted to AGND sets the threshold to 85% of VOUTLDO. |  |

| 47 | AGND     | GROUND   | Device analog ground.                                                                                                                          |  |

| 48 | SUB      | GROUND   | Device substrate ground.                                                                                                                       |  |

| 49 | TAB      | -        | Device slug connection.                                                                                                                        |  |

| 50 | N.C.     | -        | Not Connected.                                                                                                                                 |  |

| 51 | WDI      | IN       | Watchdog input from Microcontroller. Internal Pull Down.                                                                                       |  |

| 52 | FBLDO    | IN/OUT   | LDO regulator output feedback.                                                                                                                 |  |

| 53 | VOUTLDO  | OUT      | LDO regulator output.                                                                                                                          |  |

| 54 | VINLDO   | SUPPLY   | LDO regulator power supply.                                                                                                                    |  |

| 55 | VBAT     | SUPPLY   | Dedicated high voltage supply for reference blocks.                                                                                            |  |

| 56 | HSD_EN   | OUT      | Enable signal for external High Side switch (active low). Only active in microcontroller mode, high impedance in normal mode.                  |  |

| 57 | ENLPM    | IN       | Low Power Mode enable: pin floating enables the Low Power Mode; shorted to AGND disables the Low Power Mode.                                   |  |

| 58 | WAKEL    | IN       | Wake-up signal to enable DC/DC1 in OR internally with ENBUCK1 pin (ignored in Normal Mode, active low in Microcontroller Mode).                |  |

| 59 | ENLDO    | IN       | LDO regulator enable (active high).                                                                                                            |  |

L5964 Pins description

Table 2. LQFP64 pin list (continued)

| N# | Pin name              | Pin type | Pin description                                                                                                                                                                          |  |

|----|-----------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 60 | PGDELAYLDO            | IN       | LDO Power good output delay time adjustable by connecting a capacitor to AGND.                                                                                                           |  |

| 61 | SYNCOUT               | OUT      | xternal Switching clock output signal.                                                                                                                                                   |  |

| 62 | SYNCIN                | IN       | External clock input connection. Connect an external clock at SYNCIN for frequency synchronization.                                                                                      |  |

| 63 | N.C.                  | -        | Not Connected.                                                                                                                                                                           |  |

| 64 | PGDELAY1/<br>RSTDELAY | IN       | DC/DC1 Power good output delay time adjustable by connecting a capacitor from PGDELAY1 to AGND. In Microcontroller Mode, a capaci sets the power up delay, from reset to watchdog input. |  |

L5964 **Block diagram**

#### 3 **Block diagram**

Figure 3. Block diagram VBAT 3.3V SUPPLY BS2 VINLDO BANDGAP and BIAS VINBUCK2 - FBLDO Control and

Driver

Logic

BUCK 2 VOUTLDO SLOPE COMPENSATION PHASE2 0.9V ERROR AMPLIFIER Ą SOFT START PGND2 V to I 3.3V FB2 Ā 10µА COMP2 FREQSET osc 180° BS1 SYNCIN SYNC BLOCK VINBUCK1 SYNCOUT MUX Control and Driver FDIVISION Ą Logic BUCK 1 SLOPE COMPENSATION PHASE1 0.9V SOFT\_START PGND1 V to I FB1 COMP1 **10μA** PGTHLDO PGDELAY1/RSTDELAY PGDELAY2/PWUPDELAY Window Watchdog WDI PGLDO WAKEL ENLDO <2:1> PGOV1 PGOV2 ENBUCK1 UV1 UV2 ENBUCK2 PGTHLDO Logic Core PGTH1 Voltage Supervisor PGTH2 RESET OCPSET2 OCPSET1 ☐ HSD\_EN MODE [ **HSD** Driver 50Ω ENLPM Ł

GAPGPS03084

AGND

SWGND

#### **Application diagrams** 4

577

## 5 Electrical specifications

## 5.1 Absolute maximum ratings

Table 3. Absolute maximum ratings

| Pin name / symbol                                                                                       | Parameter                                                       | Value                    | Unit |

|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------------|------|

| VBAT, VINBUCK1,2,VINLDO,<br>PHASE1,2                                                                    | Maximum transient supply voltage                                | -0.3 to +40              | V    |

| ENBUCK2, WAKEL, ENLDO,<br>HSD_EN                                                                        | Enable pins voltage                                             | -0.3 to +40              | V    |

| ENBUCK1                                                                                                 | Enable pin voltage                                              | -0.3 to +4.6             | V    |

| PGND1/2, AGND, SWGND,<br>TAB                                                                            | Ground pins voltage                                             | -0.3 to +0.3             | V    |

| VOUTLDO, PGLDO,<br>PGOV1,2, UV1,2                                                                       | LDO regulator output, Power Good signals, under voltage signals | -0.3 to 12               | V    |

| BS1,2                                                                                                   | Boot-strap capacitor pins                                       | -0.3 to VINBUCK1,2 + 4.6 | V    |

| FB1, FB2, FBLDO, COMP1-2,<br>PGDELAY1-2, PGDELAYLDO                                                     | Regulators pins                                                 | -0.3 to +4.6             | V    |

| PGTHLDO, PGTH12, OCPSET12,FREQSET, SYNCIN, SYNCOUT, FDIVISION, TJTEST, RESET, MODE, WDI, IGN_BUF, ENLPM | Other I/O pins maximum voltage                                  | -0.3 to +4.6             | V    |

| T <sub>op</sub>                                                                                         | Operating ambient temperature range                             | -40 to +105              | °C   |

| T <sub>stg</sub>                                                                                        | Storage temperature range                                       | -55 to +150              | °C   |

| T <sub>j</sub>                                                                                          | Junction temperature                                            | 150                      | °C   |

## 5.2 Operating voltage

Table 4. Operating voltage

| Pin name / symbol                                                                                       | Parameter                                                       | Value                    | Unit |

|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------------|------|

| VBAT, VINBUCK1,2, VINLDO,<br>PHASE1,2                                                                   | Operating input voltage                                         | -0.3 to +26              | V    |

| ENBUCK2 WAKEL, ENLDO,<br>EN_HSD                                                                         | Enable pins voltage                                             | -0.3 to +26              | V    |

|                                                                                                         | Enable pin voltage in normal mode                               | -0.3 to +26              | V    |

| ENBUCK1                                                                                                 | Enable pin voltage in microcontroller mode                      | -0.3 to +5               | V    |

| VOUTLDO, PGLDO,<br>PGOV1,2, UV1,2                                                                       | LDO regulator output, Power Good signals, under voltage signals | -0.3 to 10               | >    |

| BS1,2                                                                                                   | Boot-strap capacitor pins                                       | -0.3 to VINBUCK1,2 + 3.6 | ٧    |

| FB1, FB2, FBLDO, COMP1,2,<br>PGDELAY1,2, PGDELAYLDO                                                     | Regulators pins                                                 | -0.3 to +3.6             | ٧    |

| PGTHLDO, PGTH12, OCPSET12,FREQSET,SYNC IN, SYNCOUT, FDIVISION, TJTEST, RESET, MODE, WDI, IGN_BUF, ENLPM | Other I/O pins operating voltage                                | -0.3 to +3.6             | ٧    |

| T <sub>op</sub>                                                                                         | Operating ambient temperature range                             | -40 to +105              | °C   |

| T <sub>stg</sub>                                                                                        | Storage temperature range                                       | -55 to +150              | °C   |

| Tj                                                                                                      | Junction temperature                                            | 150                      | °C   |

## 5.3 Thermal data

Table 5. Thermal data (LQFP64)

| Symbol                 | Parameter                           | Тур  | Max | Unit |

|------------------------|-------------------------------------|------|-----|------|

| R <sub>th j-case</sub> | Thermal resistance junction-to-case | 1.25 | 1.6 | °C/W |

DS12453 Rev 2 15/50

### 5.4 Electrical characteristics

$V_{VBAT}$  = 14.4 V,  $V_{INBUCK1/2}$  = 14.4 V,  $V_{VINLDO}$  = 14.4 V,  $T_{amb}$  = 25 °C unless otherwise specified.

**Table 6. Electrical characteristics**

| Symbol                                        | Parameter                             | Condition                                                                                                                                                                                            | Min | Тур  | Max | Unit |

|-----------------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| Battery Suppl                                 | у                                     |                                                                                                                                                                                                      |     |      |     |      |

| $V_{VBAT}$                                    | Battery voltage operating range       | -                                                                                                                                                                                                    | 3.3 | 14.4 | 26  | V    |

| I <sub>SHUTDOWN</sub>                         | Shutdown mode power supply current    | V <sub>VBAT</sub> =V <sub>VINLDO</sub> =V <sub>VINBUCK1</sub> =V <sub>VIBUCKN2</sub> =14.4V<br>V <sub>ENLDO</sub> = V <sub>ENBUCK1</sub> = V <sub>ENBUCKN2</sub> = Low;<br>V <sub>WAKEUP</sub> =High | -   | 3    | 5   | μΑ   |

| I <sub>STANDBY_LDO</sub>                      | LDO standby mode power supply current | $\begin{aligned} & V_{VBAT} = V_{VINLDO} = V_{VINBUCK1} = V_{VIBUCKN2} = 14.4V \\ = V_{ENLDO} \ , \\ & V_{ENBUCK1} = V_{ENBUCKN2} = Low; \ V_{WAKEUP} = \\ & High, \ No \ Load \end{aligned}$        | -   | 35   | 45  | μА   |

| OV <sub>VBAT,</sub>                           | Overvoltage lockout                   | V <sub>VBAT</sub> Rising                                                                                                                                                                             | 30  | 32   | 34  | ٧    |

| OV <sub>VNBUCK,</sub><br>OV <sub>VNLDO,</sub> | threshold                             | V <sub>VBAT</sub> Falling                                                                                                                                                                            | 28  | 30   | 32  | ٧    |

| Undervoltage lockout                          |                                       | V <sub>VBAT</sub> Rising                                                                                                                                                                             | 2.8 | 3    | 3.2 | ٧    |

| $UV_VBAT$                                     | threshold                             | V <sub>VBAT</sub> Falling                                                                                                                                                                            | 2.7 | 2.9  | 3.1 | ٧    |

| Buck converte                                 | ers Enable                            |                                                                                                                                                                                                      |     |      | •   |      |

|                                               |                                       | Normal mode                                                                                                                                                                                          |     |      |     |      |

| .,                                            | ENBUCK1/2 threshold,                  | V <sub>ENBUCK1/2</sub> Rising                                                                                                                                                                        | 1.5 | 1.7  | 1.9 | V    |

| $V_{EN1/2}$                                   | oscillator, BUCK On                   | V <sub>ENBUCK1/2</sub> Falling                                                                                                                                                                       | 1   | 1.3  | 1.6 | V    |

| I <sub>EN1/2_LEAKAGE</sub>                    | ENBUCK1/2 leakage current             | V <sub>ENBUCK1/2</sub> =14V                                                                                                                                                                          | -   | 1    | 2   | μA   |

|                                               |                                       | Microcontroller mode                                                                                                                                                                                 |     |      |     |      |

| En_Tmin                                       | High level duration of ENBUCK1 enable | -                                                                                                                                                                                                    | 20  | 70   | 150 | μs   |

| I <sub>EN1</sub>                              | ENBUCK1 leakage current               | -                                                                                                                                                                                                    | -   | 3.5  | 5   | μA   |

|                                               |                                       | WAKEL                                                                                                                                                                                                |     | •    | •   |      |

| $V_{WAKEL}$                                   | WAKEL Threshold,                      | WAKEL Falling                                                                                                                                                                                        | 0.8 | 1    | 1.3 | V    |

| ▼ WAKEL                                       | BUCK1 On                              | WAKEL Rising                                                                                                                                                                                         | 1.5 | 1.8  | 2.1 | V    |

| I <sub>WAKEL</sub>                            | WAKEL Leakage<br>Current              | WAKEL = 0 V                                                                                                                                                                                          | -   | 1.5  | 3   | μΑ   |

Table 6. Electrical characteristics (continued)

| Symbol                                      | Parameter                           | Condition                                                               | Min  | Тур  | Max | Unit |

|---------------------------------------------|-------------------------------------|-------------------------------------------------------------------------|------|------|-----|------|

| Buck converte                               | er                                  |                                                                         |      | ı    | ı   |      |

| V <sub>VIN1/2</sub><br>OVV <sub>IN1/2</sub> | Operating range                     | -                                                                       | 3.3  | -    | 26  | V    |

| HYS <sub>OVVinbuck</sub>                    | Hysteresis                          | -                                                                       | -    | 0.4  | -   | V    |

| LIV                                         | Undervoltage lockout                | V <sub>VINBUCK1/2</sub> Rising @ V <sub>out</sub> = 1.2 V               | 2.7  | 3.0  | 3.3 | V    |

| UV <sub>Vinbuck</sub>                       | threshold                           | V <sub>VINBUCK1/2</sub> Falling @ V <sub>out</sub> = 1.2 V              | 2.6  | 2.9  | 3.2 | V    |

| V <sub>FB1/2</sub> _VFB1/2                  | Feedback voltage                    | -                                                                       | 880  | 900  | 920 | mV   |

| $\Delta V_{LOADR}$                          | Load regulation                     | Load = 0.3 A to 1.5 A                                                   | -    | 0.1  | -   | mV   |

| ΔV <sub>LINER_VFB1/2</sub>                  | Line regulation                     | V <sub>VIN1/2</sub> = 3.3 V to 26 V                                     | -    | 0.1  | -   | mV   |

| ΔV <sub>FB1/2</sub> /                       | V <sub>FB1/2</sub> undershoot       | Load = 0.5 A ↔ 1.5 A, Δt = 10 μs                                        | -5   | -    | 5   | %    |

| V <sub>FB1/2</sub>                          | VFB1/2 undershoot                   | $V_{VIN1/2} = 8V \leftrightarrow 18 \text{ V}, \Delta t = 1 \text{ ms}$ | -5   | -    | 5   | %    |

| Ron <sub>HS</sub>                           | High side switch on resistance      | -                                                                       | -    | 90   | 110 | mΩ   |

| Ron <sub>LS</sub>                           | Low side switch on resistance       | -                                                                       |      | 70   | 90  | mΩ   |

| ΔV <sub>FBSWx</sub> / Δt                    | FB pin Slope at Turn-<br>on         | Soft start time related                                                 | -    | 1    | 2   | V/ms |

| Error amplifie                              | r                                   |                                                                         |      | •    | •   |      |

| g <sub>m</sub>                              | Error Amplifier<br>Transconductance | (1)                                                                     | -    | 1    | -   | mS   |

| Oscillator                                  |                                     |                                                                         | •    | •    | •   |      |

| •                                           | Free-run switching                  | FREQSET pin floating                                                    | 2    | 2.2  | 2.4 | MHz  |

| f <sub>OSC</sub>                            | frequency                           | FREQSET pin connected to AGND                                           | 0.24 | 0.27 | 0.3 | MHz  |

| Peak current                                | limit                               |                                                                         | •    | •    | •   |      |

|                                             | Switch peak current                 | OCPSET1/2 Floating                                                      | 3.7  | 4.8  | -   | Α    |

| IPEAK_LIMIT                                 | limit                               | OCPSET1/2 Connected to Ground <sup>(2)</sup>                            | 1.7  | 2    | -   | Α    |

| Low power m                                 | ode                                 | •                                                                       | •    | •    | •   |      |

| lq_LPM                                      | Total quiescent current             | Buck1 or Buck 2 on, no loads<br>240 kHz < f <sub>sw</sub> < 300 kHz     | -    | 100  | 150 | μA   |

| IY_LFIVI                                    | in low power mode                   | Buck1 and Buck 2 on, no loads<br>240 kHz < f <sub>sw</sub> < 300 kHz    | -    | 160  | 300 | μA   |

DS12453 Rev 2 17/50

Table 6. Electrical characteristics (continued)

| Symbol                                          | Parameter                     | Condition                              | Min | Тур | Max  | Unit |

|-------------------------------------------------|-------------------------------|----------------------------------------|-----|-----|------|------|

| Power Good a                                    | and Power Good Delay 1        | for BUCK1/2                            |     |     |      |      |

| <b>-</b>                                        | PGOV1/2 threshold as          | PGTH1/2 pin connected to AGND          | 80  | 85  | 92   | %    |

| TH <sub>PG1/2</sub>                             | FB Voltage Percentage         | PGTH1/2 pin Floating                   | 90  | 95  | 99.5 | %    |

| V <sub>PG1/2L</sub>                             | PGOV1/2 Voltage Low           | I <sub>PGOV1/2</sub> = 1 mA            | -   | 0.1 | 0.2  | V    |

| I <sub>PG1/2</sub> LEAKAGE                      | PGOV1/2 Leakage<br>Current    | V <sub>PGOV1/2</sub> = 5 V             | -   | -   | 1    | μA   |

| t <sub>PG1/2</sub>                              | Delay for reporting a fault   | C = 0pF on PGDELAY1,2 pin              | -   | 1   | -    | μs   |

| I <sub>PG_CHARGE</sub>                          | PGDELAY1/2 Charging current   |                                        | 7   | 10  | 13   | μA   |

| V <sub>THPGDLY1/2</sub>                         | PGDELAY1/2<br>Threshold       |                                        | 1.5 | 1.9 | 2.5  | V    |

| t <sub>PG1/2</sub>                              | Power Good Delay<br>Time      | 10                                     | 20  | 25  | μs   |      |

| OV and UV for                                   | r BUCK1/2 output volta        | ge                                     |     |     |      |      |

| TU                                              | OV Threshold as               | PGTH1/2 connect to ground              | 105 | 110 | 115  | %    |

| TH <sub>OV1/2</sub> Percentage of FB1/2 Voltage |                               | PGTH1/2 Floating                       | 115 | 120 | 125  | %    |

| HYS <sub>OV1/2</sub>                            | Hysteresis on OV1/2           | PGTH1/2 pin floating/connected to AGND | 4   | 6.5 | 8    | %    |

| t <sub>OV1/2_GLITCH</sub>                       | Glitch filter time for OV1/2  | -                                      | -   | 5   | -    | μs   |

| TH <sub>UV1/2</sub>                             | UV Threshold as<br>Percentage | PGTH1/2 Connect to Ground              | 72  | 80  | 84   | %    |

| 111UV1/2                                        | of FB1/2 Voltage              | PGTH1/2 Floating                       | 82  | 90  | 94   | %    |

| HYS <sub>UV1/2</sub>                            | Hysteresis on UV1/2           | PGTH1/2 pin floating/connected to AGND | -   | 2   | 4    | %    |

| V <sub>UV1/2L</sub>                             | UV1/2 Voltage Low             | I <sub>UV1/2</sub> = 1 mA              | -   | 0.1 | 0.2  | V    |

| I <sub>UV_LEAKAGE</sub>                         | UV1/2 Leakage<br>Current      | V <sub>UV1/2</sub> = 5 V               | -   | -   | 1    | μA   |

| t <sub>UV1/2_GLITCH</sub>                       | Glitch Filter Time for UV1/2  | -                                      | 5   | 6.5 | 10   | μs   |

| Synchronizati                                   | on                            |                                        |     |     | •    |      |

| f <sub>SYNC</sub>                               | Frequency Range               | 50% Duty-cycle Wave on SYNCIN Pin      | 125 | -   | 2300 | kHz  |

| -                                               | SYNCIN Low<br>Threshold       | -                                      | -   | -   | 0.8  | V    |

| -                                               | SYNCIN High<br>Threshold      | -                                      | 2   | -   | -    | V    |

| -                                               | SYNCIN Pin Current            | V <sub>SYNCIN</sub> = 3 V              | 4   | 6   | 7.5  | μΑ   |

Table 6. Electrical characteristics (continued)

| Symbol                    | Parameter                                                                | Condition                                                                              | Min               | Тур                                      | Max                 | Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------|------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FDIVISION Pir             | 1                                                                        | <u> </u>                                                                               | <u> </u>          |                                          |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                           |                                                                          | R <sub>FDI</sub> < 10 kΩ                                                               | Par               | allel M                                  | ode                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                           | Resistors connected to                                                   | 32 kΩ < R <sub>FDI</sub> <40 kΩ                                                        | f <sub>SWB</sub>  | f <sub>SWBUCK2</sub> =1*f <sub>SWI</sub> |                     | UCK1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| R <sub>FDI</sub>          | FDIVISON pin to set switching frequency of                               | 62 kΩ < R <sub>FDI</sub> <76 kΩ                                                        | f <sub>SWBU</sub> | <sub>JCK2</sub> =1                       | /2*f <sub>SWE</sub> | BUCK1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                           | DC/DC2                                                                   | 125 kΩ < R <sub>FDI</sub> <160 kΩ                                                      | f <sub>SWBL</sub> | BUCK1                                    |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                           |                                                                          | R <sub>FDI</sub> > 270 kΩ                                                              | f <sub>SWBL</sub> | <sub>JCK2</sub> =1                       | /8*f <sub>SWE</sub> | BUCK1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Thermal Shute             | down for BUCK1/2                                                         |                                                                                        | •                 |                                          |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TSD <sub>SWx</sub>        | Thermal shut-down temperature                                            | Temperature Rising                                                                     | 155               | 165                                      | 175                 | °C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Hys <sub>TSDSWx</sub>     | Hysteresis on thermal shutdown temperature                               | -                                                                                      | -                 | 8                                        | -                   | °C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |