### Rad-hard LVDS serializer

#### Ceramic Flat-48

The upper metallic lid is connected to pin 17

### **Features**

- 15 to 75 MHz shift clock support

- Fail-safe function

- 8 kV HBM on LVDS pins

- Power-down mode < 216 μW (max.)</li>

- · Cold sparing all pins

- Narrow bus reduces cable size and cost

- · Up to 1.575 Gbps throughput

- · Up to 197 Mbytes/s bandwidth

- 325 mV (typ.) LVDS swing

- PLL requires no external components

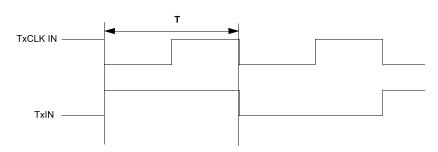

- · Rising edge strobe

- Operational environment: total dose irradiation testing to MIL-STD-883 method 1019

- Total dose: 300 krad (Si)

- Latch-up immune (LET > 120 MeV-cm2/mg)

- Compatible with ANSI/TIA/EIA-644 standard

### **Description**

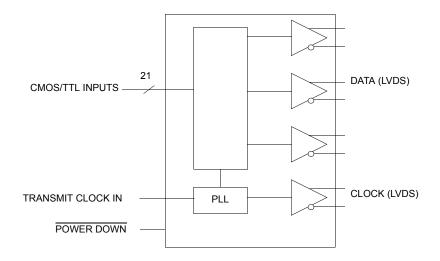

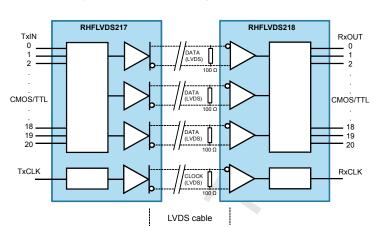

The RHFLVDS217 serializer converts 21 bits of CMOS/TTL data into three LVDS (low voltage differential signaling) data streams. A phase-locked transmitter clock is transmitted in parallel with the data streams over a fourth LVDS link. With every cycle of the transmitter clock, 21 bits of input data are sampled and transmitted.

At a transmitter clock frequency of 75 MHz, 21 bits of TTL data are transmitted at a rate of 525 Mbps per LVDS data channel. Using a 75 MHz clock, the data throughput is 1.575 Gbit/s (197 Mbytes/s).

The RHFLVDS217 serializer allows the use of wide, high speed TTL interfaces while reducing overall EMI and cable size.

All pins have cold spare buffers. These buffers are high impedance when  $V_{CC}$  is tied to 0 V.

### Product status link

RHFLVDS217

# 1 Functional description

Figure 1. RHFLVDS217 serializer functional block diagram

DS11557 - Rev 3 page 2/22

# 2 Pin configuration

**Table 1. Pin description**

| Pin name             | I/O | Number | Description                                                                                                     |

|----------------------|-----|--------|-----------------------------------------------------------------------------------------------------------------|

| TxIN                 | 1   | 21     | TTL level input                                                                                                 |

| TxOUT+               | 0   | 3      | Positive LVDS differential data output                                                                          |

| TxOUT-               | 0   | 3      | Negative LVDS differential data output                                                                          |

| TxCLK IN             | I   | 1      | TTL level clock input. The rising edge acts as data strobe. Pin name TxCLK IN                                   |

| TxCLK OUT+           | 0   | 1      | Positive LVDS differential clock output                                                                         |

| TxCLK OUT-           | 0   | 1      | Negative LVDS differential clock output                                                                         |

| PWR DWN              | I   | 1      | TTL level input. Assertion (low input) TRISTATEs the clock and data outputs, ensuring low current at power down |

| V <sub>CC</sub>      | ı   | 4      | Power supply pins for TTL inputs and logic                                                                      |

| GND                  | 1   | 5      | Ground pins for TTL inputs and logic                                                                            |

| PLL V <sub>CC</sub>  | 1   | 1      | Power supply pins for PLL                                                                                       |

| PLL GND              | 1   | 2      | Ground pins for PPL                                                                                             |

| LVDS V <sub>CC</sub> | I   | 1      | Power supply pin for LVDS output                                                                                |

| LVDS GND             | 1   | 3      | Ground pins for LVDS outputs                                                                                    |

Figure 2. RHFLVDS217 pinout

| TxIN4           | 1  |            | 48 | TxIN3                   |

|-----------------|----|------------|----|-------------------------|

| V <sub>DD</sub> | 2  |            | 47 | TxIN2                   |

| TxIN5           | 3  |            | 46 | GND                     |

| TxIN6           | 4  |            | 45 | TxIN1                   |

| GND             | 5  |            | 44 | TxIN0                   |

| TxIN7           | 6  |            | 43 | N/C                     |

| TxIN8           | 7  | RHFLVDS217 | 42 | LVDS GND                |

| V <sub>DD</sub> | 8  |            | 41 | TxOUT0-                 |

| TxIN9           | 9  |            | 40 | TxOUT0+                 |

| TxIN10          | 10 |            | 39 | TxOUT1-                 |

| GND             | 11 |            | 38 | TxOUT1+                 |

| TxIN11          | 12 |            | 37 | LVDS V <sub>DD</sub>    |

| TxIN12          | 13 |            | 36 | LVDS GND                |

| $V_{DD}$        | 14 |            | 35 | TxOUT2-                 |

| TxIN13          | 15 |            | 34 | TxOUT2+                 |

| TxIN14          | 16 |            | 33 | TxCLK OUT-              |

| GND             | 17 |            | 32 | TxCLK OUT+              |

| TxIN15          | 18 |            | 31 | _LVDS GND               |

| TxIN16          | 19 |            | 30 | PLL GND                 |

| TxIN17          | 20 |            | 29 | <br>PLL V <sub>DD</sub> |

| V <sub>DD</sub> | 21 |            | 28 | PLL GND                 |

| TxIN18          | 22 |            | 27 | PWR DWN                 |

| TxIN19          | 23 |            | 26 | TxCLK IN                |

| GND             | 24 |            | 25 | TxIN20                  |

DS11557 - Rev 3 page 3/22

# 3 Typical application

Figure 3. RHFLVDS217 typical application

DS11557 - Rev 3 page 4/22

### 4 Absolute maximum ratings and operating conditions

Stresses outside the listed absolute maximum ratings may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions beyond the limits indicated in the operational sections of this specification are not recommended. Exposure to absolute maximum rating conditions for extended periods may affect device reliability and performance.

Table 2. Absolute maximum ratings (references to GND)

| Symbol            | Pa                                      | arameter                     | Value | Unit |  |

|-------------------|-----------------------------------------|------------------------------|-------|------|--|

| V <sub>CC</sub>   | Supply voltage (1)                      | Supply voltage (1)           |       |      |  |

| Vi                | TTL inputs (operating or cold-spare)    | -0.3 to 4.8                  | V     |      |  |

| T <sub>stg</sub>  | Storage temperature range               | -65 to 150                   | °C    |      |  |

| Tj                | Maximum junction temperature            | 150                          | C     |      |  |

| R <sub>thjc</sub> | Thermal resistance junction to case (2) |                              | 10    | °C/W |  |

|                   | LIPM: human hady model                  | All pins except LVDS outputs | 2     | kV   |  |

| ESD               | HBM: human body model                   | 8                            | N.V   |      |  |

|                   | CDM: charge device model                |                              |       | V    |  |

<sup>1.</sup> All voltages, except the differential I/O bus voltage, are with respect to the network ground terminal.

Table 3. Recommended operating conditions (referenced to GND)

| Symbol          | Parameter                            |     | Тур. | Max. | Unit |

|-----------------|--------------------------------------|-----|------|------|------|

| V <sub>CC</sub> | Supply voltage                       | 3   | 3.3  | 3.6  | V    |

| V <sub>IN</sub> | Driver DC input voltage (TTL inputs) | 0   |      | VCC  | V    |

| T <sub>A</sub>  | Ambient temperature range            | -55 |      | 125  | °C   |

DS11557 - Rev 3 page 5/22

<sup>2.</sup> Test per MIL-STD-883, method 1012. Short-circuits can cause excessive heating. Destructive dissipation can result from short-circuits on the amplifiers.

### 5 Electrical characteristics

In Table 4. DC electrical characteristics,  $V_{CC}$  = 3 V to 3.6 V, - 55 °C <  $T_A$  < 125 °C, unless otherwise specified,  $T_A$  is per the temperature noted. Current into device pins is defined as positive. Current out of device pins is defined as negative. All voltages are referenced to ground.

Table 4. DC electrical characteristics

| Symbol                         | Parameter                                                     | Conditions                                                                                                              | Min.  | Max.            | Unit |

|--------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------|-----------------|------|

|                                |                                                               | CMOS/TTL DC specifications                                                                                              |       |                 |      |

| V <sub>IH</sub>                | High-level input voltage                                      |                                                                                                                         | 2.0   | V <sub>CC</sub> | V    |

| V <sub>IL</sub>                | Low-level input voltage                                       | _ow-level input voltage                                                                                                 |       | 0.8             | V    |

| I <sub>IH</sub>                | High-level input current                                      | High-level input current $V_{IN} = 3.6 \text{ V}, V_{CC} = 3.6 \text{ V}$                                               |       | 10              |      |

| I <sub>IL</sub>                | Low-level input current                                       | V <sub>IN</sub> = 0 V, V <sub>CC</sub> = 3.6 V                                                                          | -10   | 10              | μA   |

| V <sub>CL</sub>                | Input clamp voltage                                           | I <sub>CL</sub> = -18 mA                                                                                                |       | -1.5            | V    |

| I <sub>CS</sub>                | Cold spare leakage current                                    | V <sub>IN</sub> = 3.6V, V <sub>CC</sub> = 0 V                                                                           | -20   | 20              | μA   |

|                                | LVDS                                                          | S output DC specifications (OUT+, OUT-)                                                                                 |       |                 |      |

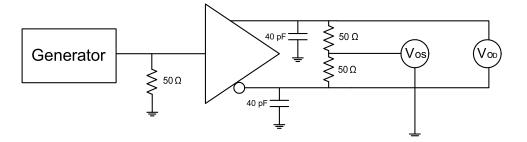

| V <sub>OD</sub> <sup>(1)</sup> | Differential output voltage                                   | R <sub>L</sub> = 100 ohm (see Figure 14. Driver V <sub>OD</sub> and V <sub>OS</sub> test circuit or equivalent circuit) | 250   | 400             | mV   |

| DV <sub>OD</sub> (1)           | Change in V <sub>OD</sub> between complimentary output states | , 52                                                                                                                    |       | 35              | IIIV |

| V <sub>OS</sub> (1)            | Offset voltage                                                | $R_L = 100 \text{ ohm}, V_{OS} = (V_{OH} + V_{OL})/2$                                                                   | 1.125 | 1.450           | V    |

| DV <sub>OS</sub> (1)           | Change in V <sub>OS</sub> between complimentary output states | R <sub>L</sub> = 100ohm                                                                                                 |       | 35              | mV   |

| I <sub>OZ</sub>                | Output three-state current                                    | PWR DWN = 0 V<br>V <sub>OUT</sub> = 0 V or V <sub>CC</sub>                                                              | -10   | 10              | μA   |

| I <sub>OS</sub> (2)            | Output short circuit current                                  | V <sub>OUT</sub> + or V <sub>OUT</sub> - = 0 V                                                                          | 3.5   | 9               | mA   |

| I <sub>CSOUT</sub>             | Cold spare leakage current                                    | V <sub>IN</sub> = 3.6 V, V <sub>CC</sub> = 0 V                                                                          | -20   | 20              | μA   |

|                                |                                                               | Supply current                                                                                                          |       |                 |      |

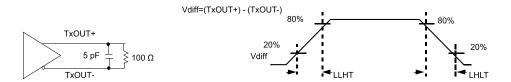

| I <sub>CCL</sub>               | Transmitter supply current with loads                         | $R_L$ = 100 ohm all channels $C_L$ = 5 pF, f = 50 MHz, (see Figure 5. RHFLVDS217 output load and transition times)      |       | 65              | mA   |

| I <sub>CCZ</sub>               | Power down current                                            | D <sub>IN</sub> = V <sub>CC</sub> or 0 V, PWR DWN = 0 V, f = 0 Hz                                                       |       | 200             | μA   |

<sup>1.</sup> Clock outputs guaranteed by design.

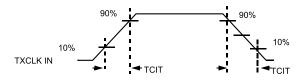

In Table 5. AC switching characteristics,  $V_{CC}$  = 3 V to 3.6 V, - 55 °C <  $T_A$  < 125 °C, unless otherwise specified,  $T_A$  is per the temperature noted. For devices procured with a total ionizing dose tolerance guarantee, the post-irradiation performance is guaranteed at 25 °C per MIL-STD-883 Method 1019, condition A up to the maximum TID level procured. The recommend transition time for TXCLK In is 1.0 to 6.0 ns (see Figure 6. RHFLVDS217 input clock transition time)

DS11557 - Rev 3 page 6/22

Output short-circuit current (I<sub>OS</sub>) is specified as magnitude only, minus sign indicates direction only. Only one output should be shorted at a time, for a maximum duration of one second.

Table 5. AC switching characteristics

| Symbol       | Parameter                                                                                                             | Min.                  | Max.                  | Unit |

|--------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|------|

| LLHT (1)     | LVDS low-to-high transition time (seeFigure 5. RHFLVDS217 output load and transition times )                          |                       | 1.5                   |      |

| LHLT (1)     | LVDS high-to-low transition time (see Figure 5. RHFLVDS217 output load and transition times )                         |                       | 1.5                   |      |

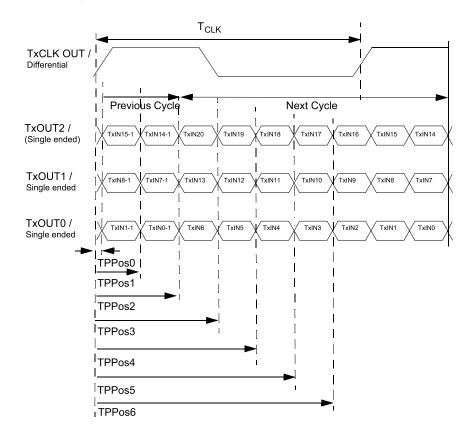

| TPPos0 (1)   | Transmitter output pulse position for bit 0 (see Figure 13. RHFLVDS217 output pulse position measurement), f = 50 MHz | 0.07                  | 0.24                  |      |

| 111 030 17   | Transmitter output pulse position for bit 0 (see Figure 13. RHFLVDS217 output pulse position measurement), f = 75 MHz | 0.08                  | 0.30                  |      |

| TPPos1 (1)   | Transmitter output pulse position for bit 0 (see Figure 13. RHFLVDS217 output pulse position measurement), f = 50 MHz | 2.84                  | 3.26                  |      |

| 111031       | Transmitter output pulse position for bit 0 (see Figure 13. RHFLVDS217 output pulse position measurement), f = 75 MH  | 1.98                  | 2.30                  |      |

| TPPos2 (1)   | Transmitter output pulse position for bit 0 (see Figure 13. RHFLVDS217 output pulse position measurement), f = 50 MHz | 5.63                  | 5.98                  |      |

| 111032       | Transmitter output pulse position for bit 0 (see Figure 13. RHFLVDS217 output pulse position measurement), f = 75 MHz | 3.85                  | 4.13                  |      |

| TPPos3 (1)   | Transmitter output pulse position for bit 0 (see Figure 13. RHFLVDS217 output pulse position measurement), f = 50 MHz | 8.58                  | 9.07                  |      |

| 111030       | Transmitter output pulse position for bit 0 (see Figure 13. RHFLVDS217 output pulse position measurement), f = 75 MHz | 5.79                  | 6.14                  |      |

| TPP0s4 (1)   | Transmitter output pulse position for bit 0 (see Figure 13. RHFLVDS217 output pulse position measurement), f = 50 MHz | 11.14                 | 11.66                 |      |

| 1111034      | Transmitter output pulse position for bit 0 (see Figure 13. RHFLVDS217 output pulse position measurement), f = 75 MHz | 7.54                  | 7.89                  | ns   |

| TPP0s5 (1)   | Transmitter output pulse position for bit 0 (see Figure 13. RHFLVDS217 output pulse position measurement), f = 50 MHz | 14.20                 | 14.54                 | 113  |

| 177053       | Transmitter output pulse position for bit 0 (see Figure 13. RHFLVDS217 output pulse position measurement), f = 75 MHz | 9.52                  | 9.78                  |      |

| TPP0s6 (1)   | Transmitter output pulse position for bit 0 (see Figure 13. RHFLVDS217 output pulse position measurement), f = 50 MHz | 17.00                 | 17.46                 |      |

| 177050       | Transmitter output pulse position for bit 0 (see Figure 13. RHFLVDS217 output pulse position measurement), f = 75 MHz | 11.41                 | 11.76                 |      |

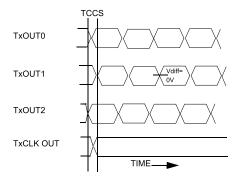

| TCCS (2)     | Channel-to-channel skew (see Figure 7. RHFLVDS217 channel-to-channel skew), f = 75 MHz                                |                       | 0.45                  |      |

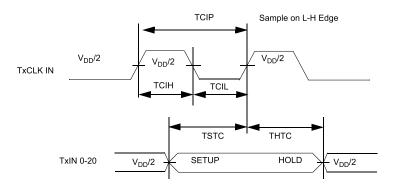

| TCIP (1) (2) | TxCLK IN period (see Figure 8. RHFLVDS217 setup/hold and high/low times)                                              | 13.3                  | 66.7                  |      |

| TCIH (3) (2) | TxCLK IN high time (see Figure 8. RHFLVDS217 setup/hold and high/low times)                                           | 0.35 T <sub>cip</sub> | 0.65 T <sub>cip</sub> |      |

| TCIL (2) (3) | TxCLK IN low time (see Figure 8. RHFLVDS217 setup/hold and high/low times)                                            | 0.35 T <sub>cip</sub> | 0.65 T <sub>cip</sub> |      |

| TSTC (1) (2) | TxIN setup to TxCLK IN (see Figure 8. RHFLVDS217 setup/hold and high/low times), 15 MHz                               | 1.0                   |                       |      |

| 1310 (17 (2) | TxIN setup to TxCLK IN (see Figure 8. RHFLVDS217 setup/hold and high/low times), 75 MHz                               | 0.5                   |                       |      |

| THTC (1) (2) | TxIN hold to TxCLK IN (see Figure 8. RHFLVDS217 setup/hold and high/low times), 15 MHz                                | 0.7                   |                       |      |

| INIC (*/ (=/ | TxIN hold to TxCLK IN (see Figure 8. RHFLVDS217 setup/hold and high/low times), 75 MHz                                | 0.5                   |                       |      |

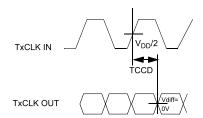

| TCCD (2)     | TxCLK IN to TxCLK OUT delay (see Figure 9. RHFLVDS217 clock-to-clock out delay)                                       | 0.5                   | 3                     |      |

| Symbol        | Parameter                                                                            | Min. | Max. | Unit |

|---------------|--------------------------------------------------------------------------------------|------|------|------|

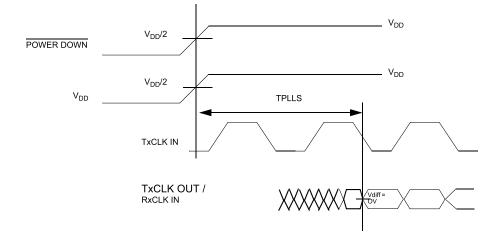

| TPLLS (4) (2) | Transmitter phase lock loop set (see Figure 10. RHFLVDS217 phase-lock-loop set time) |      | 10   | ms   |

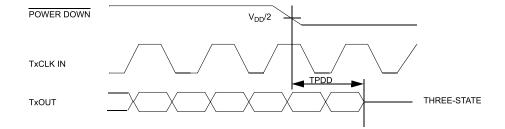

| TPDD          | Transmitter power down delay (see Figure 12. Transmitter power-down delay)           |      | 100  | μs   |

- 1. Guaranteed by characterization.

- 2. Recommended transition time for TxCLK IN is 1 to 6 ns (see Figure 6. RHFLVDS217 input clock transition time)

- 3. Guaranteed by design

- 4. Functionally tested

### **Cold sparing**

The RHFLVDS217 features a cold spare input and output buffer. In high reliability applications, cold sparing enables a redundant device to be tied to the data bus with its power supply at 0 V (VCC = GND) without affecting the bus signals or injecting current from the I/Os to the power supplies. Cold sparing also allows redundant devices to be kept powered off so that they can be switched on only when required. This has no impact on the application. Cold sparing is achieved by implementing a high impedance between the I/Os and VCC. ESD protection is ensured through a non-conventional dedicated structure.

#### Fail-safe

In many applications, inputs need a fail-safe function to avoid an uncertain output state when the inputs are not connected properly. In case of TTL floating inputs, the LVDS outputs remain in a stable logic-high state.

DS11557 - Rev 3 page 8/22

### 6 Radiations

### Total dose (MIL-STD-883 TM 1019)

The products guaranteed in radiation within the RHA QML-V system fully comply with the MIL-STD-883 TM 1019 specification.

The RHFLVDS217 is RHA QML-V, tested and characterized in full compliance with the MIL-STD-883 specification, between 50 and 300 rad/s only (full CMOS technology).

All parameters provided in Table 4. DC electrical characteristics apply to both pre- and post-irradiation, as follows:

- All tests are performed in accordance with MIL-PRF-38535 and test method 1019 of MIL-STD-883 for total ionizing dose (TID).

- · The initial characterization is performed in qualification only on both biased and unbiased parts.

- Each wafer lot is tested at high dose rate only, in the worst bias case condition, based on the results obtained during the initial qualification.

### **Heavy-ions**

The behavior of the product when submitted to heavy-ions is not tested in production. Heavy-ion trials are performed on qualification lots only.

| Tab | le 6. | Radiation |

|-----|-------|-----------|

|     |       |           |

| Туре               | Characteristics                                                                                                        | Value | Unit          |

|--------------------|------------------------------------------------------------------------------------------------------------------------|-------|---------------|

| TID <sup>(1)</sup> | High-dose rate (50 - 300 rad/s) up to:                                                                                 |       | krad          |

| Heavy-ions         | SEL <sup>(2)</sup> immune up to:<br>(with a particle angle of 60 ° at 125 °C) and a fluence of 1e+7 cm <sup>-2</sup> ) | 120   | MeV.cm²/mg    |

| i icavy-ioris      | SEL <sup>(2)</sup> immune up to:<br>(with a particle angle of 0 ° at 125 °C) and a fluence of 1e+7 cm <sup>-2</sup> )  | 60    | wev.dii /ilig |

- 1. A total ionizing dose (TID) of 300 krad(Si) is equivalent to 3000 Gy(Si), (1 gray = 100 rad).

- 2. SEL: single event latch-up.

DS11557 - Rev 3 page 9/22

## 7 Test circuit and AC timing diagrams

Figure 4. Test pattern

Figure 5. RHFLVDS217 output load and transition times

Figure 6. RHFLVDS217 input clock transition time

Figure 7. RHFLVDS217 channel-to-channel skew

- Measurements at V<sub>DIFF</sub> = 0 V

- 2. TCCS measured between earliest and latest LVDS edges

- 3. TxCLK differential low-high edge

DS11557 - Rev 3 page 10/22

Figure 8. RHFLVDS217 setup/hold and high/low times

Figure 9. RHFLVDS217 clock-to-clock out delay

Figure 10. RHFLVDS217 phase-lock-loop set time

DS11557 - Rev 3 page 11/22

TxCLK OUT / RxCLK IN Next Cycle Previous Cycle TxOUT2 / TxIN15-1 TxIN14-1 TxIN19 TxIN18 TxIN17 TxIN16 RxIN2 TxOUT1/ TxIN8-1 TxIN7 TxIN7-1 TxIN13 TxIN12 TxIN11 TxIN10 TxIN9 TxIN8 RxIN1

Figure 11. RHFLVDS217 parallel TTL data inputs mapped to LVDS outputs

TxIN5

TxIN4

TxIN3

TxIN2

TxIN1

TxIN0

TxOUT0 /

RxIN0

TxIN1-1

TxIN0-1

DS11557 - Rev 3 page 12/22

Figure 13. RHFLVDS217 output pulse position measurement

Figure 14. Driver  $V_{\mbox{\scriptsize OD}}$  and  $V_{\mbox{\scriptsize OS}}$  test circuit or equivalent circuit

DS11557 - Rev 3 page 13/22

## 8 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: www.st.com. ECOPACK® is an ST trademark.

### 8.1 Ceramic Flat-48 package information

(N-2 places)

Pin 1 identifier

(N-2 places)

(N places)

(A places)

(A places)

Figure 15. Ceramic Flat-48 package outline

1. The upper metallic lid is connected to pin 17.

DS11557 - Rev 3 page 14/22

Table 7. Ceramic Flat-48 mechanical data

| Dim.   |       | mm    |       | Inches |       |       |  |

|--------|-------|-------|-------|--------|-------|-------|--|

| Dilli. | Тур   | Min.  | Max.  | Тур.   | Min.  | Max.  |  |

| Α      | 2.47  | 2.18  | 2.72  | 0.097  | 0.086 | 0.107 |  |

| b      | 0.254 | 0.20  | 0.30  | 0.010  | 0.008 | 0.012 |  |

| С      | 0.15  | 0.12  | 0.18  | 0.006  | 0.005 | 0.007 |  |

| D      | 15.75 | 15.57 | 15.92 | 0.620  | 0.613 | 0.627 |  |

| E      | 9.65  | 9.52  | 9.78  | 0.380  | 0.375 | 0.385 |  |

| E2     | 6.35  | 6.22  | 6.48  | 0.250  | 0.245 | 0.255 |  |

| E3     | 1.65  | 1.52  | 1.78  | 0.065  | 0.060 | 0.070 |  |

| е      | 0.635 |       |       | 0.025  |       |       |  |

| f      | 0.20  |       |       | 0.008  |       |       |  |

| L      | 8.38  | 6.85  | 9.40  | 0.330  | 0.270 | 0.370 |  |

| Q      | 0.79  | 0.66  | 0.92  | 0.031  | 0.026 | 0.036 |  |

| S1     | 0.43  | 0.25  | 0.61  | 0.017  | 0.010 | 0.024 |  |

### 9 Ordering information

Table 8. Order code

| Order code     | SMD <sup>(1)</sup> | Quality level     | Temp.<br>range | Mass   | Package  | Lead<br>finish | Marking <sup>(2)</sup> | Packing    |

|----------------|--------------------|-------------------|----------------|--------|----------|----------------|------------------------|------------|

| RHFLVDS217K1   | -                  | Engineering model | -55 to         | 1.22 g | Flat-48  | Gold           | RHFLVDS217K1           | Conductive |

| RHFLVDS217K01V | 5962F01534         | QML-V flight      | +125 °C        | 1.22 g | 1 lat-40 | Gold           | 5962F0153403VYC        | strip pack |

- 1. Standard microcircuit drawing.

- 2. Specific marking only. Complete marking includes the following:

- ST logo

- Date code (date the package was sealed) in YYWWA (year, week, and lot index of week)

- Country of origin (FR = France)

Note: Contact your ST sales office for information about the specific conditions for products in die form.

### Other information

### Date code:

The date code is structured as engineering model: EM xyywwz

#### Where

x = 3 (EM only), assembly location Rennes (France)

yy = last two digits of the year

ww = week digits

z = lot index of the week

### **Product documentation**

Each product shipment includes a set of associated documentation within the shipment box. This documentation depends on the quality level of the products, as detailed in the table below.

The certificate of conformance is provided on paper whatever the quality level. For QML parts, complete documentation, including the certificate of conformance, is provided on a CDROM.

**Table 9. Product documentation**

| Quality level     | Item                                      |  |  |  |  |

|-------------------|-------------------------------------------|--|--|--|--|

|                   | Certificate of conformance including :    |  |  |  |  |

|                   | Customer name                             |  |  |  |  |

|                   | Customer purchase order number            |  |  |  |  |

|                   | ST sales order number and item            |  |  |  |  |

| Engineering model | ST part number                            |  |  |  |  |

| Engineering model | Quantity delivered                        |  |  |  |  |

|                   | Date code                                 |  |  |  |  |

|                   | Reference to ST datasheet                 |  |  |  |  |

|                   | Reference to TN1181 on engineering models |  |  |  |  |

|                   | ST Rennes assembly lot ID                 |  |  |  |  |

DS11557 - Rev 3 page 16/22

| Quality level | Item                                                   |

|---------------|--------------------------------------------------------|

|               | Certificate of Conformance including:                  |

|               | Customer name                                          |

|               | Customer purchase order number                         |

|               | ST sales order number and item                         |

|               | ST part number                                         |

|               | Quantity delivered                                     |

|               | Date code                                              |

|               | Serial numbers                                         |

|               | Group C reference                                      |

| QML-V Flight  | Group D reference                                      |

|               | Reference to the applicable SMD                        |

|               | ST Rennes assembly lot ID                              |

|               | Quality control inspection (groups A, B, C, D, E)      |

|               | Screening electrical data in/out summary               |

|               | Precap report                                          |

|               | PIND (particle impact noise detection) test            |

|               | SEM (scanning electronic microscope) inspection report |

|               | X-ray plates                                           |

DS11557 - Rev 3 page 17/22

## **Revision history**

Table 10. Document revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 08-Apr-2016 | 1        | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 03-Oct-2016 | 2        | Status of datasheet changed from "preliminary data" to "production data".  Added order code RHFLVDS217K01V to Table 1: "Device summary"  Table 3: "Absolute maximum ratings (references to GND)": updated Rthjc value from 22 °C/W to 10 °C/W; updated footnote 2.  Table 5: "DC electrical characteristics": updated ICCZ condition; updated footnotes.  Table 6: "AC switching characteristics": updated footnotes  Added order code RHFLVDS217K01V to Table 9: "Order codes" |

| 04-Jul-2018 | 3        | Updated Section 5 Electrical characteristics, Section 6 Radiations and Section 9 Ordering information.                                                                                                                                                                                                                                                                                                                                                                          |

## **Contents**

| 1   | Functional description                            | 2  |

|-----|---------------------------------------------------|----|

| 2   | Pin configuration                                 | 3  |

| 3   | Typical application                               | 4  |

| 4   | Absolute maximum ratings and operating conditions | 5  |

| 5   | Electrical characteristics                        | 6  |

| 6   | Radiations                                        | 9  |

| 7   | Test circuit and AC timing diagrams               | 10 |

| 8   | Package information                               | 14 |

|     | 8.1 Ceramic Flat-48 package information           | 14 |

| 9   | Ordering information                              | 16 |

| Rev | vision history                                    | 18 |

## **List of tables**

| Table 1.  | Pin description                                      |

|-----------|------------------------------------------------------|

| Table 2.  | Absolute maximum ratings (references to GND)         |

| Table 3.  | Recommended operating conditions (referenced to GND) |

| Table 4.  | DC electrical characteristics                        |

| Table 5.  | AC switching characteristics                         |

| Table 6.  | Radiation                                            |

| Table 7.  | Ceramic Flat-48 mechanical data                      |

| Table 8.  | Order code                                           |

| Table 9.  | Product documentation                                |

| Table 10. | Document revision history                            |

# **List of figures**

| Figure 1.  | RHFLVDS217 serializer functional block diagram                                | . 2 |

|------------|-------------------------------------------------------------------------------|-----|

| Figure 2.  | RHFLVDS217 pinout                                                             | . 3 |

| Figure 3.  | RHFLVDS217 typical application                                                | . 4 |

| Figure 4.  | Test pattern                                                                  | 10  |

| Figure 5.  | RHFLVDS217 output load and transition times                                   | 10  |

| Figure 6.  | RHFLVDS217 input clock transition time                                        | 10  |

| Figure 7.  | RHFLVDS217 channel-to-channel skew                                            | 10  |

| Figure 8.  | RHFLVDS217 setup/hold and high/low times                                      | 11  |

| Figure 9.  | RHFLVDS217 clock-to-clock out delay                                           | 11  |

| Figure 10. | RHFLVDS217 phase-lock-loop set time                                           | 11  |

| Figure 11. | RHFLVDS217 parallel TTL data inputs mapped to LVDS outputs                    | 12  |

| Figure 12. | Transmitter power-down delay                                                  | 12  |

| Figure 13. | RHFLVDS217 output pulse position measurement                                  | 13  |

| Figure 14. | Driver V <sub>OD</sub> and V <sub>OS</sub> test circuit or equivalent circuit | 13  |

| Figure 15. | Ceramic Flat-48 package outline                                               | 14  |

### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2018 STMicroelectronics - All rights reserved

DS11557 - Rev 3 page 22/22