# L9177

Datasheet - production data

# Peripheral on chip for low end engine control

## Features

- Supply voltage from 6 V to 18 V

- Basic functionality guaranteed down to 3.9 V

- 5 V regulator up to 300 mA with thermal shutdown protection in current limitation condition

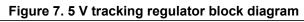

- 5 V tracking regulator up to 40 mA and short to battery protection

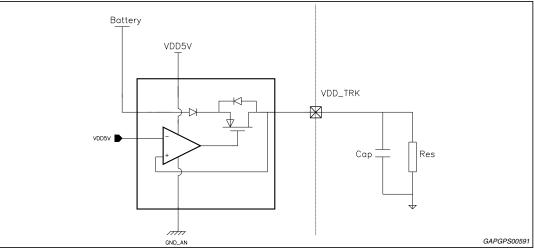

- 5 V standby regulator up to 2.5 mA

- 2 channels injectors drivers

- Parallel and serial driving

- Output internally clamped to 60 V

- Minimum overcurrent at 2.8 A

- Ron 0.6 Ω worst case (at  $T_i = 150$  °C)

- 3 relay drivers

- 2 with parallel and serial driving, 1 with serial driving

- Output internally clamped to 45 V

- Minimum guaranteed output current 1 A

- Ron 1.5 Ω worst case (at T<sub>i</sub> = 150 °C)

- Tachometer driver

- Parallel and serial driving

- Minimum guaranteed output current 25 mA

- Ron 5  $\Omega$  worst case (at T<sub>i</sub> = 150 °C)

- Lamp driver

- Serial driving

- Output internally clamped to 45 V

- Minimum guaranteed output current 1 A (2 A during in-rush)

- Ron 1.5 Ω worst case (at T<sub>i</sub> = 150 °C)

- Stepper motor driver

- Parallel driving

- Minimum guaranteed output current 500 mA - full step

- Ron 2.6 Ω worst case on the diagonal (at T<sub>j</sub> = 150 °C)

- O2 sensor heater

- Parallel and serial driving

- Output internally clamped to 45 V

- Minimum guaranteed output current 3 A

- Ron 0.5 Ω worst case (at T<sub>j</sub> = 150 °C)

- Protected high side driver

- 100 mA min. current limitation threshold

- Full diagnosis by SPI

- Injector driver: OL, STG, OC

- Relay and Lamp drivers: OL, STG, OC

- O2 sensor heater: OL, STG, OC

- Tachometer: OL, STG, OC

- Stepper motor driver: OL, STG, STB, OC

- general diagnostic: over-temperature

- Protection for STB, STG (for stepper motor drivers and tracking regulator)

- Self configuring variable reluctance sensor interface

- K-line transceiver

- Microcontroller reset logic

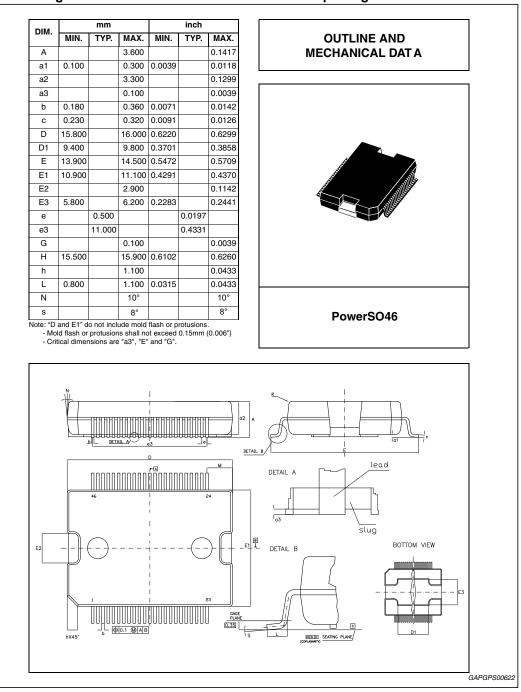

- Packaged in PowerSO46

#### Table 1. Device summary

| Order code | Package    | Packing       |

|------------|------------|---------------|

| L9177      | PowerSO46  | Tube          |

| L9177TR    | 1 00013040 | Tape and reel |

November 2013

DocID17617 Rev 1

This is information on a product in full production.

1/49

# Contents

| 1    | Dese | cription  |                                      | 6        |

|------|------|-----------|--------------------------------------|----------|

| 2    | Bloc | k diagra  | m and pin description                | 7        |

|      | 2.1  | Block o   | liagram                              | 7        |

|      | 2.2  | Pin des   | scription                            | 8        |

| 3    | Elec | trical sp | ecifications                         | 10       |

|      | 3.1  | Operat    | ing range                            | 10       |

|      | 3.2  | Absolu    | te maximum ratings                   |          |

|      | 3.3  | Latch-ι   | ıp test                              |          |

|      | 3.4  | Tempe     | rature ranges and thermal data       |          |

|      | 3.5  | -         | al characteristics                   |          |

|      |      | 3.5.1     | Supply                               |          |

|      |      | 3.5.2     | Кеу                                  |          |

|      |      | 3.5.3     | Digital pins                         |          |

|      |      | 3.5.4     | Digital output pins                  |          |

|      |      | 3.5.5     | 5 V voltage regulator                |          |

|      |      | 3.5.6     | Reset                                |          |

|      |      | 3.5.7     | 5 V tracking voltage regulator       |          |

|      |      | 3.5.8     | Standby regulator                    |          |

|      |      | 3.5.9     | High side switch                     |          |

|      |      | 3.5.10    | Injector driver                      |          |

|      |      | 3.5.11    | Relay drivers                        |          |

|      |      | 3.5.12    | Lamp driver                          |          |

|      |      | 3.5.13    | Tachometer driver                    |          |

|      |      | 3.5.14    | Stepper motor driver                 |          |

|      |      | 3.5.15    | O2 sensor heater driver              |          |

|      |      | 3.5.16    | Variable reluctance sensor interface |          |

|      |      | 3.5.17    | K-line                               |          |

|      |      | 3.5.18    | SPI interface                        |          |

| 4    | Fund | ctional d | escription                           |          |

|      | 4.1  | Chip w    | orking conditions                    |          |

|      | 4.2  | Chip bi   | as current generation                |          |

| 2/49 |      |           | DocID17617 Rev 1                     | <b>T</b> |

| 4.3  | Power     | up/down sequences                                                                         |

|------|-----------|-------------------------------------------------------------------------------------------|

| 4.4  | SPI .     |                                                                                           |

|      | 4.4.1     | Data in (DIN)                                                                             |

|      | 4.4.2     | Data out                                                                                  |

| 4.5  | Diagno    | osis                                                                                      |

|      | 4.5.1     | Voltage regulators thermal warning and shutdown                                           |

|      | 4.5.2     | Overvoltage shut down                                                                     |

|      | 4.5.3     | Undervoltage shut down                                                                    |

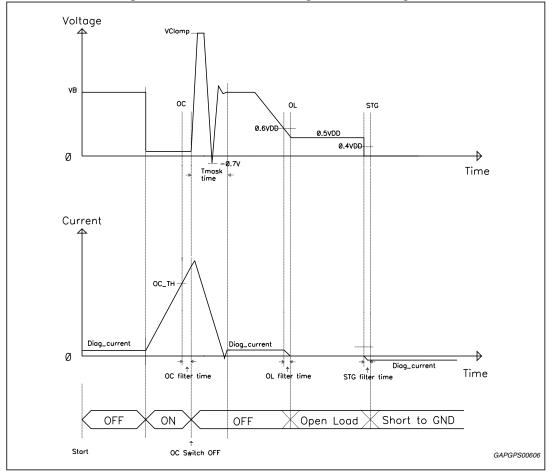

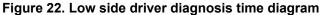

|      | 4.5.4     | Low side on/off diagnosis (INJ, RLY's, TACH, O2H)                                         |

|      | 4.5.5     | Lamp driver on/off diagnosis35                                                            |

|      | 4.5.6     | Stepper motor driver off diagnosis (EN signal high and output in high impedance state) 36 |

|      | 4.5.7     | Stepper motor driver on diagnosis (EN signal Low and output driven by input commands) 36  |

|      | 4.5.8     | VRS diagnosis                                                                             |

| 4.6  | VRS ir    | nterface                                                                                  |

|      | 4.6.1     | Function characteristic                                                                   |

|      | 4.6.2     | Auto-adaptative hysteresis                                                                |

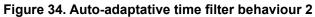

|      | 4.6.3     | Auto-adaptative time filter                                                               |

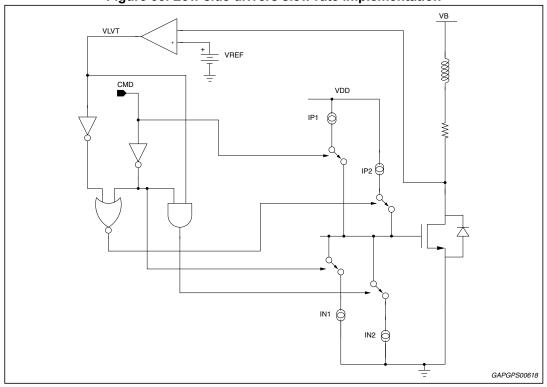

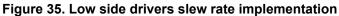

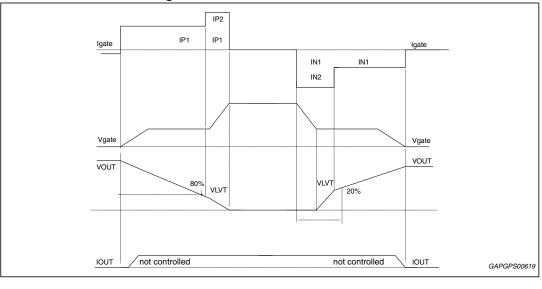

| Low  | side dr   | ivers                                                                                     |

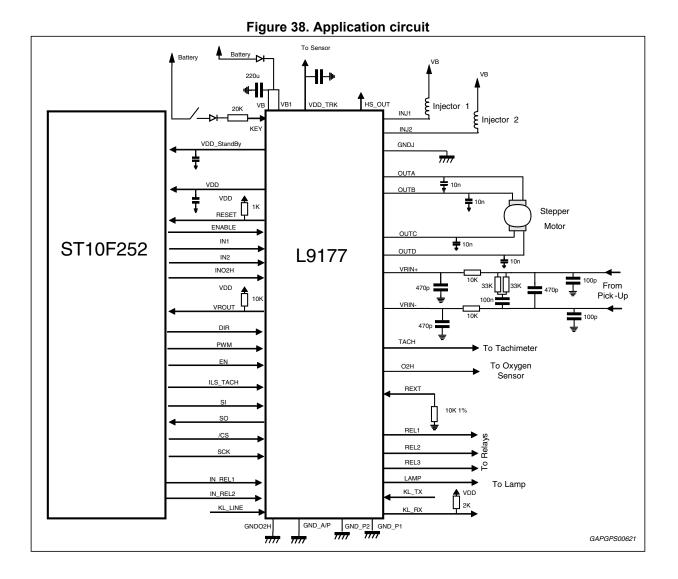

| Appl | ication   | circuit                                                                                   |

| 6.1  | Bill of I | material                                                                                  |

| Pack | age inf   | ormation                                                                                  |

| Revi | sion his  | story                                                                                     |

5

6

7

8

# List of tables

| Table 1.  | Device summary                                                  | . 1 |

|-----------|-----------------------------------------------------------------|-----|

| Table 2.  | Pin function                                                    | . 8 |

| Table 3.  | Operating conditions                                            | 10  |

| Table 4.  | Absolute maximum ratings                                        | 10  |

| Table 5.  | ESD protection                                                  | 12  |

| Table 6.  | Temperature ranges and thermal data                             | 12  |

| Table 7.  | Supply electrical characteristics                               | 12  |

| Table 8.  | Key electrical characteristics.                                 | 13  |

| Table 9.  | Digital pins characteristics                                    | 14  |

| Table 10. | Digital output pins characteristics                             | 14  |

| Table 11. | VDD output electrical characteristics                           | 14  |

| Table 12. | Reset function electrical characteristics                       | 15  |

| Table 13. | VDD_TRK output electrical characteristics                       | 16  |

| Table 14. | VDD_SB output electrical characteristics                        | 17  |

| Table 15. | HS_OUT output electrical characteristics                        | 18  |

| Table 16. | Injector driver electrical characteristic                       | 18  |

| Table 17. | Relay driver characteristics.                                   | 20  |

| Table 18. | Lamp driver characteristics                                     |     |

| Table 19. | Tachometer driver electrical characteristics                    |     |

| Table 20. | Stepper motor driver electrical characteristics                 |     |

| Table 21. | O2 sensor heater driver characteristics                         |     |

| Table 22. | Variable reluctance sensor interface electrical characteristics | 24  |

| Table 23. | K-Line interface electrical characteristics                     |     |

| Table 24. | SPI characteristics and timings                                 |     |

| Table 25. | L9177 outputs working conditions.                               |     |

| Table 26. | Data in (DIN) words content                                     |     |

| Table 27. | Data in command bits structure                                  |     |

| Table 28. | Data in VRS hysteresis                                          |     |

| Table 29. | Data out (DOUT) words content                                   |     |

| Table 30. | Two bits diagnosis (normal drivers)                             |     |

| Table 31. | Three bits diagnosis (bridge stage).                            |     |

| Table 32. | Peak voltage detector precision                                 |     |

| Table 33. | Hysteresis threshold precision                                  |     |

| Table 34. | Values for IPx and INx current generators for each low side     |     |

| Table 35. | Bill of material                                                |     |

| Table 36. | Document revision history.                                      | 48  |

|           |                                                                 |     |

# List of figures

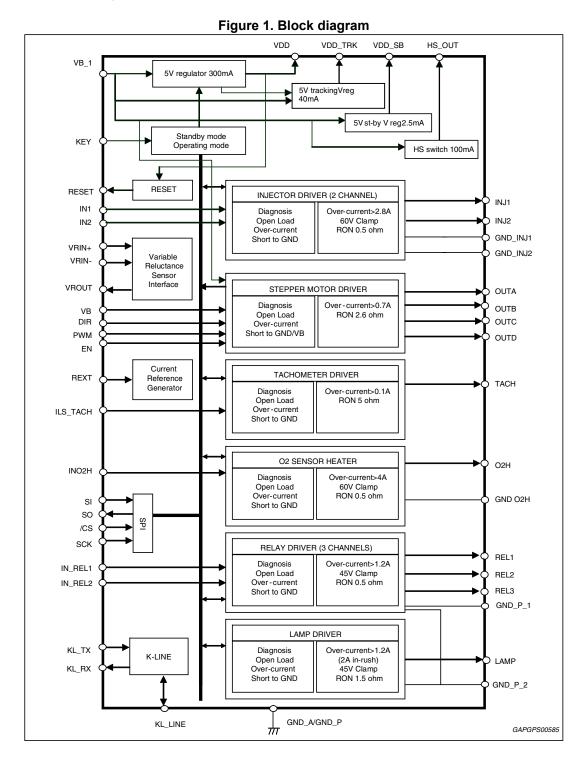

| Figure 1.  | Block diagram                                                | 7  |

|------------|--------------------------------------------------------------|----|

| Figure 2.  | Pin connection (top view)                                    | 8  |

| Figure 3.  | Input threshold                                              | 13 |

| Figure 4.  | Key block diagram                                            | 13 |

| Figure 5.  | 5 V main regulator block diagram                             | 15 |

| Figure 6.  | Reset                                                        | 15 |

| Figure 7.  | 5 V tracking regulator block diagram                         | 16 |

| Figure 8.  | 5 V standby regulator block diagram                          | 17 |

| Figure 9.  | High-side driver block diagram                               | 18 |

| Figure 10. | Low-side driver block diagram                                | 19 |

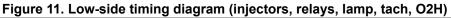

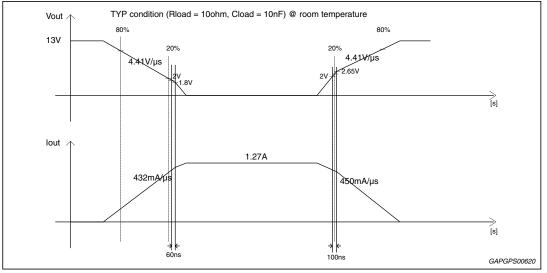

| Figure 11. | Low-side timing diagram (injectors, relays, lamp, tach, O2H) | 19 |

| Figure 12. | Stepper motor driver block diagram                           | 22 |

| Figure 13. | Stepper motor operations                                     | 23 |

| Figure 14. | VRS block diagram                                            | 25 |

| Figure 15. | K-line block diagram                                         | 26 |

| Figure 16. | -SO loading for disable time measurement                     | 27 |

| Figure 17. | SPI timing diagram                                           | 27 |

| Figure 18. | Current generator block diagram                              | 29 |

| Figure 19. | Power-up sequence                                            | 30 |

| Figure 20. | Power-down sequence                                          | 30 |

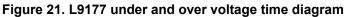

| Figure 21. | L9177 under and over voltage time diagram                    | 33 |

| Figure 22. | Low side driver diagnosis time diagram                       | 34 |

| Figure 23. | Low side driver diagnosis I-V relationship.                  | 35 |

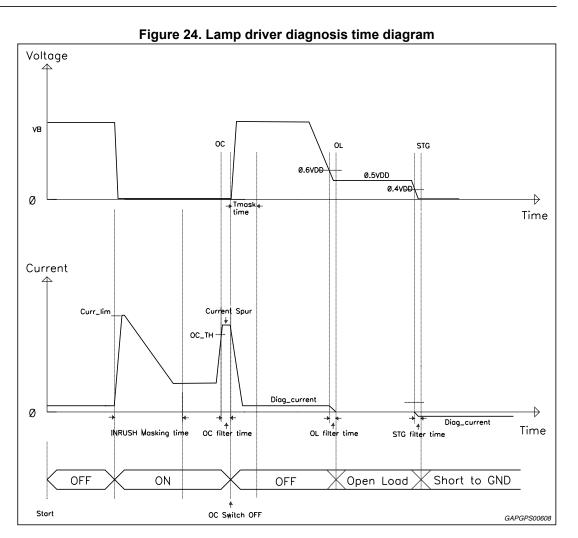

| Figure 24. | Lamp driver diagnosis time diagram                           | 36 |

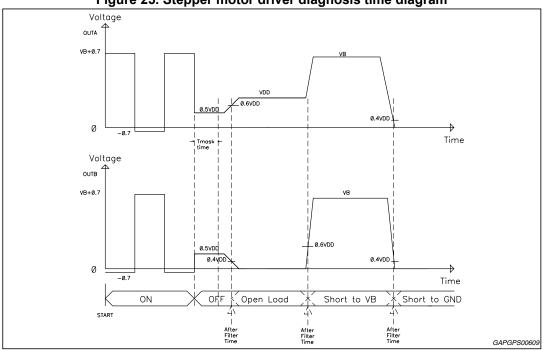

| Figure 25. | Stepper motor driver diagnosis time diagram                  | 37 |

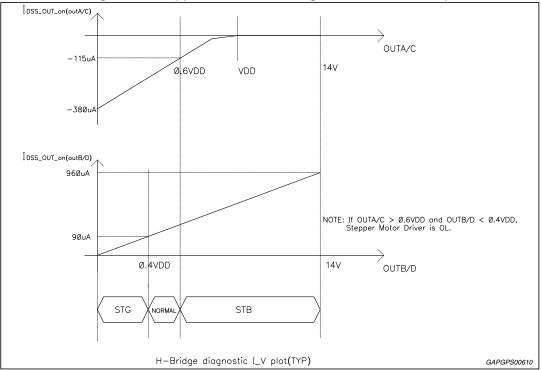

| Figure 26. | Stepper motor driver diagnosis I-V relationship              | 37 |

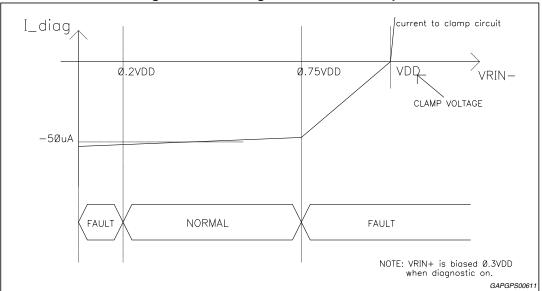

| Figure 27. | VRS diagnosis I-V relationship                               |    |

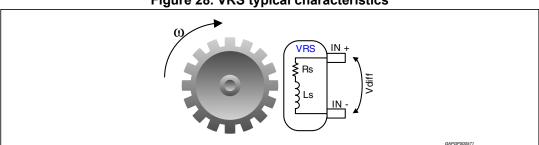

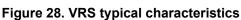

| Figure 28. | VRS typical characteristics                                  | 38 |

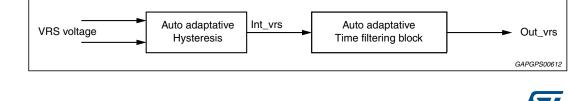

| Figure 29. | VRS interface structure                                      |    |

| Figure 30. | Auto-adaptive hysteresis block diagram                       |    |

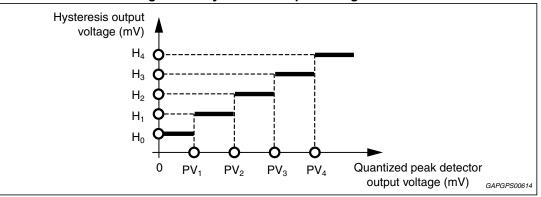

| Figure 31. | Hysteresis output voltage level                              |    |

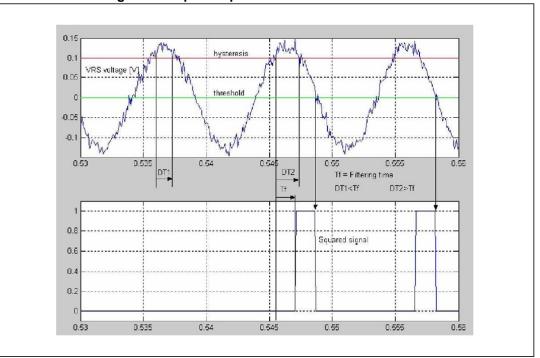

| Figure 32. | Input-output behavior of VRS interface                       |    |

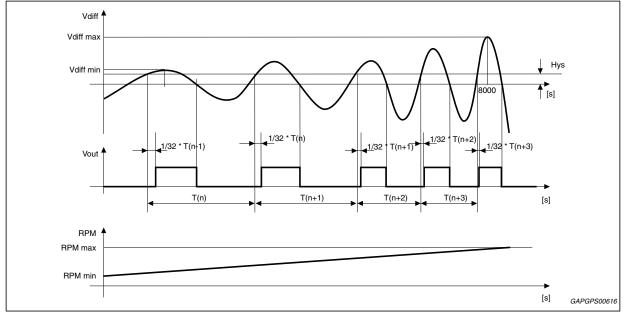

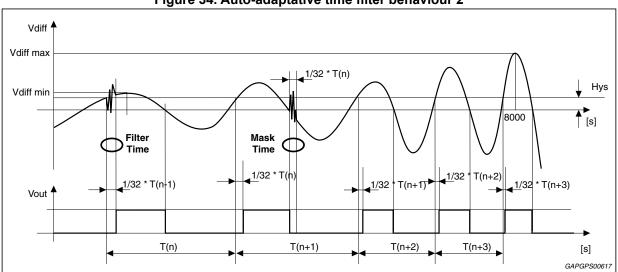

| Figure 33. | Auto-adaptative time filter behaviour 1                      |    |

| Figure 34. | Auto-adaptative time filter behaviour 2                      |    |

| Figure 35. | Low side drivers slew rate implementation                    |    |

| Figure 36. | Low side drivers slew rate                                   |    |

| Figure 37. | O2H low side driver slew rate                                |    |

| Figure 38. | Application circuit                                          |    |

| Figure 39. | PowerSO46 mechanical data and package dimensions.            | 47 |

# 1 Description

L9177 is a device realized in ST BCD proprietary technology, able to provide the full set of power supplies and signal preprocessing peripherals needed to control a 2 Cylinder internal combustion Engine for Low End Application (e.g. small motorcycle, K-car, nautical engines, etc.).

L9177 integrates a 5 V main voltage regulator, a 5 V 40 mA tracking regulator for sensor supply and a 2.5 mA 5 V standby regulator.

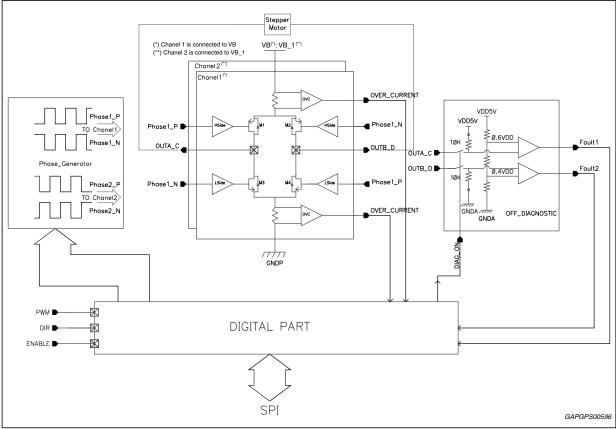

The two channels injector drivers, the O2 sensor heater and two relay drivers can be controlled both with parallel input and with SPI interface. One additional relay driver and the lamp driver are controlled by SPI. The stepper motor driver is designed for a double winding coil motor, used for engine idle speed control.

Low side drivers implement SR control to minimize emission.

A protected 50 mA high side driver is provided.

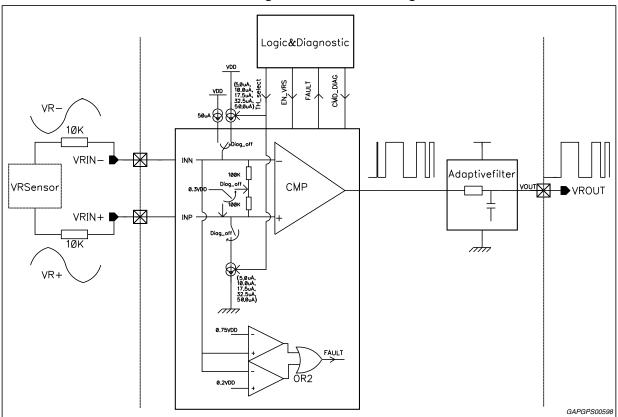

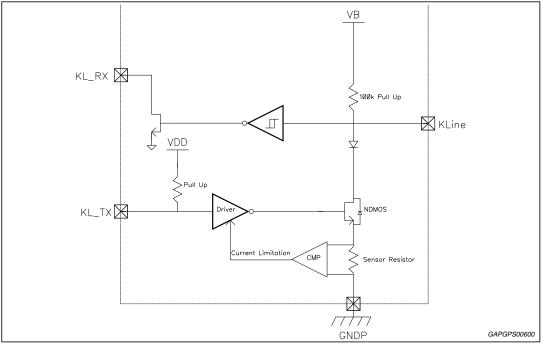

A Variable Reluctance Sensor interface allows the connection to a commercial magnetic pick-up, allowing the indirect measurement of internal combustion engine crank angle. A K-line (standard ISO-9141 compatible) is provided as data communication interface.

All functionalities are fully protected and provide complete diagnostics via a 24bit SPI interface. An overall protection against over temperature is provided as well.

The device is available in PowerSO46, ST proprietary package for high power application.

# 2 Block diagram and pin description

## 2.1 Block diagram

# 2.2 Pin description

|            | 1 46              |              |  |  |  |  |  |

|------------|-------------------|--------------|--|--|--|--|--|

| OUTB E     | 2 4               |              |  |  |  |  |  |

| OUTA E     | 3 44              | 1 🗆 VВ       |  |  |  |  |  |

| VB_1 [     | 4 43              | 3 🗖 VDD_SB   |  |  |  |  |  |

| EN 🗆       | 5 42              | 2 🗖 PWM      |  |  |  |  |  |

|            | 6 4 <sup>.</sup>  |              |  |  |  |  |  |

| VDD_TRK E  | 7 40              | ) 🗇 KL_Line  |  |  |  |  |  |

| REXT [     | 8 39              | Ð □ KL_RX    |  |  |  |  |  |

| HS_OUT E   | 9 38              | 3 🗆 KL_TX    |  |  |  |  |  |

| VRIN+ 🗆    | 10 37             | 7 🗇 INJ2     |  |  |  |  |  |

| VRIN- 🗆    | 11 36             | 5 🗆 IN2      |  |  |  |  |  |

| VROUT E    | 12 35             | 5 🛛 GND_INJ2 |  |  |  |  |  |

| O2H 🗆      | 13 3 <sup>4</sup> | 1 🗇 GND_INJ1 |  |  |  |  |  |

| TACH E     | 14 33             | 3 🗇 IN1      |  |  |  |  |  |

| ILS_TACH E | 15 32             | 2 🗇 INJ1     |  |  |  |  |  |

| GND_O2H E  | 16 3 <sup>.</sup> |              |  |  |  |  |  |

| INO2H 🗆    | 17 30             |              |  |  |  |  |  |

| RESET C    | 18 29             | Э 🗆 SCK      |  |  |  |  |  |

| IN-REL2    | 19 28             | 3 🗖 SI       |  |  |  |  |  |

| IN-REL1    | 20 27             | 7 ⊐ SO       |  |  |  |  |  |

| REL2       | 21 26             | 6 🗆 LAMP     |  |  |  |  |  |

| GND_P_1 C  | 22 25             | 5 🗆 GND_P_2  |  |  |  |  |  |

| REL1 C     | 23 24             | 1 🗆 REL3     |  |  |  |  |  |

|            |                   | GAPGPS00586  |  |  |  |  |  |

Figure 2. Pin connection (top view)

| Pin # | Pin name | Description                                       |     | Class  |

|-------|----------|---------------------------------------------------|-----|--------|

| 1     | GND      | Analog and power ground                           | GND | PWR    |

| 2     | OUTB     | Output bridge 1                                   | 0   | PWR    |

| 3     | OUTA     | Output bridge 1                                   | 0   | PWR    |

| 4     | VB_1     | Battery line to bridge1                           | I   | PWR    |

| 5     | EN       | Logic input to enable stepper motor               | I   | SIGNAL |

| 6     | DIR      | Logic input to set stepper motor direction        | I   | SIGNAL |

| 7     | VDD_TRK  | Tracking voltage regulator output                 | 0   | PWR    |

| 8     | REXT     | External resistor for precision current reference | I   | SIGNAL |

| 9     | HS_OUT   | High side switch output                           | 0   | PWR    |

| 10    | VRIN+    | VRS positive differential input                   | I   | SIGNAL |

| 11    | VRIN-    | VRS negative differential input                   | I   | SIGNAL |

| 12    | VROUT    | VRS output                                        | 0   | SIGNAL |

| 13    | O2H      | O2 sensor heater output                           | 0   | PWR    |

| Pin # | Pin name | Description                            | l/O<br>type | Class  |

|-------|----------|----------------------------------------|-------------|--------|

| 14    | TACH     | Tachometer driver output               | 0           | PWR    |

| 15    | ILS_TACH | Tachometer driver input                | I           | SIGNAL |

| 16    | GND_O2H  | O2 sensor heater ground                | GND         | PWR    |

| 17    | INO2H    | O2 sensor heater input                 | I           | SIGNAL |

| 18    | RESET    | Reset signal to the micro              | 0           | SIGNAL |

| 19    | IN_REL2  | Relay 2 parallel control input         | I           | SIGNAL |

| 20    | IN_REL1  | Relay 1 parallel control input         | I           | SIGNAL |

| 21    | REL2     | Relay 2 driver output                  | 0           | PWR    |

| 22    | GND_P_1  | Power ground relay 1-2                 | 0           | PWR    |

| 23    | REL1     | Relay 1 driver output                  | 0           | PWR    |

| 24    | REL3     | Relay 3 driver output                  | 0           | SIGNAL |

| 25    | GND_P_2  | Power ground for lamp                  | GND         | PWR    |

| 26    | LAMP     | Lamp driver output                     | 0           | PWR    |

| 27    | SO       | SPI data out                           | 0           | SIGNAL |

| 28    | SI       | SPI data in                            | I           | SIGNAL |

| 29    | SCK      | SPI serial clock                       | I           | SIGNAL |

| 30    | CS       | SPI chip select                        | I           | SIGNAL |

| 31    | KEY      | Key signal                             | I           | SIGNAL |

| 32    | INJ1     | Injector 1driver power output          | 0           | PWR    |

| 33    | IN1      | Injector 1 driver input command        | I           | SIGNAL |

| 34    | GND_INJ1 | Injector 1 ground                      | GND         | PWR    |

| 35    | GND_INJ2 | Injector 2 ground                      | GND         | PWR    |

| 36    | IN2      | Injector 2 driver input command        | I           | SIGNAL |

| 37    | INJ2     | Injector 2 driver power output         | 0           | PWR    |

| 38    | KL_TX    | K-Line TX digital IN                   | I           | SIGNAL |

| 39    | KL_RX    | K-Line RX digital OUT                  | 0           | SIGNAL |

| 40    | KL_LINE  | K-Line                                 | I/O         | PWR    |

| 41    | VDD      | 5 V voltage regulator output           | 0           | PWR    |

| 42    | PWM      | Logic Input to set Stepper Motor Speed | I           | SIGNAL |

| 43    | VDD_SB   | 5 V standby voltage regulator output   | 0           | PWR    |

| 44    | VB       | Battery line to bridge 2               | I           | PWR    |

| 45    | OUTD     | Output bridge 2                        | 0           | PWR    |

| 46    | OUTC     | Output bridge 2                        | 0           | PWR    |

Table 2. Pin function (continued)

#### **Electrical specifications** 3

#### **Operating range** 3.1

The device may not operate properly if maximum operating conditions are exceeded.

| Symbol | Parameter             | Value                    | Unit |

|--------|-----------------------|--------------------------|------|

| VB     | Supply voltage        | 6 to 18 <sup>(1)</sup>   | V    |

|        | I/O logic             | 0 to Vdd                 | V    |

|        | Stepper motor outputs | -0.3 to Vb+              | V    |

|        | Low side              | -0.3 to clamp<br>voltage | V    |

| Table | 3. O | perating | conditions  |

|-------|------|----------|-------------|

| Table | J. U | perating | contaitions |

1. Below 3.9 V the device is in a safety state (internal circuitries are on but all the outputs are off).

From 3.9 V to 5.5 V (cranck functionality) Reset function; VDD > 3.3 V (rds-on state) IVDD=100mA; 3.3 V<VDD\_TRK<VDD (rds-on state); Low-sides, K-Line, H-Bridge OFF if Reset = 0; SPI not available, internal registers resetted if Reset = 0; All Diagnosis disabled if Reset=0; VRS function limited (Vdiff max =1000mV).

From 5.5 V to 6 V (low battery) All the functions are granted with the following degraded parameters; VDD5>4.510V; VDD Reset function guaranteed, but no Reset asserted; Tracking error < 100 mV (lload = 40 mA, rds-on state).

From 18 V to  $V_{B off}$  (load dump transient) All the functions are granted with increased power dissipation and no reset is asserted during transient.

From  $V_B$  off to 40 V (internal circuitries are on but all the outputs are off) The device is on in a safety state.

#### 3.2 Absolute maximum ratings

Maximum ratings are absolute ratings; exceeding any one of these values may cause permanent damage to the integrated circuit.

| Parameter                                   | Condition   | Min  | Мах           | Unit |

|---------------------------------------------|-------------|------|---------------|------|

| DC supply voltage                           | pin VB/VB_1 | -0.3 | 40            | V    |

| I/O low voltage pins <sup>(1)</sup>         | -           | -0.3 | 7             | V    |

| I/O low voltage digital pins <sup>(2)</sup> | -           | -0.3 | Vdd+0.3       | V    |

| I/O power pins <sup>(3)</sup> voltage range | -           | -0.3 | Clamp voltage | V    |

| TACH pin                                    | -           | -0.3 | 40            | V    |

| OUTA-D                                      | -           | -0.3 | VB +0.3       | V    |

| 105                                                | (continu                                                                                                                                                                |      |           |          |  |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------|----------|--|

| Parameter                                          | Condition                                                                                                                                                               | Min  | Мах       | Unit     |  |

| KEY pin                                            | To be protected with Rkey_ext to<br>limit sourced/sinked current to<br>$\pm$ 5 mA in dc conditions and $\pm$ 20 mA<br>during transients<br>(ISO-pulses on battery line) | -0.3 | 10        | v        |  |

| VRIN- / VRIN+                                      | Max current  20 mA  to be limited with external resistors                                                                                                               | -0.3 | Vdd + 0.3 | V        |  |

| VDD_TRK pin                                        | -                                                                                                                                                                       | -2   | 40        | V        |  |

| KL_LINE pin                                        | -                                                                                                                                                                       | -16  | 40        | V        |  |

| Maximum voltage shift between GND pins             | PIN GND, GND_O2H, GND_P_1,2,<br>GND_INJ1,2, GNDA, GNDP                                                                                                                  | -0.3 | 0.3       | V        |  |

| I/O power pins <sup>(3)</sup>                      | Injector drivers                                                                                                                                                        | -    | 50        | mJ       |  |

| maximum energy (single                             | O2 sensor heater                                                                                                                                                        | -    | 60        | mJ       |  |

| pulse, max. current)                               | Relay/lamp drivers                                                                                                                                                      | -    | 25        | mJ       |  |

| I/O power pins <sup>(3)</sup>                      | Injector drivers                                                                                                                                                        | -    | 18        | mJ       |  |

| maximum energy<br>(continuous pulse, max.          | O2 sensor heater                                                                                                                                                        | -    | 22        | mJ       |  |

| current, 36 million pulses<br>with T = 100 ms)     | Relay/lamp drivers                                                                                                                                                      | -    | 8         | mJ       |  |

| Reverse current through                            | Static (room temperature, max reverse diode voltage 1.5 V)                                                                                                              | -    | 2.5       |          |  |

| O2H output without supply voltage <sup>(4)</sup>   | Dynamic (guarantee by iso-pulse test immunity on application board)                                                                                                     | -    | -         | A        |  |

| Reverse current through                            | Static (room temperature, max reverse diode voltage 1.5 V)                                                                                                              | -    | 2.2       |          |  |

| INJx outputs without supply voltage <sup>(4)</sup> | Dynamic (guarantee by iso-pulse test immunity on application board)                                                                                                     | -    | -         | A        |  |

| Reverse current through                            | Static (room temperature, max reverse diode voltage 1.5v)                                                                                                               | -    | 1.2       |          |  |

| LAMP output without supply voltage <sup>(4)</sup>  | Dynamic (guarantee by iso-pulse test immunity on application board)                                                                                                     | -    | -         | A        |  |

| Reverse current through                            | Static (room temperature, max reverse diode voltage 1.5 V)                                                                                                              | -    | 1.5       |          |  |

| RLYx outputs without supply voltage <sup>(4)</sup> | Dynamic (guarantee by iso-pulse<br>test immunity on application board)                                                                                                  | -    | -         | - A      |  |

| Reverse current through                            | Static (room temperature, max reverse diode voltage 1.5 V)                                                                                                              | -    | 0.5       | <u> </u> |  |

| TACH output without supply voltage <sup>(4)</sup>  | Dynamic (guarantee by iso-pulse test immunity on application board)                                                                                                     | -    | -         | A        |  |

| Table 4. A | bsolute | maximum | ratings | (continued) |

|------------|---------|---------|---------|-------------|

|------------|---------|---------|---------|-------------|

1. Pins are VDD, VDD\_SB, REXT, DIR

2. Pins are CS, SCK, SI, SO, VROUT, RESET, PWM, EN, INO2H, ILS\_TACH, IN, KL\_TX, KL\_RX

3. Pins are O2H, LAMP, INJ1-2, REL1-2-3

4. Reverse battery connection, parameter not tested for info only

| Item                             | Condition                                | Min           | Max         | Unit |  |  |  |  |

|----------------------------------|------------------------------------------|---------------|-------------|------|--|--|--|--|

| All pins <sup>(1)</sup>          | НВМ                                      | -2            | 2           | kV   |  |  |  |  |

| All pins                         | ММ                                       | -200          | 200         | V    |  |  |  |  |

| All pins                         | CDM (values for corner pins in brackets) | -500 / (-750) | 500 / (750) | V    |  |  |  |  |

| Pins to connector <sup>(2)</sup> | НВМ                                      | -4            | 4           | kV   |  |  |  |  |

Table 5. ESD protection

1. Except: OUTA-D, TACH, O2H, LAMP, INJ1-2, REL1-2-3 vs. GNDP1:-1 / 1 kV OUTA-D, TACH, O2H, LAMP, INJ1-2, REL1-2-3 vs. GNDP2, GNDO2:-1.5 / 1.5 kV

2. Pins are OUTA-D, TACH, O2H, LAMP, INJ1-2, KEY, REL1-2-3, VB, KL\_LINE, VDD\_TRK all GND connected together. The device is AEC-Q100 compliant.

#### 3.3 Latch-up test

According to JEDEC 78 class 2 level A.

#### 3.4 Temperature ranges and thermal data

| Table 6. Temperature ranges and thermal data |                                                       |     |     |      |  |  |  |

|----------------------------------------------|-------------------------------------------------------|-----|-----|------|--|--|--|

| Symbol                                       | Parameter                                             | Min | Мах | Unit |  |  |  |

| T <sub>amb</sub>                             | Operating temperature (ECU environment)               | -40 | 125 | °C   |  |  |  |

| Tj                                           | Operating junction temperature                        | -40 | 150 | °C   |  |  |  |

| T <sub>stg</sub>                             | Storage temperature                                   | -40 | 150 | °C   |  |  |  |

| T <sub>ot</sub>                              | Thermal shut-down temperature                         | 155 | 200 | °C   |  |  |  |

| O <sub>Thys</sub>                            | Thermal shut-down temperature hysteresis              | 10  |     | °C   |  |  |  |

| R <sub>Th j-amb</sub>                        | Thermal resistance junction-to-ambient <sup>(1)</sup> |     | 16  | °C/W |  |  |  |

| R <sub>Th j-case</sub>                       | Thermal resistance junction-to-case                   |     | 2   | °C/W |  |  |  |

### Table 6 Temperature ranges and thermal data

1. with 2s2p PCB thermally enhanced.

#### 3.5 **Electrical characteristics**

$V_B = 6 V$  to 18 V,  $T_{amb} = -40 \degree C$  to 125  $\degree C$ .

#### 3.5.1 Supply

| Symbol             | Parameter                         | Condition | Min | Тур | Мах | Unit |

|--------------------|-----------------------------------|-----------|-----|-----|-----|------|

| V <sub>B</sub>     | Operating supply voltage range    | -         | 6   | -   | 18  | V    |

| V <sub>B_off</sub> | Vbat switch off threshold voltage | -         | 30  | 32  | 34  | V    |

| V <sub>B OVh</sub> | Overvoltage threshold hysteresis  | -         | 0.5 | -   | -   | V    |

12/49

| Symbol               | Parameter                            | Condition                               | Min | Тур  | Max | Unit |

|----------------------|--------------------------------------|-----------------------------------------|-----|------|-----|------|

| V <sub>B UVL</sub>   | Undervoltage disable LOW threshold   | -                                       | 3.5 | 3.7  | 3.9 | V    |

| V <sub>B UVh</sub>   | Undervoltage threshold<br>hysteresis | -                                       | 0.3 | -    | 1   | V    |

| I <sub>VB(dis)</sub> | Standby current                      | VB= 13 V, device<br>disabled, KEY<0.7 V | -   | -    | 120 | μA   |

| $I_{VB}$             | Quiescent current                    | VB= 13 V, outputs floating              | -   | -    | 20  | mA   |

| V <sub>rext</sub>    | ASIC Bias reference                  | Application note                        | -   | 1.22 | -   | V    |

| fint_clk             | Internal clock reference             | Application note                        | -   | 5.6  | -   | MHz  |

Table 7. Supply electrical characteristics (continued)

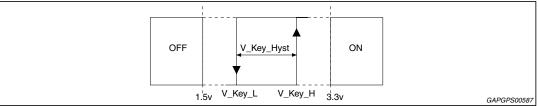

### 3.5.2 Key

### Table 8. Key electrical characteristics

| Symbol         | Parameter                                          | Condition                                              | Min | Тур | Мах | Unit |

|----------------|----------------------------------------------------|--------------------------------------------------------|-----|-----|-----|------|

| V_Key_L        | Input low threshold                                | -                                                      | 1.5 | -   | -   | V    |

| V_Key_H        | Input high threshold                               | -                                                      | -   | -   | 3.3 | V    |

| V_Key_Hyst     | Input voltage hysteresis                           | -                                                      | 0.5 | -   | 1.8 | V    |

| R_Key          | Internal pull down                                 | -                                                      | 50  | 150 | 300 | kΩ   |

| T_key_deglitch | Key input filter time                              | Guaranteed by scan                                     | 26  | -   | 40  | μs   |

| T_key_delay    | Maximum delay time from<br>Key to regulator enable | Time from key rising<br>edge to 20% VDD<br>rising edge | -   | -   | 200 | μs   |

#### Figure 3. Input threshold

### Figure 4. Key block diagram

#### 3.5.3 **Digital pins**

#### Table 9. Digital pins characteristics

| Symbol            | Parameter                                 | Condition | Min     | Тур | Мах     | Unit |

|-------------------|-------------------------------------------|-----------|---------|-----|---------|------|

| V <sub>in_L</sub> | Input level threshold low                 | -         | 0.3*Vdd | -   | -       | V    |

| V <sub>in_H</sub> | Input level threshold high                | -         | -       | -   | 0.7*Vdd | V    |

| V <sub>hin</sub>  | Input voltage hysteresis                  | -         | 0.1     | -   | -       | V    |

| R_pull            | Internal pull-down/pull-up <sup>(1)</sup> | -         | 50      | 150 | 250     | kΩ   |

| I_pull_down       | Active pull-down                          | -         | 10      | -   | 100     | μA   |

Pins with pull-up: SI, SCK, CS, KL-TX; Pins with pull-down: EN, PWM, ISL-TACH, INO2H, IN\_REL1-2, IN1-2; Pins with active pull-down: DIR. 1.

**Digital output pins** 3.5.4

#### Table 10. Digital output pins characteristics

| Symbol | Parameter         | Condition                | Min     | Тур | Мах | Unit |

|--------|-------------------|--------------------------|---------|-----|-----|------|

|        | Output level low  | I <sub>sink</sub> = 2mA  | -       | -   | 0.4 | V    |

|        | Output level high | $I_{source} = 2mA^{(1)}$ | Vdd-0.5 | -   | -   | V    |

Pins with open drain output: RESET, VROUT; 1. Pins with push-pull stage and tri-state condition: SDO

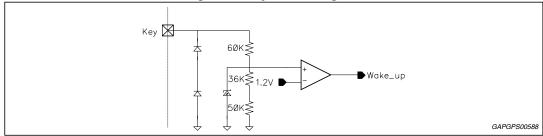

#### 3.5.5 5 V voltage regulator

#### Symbol Condition Unit Parameter Min Тур Max 5 5.1 V Output voltage 4.9 V<sub>dd</sub> $V_{\rm B} = 6 \, \text{V}$ to 18 V Ln\_vdd Line regulation -25 25 mV I<sub>load</sub> = 150 mA V<sub>B</sub> = 13 V -25 25 Ld\_vdd mV Load regulation \_ $I_{load}$ = 5 mA to 300 mA Recovery from ISO pulse stimuli on V $V_{dd\_OS}$ Max overshoot \_ 5.5 battery line (guaranteed by design) Voltage slew-rate at power- $V_{dd\_SR}$ $C_{load}$ = 4.7 $\mu$ F 2 25 V/ms on Load current 5 300 mΑ I<sub>dd</sub> Output short to 4 V 350 $I_{dd_max}$ Current limitation 600 mΑ Short to ground current Output shorted to GND 350 700 mΑ I<sub>dd\_STG</sub> limitation Sin wave @ 1 kHz 1V pp V<sub>B</sub> = 13 V PSRR Power supply rejection ratio 40 dB $I_{load}$ = 5 mA to 300 mA V<sub>B</sub> - V<sub>dd</sub> - V<sub>dd</sub> dropout V<sub>dr5</sub> V<sub>B</sub> = 5 V I<sub>load</sub> = 300 mA V 0.30 0.75

#### Table 11. VDD output electrical characteristics

voltage

Figure 5. 5 V main regulator block diagram

### 3.5.6 Reset

Table 12. Reset function electrical characteristics

| Symbol                 | Parameter                        | Condition                                       | Min | Тур | Max             | Unit |

|------------------------|----------------------------------|-------------------------------------------------|-----|-----|-----------------|------|

| VUV_LO                 | Output low voltage               | 1 < Vdd< Vth_UV,<br>I <sub>reset</sub> = 2 mA   | -   | -   | 0.6             | V    |

| IUV_LO                 | Reset current capability         | 1 < Vdd < Vth_UV,<br>V <sub>reset</sub> = 0.6 V | 2   | -   | -               | mA   |

| l <sub>lk</sub>        | Leakage current                  | VUV_reset = 4.5 V                               | -   | -   | 1               | μA   |

| Vth_UV                 | Vdd under voltage low threshold  | V <sub>B</sub> = 13.5 V                         | 4.5 | -   | Vdd -<br>150 mV | V    |

| Vth_UV Tht             | Vdd under voltage high threshold | -                                               | 4.5 | -   | Vdd -<br>50 mV  | V    |

| Vth_UV HYS             | Vdd under voltage<br>hysteresis  | -                                               | 50  | -   | -               | mV   |

| Td_UV_ rst             | Power on UV reset delay          | -                                               | 17  | 22  | 30              | ms   |

| T <sub>fUV_reset</sub> | UV reset filter                  | Vdd< Vth_UV                                     | 25  | 50  | 75              | μs   |

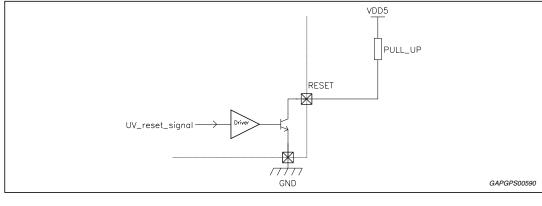

#### Figure 6. Reset

## 3.5.7 5 V tracking voltage regulator

| Symbol               | Parameter                                                  | Condition                                                                          | Min | Тур | Мах            | Unit |

|----------------------|------------------------------------------------------------|------------------------------------------------------------------------------------|-----|-----|----------------|------|

| DV <sub>ddtrk</sub>  | Output voltage tracking error                              | $V_B = 6 V$ ,<br>$I_{trk} = 1 to 40 mA$                                            | -15 | -   | 15             | mV   |

| V <sub>short</sub>   | Tracking output short circuit voltage range                | -                                                                                  | -2  | -   | V <sub>B</sub> | V    |

| I <sub>trk_max</sub> | Output current limitation                                  | Output short to 4 V                                                                | 50  | -   | 100            | mA   |

| l <sub>trk_sb</sub>  | Tracking output reverse current (limited by the regulator) | Output shorted to $V_B = 16 V$                                                     | -   | -   | 10             | mA   |

| I <sub>dd</sub>      | Load current                                               | -                                                                                  | 1   | -   | 40             | mA   |

| Ln_vdd_trk           | Line regulation                                            | $V_B = 6 V$ to 18 V - I <sub>load</sub> = 40 mA                                    | -15 | -   | 15             | mV   |

| Ld_vdd_trk           | Load regulation                                            | $V_B$ = 13 V I <sub>load</sub> = 1 to 40 mA                                        | -15 | -   | 15             | mV   |

| PSRR                 | Power supply rejection ratio                               | Sin wave @ 1 kHz 1V pp $V_B = 13 \text{ V I}_{load} = 1 \text{ to } 40 \text{ mA}$ | 40  | _   | -              | dB   |

Table 13. VDD\_TRK output electrical characteristics

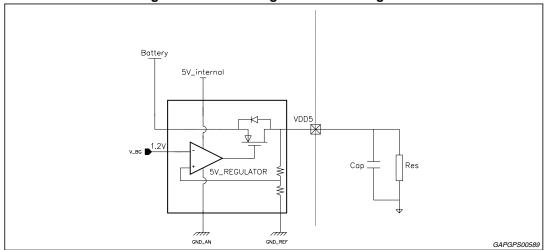

## 3.5.8 Standby regulator

| Symbol              | Parameter                     | Condition                                                                          | Min  | Тур | Max  | Unit |  |  |  |  |

|---------------------|-------------------------------|------------------------------------------------------------------------------------|------|-----|------|------|--|--|--|--|

| V <sub>ddsb</sub>   | Output voltage                | -                                                                                  | 4.75 | 5   | 5.25 | V    |  |  |  |  |

| Ln_vsb              | Line regulation               | V <sub>B</sub> =6 V to 18 V<br>I <sub>load</sub> = 1 mA                            | -25  | -   | 25   | mV   |  |  |  |  |

| Ld_vsb              | Load regulation               | $V_B = 13 V$<br>$I_{load} = 0.1 \text{ mA to } 2.5 \text{ mA}$                     | -25  | -   | 25   | mV   |  |  |  |  |

| V <sub>dd_OS</sub>  | Max overshoot                 | -                                                                                  | -    | -   | 5.5  | V    |  |  |  |  |

| I <sub>dd</sub>     | Load current                  | -                                                                                  | 0.1  | -   | 2.5  | mA   |  |  |  |  |

| I <sub>sb_max</sub> | Current limitation            | Output short to 4 V                                                                | 5    | -   | 50   | mA   |  |  |  |  |

| $V_{sb\_SR}$        | Voltage slew-rate at power on | Cload = 1 µF                                                                       | 2    | -   | 30   | V/ms |  |  |  |  |

| PSRR                | Power supply rejection ratio  | Sin wave @ 1 kHz 1V pp<br>V <sub>B</sub> = 13 V<br>I <sub>load</sub> = 0.1 to 1 mA | 40   | -   | -    | dB   |  |  |  |  |

#### Table 14. VDD\_SB output electrical characteristics

### Figure 8. 5 V standby regulator block diagram

### 3.5.9 High side switch

|                     | Table 15. HS_OUT output electrical characteristics |                         |     |   |     |    |  |  |  |  |  |

|---------------------|----------------------------------------------------|-------------------------|-----|---|-----|----|--|--|--|--|--|

| Symbol              | SymbolParameterConditionMinTypMaxUnit              |                         |     |   |     |    |  |  |  |  |  |

| R <sub>on_hs</sub>  | Ron                                                | I <sub>hs</sub> = 50 mA | -   | - | 14  | Ω  |  |  |  |  |  |

| I <sub>hs_max</sub> | Current limitation                                 | V <sub>B</sub> =13.5 V  | 100 | - | 400 | mA |  |  |  |  |  |

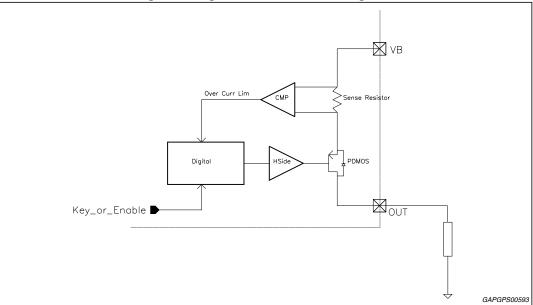

### Figure 9. High-side driver block diagram

### 3.5.10 Injector driver

| Table 16 | . Injector driver | electrical | characteristic |

|----------|-------------------|------------|----------------|

|----------|-------------------|------------|----------------|

| Symbol                               | Parameter                 | Condition                              | Min      | Тур     | Max      | Unit |

|--------------------------------------|---------------------------|----------------------------------------|----------|---------|----------|------|

| I <sub>max</sub>                     | Output current            | -                                      | -        | -       | 2.2      | А    |

| I_oc                                 | Overcurrent threshold     | -                                      | 2.8      | -       | 5        | А    |

| V <sub>DS</sub>                      | Output clamping voltage   | I = 2.2 A                              | 55       | -       | 65       | V    |

| R <sub>on</sub>                      | On resistance             | I = 2.2 A                              | -        | -       | 0.6      | Ω    |

| I <sub>lk_off</sub>                  | Leakage current           | V <sub>out</sub> = 18 V, diagnosis OFF | -        | -       | 10       | μA   |

| I <sub>lk_on</sub>                   | Leakage current           | V <sub>out</sub> = 18 V, diagnosis ON  | -        | -       | 100      | μA   |

| t <sub>on-off</sub>                  | Turn on-off delay         | from CMD edge to 50% output variation  | -        | -       | 6        | μs   |

| V <sub>OL</sub>                      | Open load output voltage  | Driver in OFF condition                | 0.46*VDD | 0.5*VDD | 0.54*VDD | V    |

| V <sub>diagth_H</sub> <sup>(1)</sup> | Diagnostic high threshold | Driver in OFF condition                | 0.54*VDD | 0.6*VDD | 0.66*VDD | V    |

| V <sub>diagth_L</sub> <sup>(1)</sup> | Diagnostic low threshold  | Driver in OFF condition                | 0.36*VDD | 0.4*VDD | 0.44*VDD | V    |

1.  $V_{diagth_L} < V_{out} < V_{diagth_H} \rightarrow Open Load; V_{out} < V_{diagth_L} \rightarrow Short to GND$

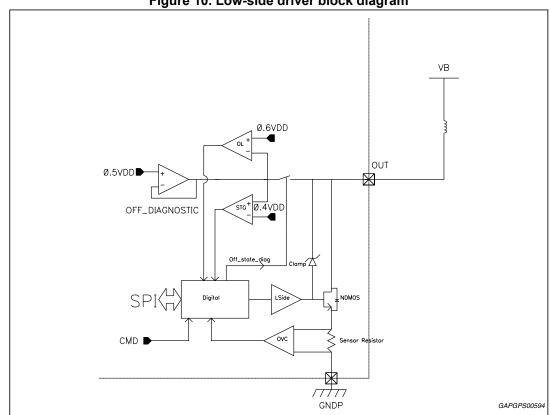

Figure 10. Low-side driver block diagram

## 3.5.11 Relay drivers

| Symbol                               | Parameter                 | Condition                                 | Min      | Тур     | Max      | Unit |

|--------------------------------------|---------------------------|-------------------------------------------|----------|---------|----------|------|

| I <sub>max</sub>                     | Output current            | -                                         | -        | -       | 1        | А    |

| I_oc                                 | Overcurrent threshold     | -                                         | 1.2      | -       | 2.5      | А    |

| V <sub>DS</sub>                      | Output clamping voltage   | I = 1 A                                   | 40       | -       | 50       | V    |

| R <sub>on</sub>                      | On resistance             | I = 1 A                                   | -        | -       | 1.5      | Ω    |

| I <sub>lk_off</sub>                  | Leakage current           | V <sub>out</sub> = 18 V, diagnosis OFF    | -        | -       | 10       | μA   |

| I <sub>lk_on</sub>                   | Leakage current           | V <sub>out</sub> = 18 V, diagnosis ON     | -        | -       | 100      | μA   |

| t <sub>on_off</sub>                  | Turn on-off delay         | From CMD (serial or parallel) rising edge | -        | -       | 6        | μs   |

| V <sub>OL</sub>                      | Open load output voltage  | Driver in OFF condition                   | 0.46*VDD | 0.5*VDD | 0.54*VDD | V    |

| V <sub>diagth_H</sub> <sup>(1)</sup> | Diagnostic high threshold | Driver in OFF condition                   | 0.54*VDD | 0.6*VDD | 0.66*VDD | V    |

| V <sub>diagth_L</sub> <sup>(1)</sup> | Diagnostic low threshold  | Driver in OFF condition                   | 0.36*VDD | 0.4*VDD | 0.44*VDD | V    |

Table 17. Relay driver characteristics

1.  $V_{diagth\_L} < V_{out} < V_{diagth\_H} \rightarrow Open Load; V_{out} < V_{diagth\_L} \rightarrow Short to GND$

## 3.5.12 Lamp driver

| Table 18 | . Lamp | driver | characteristics |

|----------|--------|--------|-----------------|

|----------|--------|--------|-----------------|

| Symbol                               | Parameter                 | Condition                                | Min      | Тур     | Max      | unit |

|--------------------------------------|---------------------------|------------------------------------------|----------|---------|----------|------|

| ILI                                  | Linear current limitation | -                                        | 2        | -       | 4        | А    |

| I <sub>oc</sub>                      | Overcurrent threshold     | Masked for lamp driver<br>during in-rush | 1.2      | -       | 2.4      | A    |

| t <sub>dgmsk</sub>                   | Diagnosis masking time    | Guaranteed by scan                       | 2        | -       | 5        | ms   |

| V <sub>DS</sub>                      | Output clamping voltage   | I = 200 mA                               | 40       | -       | 50       | V    |

| R <sub>on</sub>                      | On resistance             | I = 200 mA                               | -        | -       | 1.5      | Ω    |

| I <sub>lk_off</sub>                  | Leakage current           | V <sub>out</sub> = 18 V, diagnosis OFF   | -        | -       | 10       | μA   |

| I <sub>lk_on</sub>                   | Leakage current           | V <sub>out</sub> = 18 V, diagnosis ON    | -        | -       | 100      | μA   |

| t <sub>on_off</sub>                  | Turn on-off delay         | From SPI CS rising edge                  | -        | -       | 6        | μs   |

| V <sub>OL</sub>                      | Open load output voltage  | Driver in OFF condition                  | 0.46*VDD | 0.5*VDD | 0.54*VDD | V    |

| $V_{\text{diagth}\_H}{}^{(1)}$       | Diagnostic high threshold | Driver in OFF condition                  | 0.54*VDD | 0.6*VDD | 0.66*VDD | V    |

| V <sub>diagth_L</sub> <sup>(1)</sup> | Diagnostic low threshold  | Driver in OFF condition                  | 0.36*VDD | 0.4*VDD | 0.44*VDD | V    |

1.  $V_{diagth_L} < V_{out} < V_{diagth_H} \rightarrow Open Load; V_{out} < V_{diagth_L} \rightarrow Short to GND$

51

### L9177

## 3.5.13 Tachometer driver

| Symbol                               | Parameter                 | Condition                                 | Min      | Тур     | Max      | Unit |  |  |  |  |

|--------------------------------------|---------------------------|-------------------------------------------|----------|---------|----------|------|--|--|--|--|

| I <sub>oc</sub>                      | Overcurrent threshold     | -                                         | 100      | -       | 500      | mA   |  |  |  |  |

| R <sub>on</sub>                      | On resistance             | I = 25 mA                                 | -        | -       | 5        | Ω    |  |  |  |  |

| I <sub>lk_off</sub>                  | Leakage current           | V <sub>out</sub> = 18 V, diagnosis OFF    | -        | -       | 10       | μA   |  |  |  |  |

| I <sub>lk_on</sub>                   | Leakage current           | V <sub>out</sub> = 18 V, diagnosis ON     | -        | -       | 100      | μA   |  |  |  |  |

| t <sub>on_off</sub>                  | Turn on-off delay         | From CMD (serial or parallel) rising edge | -        | -       | 6        | μs   |  |  |  |  |

| V <sub>OL</sub>                      | Open load output voltage  | driver in OFF condition                   | 0.46*VDD | 0.5*VDD | 0.54*VDD | V    |  |  |  |  |

| V <sub>diagth_H</sub> <sup>(1)</sup> | Diagnostic high threshold | Driver in OFF condition                   | 0.54*VDD | 0.6*VDD | 0.66*VDD | V    |  |  |  |  |

| $V_{diagth_L}^{(1)}$                 | Diagnostic low threshold  | Driver in OFF condition                   | 0.36*VDD | 0.4*VDD | 0.44*VDD | V    |  |  |  |  |

| Table 19. | Tachometer | driver electrical | characteristics |

|-----------|------------|-------------------|-----------------|

|-----------|------------|-------------------|-----------------|

1.  $V_{diagth\_L} < V_{out} < V_{diagth\_H} \rightarrow Open Load; V_{out} < V_{diagth\_L} \rightarrow Short to GND$

### 3.5.14 Stepper motor driver

| Symbol                              | Parameter                    | Condition                                                                   | Min      | Тур     | Max      | Unit |

|-------------------------------------|------------------------------|-----------------------------------------------------------------------------|----------|---------|----------|------|

| I <sub>oc</sub>                     | Overcurrent threshold        | ON condition                                                                | 0.85     | -       | 2        | А    |

| R <sub>dsON</sub>                   | On resistance HS+LS          | I <sub>out</sub> = 0.5 A,<br>T <sub>j</sub> = 150 °C, V <sub>B</sub> = 14 V | -        | -       | 2.6      | Ω    |

| f <sub>stepper</sub>                | Working frequency            | Application note                                                            | -        | -       | 20       | kHz  |

| V <sub>out_off</sub> <sup>(1)</sup> | OUTA_B_C_D output<br>voltage | OUTA short to OUTB;<br>OUTC short to OUTD;<br>Stepper driver disable        | 0.44*VDD | 0.5*VDD | 0.54*VDD | V    |

| V <sub>diagth_H</sub>               | Diagnostic high threshold    | Driver in OFF condition                                                     | 0.54*VDD | 0.6*VDD | 0.66*VDD | V    |

| V <sub>diagth_L</sub>               | Diagnostic low threshold     | Driver in OFF condition                                                     | 0.36*VDD | 0.4*VDD | 0.44*VDD | V    |

| I <sub>DSS_OUT</sub>                | Output leakage current       | Driver in OFF condition                                                     | -        | -       | 10       | μA   |

| t <sub>scvb</sub>                   | Over current switch_off time | Guaranteed by scan                                                          | -        | -       | 25       | μs   |

| t <sub>rb</sub>                     | Rise output time             | V <sub>B</sub> = 12 V, R <sub>I</sub> = 39 Ω                                | -        | -       | 15       | μs   |

| t <sub>fb</sub>                     | Fall output time             | V <sub>B</sub> = 12 V, R <sub>I</sub> = 39 Ω                                | -        | -       | 15       | μs   |

| t <sub>rb-a</sub>                   | Rise output time             | T <sub>amb</sub> = 25 °C,                                                   | -        | -       | 10       | μs   |

| t <sub>fb-a</sub>                   | Fall output time             | V <sub>B</sub> = 12 V, R <sub>I</sub> = 39 Ω                                | -        | -       | 10       | μs   |

| t <sub>pHLb</sub>                   | Turn-off in/out delay time   | V <sub>B</sub> = 12 V, R <sub>I</sub> = 39 Ω                                | -        | -       | 15       | μs   |

| t <sub>pLHb</sub>                   | Turn-off in/out delay time   | $ V_{B} - 12 v, R  - 39 \Omega$                                             | -        | -       | 15       | μs   |

| V <sub>reverse_HS</sub>             | Reverse HS diode drop        | Driver in OFF condition<br>I <sub>injected</sub> = 0.5 A                    | -        | -       | 1.5      | V    |

#### Table 20. Stepper motor driver electrical characteristics

| Symbol                  | Parameter             | Condition                                               | Min | Тур | Max  | Unit |

|-------------------------|-----------------------|---------------------------------------------------------|-----|-----|------|------|

| V <sub>reverse_LS</sub> | Reverse LS diode drop | Driver in OFF condition<br>I <sub>Sourced</sub> = 0.5 A | -   | -   | -1.5 | V    |

Table 20. Stepper motor driver electrical characteristics (continued)

VoutA >Vdiagth\_H and VoutB<Vdiagth\_L or VoutC>Vdiagth\_H and VoutD<Vdiagth\_L  $\rightarrow$  Open load VoutA\_B\_C\_D>Vdiagth\_H  $\rightarrow$  Short to Battery VoutA\_B\_C\_D<Vdiagth\_L  $\rightarrow$  Short to GND VoutA<Vdiagth\_H and VoutB>Vdiagth\_L  $\rightarrow$  No Fault VoutA<Vdiagth\_H and VoutB>Vdiagth\_L  $\rightarrow$  No Fault 1.

### Figure 12. Stepper motor driver block diagram

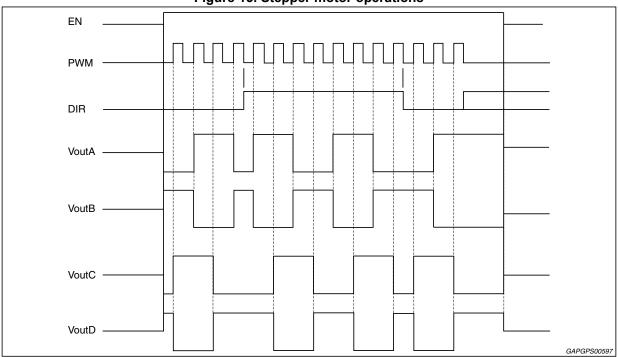

#### Figure 13. Stepper motor operations

### 3.5.15 O2 sensor heater driver

#### Table 21. O2 sensor heater driver characteristics

| Symbol                               | Parameter                 | Condition                                 | Min      | Тур     | Max      | Unit |

|--------------------------------------|---------------------------|-------------------------------------------|----------|---------|----------|------|

| R <sub>dsON</sub>                    | On resistance             | I <sub>out</sub> = 3 A                    | -        | -       | 0.5      | Ω    |

| V <sub>C</sub>                       | Output clamping voltage   | I <sub>out</sub> = 3 A                    | 40       | -       | 50       | V    |

| I <sub>lk_off</sub>                  | Leakage current           | V <sub>out</sub> = 18 V, diagnosis OFF    | -        | -       | 10       | μA   |

| I <sub>lk_on</sub>                   | Leakage current           | V <sub>out</sub> = 18 V, diagnosis ON     | -        | -       | 100      | μA   |

| t <sub>on_off</sub>                  | Turn on-off delay         | From CMD (serial or parallel) rising edge | -        | -       | 6        | μs   |

| V <sub>OL</sub>                      | Open load output voltage  | Driver in OFF condition                   | 0.46*VDD | 0.5*VDD | 0.54*VDD | V    |

| I <sub>OC</sub>                      | Overcurrent threshold     |                                           | 3.8      | -       | 5        | А    |

| V <sub>diagth_H</sub> <sup>(1)</sup> | Diagnostic high threshold | Driver in OFF condition                   | 0.54*VDD | 0.6*VDD | 0.66*VDD | V    |

| V <sub>diagth_L</sub> <sup>(1)</sup> | Diagnostic low threshold  | Driver in OFF condition                   | 0.36*VDD | 0.4*VDD | 0.44*VDD | V    |

1.  $V_{diagth_L} < V_{out} < V_{diagth_H} \rightarrow Open Load; V_{out} < V_{diagth_L} \rightarrow Short to GND$

## 3.5.16 Variable reluctance sensor interface

| Table 22. Variable reluctance sensor interface electrical characteristic | cs |

|--------------------------------------------------------------------------|----|

|--------------------------------------------------------------------------|----|

| Symbol                               | Parameter                                                                             | Condition                                                          | Min      | Тур      | Мах      | Unit |

|--------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------|----------|----------|------|

| V <sub>HTH</sub>                     | Input high to low<br>differential<br>threshold voltage at<br>VRIN+ and VRIN-<br>nodes | -                                                                  | -50      | -        | 50       | mV   |

| V <sub>CM</sub>                      | Common mode<br>operating range at<br>VRIN+ and VRIN-                                  | -                                                                  | 0        | 1.5      | 3        | V    |

| V <sub>cm_internal</sub>             | Internal common<br>mode voltage                                                       | Switch off hysteresis current                                      | 0.27*VDD | 0.3*VDD  | 0.33*VDD | V    |

| V <sub>diagth_H</sub> <sup>(1)</sup> | Diagnostic high<br>threshold                                                          | Diagnostic voltage referred to                                     | 0.67*VDD | 0.75*VDD | 0.82*VDD | V    |

| V <sub>diagth_L</sub> <sup>(1)</sup> | Diagnostic low<br>threshold                                                           | VRIN- (see <i>Figure 14</i> )                                      | 0.18*VDD | 0.2*VDD  | 0.22*VDD | V    |

| I <sub>diag</sub>                    | Diagnostic current                                                                    | Current from VRIN- when diagnostic on                              | 35       | 50       | 65       | μA   |

| R <sub>internal</sub> _<br>common    | Internal common mode resistor                                                         | Switch off hysteresis current                                      | 50       | 200      | 350      | kΩ   |

| I <sub>IB</sub>                      | Input bias current                                                                    | VRIN+ = VRIN- = 1.5 V                                              | -        | -        | 2        | μA   |

| I <sub>leak</sub>                    | Output leakage                                                                        | VROUT = 5 V                                                        | -        | -        | 1        | μA   |

| V <sub>CLPH</sub>                    | Input high clamping voltage                                                           | VRIN+ =  VRIN-  = 20 mA                                            | -        | 5        | -        | V    |

| V <sub>CLPL</sub>                    | Input low clamping voltage                                                            | VRIN+ =  VRIN-  =  20 mA                                           | -1.5     | -        | -0.3     | V    |

| t <sub>of</sub>                      | Output fall time                                                                      | $C_{LOAD}$ = 20 pF, $R_{LOAD}$ = 5 k $\Omega$                      | -        | -        | 300      | ns   |

| t <sub>of_1nf</sub>                  | Output fall time                                                                      | C <sub>LOAD</sub> = 1nF                                            | -        | -        | 1.5      | μs   |

| V <sub>OUTL</sub>                    | Output buffer low voltage                                                             | I <sub>sink</sub> = 2 mA                                           | -        | -        | 0.6      | V    |

| I <sub>OUTL</sub>                    | Output current capability                                                             | V <sub>out</sub> = 0.6 V                                           | 2        | -        | -        | mA   |

| t <sub>prop</sub>                    | Propagation delay                                                                     | VRS INM = 0.5 V, INP applied to<br>1 V to make VRS OUT<br>commuted | 0.1      | 0.45     | 0.8      | μs   |

1. if (VRIN- > Vdiagth\_H) or (VRIN- < Vdiagth\_L) then Fault is detected.

### 3.5.17 K-line

| Pin        | Symbol                                | Parameter                         | Test conditions                     | Min.    | Тур. | Max.        | Unit |

|------------|---------------------------------------|-----------------------------------|-------------------------------------|---------|------|-------------|------|

| 11 Xsource |                                       | Transmitter input source current  | -                                   | 10      | -    | 100         | μA   |

| KL_TX      | ITXsink                               | Transmitter input<br>sink current | KL_TX = VDD                         | -       | -    | 2.1         | μA   |

|            | VKoutL Transmitter output low voltage |                                   | IsinkK_LINE = 35 mA,<br>KL_TX = Low | -1      | -    | 1.5         | V    |

|            | VKinH                                 | Receiver input high voltage       | -                                   | 0.7xVB  | -    | VB          | V    |

| K_LINE     | VKinL                                 | Receiver input low voltage        | -                                   | -1      | -    | 0.35xV<br>B | V    |

| VKH        |                                       | Receiver input<br>hysteresis      | -                                   | 0.05xVB | -    | 0.3xVB      | V    |

|            | lKleak                                | Receiver leakage current          | KL_LINE = VB,KL_TX =<br>High        | -       | -    | 1           | μA   |

Table 23. K-Line interface electrical characteristics

| Dim                 |           |                                            |                                                         | Ňin. | ,    | Maria | 1114 |

|---------------------|-----------|--------------------------------------------|---------------------------------------------------------|------|------|-------|------|

| Pin                 | Symbol    | Parameter                                  | Parameter Test conditions                               |      | Тур. | Max.  | Unit |

| lKshor              |           | Transmitter short<br>circuit current       | KL_LINE = VB, KL_TX =<br>Low                            | 60   | -    | -     | mA   |

| K LINE              | lKrev     | Reverse battery or<br>GND loss current     | ENABLE = KEY = VB = 0 V,<br>KL_LINE = -13.5             | -    | -    | 10    | mA   |

| K_LINE              | lKpull-up | KLINE internal pull-<br>up                 | KL_TX = High                                            | 60   | -    | 140   | kΩ   |

| IKuv                |           | Under voltage<br>current                   | KEY = High, KL_TX = Low,<br>VB = 13.5 V, KL_LINE = -1 V | -    | -    | 1     | mA   |

| KL_RX               | VRXoutL   | KL_RX output low voltage                   | I <sub>sink</sub> = 0.4 mA                              | -    | -    | 0.4   | V    |

| KL_TX to<br>K_LINE  | Tp_HLT    | Transmitter turn-on delay time             | CKline = 10 nF,<br>RKline = 510 $\Omega$                | -    | -    | 5     | μs   |

| K_LINE              | T_fT      | Transmitter fall time                      | CKline = 10 nF,<br>RKline = 510 Ω                       | -    | -    | 10    | μs   |

| KL_LINE<br>to KL_RX | TpR       | Receiver turn-on delay time                | C <sub>load</sub> = 20 pF,<br>RPKL_Rx = 2 kΩ            | -    | -    | 4     | μs   |

| KL_RX               | T_fR      | Receiver fall time                         | C <sub>load</sub> = 20 pF,<br>RPKL_Rx = 2 kΩ            | -    | -    | 2     | μs   |

| T_rR                |           | Receiver rise time                         | C <sub>load</sub> = 20 pF,<br>RPKL_Rx = 2 kΩ            | -    | -    | 2     | μs   |

| K_LINE              | fMax      | Max transmission<br>Operating<br>frequency | Application note                                        | _    | -    | 60    | kHz  |

Table 23. K-Line interface electrical characteristics (continued)

### Figure 15. K-line block diagram

DocID17617 Rev 1

57

## 3.5.18 SPI interface

| Symbol               | Parameter                                                                 | Test conditions                                     | Min | Тур | Мах | Unit |

|----------------------|---------------------------------------------------------------------------|-----------------------------------------------------|-----|-----|-----|------|

| SICin                |                                                                           | -                                                   | -   | -   | 20  | pF   |

| SCKCin               | Input capacitance                                                         | -                                                   | -   | -   | 20  | pF   |

| t <sub>SCKCS</sub>   | Clock inactive time before frame                                          | -                                                   | 100 | -   | -   | ns   |

| t <sub>CSSO</sub>    | Access time                                                               | See Figure 17                                       | -   | -   | 500 | ns   |

| t <sub>SOdis</sub>   | Output data (SO) disable time No Capacitor on SO,<br>See <i>Figure 16</i> |                                                     | -   | -   | 500 | ns   |

| t <sub>lead</sub>    | Channels elect (CS) lead time                                             | See Figure 17                                       | 500 | -   | -   | ns   |

| t <sub>SCKFSO</sub>  | Output valid time                                                         | See <i>Figure 17</i> , @ f <sub>CLK</sub> = 5.4 MHz | 60  | -   | -   | ns   |

| t <sub>socs</sub>    | Output data (SO) disable time                                             | No capacitor on SO, see Figure 17                   |     | -   | 500 | ns   |

| t <sub>SIsetup</sub> | Input data (SI) set-up time                                               | See Figure 17, @ f <sub>CLK</sub> = 5.4 MHz         | 20  | -   | -   | ns   |

| t <sub>SIhold</sub>  | Input data (SI) hold time                                                 | See <i>Figure 17</i> , @ f <sub>CLK</sub> = 5.4 MHz | 20  | -   | -   | ns   |

| t <sub>SCK</sub>     | CLK period                                                                | -                                                   | 185 | -   | -   | ns   |

| t <sub>cscк</sub>    | Clock inactive time after frame                                           | -                                                   | 600 | -   | -   | ns   |

| t <sub>CSN</sub>     | CS de asserted time                                                       | -                                                   | 600 | -   | -   | ns   |

| Table 24 | SPI | characteristics  | and | timinas |

|----------|-----|------------------|-----|---------|

|          |     | character istics | ana | unnigs  |

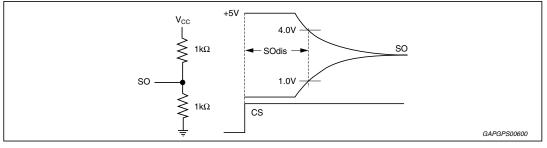

### Figure 16. -SO loading for disable time measurement

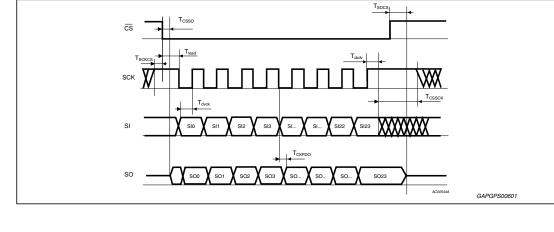

Figure 17. SPI timing diagram

# 4 Functional description

# 4.1 Chip working conditions

| -                             | Standby | Run<br>mode | VB_OV   | VB_UV   | Reset   | Over current               | Thermal<br>warning                                  |

|-------------------------------|---------|-------------|---------|---------|---------|----------------------------|-----------------------------------------------------|

| VDD_SB regulator              | ON      | ON          | ON      | ON      | ON      | Current limitation         | ON                                                  |

| VDD regulator                 | OFF     | ON          | OFF     | OFF     | ON      | Current limitation         | OFF if linked with<br>VDD current<br>limitation     |

| VDD_TRK regulator             | OFF     | ON          | OFF     | OFF     | ON      | Current limitation         | OFF if linked with<br>VDD_TRK<br>current limitation |

| All LS drivers                | OFF     | ON          | OFF     | OFF     | OFF     | Over current<br>switch off | ON                                                  |

| Diagnostics of all LS drivers | OFF     | ON          | OFF     | OFF     | ON      | -                          | ON                                                  |

| HS Driver                     | OFF     | ON          | OFF     | OFF     | OFF     | Current limitation         | ON                                                  |

| Stepper Motor<br>Driver       | OFF     | ON          | OFF     | OFF     | OFF     | Over current<br>switch off | ON                                                  |

| K-line Transceiver            | OFF     | ON          | OFF     | OFF     | OFF     | Current limitation         | ON                                                  |

| VRS                           | OFF     | ON          | OFF     | OFF     | OFF     | -                          | ON                                                  |

| SPI                           | Default | Default     | Default | Default | Default | ON                         | ON                                                  |

### Table 25. L9177 outputs working conditions

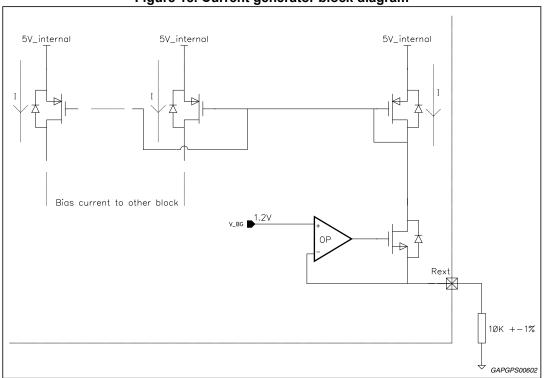

## 4.2 Chip bias current generation

The Internal current generator circuit is buffering internal band-gap voltage (1.2 V typ.) on a high precision external resistor (10 k $\Omega \pm 1$  %) and generates an accurate current reference used to create all the chip bias currents.

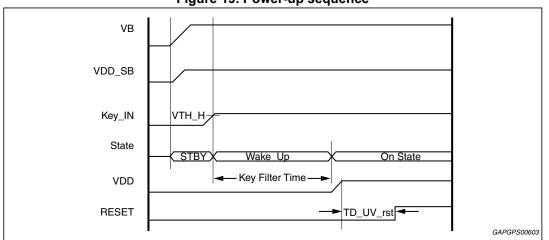

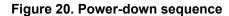

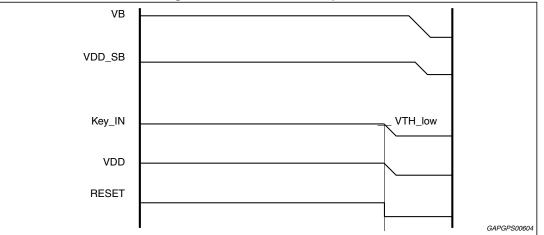

## 4.3 Power up/down sequences

Below figures show the power-on, power-off and time diagram behaviour of L9177.

VDD\_SB (standby voltage) rises together with battery input, and in standby it is always present if battery is present, no matter the KEY\_IN status.

When the KEY\_IN signal rises up and remains stable for at least T\_key\_deglitch (see *Table 8*), the device goes in ON state, meaning that all voltage regulators and functions are active.

Wake-up is an intermediate status between standby and on mode, with current consumption higher than the standby one.

When Key\_IN goes low, device goes in OFF mode but standby regulator remains ON.

Figure 19. Power-up sequence

Reset signal detects a VDD undervoltage longer than UV\_Reset\_Filter\_time by going to low level. When VDD recovers to normal level Reset signal returns to high level after Power\_On\_UV\_Reset\_Delay time (td\_UV\_rst). The Reset signal resets all the internal SPI registers.

## 4.4 SPI

SPI is a standard four wires interface, that communicates with a data word of 24 bits. By means of SPI all the channels can be driven in serial way and diagnosis is sent out. Timing of SPI's operations are reported in *Figure 17*. The input data (DIN) is read on the rising edge of the SPI's clock (SCLK), in the same way the output data (DOUT) must be read by the Microcontroller on the SCLK's rising edge.

### 4.4.1 Data in (DIN)

DIN command is used to turn On/Off internal channels which do not have Parallel Input command, and to clear diagnostic latches.

DIN is decoded at the end of the frame if the integrity checks are passed.

| Table 20. Data in (Dity) words content |        |        |          |          |          |            |        |  |

|----------------------------------------|--------|--------|----------|----------|----------|------------|--------|--|

| DIN0                                   | DIN1   | DIN2   | DIN3     | DIN4     | DIN5     | DIN6       | DIN7   |  |

| Mask                                   | LAMP_0 | LAMP_1 | VRS Diag | VRS Hys0 | VRS Hys1 | VRS Hys2   | 0      |  |