## STDVE103A

## Adaptive 3.4 Gbps 3:1 TMDS/HDMI signal equalizer

#### **Features**

- Digital video signal equalizer with 3:1 HDMI switch

- Compatible with the high-definition multimedia interface (HDMI) v1.3 digital interface

- 340 MHz maximum clock speed operation supports all video formats with deep color at maximum refresh rates

- 3.4 Gbps data rate per channel

- Fully automatic adaptive equalizer for cable lengths up to 25 m

- Selectable 50  $\Omega$  input termination to V<sub>CC</sub>: 3.135 to 3.465 V

- Low speed control lines supply to V<sub>DD</sub>:5 V (typ)

- ESD HBM model: > ±5 KV for TMDS I/Os

- Integrated open-drain I<sup>2</sup>C buffer for display data channel (DDC)

- 5.3 V tolerant DDC and HPD I/Os

- Lock-up free operation of I<sup>2</sup>C bus

- 0 to 400 kHz clock frequency for I<sup>2</sup>C bus

- Low capacitance TMDS channels

- Equalizer for signal regeneration

- Low output skew and jitter

## **Applications**

- Advanced TVs supporting the HDMI/DVI standard

- Front projectors, LCD TVs and PDPs

- Monitors and notebooks

- Set-top box and DVD players **Table 1. Device summary**

## Description

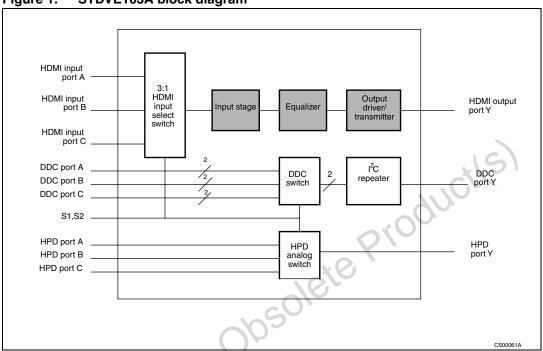

The STDVE103A integrates a 4-channel 3.4 Gbps TMDS equalizer and a 3:1 switch to select one of the three HDMI ports. The high-speed data paths and flow-through pinout minimize the internal device jitter and simplify the board layout. The equalizer overcomes the jitter effects from lossy cables. The buffer/driver on the output can drive the TMDS output signals over long distances.

Also, STDVE103A integrates the 50  $\Omega$  termination resistor on all the input channels to improve performance and reduce board space. The device can be placed in a low-power mode by disabling the output current drivers.

The differential signal from the HDMI/DVI ports can be routed through the STDVE103A to guarantee good signal quality at the HDMI receiver.

Designed for very low skew, jitter and low I/O capacitance, the switch preserves the signal integrity to pass the stringent HDMI compliance requirements.

| Order code   | Operating temperature | Package | Packaging     |

|--------------|-----------------------|---------|---------------|

| STDVE103ABTR | -40°C to 85°C         | TQFP64  | Tape and reel |

| STDVE103ABTY | -40°C to 85°C         | TQFP64  | Tray          |

June 2009 Doc ID 14911 Rev 4 1/44

Contents STDVE103A

# **Contents**

| 1    | Gener  | ral description                                     |

|------|--------|-----------------------------------------------------|

| 2    | Block  | diagram                                             |

|      | 2.1    | Application diagrams 8                              |

| 3    | Pin co | onfiguration                                        |

| 4    | Funct  | ional description12                                 |

|      | 4.1    | Adaptive equalizer                                  |

|      | 4.2    | Operating modes                                     |

|      |        | 4.2.1 SEL operating modes                           |

|      | 4.3    | HPD pins                                            |

|      | 4.4    | HPD pins       15         DDC channels       15     |

|      | 4.5    | I2C DDC line repeater                               |

|      | 4.6    | Power-down condition                                |

|      | 4.7    | Bias 17                                             |

|      | 4.8    | Timing between HPD and DDC                          |

| 5    | Maxin  | num rating                                          |

|      | 5.1    | Recommended operating conditions                    |

|      | 5.2    | DC electrical characteristics                       |

| 10   | 5.3    | DC electrical characteristics (I2C repeater)        |

| c0// | 5.4    | Dynamic switching characteristics                   |

| 03   | 5.5    | Dynamic switching characteristics (I2C repeater) 28 |

| 6    | Applic | cation information                                  |

|      | 6.1    | Power supply sequencing                             |

|      | 6.2    | Power supply requirements 38                        |

|      | 6.3    | Differential traces                                 |

|      |        | 6.3.1 I2C lines application information             |

| 7    | Packa  | nge mechanical data                                 |

| DVE103A | Content |

|---------|---------|

| DVE103A | Co      |

Obsolete Product(s). Obsolete Product(s)

List of tables STDVE103A

# **List of tables**

|   | Table 1.  | Device summary                                                                                                         | I        |

|---|-----------|------------------------------------------------------------------------------------------------------------------------|----------|

|   | Table 2.  | Pin description                                                                                                        | Э        |

|   | Table 3.  | Gain frequency response                                                                                                | 2        |

|   | Table 4.  | SEL operating modes                                                                                                    |          |

|   | Table 5.  | Bias parameter                                                                                                         | 7        |

|   | Table 6.  | Absolute maximum ratings                                                                                               |          |

|   | Table 7.  | Thermal data18                                                                                                         |          |

|   | Table 8.  | Power supply characteristics                                                                                           | Э        |

|   | Table 9.  | DC specifications for TMDS differential inputs                                                                         | Э        |

|   | Table 10. | DC specifications for TMDS differential outputs                                                                        | C        |

|   | Table 11. | DC specifications for SEL (S1, S2) inputs                                                                              | 1        |

|   | Table 12. | Input termination resistor                                                                                             | 1        |

|   | Table 13. | External reference resistor                                                                                            | 1        |

|   | Table 14. | DDC I/O pins (switch)       22         Status pins (HPD_SINK)       22         Status pins (HPD1, HPD2, HPD3)       23 | 2        |

|   | Table 15. | Status pins (HPD_SINK)                                                                                                 | 2        |

|   | Table 16. | Status pins (HPD1, HPD2, HPD3)                                                                                         | 3        |

|   | Table 17. | Supplies 24                                                                                                            | 4        |

|   | Table 18. | Input/output SDA, SCL                                                                                                  | 4        |

|   | Table 19. | Clock and data rate                                                                                                    | 5        |

|   | Table 20. | Folializer dain 25                                                                                                     | <b>'</b> |

|   | Table 21. | Differential output timings                                                                                            | 5        |

|   | Table 22. | Skew times                                                                                                             | O        |

|   | Table 23. | Turn-on and turn-off times                                                                                             |          |

|   | Table 24. | DDC I/O pins                                                                                                           |          |

|   | Table 25. | Status pins (HPD_SINK, HPD1, HPD2, HPD3, S1, S2)                                                                       |          |

|   | Table 26. | Jitter                                                                                                                 |          |

|   | Table 27. | I2C repeater         28                                                                                                |          |

|   | Table 28. | ESD performance                                                                                                        |          |

|   | Table 29. | TQFP64 mechanical data                                                                                                 |          |

|   | Table 30. | Document revision history                                                                                              | 3        |

| C | osole     | ie ,                                                                                                                   |          |

|   |           |                                                                                                                        |          |

STDVE103A List of figures

# **List of figures**

| Figure 1.  | STDVE103A block diagram                        | 7  |

|------------|------------------------------------------------|----|

| Figure 2.  | Equalizer functional diagram (one signal pair) | 7  |

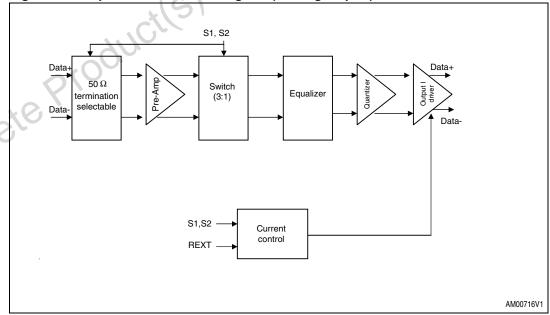

| Figure 3.  | DDC I2C bus repeater                           | 8  |

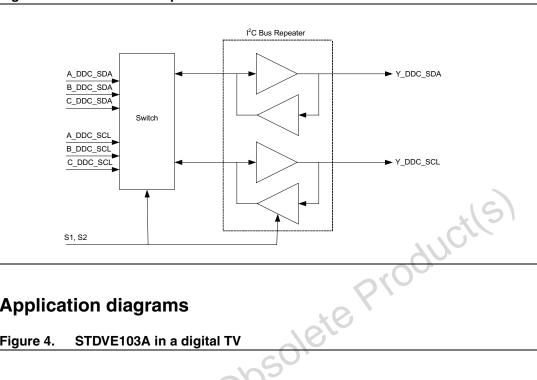

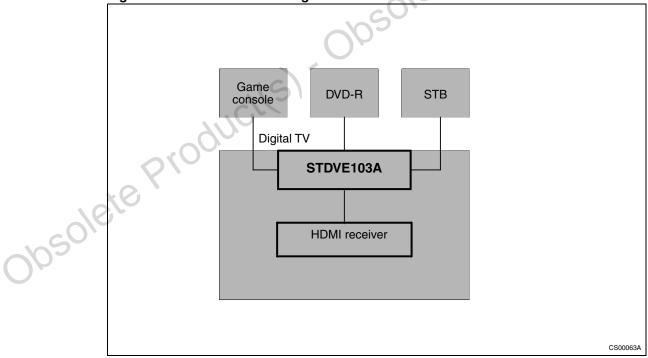

| Figure 4.  | STDVE103A in a digital TV                      | 8  |

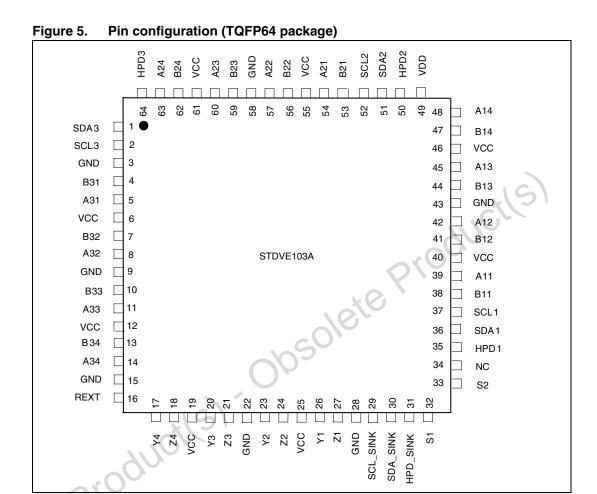

| Figure 5.  | Pin configuration (TQFP64 package)             | 9  |

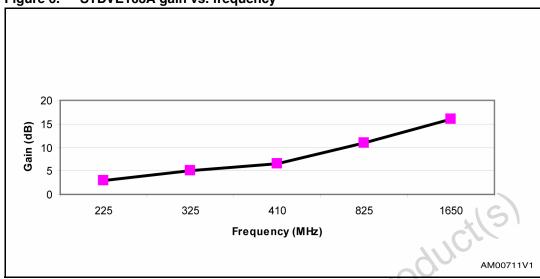

| Figure 6.  | STDVE103A gain vs. frequency                   | 13 |

| Figure 7.  | Test circuit for electrical characteristics    | 32 |

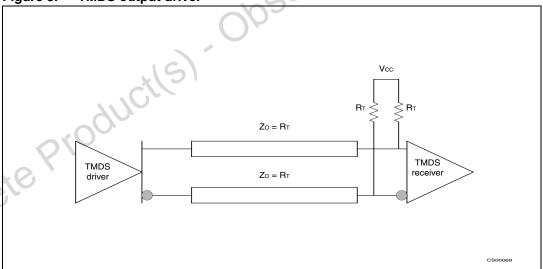

| Figure 8.  | TMDS output driver                             | 32 |

| Figure 9.  | Test circuit for HDMI receiver and driver      | 33 |

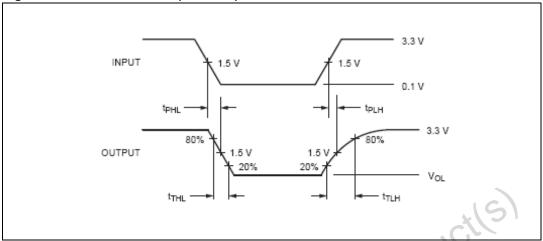

| Figure 10. | Test circuit for turn off and turn off times   | 34 |

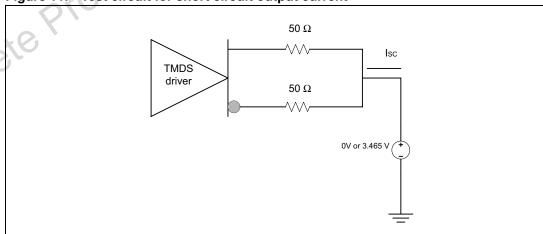

| Figure 11. | Test circuit for short circuit output current  | 34 |

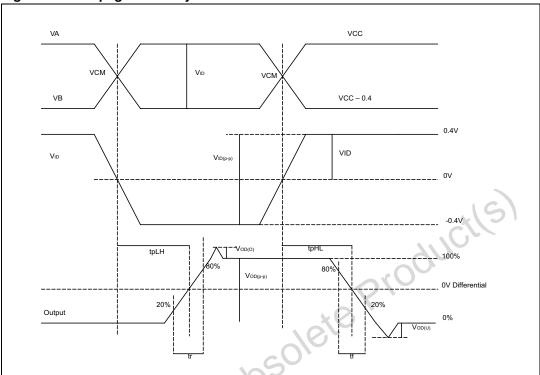

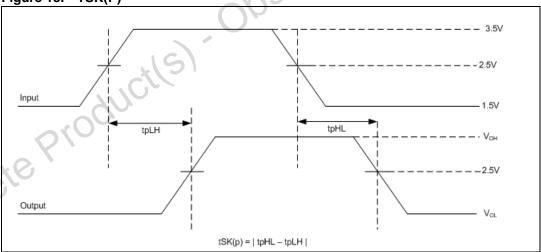

| Figure 12. | Propagation delays                             | 35 |

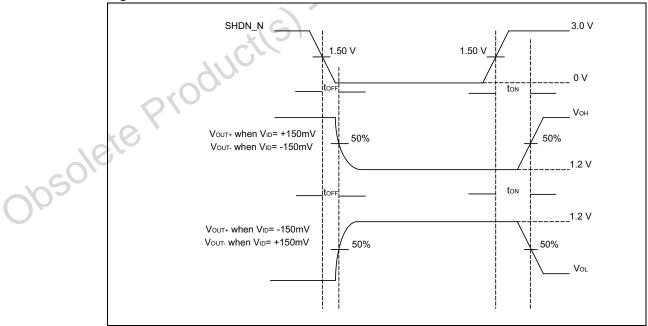

| Figure 13. | Turn-on and turn-off times                     | 35 |

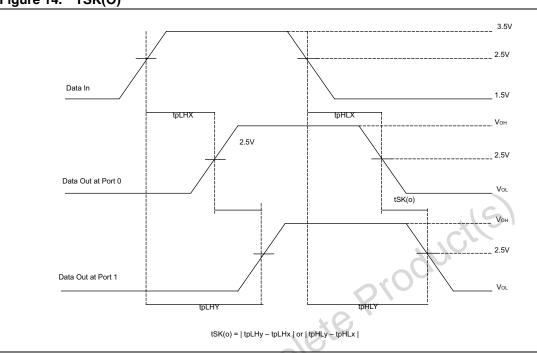

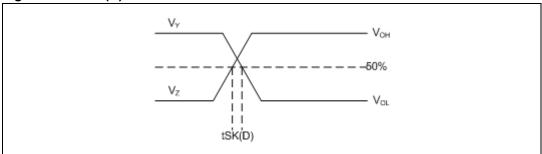

| Figure 14. | TSK(O)                                         | 36 |

| Figure 15. | TSK(O)                                         | 36 |

| Figure 16. | TSK(D)                                         | 36 |

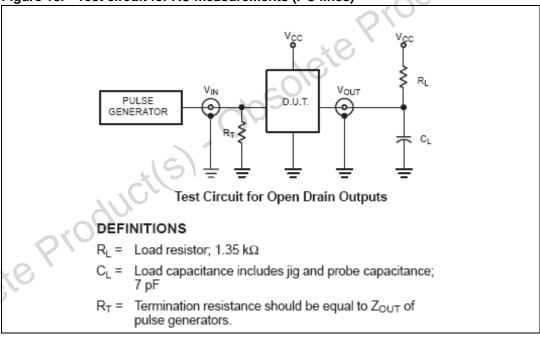

| Figure 17. | AC waveform 1 (I2C lines)                      | 37 |

| Figure 18. | Test circuit for AC measurements (I2C lines)   | 37 |

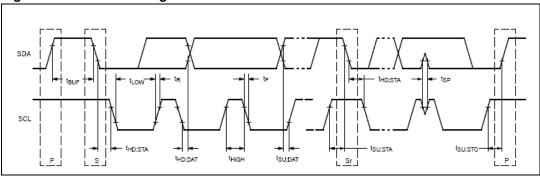

| Figure 19. | I2C bus timing                                 | 37 |

| Figure 20. | Typical application of I2C bus system          | 39 |

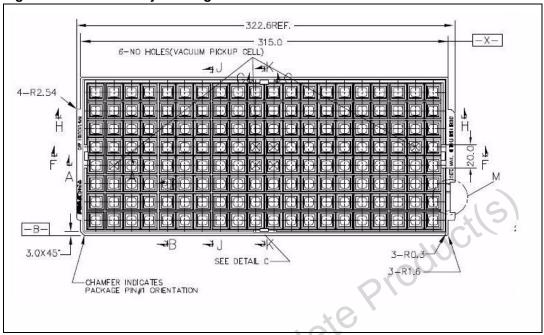

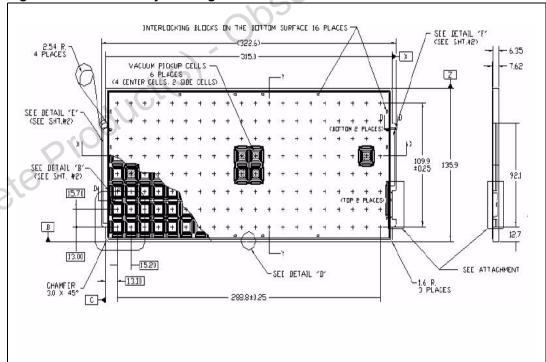

| Figure 21. | TQFP64 package outline                         | 40 |

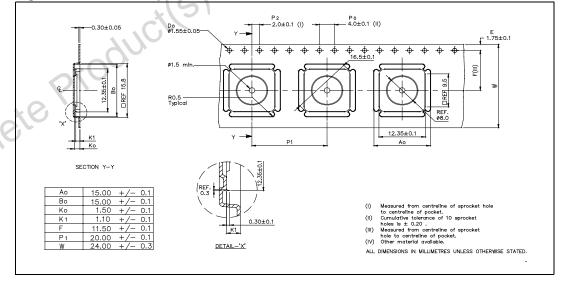

| Figure 22. | TQFP64 tape and reel information               | 41 |

| Figure 23. |                                                | 12 |

| Figure 24. | TQPF64 tray drawing dimensions                 |    |

| Obsol      | TQPF64 tray drawing                            |    |

|            |                                                |    |

General description STDVE103A

## 1 General description

The STDVE103A is a TMDS/HDMI 3:1 switch with signal equalizer. The device is a HDMI switch featuring an integrated 4-channel 3.4 Gbps TMDS equalizer and 3:1 switch to select one of the three HDMI ports (either external ports or internal sources).

The high-speed data paths and flow-through pinout minimize the internal device jitter and simplify the board layout.

The equalizer provides compensation to overcome the intersymbol interference (ISI) jitter effects from lossy cables.

The output driver buffers the TMDS output signals over long distances.

Also, the STDVE103A integrates the 50  $\Omega$  termination resistor on all the input channels to improve performance and reduce board space.

The device can operate in a low-power mode by disabling the output current drivers.

The STDVE103A is ideal for advanced TV and STB applications supporting the HDMI/DVI standard. The differential signal from the HDMI/DVI ports can be routed through the STDVE103A to guarantee good signal quality at the HDMI receiver. Designed for very low skew, jitter and low I/O capacitance, the switch preserves the signal integrity to pass the stringent HDMI compliance requirements.

The STDVE103A provides the ability to boost the incoming TMDS signal and drive it to a level which allows efficient signal recovery at the HDMI receiver. It is especially useful for boosting signals for longer distance transmission when the HDMI receiver is physically distant from the HDMI input port.

STDVE103A Block diagram

# 2 Block diagram

Figure 1. STDVE103A block diagram

Figure 2. Equalizer functional diagram (one signal pair)

STDVE103A **Block diagram**

Figure 3. DDC I<sup>2</sup>C bus repeater

#### **Application diagrams** 2.1

Figure 4. STDVE103A in a digital TV

STDVE103A Pin configuration

# 3 Pin configuration

Table 2. Pin description

| Pin number | Pin name        | Туре        | Function                                 |  |

|------------|-----------------|-------------|------------------------------------------|--|

| 1-2        | SDA3, SCL3      | I/O         | Port3 DDC bus data and clock lines       |  |

| 3          | GND             | Power       | Ground                                   |  |

| 4-5        | B31, A31        | Input, TMDS | Port 3 differential inputs for channel 1 |  |

| 6          | V <sub>CC</sub> | Power       | Supply voltage (3.3 V ± 5%)              |  |

| 7-8        | B32, A32        | Input, TMDS | Port 3 differential inputs for channel 2 |  |

| 9          | GND             | Power       | Ground                                   |  |

| 10-11      | B33, A33        | Input, TMDS | Port 3 differential inputs for channel 3 |  |

| 12         | $V_{CC}$        | Power       | Supply voltage (3.3 V ± 5%)              |  |

| 13-14      | B34, A34        | Input, TMDS | Port 3 differential inputs for channel 4 |  |

| 15         | GND             | Power       | Ground                                   |  |

57

Doc ID 14911 Rev 4

9/44

Pin configuration STDVE103A

Table 2. Pin description (continued)

|     | Pin number | Pin name         | Туре            | Function                                                                                                                                                                              |

|-----|------------|------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | 16         | R <sub>EXT</sub> | Analog          | Connect to GND through a 4.7 K ± 1% precision reference resistor. Sets the output current to generate the output voltage compliant with TMDS                                          |

|     | 17-18      | Y4, Z4           | Output,<br>TMDS | Channel 4 differential outputs                                                                                                                                                        |

|     | 19         | V <sub>CC</sub>  | Power           | Supply voltage (3.3 V ± 5%)                                                                                                                                                           |

|     | 20-21      | Y3, Z3           | Output,<br>TMDS | Channel 3 differential outputs                                                                                                                                                        |

|     | 22         | GND              | Power           | Ground                                                                                                                                                                                |

|     | 23-24      | Y2, Z2           | Output,<br>TMDS | Channel 2 differential outputs                                                                                                                                                        |

|     | 25         | V <sub>CC</sub>  | Power           | Supply voltage (3.3 V ± 5%)                                                                                                                                                           |

|     | 26-27      | Y1, Z1           | Output,<br>TMDS | Channel 1 differential outputs                                                                                                                                                        |

|     | 28         | GND              | Power           | Ground                                                                                                                                                                                |

|     | 29         | SCL_SINK         | I/O             | Sink side DDC bus clock line                                                                                                                                                          |

|     | 30         | SDA_SINK         | I/O             | Sink side DDC bus data line                                                                                                                                                           |

|     | 31         | HPD_SINK         | Input           | Sink side hot plug detector input High: 5 V power signal asserted from source to sink and EDID is ready Low: No 5 V power signal is asserted from source to sink or EDID is not ready |

|     | 32-33      | S1,S2            | Input           | Source select inputs                                                                                                                                                                  |

|     | 34         | NC               |                 | No connect                                                                                                                                                                            |

|     | 35         | HPD1             | Output          | Port 1 hot plug detector output.                                                                                                                                                      |

|     | 36         | SDA1             | I/O             | Port 1 DDC bus data line                                                                                                                                                              |

| 16  | 37         | SCL1             | I/O             | Port 1 DDC bus clock line                                                                                                                                                             |

| 60, | 38-39      | B11, A11         | Input, TMDS     | Port 1 differential inputs for channel 1                                                                                                                                              |

| 002 | 40         | $V_{CC}$         | Power           | Supply voltage (3.3 V ± 5%)                                                                                                                                                           |

| 0   | 41-42      | B12, A12         | Input, TMDS     | Port 1 differential inputs for channel 2                                                                                                                                              |

|     | 43         | GND              | Power           | Ground                                                                                                                                                                                |

|     | 44-45      | B13, A13         | Input, TMDS     | Port 1 differential inputs for channel 3                                                                                                                                              |

|     | 46         | V <sub>CC</sub>  | Power           | Supply voltage (3.3 V ± 5%)                                                                                                                                                           |

|     | 47-48      | B14, A14         | Input, TMDS     | Port 1 differential inputs for channel 4                                                                                                                                              |

|     | 49         | $V_{DD}$         | Power           | Supply voltage (5.0 V $\pm$ 10%) for DDC, HPD and source selector pins                                                                                                                |

|     | 50         | HPD2             | Output          | Port 2 hot plug detector output                                                                                                                                                       |

|     | 51         | SDA2             | I/O             | Port 2 DDC bus data line                                                                                                                                                              |

STDVE103A Pin configuration

Table 2. Pin description (continued)

|         | Pin number | Pin name        | Туре        | Function                                 |

|---------|------------|-----------------|-------------|------------------------------------------|

|         | 52         | SCL2            | I/O         | Port 2 DDC bus clock line                |

|         | 53-54      | B21, A21        | Input, TMDS | Port 2 differential inputs for channel 1 |

|         | 55         | V <sub>CC</sub> | Power       | Supply voltage (3.3 V ± 5%)              |

|         | 56-57      | B22, A22        | Input, TMDS | Port 2 differential inputs for channel 2 |

|         | 58         | GND             | Power       | Ground                                   |

|         | 59-60      | B23, A23        | Input, TMDS | Port 2 differential inputs for channel 3 |

|         | 61         | V <sub>CC</sub> | Power       | Supply voltage (3.3 V ± 5%)              |

|         | 62-63      | B24, A24        | Input, TMDS | Port 2 differential inputs for channel 4 |

|         | 64         | HPD3            |             | Port 3 hot plug detector output.         |

| Olosole | te Pro     | ducils          | 0,0         | Port 3 hot plug detector output.         |

## 4 Functional description

The STDVE103A routes physical layer signals for high bandwidth digital video and is compatible with low voltage differential signaling standards such as the TMDS. The device passes the differential inputs from a video source to a common display when it is in the active mode of operation. The device conforms to the TMDS standard on both inputs and outputs.

The low on-resistance and low I/O capacitance of the switch in STDVE103A result in a very small propagation delay. The device integrates SPDT-type switches for 3 differential data TMDS channels and 1 differential clock channel. Additionally, it integrates the switches for DDC and HPD line switching with I<sup>2</sup>C repeater on the DDC lines.

The  $I^2C$  interface of the selected input port is linked to the  $I^2C$  interface of the output port, and the hot plug detector (HPD) of the selected input port is output to HPD\_SINK. For the unused ports, the  $I^2C$  interfaces are isolated and the HPD pins are driven to L state.

## 4.1 Adaptive equalizer

The equalizer dramatically reduces the intersymbol interference (ISI) jitter and attenuation from long or lossy transmission media. The inputs present high impedance when the device is not active or when  $V_{CC}$  is absent or 0 V. In all other cases, the 50  $\Omega$  termination resistors on input channels are present.

This circuit helps to improve the signal eye pattern significantly. Shaping is performed by the gain stage of the equalizer to compensate the signal degradation and then the signals are driven on to the output ports.

The equalizer is fully adaptive and automatic in function providing smaller gain at low frequencies and higher gain at high frequencies. The equalizer is optimized internally for an adaptive operation.

Table 3. Gain frequency response

| 7/6    | Frequency<br>(MHz) | Gain in dB |

|--------|--------------------|------------|

| 0,020. | 225                | 3          |

|        | 325                | 5          |

|        | 410                | 6.5        |

|        | 825                | 11         |

|        | 1650               | 16         |

Figure 6. STDVE103A gain vs. frequency

The STDVE103A equalizer is fully adaptive and automatic in function. The equalizer's performance is optimized for all frequencies over the cable lengths from 1 m to 25 m.

#### Input termination

The STDVE103A integrates precise 50  $\Omega\pm5\%$  termination resistors, pulled up to V<sub>CC</sub>, on all its differential input channels. External terminations are not required. This gives better performance and also minimizes the PCB board space. These on-chip termination resistors should match the differential characteristic impedance of the transmission line. Since the output driver consists of current steering devices, an output voltage is not generated without a termination resistor. Output voltage levels are dependent on the value of the total termination resistance. The STDVE103A produces TMDS output levels for point-to-point links that are doubly terminated (100  $\Omega$  at each end). With the typical 10 mA output current, the STDVE103A produces an output voltage of 3.3 - 0.5 V = 2.8 V when driving a termination line terminated at each end. The input terminations are selectable thus saving power for the unselected ports.

#### **Output buffers**

Each differential output of the STDVE103A drives external 50  $\Omega$  load (pull-up resistor) and conforms to the TMDS voltage standard. The output drivers consist of 10 mA differential current-steering devices.

The driver outputs are short-circuit current limited and are high-impedance to ground when S1, S2 = HL or the device is not powered. The current steering architecture requires a resistive load to terminate the signal to complete the transmission loop from  $V_{CC}$  to GND through the termination resistor. Because the device switches the direction of the current flow and not voltage levels, the output voltage swing is determined by  $V_{CC}$  minus the voltage drop across the termination resistor. The output current drivers are controlled by the S1, S2 pin and are turned off when S1, S2 is a HL. A stable 10 mA current is derived by accurate internal current mirrors of a stable reference current which is generated by band-gap voltage across the REXT. The differential output driver provides a typical 10 mA current sink capability, which provides a typical 500 mV voltage drop across a 50  $\Omega$  termination resistor.

57

Doc ID 14911 Rev 4

13/44

#### **TMDS voltage levels**

The TMDS interface standard is a signaling method intended for point-to-point communication over a tightly controlled impedance medium. The TMDS standard uses a lower voltage swing than other common communication standards, achieving higher data rates with reduced power consumption while reducing EMI emissions and system susceptibility to noise. The device is capable of detecting differential signals as low as 100 mV within the entire common mode voltage range.

Obsolete Product(s). Obsolete Product(s)

### 4.2 Operating modes

#### 4.2.1 SEL operating modes

The active source is selected by configuring source select inputs, S1 and S2. The selected TMDS inputs from each port are switched through a 3-to-1 multiplexer. The I<sup>2</sup>C interface of the selected input port is linked to the I<sup>2</sup>C interface of the output port, and the hot plug detector (HPD) of the selected input port is output to HPD\_SINK.

Table 4. SEL operating modes

| Control pins |    | I/O selected                                                 | Hot-plug detect status                        |          | tatus    |          |

|--------------|----|--------------------------------------------------------------|-----------------------------------------------|----------|----------|----------|

| S2           | S1 | Y/Z                                                          | SCL_SINK<br>SDA_SINK                          | HPD1     | HPD2     | HPD3     |

| Н            | Н  | A1/B1 terminations<br>of A2/B2 and A3/B3<br>are disconnected | SCL1<br>SDA1                                  | HPD_SINK | OGY      | Z        |

| Н            | L  | A2/B2 terminations<br>of A1/B1 and A3/B3<br>are disconnected | SCL2<br>SDA2                                  | e z      | HPD_SINK | Z        |

| L            | L  | A3/B3 terminations<br>of A1/B1 and A2/B2<br>are disconnected | SCL3<br>SDA3                                  | Z        | Z        | HPD_SINK |

| L            | Н  | None (Z). All terminations are disconnected                  | None (Z). Pulled high by external termination | Z        | Z        | Z        |

H: logic high; L: logic low; X: don't care; Z: high impedance

## 4.3 HPD pins

The input pin HPD\_SINK is 5 V tolerant, allowing direct connection to 5 V signals. The switch is able to pass both 0 V and 5 V signal levels. The HPD\_SINK is an input pin while the HPD1, HPD2 and HPD3 are outputs.

### 4.4 DDC channels

The DDC channels are designed with a bidirectional NMOS gate, providing 5 V signal tolerance. The 5 V tolerance allows direct connection to a standard I<sup>2</sup>C bus, thus eliminating the need for a level shifter. There should be external pull-up resistors on either side of the device on both the SCL and SDA lines.

## 4.5 I<sup>2</sup>C DDC line repeater

The device contains two identical bidirectional open-drain, non-inverting buffer circuits that enable I<sup>2</sup>C DDC bus lines to be extended without degradation in system performance. The STDVE103A buffers both the serial data (DDC SDA) and serial clock (DDC SCL) on the I<sup>2</sup>C bus, while retaining all the operating modes and features of the I<sup>2</sup>C system. This enables two buses of 400 pF bus capacitance to be connected in an I<sup>2</sup>C application. These buffers are operational from a supply voltage of 3.0 to 3.6 V.

The  $I^2C$  bus capacitance limit of 400 pF restricts the number of devices and bus length. The STDVE103A enables the system designer to isolate the two halves of a bus, accommodating more  $I^2C$  devices or longer trace lengths. It can also be used to run two buses, one at 5 V and the other at 3.3 V or a 400 kHz and 100 kHz bus, where the 100 kHz bus is isolated when 400 kHz operation of the other bus is required. The STDVE103A can be used to run the  $I^2C$  bus at both 5 V and 3.3 V interface levels.

Two or more STDVE103As cannot be connected in series. The STDVE103A design does not allow this configuration. Since there is no direction pin, slightly different "legal" low voltage levels are used to avoid lock-up conditions between the input and output. A valid low applied at the input of STDVE103A is propagated as a buffered low with a slightly higher value on the enabled outputs.

When this buffered low is applied to another STDVE103A in series, the second STDVE103A will not recognize it as a valid low and will not propagate it as a buffered low again.

The S1 and S2 (SEL) lines act as control signals for the corresponding A, B or C ports. Note that the SEL line has an internal pull-down resistor. The SEL line should not change state during an I<sup>2</sup>C operation, because disabling during bus operation hangs the bus and enabling part way through a bus cycle could confuse the I<sup>2</sup>C parts being enabled. The SEL input should change state only when the global bus and the repeater port are in idle state, to prevent system failures.

The output low levels for each internal buffer are approximately 0.5 V, but the input voltage of each internal buffer must be 70 mV or more below the output low level, when the output internally is driven low. This prevents a lock-up condition from occurring when the input low condition is released.

As with the standard I<sup>2</sup>C system, pull up resistors are required to provide the logic high levels on the buffered bus. The STDVE103A has standard open collector configuration of the I<sup>2</sup>C bus. The size of the pull up resistors depends on the system, but each side of the repeater must have a pull up resistor.

This part is designed to work with standard mode and fast mode I<sup>2</sup>C devices. Standard mode I<sup>2</sup>C devices only specify 3 mA output drive, this limits the termination current to 3 mA in a generic I<sup>2</sup>C system where standard mode devices and multiple masters are possible. Under certain conditions, higher termination currents can be used.

#### 4.6 Power-down condition

The HL combination of S1, S2 is used to disable most of the internal circuitry of STDVE103A that puts the device in a low power mode of operation.

#### **4.7** Bias

The bandgap reference voltage over the external  $R_{EXT}$  reference resistor sets the internal bias reference current. This current and its factors (achieved by employing highly accurate and well matched current mirror circuit topologies) are generated on-chip and used by several internal modules. The 10 mA current used by the transmitter block is also generated using this reference current. It is important to ensure that the  $R_{EXT}$  value is within the  $\pm 1\%$  tolerance range of its typical value.

Table 5. Bias parameter

| Parameter       | Min | Тур | Max | Unit |

|-----------------|-----|-----|-----|------|

| Bandgap voltage | -   | 1.2 | -   | V    |

The output voltage swing depends on 3 components: supply voltage ( $V_{supply}$ ), termination resistor ( $R_T$ ) and current drive ( $I_{drive}$ ). The supply voltage can vary from 3.3 V  $\pm$ 5%, termination resistor can vary from 50  $\Omega\pm$ 10%.

The voltage on the output is given by:

The variation on  $I_{drive}$  must be controlled to ensure that the voltage on HDMI output is within the HDMI specification under all conditions.

This is achieved when:

$$400\text{mV} \leq_{\text{drive}} \times R_{\text{T}} \leq 600\text{mV}$$

with typical value centered at 500 mV.

## 4.8 Timing between HPD and DDC

It is important to ensure that the  $I^2C$  DDC interface is ready by the time the HPD detection is complete.

As soon as the discovery is finished by the HPD detection, the configuration data is exchanged between a source and sink through the  $I^2C$  DDC interface. The STDVE003's DDC interface is ready for communication as soon as the power supply to the chip is present and stable. When the desired port is enabled and the chip is out of shutdown mode, the  $I^2C$  DDC lines can be used for communication.

Thus, as soon as the HPD detection sequence is complete, the DDC interface can be readily used. There is no delay between the HPD detection and I<sup>2</sup>C DDC interface to be ready.

577

# 5 Maximum rating

Stressing the device above the rating listed in the "absolute maximum ratings" table may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 6. Absolute maximum ratings

| Symbol           | Parameter                                                                                 | Value        | Unit |

|------------------|-------------------------------------------------------------------------------------------|--------------|------|

| V <sub>CC</sub>  | Supply voltage to ground                                                                  | -0.5 to +4.0 | V    |

| V <sub>DD</sub>  | Supply voltage to Ground (DDC, HPD, S1, S2)                                               | -0.5 to +6.0 | ٧    |

|                  | DC input voltage (TMDS ports)                                                             | 1.7 to +4.0  | V    |

| VI               | SDA1, SCL1, SDA2, SCL2, SDA3, SCL3,SDA_SINK, SCL_SINK, HPD_SINK, HPD1, HPD2, HPD3, S1, S2 | -0.5 to +6.0 | V    |

| IO               | DC output current                                                                         | 120          | mA   |

| T <sub>STG</sub> | Storage temperature                                                                       | -65 to +150  | °C   |

| TL               | Lead temperature (10 sec)                                                                 | 300          | °C   |

Table 7. Thermal data

|      | Symbol           | Parameter                              | TQFP-64 | Unit |

|------|------------------|----------------------------------------|---------|------|

|      | $\Theta_{\! JA}$ | Thermal coefficient (junction-ambient) | 35      | °C/W |

|      |                  | AULUS                                  |         |      |

|      | 0                | 100                                    |         |      |

|      | O, Y             |                                        |         |      |

| 7/6  |                  |                                        |         |      |

| WS0. |                  |                                        |         |      |

| ) (  |                  |                                        |         |      |

|      |                  |                                        |         |      |

STDVE103A Maximum rating

## 5.1 Recommended operating conditions

#### 5.2 DC electrical characteristics

$T_A$  = -40 to +85 °C,  $V_{CC}$  = 3.3 V ± 5% <sup>(a)</sup>

Table 8. Power supply characteristics

| Cumbal          | Parameter                               | Test condition                                                                                                                             |       |      | Unit  |       |

|-----------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|-------|

| Symbol          |                                         | rest condition                                                                                                                             | Min   | Тур  | Max   | Offit |

| V <sub>CC</sub> | Supply voltage                          |                                                                                                                                            | 3.135 | 3.3  | 3.465 | V     |

| $V_{DD}$        | Supply voltage                          |                                                                                                                                            | 4.5   | 5.0  | 5.5   | ٧     |

| Icc             | Supply current                          | All inputs/outputs are enabled. Inputs are terminated with 50 $\Omega$ to V <sub>CC</sub> . V <sub>CC</sub> = 3.465 V Data rate = 3.4 Gbps | -     | epro | 300   | mA    |

| I <sub>CC</sub> | Supply current                          | S1, S2 = HL                                                                                                                                |       | -    | 20    | mA    |

| I <sub>DD</sub> | Supply current (V <sub>DD</sub> supply) | O/                                                                                                                                         | 25.   | 2    | 5     | mA    |

Table 9. DC specifications for TMDS differential inputs

| Symbol           | Parameter                                                      | Test condition                                          |                       | Value |                        | - Unit |

|------------------|----------------------------------------------------------------|---------------------------------------------------------|-----------------------|-------|------------------------|--------|

| Зупьог           | rarameter                                                      | Test condition                                          | Min                   | Тур   | Max                    | Offic  |

| V <sub>TH</sub>  | Differential input high<br>threshold<br>(peak-to-peak)         | $V_{CC} = 3.465 \text{ V}$<br>over the entire $V_{CMR}$ | -                     | 0     | 150                    | mV     |

| V <sub>TL</sub>  | Differential input low threshold                               | $V_{CC} = 3.465 \text{ V}$<br>over the entire $V_{CMR}$ | -150                  | 0     | -                      | mV     |

| V <sub>ID</sub>  | Differential input<br>voltage<br>(peak-to-peak) <sup>(1)</sup> | V <sub>CC</sub> = 3.465 V                               | 150                   | 1     | 1560                   | mV     |

| V <sub>CMR</sub> | Common mode voltage range                                      |                                                         | V <sub>CC</sub> - 0.3 |       | V <sub>CC</sub> - 0.04 | V      |

| C <sub>IN</sub>  | Input capacitance                                              | IN+ or IN- to GND<br>F = 1 MHz                          | -                     | 3.5   | -                      | pF     |

Differential output voltage is defined as I (OUT+ - OUT-) I. Differential input voltage is defined as I (IN+ - IN-) I.

Doc ID 14911 Rev 4 19/44

a. Typical parameters are measured at  $V_{CC}$  = 3.3 V,  $T_{A}$  = +25  $^{\circ}C.$

Table 10. DC specifications for TMDS differential outputs

| Symbol             | Parameter                                                       | Test condition                                                           |                      | Value |                      | Unit  |

|--------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------|----------------------|-------|----------------------|-------|

| Symbol             | Parameter                                                       | rest condition                                                           | Min                  | Тур   | Max                  | Offic |

| V <sub>OH</sub>    | Single-ended high level output voltage                          |                                                                          | V <sub>CC</sub> -10  | -     | V <sub>CC</sub> +10  | mV    |

| V <sub>OL</sub>    | Single-ended low level output voltage                           |                                                                          | V <sub>CC</sub> -600 | -     | V <sub>CC</sub> -400 | mV    |

| V <sub>swing</sub> | Single ended output swing voltage                               | $V_{CC} = 3.3 \text{ V}$ $R_{TERM} = 50 \Omega$                          | 400                  | 500   | 600                  | mV    |

| V <sub>OD</sub>    | Differential output<br>voltage<br>(peak-to-peak) <sup>(1)</sup> | $V_{CC} = 3.3 \text{ V}$ $R_{TERM} = 50 \Omega$                          | 800                  | 1000  | 1200                 | mV    |

| I <sub>OL</sub>    | Differential output low level current                           |                                                                          | 8                    | 10    | 12                   | mA    |

| ll <sub>SC</sub> l | Output driver short-<br>circuit current<br>(continuous)         | OUT± = GND<br>through a 50 $\Omega$<br>resistor.<br>See <i>Figure 11</i> | -                    | te Pr | 12                   | mA    |

| C <sub>OUT</sub>   | Output capacitance                                              | OUT+ or OUT-<br>to GND when tri-<br>state<br>F = 1 MHz                   | 1050l                | 5.5   | -                    | pF    |

<sup>1.</sup> Differential output voltage is defined as I (OUT+ - OUT-) I. Differential input voltage is defined as I (IN+ - IN-) I

STDVE103A Maximum rating

Table 11. DC specifications for SEL (S1, S2) inputs

| Symbol          | Parameter                | Test condition                                                 |      |      | Unit |       |  |

|-----------------|--------------------------|----------------------------------------------------------------|------|------|------|-------|--|

| Symbol          | Farameter                | rest condition                                                 | Min  | Тур  | Max  | Oilit |  |

| V <sub>IH</sub> | HIGH level input voltage | High level guaranteed                                          | 2.0  | -    | -    | V     |  |

| V <sub>IL</sub> | LOW level input voltage  | Low level guaranteed                                           | -0.5 | _    | 0.8  | V     |  |

| V <sub>IK</sub> | Clamp diode voltage      | $V_{CC} = 3.465 \text{ V}$<br>$I_{IN} = -18 \text{ mA}$        | -1.2 | -0.8 | -    | V     |  |

| I <sub>IH</sub> | Input high current       | V <sub>CC</sub> = 3.465 V<br>V <sub>IN</sub> = V <sub>CC</sub> | -5   | -    | +5   | μА    |  |

| I <sub>IL</sub> | Input low current        | V <sub>CC</sub> = 3.465 V<br>V <sub>IN</sub> = GND             | -5   | _    | +5   | μА    |  |

| C <sub>IN</sub> | Input capacitance        | Pin to GND<br>F = 1 MHz                                        | _    | 3.5  | 0    | pF    |  |

Table 12. Input termination resistor

| Symbol            | Parameter                                                                                    | Test condition           | 76, | Value |    | Unit |

|-------------------|----------------------------------------------------------------------------------------------|--------------------------|-----|-------|----|------|

| R <sub>TERM</sub> | Differential input<br>termination resistor on<br>IN± channels relative to<br>V <sub>CC</sub> | I <sub>IN</sub> = -10 mA | 45  | 50    | 55 | Ω    |

Table 13. External reference resistor

| Symbol           | Parameter                                       | Test condition        | Value |     |     | Unit  |

|------------------|-------------------------------------------------|-----------------------|-------|-----|-----|-------|

| Symbol           | raidinetei                                      | rest condition        | Min   | Тур | Max | o iii |

| R <sub>EXT</sub> | Resistor for TMDS compliant voltage swing range | Tolerance for R = ±1% | _     | 4.7 | _   | ΚΩ    |

Table 14. DDC I/O pins (switch)

| Symbol               | Parameter                | Test condition                                                                             |      | Value |      | Unit  |

|----------------------|--------------------------|--------------------------------------------------------------------------------------------|------|-------|------|-------|

| Symbol               | Farameter                | rest condition                                                                             | Min  | Тур   | Max  | Oilit |

| V <sub>I(DDC)</sub>  | Input voltage            |                                                                                            | GND  | _     | 5.3  | V     |

|                      | ((333)                   | V <sub>CC</sub> = 3.465 V<br>A, B, C ports = 5.3 V<br>Y port = 0.0 V<br>Switch is isolated | _    | _     | 6    | μА    |

| I <sub>I(leak)</sub> | Input leakage current    | V <sub>CC</sub> = 3.465 V<br>A, B, C ports = 3.3 V<br>Y port = 0.0 V<br>Switch is isolated | _    | _     | 2    | SHA   |

| 6                    | Input/output capacitance | V <sub>I</sub> =0 V<br>F = 1 MHz<br>Switch disabled                                        | _    | 50    | 7/10 | pF    |

| C <sub>I/O</sub>     | піриговіриї сарасітапсе  | $V_{l}$ =0 V<br>F = 1 MHz<br>Switch enabled                                                | Jete | 9     | _    | pF    |

Table 15. Status pins (HPD\_SINK)

| Symbol          | Parameter                | Test condition                                   | Value |     |     | Unit  |

|-----------------|--------------------------|--------------------------------------------------|-------|-----|-----|-------|

| Symbol          | raiametei                | rest condition                                   | Min   | Тур | Max | Oilit |

| V <sub>IH</sub> | High level input voltage | V <sub>CC</sub> = 3.3 V<br>High level guaranteed | 2.0   | -   | 5.3 | V     |

| V <sub>IL</sub> | Low level input voltage  | V <sub>CC</sub> = 3.3 V<br>Low level guaranteed  | GND   | -   | 0.8 | ٧     |

|                 | Ignut kokaga aurrant     | V <sub>CC</sub> = 3.465 V<br>Y = 5.3 V           | _     | -   | 4   | μΑ    |

| I(leak)         | Input leakage current    | V <sub>CC</sub> = 3.465 V<br>Y = 3.3 V           | _     | _   | 2   | μА    |

STDVE103A **Maximum rating**

Status pins (HPD1, HPD2, HPD3)<sup>(1)</sup> Table 16.

| Symbol           | Dovometer                                                                                                                                | Toot condition                                    |       | Value |     |    |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-------|-------|-----|----|

| Symbol           | $\begin{array}{c} \textbf{Parameter} & \textbf{Test condition} \\ \\ \textbf{Voltage} & \\ \textbf{V_I} = 0 \ \textbf{V} \\ \end{array}$ | Min                                               | Тур   | Max   | Uni |    |

| V                | Voltage                                                                                                                                  |                                                   | GND   | _     | 5.3 | ٧  |

| 6                |                                                                                                                                          | $V_I = 0 V$ $F = 1 MHz$ Switch disabled           | _     | 5     | -   | рF |

| C <sub>I/O</sub> | Input/output capacitance                                                                                                                 | $V_I = 0 V$ $F = 1 MHz$ Switch enabled            | _     | 9     |     | pF |

| V <sub>OL</sub>  | Output low voltage<br>(open drain I/Os)                                                                                                  | V <sub>CC</sub> = 3.3 V<br>I <sub>OL</sub> = 8 mA | _     |       | 0.4 | ٧  |

| ,                | parameters are measured at v <sub>CC</sub> = c                                                                                           | 005018                                            | ie P' | 00,   |     |    |

|                  | parameters are measured at V <sub>CC</sub> = 3                                                                                           | 005018                                            | ie P' | 000   |     |    |

# 5.3 DC electrical characteristics (I<sup>2</sup>C repeater)

(T<sub>A</sub> = -40 to +85 °C,  $V_{CC}$  = 3.3 V  $\pm$  5%, GND = 0 V; unless otherwise specified)

Table 17. Supplies

| Symbol          | Parameter         | Test condition |       | Unit |       |      |

|-----------------|-------------------|----------------|-------|------|-------|------|

| Symbol          | raiailletei       | rest condition | Min   | Тур  | Max   | Onit |

| V <sub>CC</sub> | DC supply voltage |                | 3.135 | 3.3  | 3.465 | V    |

#### Table 18. Input/output SDA, SCL

| Symbol           | Parameter                                         | Test condition                             |                     | Value |                     | Unit    |

|------------------|---------------------------------------------------|--------------------------------------------|---------------------|-------|---------------------|---------|

| Symbol           | Parameter                                         | rest condition                             | Min                 | Тур   | Max                 | South 1 |

| V <sub>IH</sub>  | High level input voltage                          |                                            | 0.7 V <sub>CC</sub> | -     | 5.3                 | V       |

| V <sub>IL</sub>  | Low level input voltage <sup>(1)</sup>            |                                            | -0.5                | 811   | 0.3 V <sub>CC</sub> | V       |

| V <sub>ILc</sub> | Low level input voltage contention <sup>(1)</sup> |                                            | -0.5                | , C_  | 0.4                 | V       |

| V <sub>IK</sub>  | Input clamp voltage                               | I <sub>I</sub> = -18 mA                    | SD,                 | _     | -1.2                | V       |

| I <sub>IL</sub>  | Input current low (SDA, SCL)                      | Input current low (SDA, SCL)               | )O                  | _     | 1                   | μΑ      |

|                  | Input current high                                | V <sub>I</sub> = 3.465 V<br>(SDA, SCL)     | _                   | _     | 10                  | μΑ      |

| I <sub>IH</sub>  | (SDA, SCL)                                        | V <sub>I</sub> = 5.3 V<br>(SDA, SCL)       | _                   | _     | 10                  | μΑ      |

| V                | LOW-level output                                  | I <sub>OL</sub> = 3 mA                     |                     |       | 0.4                 | V       |

| V <sub>OL</sub>  | voltage                                           | I <sub>OL</sub> = 6 mA                     |                     |       | 0.65                | V       |

| . 10             | Output high level                                 | V <sub>O</sub> = 3.6 V;<br>driver disabled | _                   | _     | 10                  | μΑ      |

| Іон              | leakage current                                   | V <sub>O</sub> = 5.3 V;<br>driver disabled | _                   | _     | 10                  | μΑ      |

| Cı               | Input capacitance                                 | V <sub>I</sub> = 3 V or 0 V                | _                   | 6     | 7 <sup>(2)</sup>    | pF      |

V<sub>IL</sub> specification is for the first low level seen by the SDA/SCL lines. V<sub>ILc</sub> is for the second and subsequent low levels seen by the SDA/SCL lines.

<sup>2.</sup> The SCL/SDA  $C_1$  is about 200 pF when  $V_{CC} = 0$  V. The STDVE103A should be used in applications where power is secured to the repeater but an active bus remains on either set of the SDA/SCL pins.

STDVE103A Maximum rating

# 5.4 Dynamic switching characteristics<sup>(b)</sup>

$T_A$  = -40 to +85 °C,  $V_{CC}$  = 3.3 V ± 5%,  $R_{TERM}$  = 50  $\Omega$  ± 5%,  $C_L$  = 5 pF).

Typical values are at  $T_A$  = +25 °C and  $V_{CC}$  = 3.3 V.

Table 19. Clock and data rate

| Symbol            | Parameter                                                    | Test condition - |     | Unit |     |       |

|-------------------|--------------------------------------------------------------|------------------|-----|------|-----|-------|

| Symbol            |                                                              |                  | Min | Тур  | Max | Oille |

| f <sub>CK</sub>   | Clock frequency<br>(1/10th of the<br>differential data rate) |                  | 25  | _    | 340 | MHz   |

| D <sub>rate</sub> | Signaling rate                                               |                  | _   | _    | 3.4 | Gbps  |

Table 20. Equalizer gain

| Symbol | Parameter      | Test condition |     | Value |     |      |  |

|--------|----------------|----------------|-----|-------|-----|------|--|

| Symbol |                | rest condition | Min | Тур   | Max | Unit |  |

| G_EQ   | Equalizer gain | At 225 MHz     | 40  | 10    | _   | dB   |  |

|        |                | At 340 MHz     | 0 - | 15    | _   | dB   |  |

Table 21. Differential output timings

| Symbol           | Parameter                                  | Test condition                                          |     |     | Unit |        |

|------------------|--------------------------------------------|---------------------------------------------------------|-----|-----|------|--------|

|                  |                                            |                                                         | Min | Тур | Max  | O.I.I. |

| t <sub>r</sub>   | Differential data and                      | 20% to 80% of V <sub>OD</sub>                           | 75  | 150 | 240  | ps     |

| t <sub>f</sub>   | clock output rise/fall<br>times            | 80% to 20% of V <sub>OD</sub>                           | 75  | 150 | 240  | ps     |

| t <sub>PLH</sub> | Differential low to high propagation delay | Alternating 1 and 0 pattern at slow and fast data rates | 250 | _   | 800  | ps     |

| t <sub>PHL</sub> | Differential high to low propagation delay | Measure at 50% V <sub>OD</sub> between input to output  | 250 | _   | 800  | ps     |

577

Doc ID 14911 Rev 4 25/44

b. The timing values in this section are tested during characterization and are guaranteed by design and simulation. Not tested in production.

Table 22. Skew times

| Symbol              | Parameter                                     | Test condition                                                                                                   |     |     | Unit |       |

|---------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----|-----|------|-------|

| Symbol              |                                               |                                                                                                                  | Min | Тур | Max  | Offic |

| t <sub>SK(O)</sub>  | Inter-pair channel-to-<br>channel output skew |                                                                                                                  | _   | _   | 100  | ps    |

| t <sub>SK(P)</sub>  | Pulse skew                                    | l t <sub>PLH</sub> - t <sub>PHL</sub> l                                                                          | _   | 25  | 80   | ps    |

| t <sub>SK(D)</sub>  | Intra-pair differential skew                  |                                                                                                                  | -   | _   | 50   | ps    |

| t <sub>SK(CC)</sub> | Output channel to channel skew                | Difference in<br>propagation<br>delay<br>(t <sub>PLH</sub> or t <sub>PHL</sub> )<br>among all output<br>channels | -   | 50  | 125  | Cps   |

#### Table 23. Turn-on and turn-off times

| Symbol           | Parameter                | Test condition                                          | Value  |     |     | Unit |  |

|------------------|--------------------------|---------------------------------------------------------|--------|-----|-----|------|--|

| Symbol           |                          |                                                         | Min    | Тур | Max | Onit |  |

| t <sub>ON</sub>  | TMDS output enable time  | Time from OE_N to OUT± change from tristate to active   | 0/05°0 | 12  | 20  | ns   |  |

| t <sub>OFF</sub> | TMDS output disable time | Time from OE_N to OUT± change from active to tri- state | _      | 6   | 10  | ns   |  |

## Table 24. DDC I/O pins

| Symbol Parameter | Test condition |             | Unit |     |  |

|------------------|----------------|-------------|------|-----|--|

| Symbol Parameter |                | Min         | Тур  | Max |  |

| 350              | Refer to       | Section 5.5 |      |     |  |

#### Table 25. Status pins (HPD\_SINK, HPD1, HPD2, HPD3, S1, S2)

| Symbol               | Parameter                                                                 | Test condition                                      | Value |     |     | Unit |  |

|----------------------|---------------------------------------------------------------------------|-----------------------------------------------------|-------|-----|-----|------|--|

| Syllibol             |                                                                           |                                                     | Min   | Тур | Max | Onit |  |

| t <sub>PD(HPD)</sub> | Propagation delay<br>(from Y_HPD to the<br>active port of HPD)            | $C_L = 10 \text{ pF},$ $R_{PU} = 1 \text{ K}\Omega$ | _     | 150 | -   | ns   |  |

| T <sub>ON/OFF</sub>  | Switch time<br>(from port select to the<br>latest valid status of<br>HPD) | C <sub>L</sub> = 10 pF                              | _     | 50  | _   | ns   |  |

STDVE103A Maximum rating

#### Table 26. Jitter

| Symbol Parameter | Test condition              |                                          | Value |     |     |          |

|------------------|-----------------------------|------------------------------------------|-------|-----|-----|----------|

|                  | raiailletei                 | rest condition                           | Min   | Тур | Max | Unit     |

| t <sub>JIT</sub> | Total jitter <sup>(1)</sup> | PRBS pattern<br>at 1.6 Gbps<br>(800 MHz) | _     | 35  | _   | ps (p-p) |

Total jitter is measured peak-to-peak with a histogram including 3500 window hits. Stimulus and fixture jitter has been subtracted. Input differential voltage =  $V_{ID}$  = 500 mV, PRBS random pattern at 1.65 Gbps, t<sub>r</sub>=t<sub>r</sub>=50 ps (20% to 80%). Jitter parameter is not production-tested but guaranteed through characterization on a sample-to-sample basis. Obsolete Products). Obsolete Products)

577

Doc ID 14911 Rev 4 27/44

# 5.5 Dynamic switching characteristics (I<sup>2</sup>C repeater)

$T_A$  = -40 to +85 °C,  $V_{CC}$  = 3.3 V  $\pm$  5%.

Typical values are at  $T_A$  = +25 °C and  $V_{CC}$  = 3.3 V.

Table 27. I<sup>2</sup>C repeater<sup>(1)</sup>

| Cumbal           | Parameter                        | Toot condition                                                                                                                                                   |     | Value |      | Unit |

|------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------|------|

| Symbol           | Parameter                        | Test condition                                                                                                                                                   | Min | Тур   | Max  | Unit |

| f <sub>SCL</sub> | I <sup>2</sup> C clock frequency | Standard mode                                                                                                                                                    | _   | _     | 100  | kHz  |

| ISCL             | 1 C clock frequency              | Fast mode                                                                                                                                                        | _   | -     | 400  | kHz  |

|                  | Low duration on SCL pin          | 100 KHz See Figure 19 Voltage on line = 5V Cmax=400 pF, Rmax = 2 K Depends on input signal rise time. Includes the 20% time intervals on both transitions.       | 4.7 | ,odl  | cile | μѕ   |

| t <sub>LOW</sub> |                                  | 400 KHz See Figure 19 Voltage on line = 5V Cmax = 400 pF, Rmax = 2 K Depends on input signal rise time. Includes the 20% time intervals on both transitions.     | 1.3 | _     | _    | μѕ   |

|                  | Production on SOL -in-           | 100 KHz See Figure 19 Voltage on line = 3.3 V Cmax = 400 pF, Rmax = 2 K Depends on input signal rise time. Includes the 20% time intervals on both transitions.  | 4.7 | _     | _    | μs   |

| t <sub>LOW</sub> | Low duration on SCL pin          | 400 KHz See Figure 19 Voltage on line = 3.3 V, Cmax = 400 pF, Rmax = 2 K Depends on input signal rise time. Includes the 20% time intervals on both transitions. | 1.3 | -     | _    | μѕ   |

STDVE103A Maximum rating

Table 27. I<sup>2</sup>C repeater<sup>(1)</sup> (continued)

|                   |                          | <b>—</b>                                                                                                                                                              |     | Value |      | Unit |

|-------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------|------|

| Symbol            | Parameter                | Test condition                                                                                                                                                        | Min | Тур   | Max  | Unit |

|                   | High doughton on COL nin | 100 KHz See Figure 19 Voltage on line = 5 V Cmax = 400 pF, Rmax = 2 K Depends on input signal rise time. Includes the 20% time intervals on both transitions          | 4.0 | -     | _    | μs   |

| <sup>t</sup> HIGH | High duration on SCL pin | 400 KHz See Figure 19 Voltage on line = 5 V Cmax = 400 pF, Rmax=2 K Depends on input signal rise time. Includes the 20% time intervals on both transitions            | 0.6 | 100/  | cile | μs   |

|                   | High dunsting on COL gir | 100 KHz Refer section 14.12, Voltage on line = 3.3 V Cmax = 400 pF, Rmax = 2 K Depends on input signal rise time. Includes the 20% time intervals on both transitions | 4.0 | _     | _    | μs   |

| <sup>t</sup> HIGH | High duration on SCL pin | 400 KHz See Figure 19 Voltage on line = 3.3 V, Cmax=400 pF, Rmax = 2 K Depends on input signal rise time. Includes the 20% time intervals on both transitions         | 0.6 | _     | _    | μѕ   |

| t <sub>PHC</sub>  | Propagation delay        | 400 KHz Waveform 1 ( <i>Figure 17</i> ) Voltage on line = 5 V, Cmax = 400 pF, Rmax = 2 K                                                                              | _   | _     | 250  | μs   |

| t <sub>PLH</sub>  | Propagation delay        | 400 KHz<br>Waveform 1 ( <i>Figure 17</i> )<br>Voltage on line = 5 V,<br>Cmax = 400 pF, Rmax = 2 K                                                                     | _   | _     | 300  | μs   |

| t <sub>PHL</sub>  | Propagation delay        | 400 KHz<br>Waveform 1 ( <i>Figure 17</i> )<br>Voltage on line = 3.3 V,<br>Cmax = 400 pF, Rmax = 2 K                                                                   | _   | _     | 250  | ns   |

Table 27. I<sup>2</sup>C repeater<sup>(1)</sup> (continued)

| Combal           | Parameter         | Took oo maliki o m                                                                                                |     | Value |     | Unit |

|------------------|-------------------|-------------------------------------------------------------------------------------------------------------------|-----|-------|-----|------|

| Symbol           | Parameter         | Test condition                                                                                                    | Min | Тур   | Max | Unit |

| t <sub>PLH</sub> | Propagation delay | 400 KHz Waveform 1 ( <i>Figure 17</i> ) Voltage on line = 3.3 V, Cmax = 400 pF, Rmax = 2 K                        | -   | _     | 450 | ns   |

| t <sub>PHL</sub> | Propagation delay | 100 KHz Waveform 1 ( <i>Figure 17</i> ) Voltage on line = 5 V, Cmax = 400 pF, Rmax = 2 K                          | _   | _     | 250 | ns   |

| t <sub>PLH</sub> | Propagation delay | 100 KHz Waveform 1 ( <i>Figure 17</i> ) Voltage on line = 5 V, Cmax = 400 pF, Rmax = 2 K                          | _   | .0di  | 300 | ns   |

| t <sub>PHL</sub> | Propagation delay | 100 KHz Waveform 1 ( <i>Figure 17</i> ) Voltage on line = 3.3 V, Cmax = 400 pF, Rmax = 2 K                        | e-P | -     | 250 | ns   |

| t <sub>PLH</sub> | Propagation delay | 100 KHz<br>Waveform 1 ( <i>Figure 17</i> )<br>Voltage on line = 3.3 V,<br>Cmax = 400 pF, Rmax = 2 K               | _   | _     | 450 | ns   |

| t <sub>f</sub>   | Output fall time  | 400 KHz<br>Waveform 1 ( <i>Figure 17</i> ) <sup>(2)</sup><br>Voltage on line = 5 V<br>Cmax = 400 pF, Rmax = 2 K   | _   | _     | 300 | ns   |

| ч                | Output fall time  | 400 KHz<br>Waveform 1 <sup>(2)</sup><br>Voltage on line = 3.3 V<br>Cmax = 400pF, Rmax = 2 K                       | -   | _     | 300 | ns   |

| oso)             | Output fall time  | 100 KHz<br>Waveform 1 ( <i>Figure 17</i> ) <sup>(2)</sup><br>Voltage on line = 5 V<br>Cmax = 400 pF, Rmax = 2 K   | _   | _     | 300 | ns   |

| ·f               | Capatian unic     | 100 KHz<br>Waveform 1 ( <i>Figure 17</i> ) <sup>(2)</sup><br>Voltage on line = 3.3 V<br>Cmax = 400 pF, Rmax = 2 K | _   | _     | 300 | ns   |

STDVE103A Maximum rating

Table 27. I<sup>2</sup>C repeater<sup>(1)</sup> (continued)

| Symbol         | Parameter        | Test condition                                                                                                    |     | Value |      | Unit  |

|----------------|------------------|-------------------------------------------------------------------------------------------------------------------|-----|-------|------|-------|

| Symbol         | Farameter        | rest condition                                                                                                    | Min | Тур   | Max  | Oilit |

| t <sub>r</sub> | Output rise time | 400 KHz<br>Waveform 1 ( <i>Figure 17</i> ) <sup>(2)</sup><br>Voltage on line = 5 V<br>Cmax = 400 pF, Rmax = 2 K   | _   | _     | 300  | ns    |

|                |                  | 400 KHz<br>Waveform 1 ( <i>Figure 17</i> ) <sup>(2)</sup><br>Voltage on line = 3.3 V<br>Cmax = 400 pF, Rmax = 2 K | _   | _     | 300  | ns    |

| t <sub>r</sub> | Output rise time | 100 KHz<br>Waveform 1, <sup>(2)</sup><br>Voltage on line = 5 V<br>Cmax = 400 pF, Rmax = 2 K                       | _   | 1503  | 1000 | ns    |

|                |                  | 100 KHz<br>Waveform 1 ( <i>Figure 17</i> ) <sup>(2)</sup><br>Voltage on line = 3.3 V<br>Cmax = 400 pF, Rmax = 2 K | e-P | _     | 1000 | ns    |

<sup>1.</sup> All the timing values are tested during characterization and are guaranteed by design and simulation. Not tested in production.

Table 28. ESD performance

| ESD TMDS<br>(HBM) Other | $\sim$ | Human body model Human body model | _ | ±5        | _ | kV |

|-------------------------|--------|-----------------------------------|---|-----------|---|----|

| (HBM) Other             | I/Os   | Human body model                  |   |           |   |    |

|                         |        | Traman body model                 | _ | <u>±2</u> | - | kV |

| solete                  | ,      |                                   |   |           |   |    |

<sup>2.</sup> The t<sub>r</sub> transition time is specified with maximum load of 2 kΩ pull-up resistance and 400 pF load capacitance. Different load resistance and capacitance will alter the RC time constant, thereby changing the propagation delay and transition times. Refer to *Figure 9*.

Figure 7. Test circuit for electrical characteristics

- 1.  $C_L$  = load capacitance: include jig and probe capacitance.

- 2.  $R_T$  = termination resistance; should be equal to  $Z_{OUT}$  of the pulse generator.

Figure 8. TMDS output driver

- 1.  $Z_O$  = characteristic impedance of the cable.

- 2.  $R_T$  = termination resistance: should be equal to  $Z_O$  of the cable. Both are equal to  $50_W$ .

57

STDVE103A **Maximum rating**

$V_{\text{CC}}$ Rт Rт Α C<sub>L</sub> = VID 0.5pF TMDS TMDS Vcc  $V_{\mathsf{A}}$ VY receiver driver В  $\overline{z}$  $R_{\text{T}}$  $V_{\text{ID}} = V_{\text{A}} - V_{\text{B}}$ ٧z  $V_{\text{Swing}} = V_{\text{Y}} - V_{\text{Z}}$ Obsolete Product(s). Obsolete Product(s).

Figure 9. Test circuit for HDMI receiver and driver

577

1.15 V

1.0 V

1.15 V

1.

Figure 10. Test circuit for turn off and turn off times

1.  $C_L = 5 pF$

Figure 11. Test circuit for short circuit output current

CS00072A

STDVE103A Maximum rating

Figure 12. Propagation delays

Figure 13. Turn-on and turn-off times

Figure 14. TSK(O)

Figure 15. TSK(P)

Figure 16. TSK(D)

STDVE103A Maximum rating

Figure 17. AC waveform 1 (I<sup>2</sup>C lines)

Figure 18. Test circuit for AC measurements (I<sup>2</sup>C lines)

Figure 19. I<sup>2</sup>C bus timing

577

Doc ID 14911 Rev 4

37/44

## 6 Application information

### 6.1 Power supply sequencing

Proper power-supply sequencing is advised for all CMOS devices. It is recommended to always apply  $V_{CC}$  before applying any signals to the input/output or control pins.

## 6.2 Power supply requirements

Bypass each of the  $V_{CC}$  pins with 0.1  $\mu$ F and 1 nF capacitors in parallel as close to the device as possible, with the smaller-valued capacitor as close to the  $V_{CC}$  pin of the device as possible.

All  $V_{CC}$  pins can be tied to a single 3.3 V power source. A 0.01  $\mu F$  capacitor is connected from each  $V_{CC}$  pin directly to ground to filter supply noise. The maximum power supply variation can only be  $\pm 5\%$  as per the HDMI specifications.

The maximum tolerable noise ripple on 3.3 V supply must be within a specified limit.

#### 6.3 Differential traces

The high-speed TMDS inputs are the most critical parts for the device. There are several considerations to minimize discontinuities on these transmission lines between the connectors and the device.

- (a) Maintain  $100-\Omega$  differential transmission line impedance into and out of the STDVE103A.

- (b) Keep an uninterrupted ground plane below the high-speed I/Os.

- (c) Keep the ground-path vias to the device as close as possible to allow the shortest return current path.

- (d) Layout of the TMDS differential inputs should be with the shortest stubs from the connectors.

Output trace characteristics affect the performance of the STDVE103A. Use controlled impedance traces to match trace impedance to both the transmission medium impedance and termination resistor. Run the differential traces close together to minimize the effects of the noise. Reduce skew by matching the electrical length of the traces. Avoid discontinuities in the differential trace layout. Avoid 90 degree turns and minimize the number of vias to further prevent impedance discontinuities.

Doc ID 14911 Rev 4

38/44

## 6.3.1 I<sup>2</sup>C lines application information

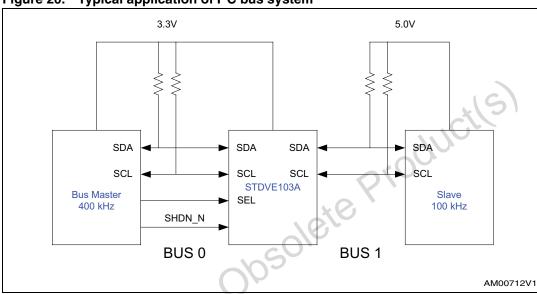

A typical application is shown in the figure below. In the example, the system master is running on a  $3.3 \text{ V I}^2\text{C}$ -bus while the slave is connected to a 5 V bus. Both buses run at 100 kHz unless the slave bus is isolated and then the master bus can run at 400 kHz. Master devices can be placed on either bus.

Figure 20. Typical application of I<sup>2</sup>C bus system

The STDVE103A DDC lines are 5 V tolerant; so it does not require any extra circuitry to translate between the different bus voltages.

**5**//

# 7 Package mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: www.st.com. ECOPACK<sup>®</sup> is an ST trademark.

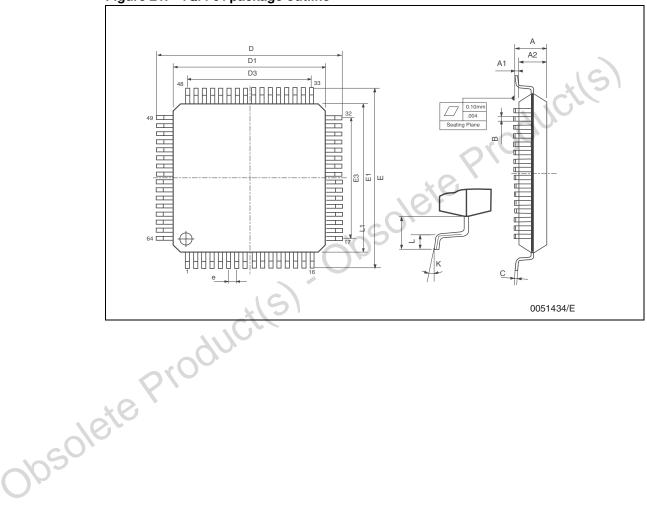

Figure 21. TQFP64 package outline

Table 29. TQFP64 mechanical data

| Symbol | Millimeters |      |       |  |  |  |

|--------|-------------|------|-------|--|--|--|

| Symbol | Min         | Тур  | Max   |  |  |  |

| A      | _           | _    | 1.20  |  |  |  |

| A1     | 0.05        | 0.10 | 0.15  |  |  |  |

| A2     | 0.95        | 1    | 1.05  |  |  |  |

| b      | 0.17        | 0.22 | 0.27  |  |  |  |

| С      | 0.09        | 0.15 | 0.20  |  |  |  |

| D      | 11.80       | 12   | 12.20 |  |  |  |

| D1     | 9.80        | 10   | 10.20 |  |  |  |