# 50 $\Omega$ ultra thin balun with integrated harmonic filter / conjugate match balun to nRF51822-CTAA/CTAC in WLCSP

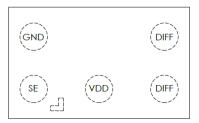

Flip-Chip (5 bumps) package

#### Pin coordinates

Top view

#### Product status

BALF-NRF01J5

#### **Features**

- 50  $\Omega$  nominal input / conjugate match to Nordic Semiconductor chips nRF51822 WLCSP

- Low insertion loss

- · Low amplitude imbalance

- · Low phase imbalance

- Small footprint: < 1.2 mm<sup>2</sup>

- Extra low profile < 350 μm after reflow</li>

- · High RF performance

- · RF BOM and area reduction

#### **Applications**

- · 2.45 GHz impedance matched balun filter

- Optimized for Nordic's chip set nRF51822-CTAA, CTAC

- Wearable applications

#### **Description**

This device is an ultraminiature extra thin balun that integrates matching network and harmonics filter.

Matching impedance has been customized for the nRF51822-CTAA and CTAC WLCSP Nordic Semiconductor circuits.

Based on IPD technology on high resistivity silicium it optimizes the RF performance.

The BALF-NRF01J5 has been tested and approved by Nordic Semiconductor.

STMicroelectronics qualified this product intended to be used in System in Package module based on standard reliability procedure. For more details, please contact ST representatives.

It is the responsibility of the customer to perform qualification reliability verifications as it is related to customer specific application / mission profile and module design / process.

# 1 Characteristics

Table 1. Absolute ratings (limiting values)

| Symbol           | Parameter                                                                                         |      |      | Value |      |  |

|------------------|---------------------------------------------------------------------------------------------------|------|------|-------|------|--|

|                  | Falameter                                                                                         | Min. | Тур. | Max.  | Unit |  |

| P <sub>IN</sub>  | Input power RF <sub>IN</sub>                                                                      |      | -    | 20    | dBm  |  |

|                  | ESD ratings human body model (JESD22-A114-C), all I/O one at a time while others connected to GND | 2000 | -    |       |      |  |

| V <sub>ESD</sub> | ESD ratings charge device model (JESD22-C101-C)                                                   | 500  | -    |       | V    |  |

|                  | ESD ratings machine model, all I/O                                                                | 200  | -    |       |      |  |

| T <sub>OP</sub>  | Operating temperature                                                                             | -40  | -    | +85   | °C   |  |

Table 2. Impedances (T<sub>amb</sub> = 25 °C)

| Symbol           | Parameter                             | Value |         |      | Unit |

|------------------|---------------------------------------|-------|---------|------|------|

|                  | Faiailietei                           | Min.  | Тур.    | Max. | Onit |

| Z <sub>OUT</sub> | Nominal differential output impedance | -     | matched | -    | Ω    |

| Z <sub>IN</sub>  | Nominal input impedance               | -     | 50      | -    | Ω    |

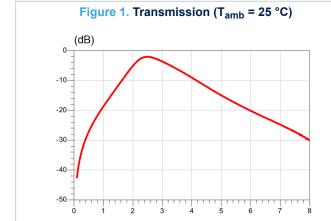

Table 3. RF performances (T<sub>amb</sub> = 25 °C)

| Symbol         | Parameter                    |          | Value |      | Unit |      |

|----------------|------------------------------|----------|-------|------|------|------|

| Symbol         | raiametei                    |          |       | Тур. | Max. | Onne |

| f              | Frequency range (bandwidth)  |          | 2400  |      | 2540 | MHz  |

| IL             | Insertion loss in bandwidth  |          |       | 2.2  | 2.4  | dB   |

| R <sub>L</sub> | Return loss in bandwidth     |          | 9     | 12   |      | dB   |

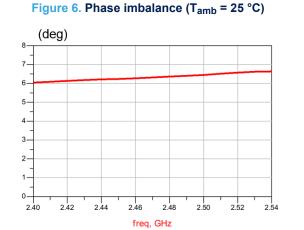

| φimb           | Phase imbalance              |          | -7.2  | 7    | 7.2  | 0    |

| Aimb           | Amplitude imbalance          |          | -0.5  | 0.3  | 0.5  | dB   |

| 2f0            | 2nd harmonic S21 attenuation | 4880 MHz | 12    | 13.5 |      | dB   |

| 3f0            | 3rd harmonic S21 attenuation | 7320 MHz | 24    | 25   |      | dB   |

DS12205 - Rev 3 page 2/9

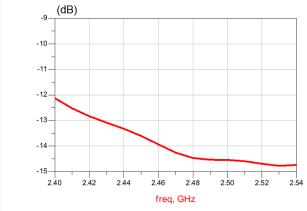

#### 1.1 On-board measurements

rigure 2. Insertion loss (T<sub>amb</sub> = 25 °C)

(dB)

-1.8

-2.0

-2.1

-2.2

-2.3

-2.4

2.40

2.42

2.44

2.46

2.48

2.50

2.52

2.54

freq, GHz

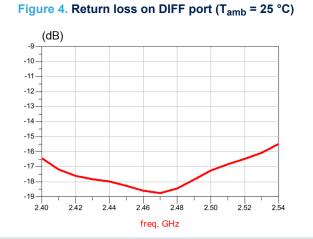

Figure 3. Return loss on SE port (T<sub>amb</sub> = 25 °C)

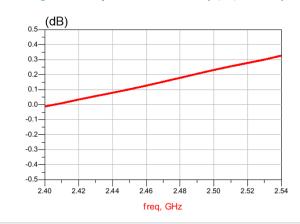

Figure 5. Amplitude imbalance (T<sub>amb</sub> = 25 °C)

DS12205 - Rev 3 page 3/9

## 2 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: www.st.com. ECOPACK® is an ST trademark.

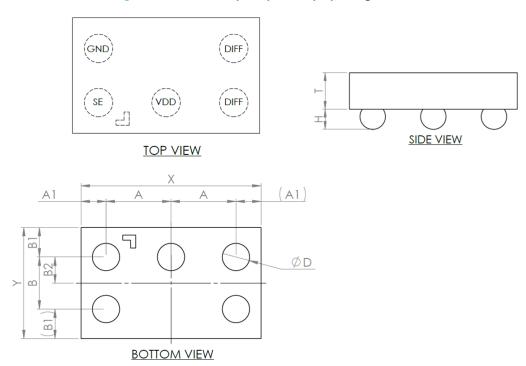

### 2.1 Ultra thin Flip-Chip 5 bumps package information

- Epoxy meets UL94, V0

- · Lead-free package

Figure 7. Ultra thin Flip-Chip 5 bumps package outline

Table 4. Ultra thin Flip-Chip 5 bumps package mechanical data

| Parameter | Description                                   | Min. | Тур.  | Max. | Unit |

|-----------|-----------------------------------------------|------|-------|------|------|

| X         | X dimension of the die                        |      | 1345  | 1375 |      |

| Y         | Y dimension of the die                        |      | 815   | 845  |      |

| Α         | X pitch 500                                   |      |       |      |      |

| В         | B Y pitch 400                                 |      |       |      |      |

| A1        | Distance from bump to edge of die on X axis   |      | 172.5 |      | um   |

| B1        | Distance from bump to edge of die on Y axis   |      | 207.5 |      | μm   |

| B2        | Distance from bump to center of die on Y axis |      |       |      |      |

| D         | Bump diameter                                 | 202  | 227   | 252  |      |

| Т         | Substrate thickness                           | 190  | 200   | 210  |      |

| Н         | Bump height                                   | 117  | 142   | 167  |      |

DS12205 - Rev 3 page 4/9

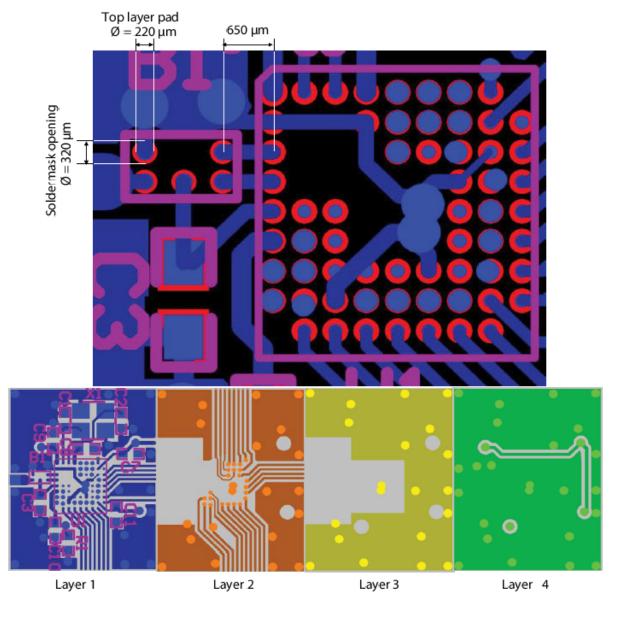

Figure 8. Recommended land pattern

Screenprinting, stencil windows 290 x 290 x 100 µm3 (coeff 0.725) Note:

Note: to achieve minimum component height after PCB reflow, the below recommendations must be followed : in assembly process, a flux must be used, not a solder paste

DS12205 - Rev 3 page 5/9

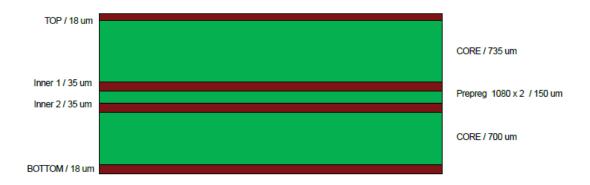

Figure 9. PCB stack-up recommendation

#### 2.2 Flip-chip 5 bumps packing information

Figure 10. Marking

Dot, ST logo

☐ ECOPACK grade

xx = marking

z = manufacturing

location

yww = datecode

Note: More packing information is available in the application note:

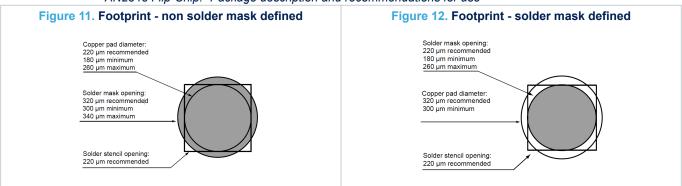

AN2348 Flip-Chip: "Package description and recommendations for use"

DS12205 - Rev 3 page 6/9

# **3** Ordering information

**Table 5. Ordering information**

| Order code   | Marking | Package           | Weight   | Base qty. | Delivery mode |

|--------------|---------|-------------------|----------|-----------|---------------|

| BALF-NRF01J5 | TL      | Flip-Chip 5 bumps | 0.631 mg | 5000      | Tape and reel |

DS12205 - Rev 3 page 7/9

# **Revision history**

**Table 6. Document revision history**

| Date        | Revision | Changes                                                                                |

|-------------|----------|----------------------------------------------------------------------------------------|

| 20-Jun-2017 | 1        | Initial release.                                                                       |

| 22-Feb-2018 | 2        | Updated Description and Table 4. Ultra thin Flip-Chip 5 bumps package mechanical data. |

| 04-Apr-018  | 3        | Updated Table 4. Ultra thin Flip-Chip 5 bumps package mechanical data.                 |

DS12205 - Rev 3 page 8/9

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2018 STMicroelectronics - All rights reserved

DS12205 - Rev 3 page 9/9