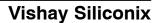

## **Matched N-Channel JFET Pairs**

| PRODUCT SUMMARY |                          |                              |                          |                         |                                                |  |  |  |  |  |  |

|-----------------|--------------------------|------------------------------|--------------------------|-------------------------|------------------------------------------------|--|--|--|--|--|--|

| Part Number     | V <sub>GS(off)</sub> (V) | V <sub>(BR)GSS</sub> Min (V) | g <sub>fs</sub> Min (mS) | I <sub>G</sub> Typ (pA) | V <sub>GS1</sub> - V <sub>GS2</sub>   Max (mV) |  |  |  |  |  |  |

| 2N5564          | −0.5 to −3               | -40                          | 7.5                      | -3                      | 5                                              |  |  |  |  |  |  |

| 2N5565          | −0.5 to −3               | -40                          | 7.5                      | -3                      | 10                                             |  |  |  |  |  |  |

| 2N5566          | −0.5 to −3               | -40                          | 7.5                      | -3                      | 20                                             |  |  |  |  |  |  |

### **FEATURES**

- Two-Chip Design

- High Slew Rate

- Low Offset/Drift Voltage

- Low Gate Leakage: 3 pA

- Low Noise: 12 nV√Hz @ 10 Hz

- Good CMRR: 76 dB

- Minimum Parasitics

#### **BENEFITS**

- Tight Differential Match vs. Current

- Improved Op Amp Speed, Settling Time Accuracy

- Minimum Input Error/Trimming Requirement

- Insignificant Signal Loss/Error Voltage

- High System Sensitivity

- Minimum Error with Large Input Signals

- Maximum High Frequency Performance

### **APPLICATIONS**

- Wideband Differential Amps

- High-Speed, Temp-Compensated, Single-Ended Input Amps

- High-Speed Comparators

- Impedance Converters

- Matched Switches

#### **DESCRIPTION**

The 2N5564/5565/5566 are matched pairs of JFETs mounted in a TO-71 package. This two-chip design reduces parasitics for good performance at high frequency while ensuring extremely tight matching. This series features high breakdown voltage ( $V_{(BR)DSS}$  typically > 55 V), high gain (typically > 9 mS), and <5 mV offset between the two die.

The hermetically-sealed TO-71 package is available with full military processing (see Military Information).

For similar products see the low-noise U/SST401 series, and the low-leakage 2N5196/5197/5198/5199 data sheets.

### **ABSOLUTE MAXIMUM RATINGS**

| Gate-Drain, Gate-Source Voltage                          |

|----------------------------------------------------------|

| Gate-Gate Voltage                                        |

| Gate Current                                             |

| Lead Temperature ( $^{1}/_{16}$ " from case for 10 sec.) |

| Storage Temperature65 to 200°C                           |

Operating Junction Temperature

-55 to 150°C

Power Dissipation:

Per Side<sup>a</sup>

325 mW

Total<sup>b</sup>

650 mW

Notes

a. Derate 2.6 mW/°C above 25°C

b. Derate 5.2 mW/°C above 25°C

# Vishay Siliconix

| _                                                              |                                                       |                                                                            |           | Limits |              |        |              |        |              |            |

|----------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------|-----------|--------|--------------|--------|--------------|--------|--------------|------------|

|                                                                |                                                       |                                                                            |           | 2N5564 |              | 2N5565 |              | 2N5566 |              |            |

| Parameter                                                      | Symbol                                                | Test Conditions                                                            | Typa      | Min    | Max          | Min    | Max          | Min    | Max          | Unit       |

| Static                                                         |                                                       |                                                                            |           |        |              |        |              |        |              |            |

| Gate-Source<br>Breakdown Voltage                               | V <sub>(BR)GSS</sub>                                  | $I_G = -1 \mu A$ , $V_{DS} = 0 V$                                          | -55       | -40    |              | -40    |              | -40    |              | V          |

| Gate-Source<br>Cutoff Voltage                                  | V <sub>GS(off)</sub>                                  | V <sub>DS</sub> = 15 V, I <sub>D</sub> = 1 nA                              | -2        | -0.5   | -3           | -0.5   | -3           | -0.5   | -3           | V          |

| Saturation Drain<br>Current <sup>b</sup>                       | I <sub>DSS</sub>                                      | $V_{DS}$ = 15 V, $V_{GS}$ = 0 V                                            | 20        | 5      | 30           | 5      | 30           | 5      | 30           | mA         |

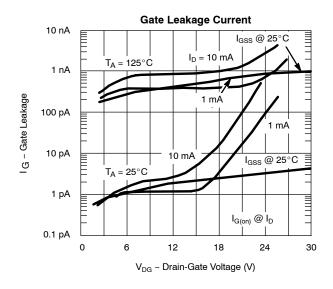

| Gate Reverse Current                                           | I <sub>GSS</sub>                                      | $V_{GS} = -20 \text{ V}, V_{DS} = 0 \text{ V}$ $T_A = 150^{\circ}\text{C}$ | -5<br>-10 |        | -100<br>-200 |        | -100<br>-200 |        | -100<br>-200 | pA<br>nA   |

|                                                                |                                                       | V <sub>DG</sub> = 15 V, I <sub>D</sub> = 2 mA                              | -10       |        | -200         |        | -200         |        | -200         | pA         |

| Gate Operating Current <sup>c</sup>                            | lG                                                    | $T_A = 125^{\circ}C$                                                       | -1        |        |              |        |              |        |              | nA         |

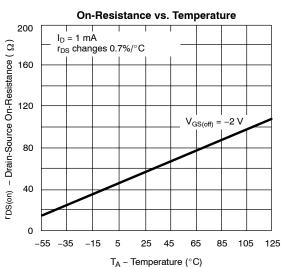

| Drain-Source<br>On-Resistance                                  | r <sub>DS(on)</sub>                                   | V <sub>GS</sub> = 0 V, I <sub>D</sub> = 1 mA                               | 50        |        | 100          |        | 100          |        | 100          | Ω          |

| Gate-Source Voltage <sup>c</sup>                               | V <sub>GS</sub>                                       | $V_{DG}$ = 15 V, $I_D$ = 2 mA                                              | -1.2      |        |              |        |              |        |              |            |

| Gate-Source<br>Forward Voltage                                 | V <sub>GS(F)</sub>                                    | $I_G = 2 \text{ mA}$ , $V_{DS} = 0 \text{ V}$                              | 0.7       |        | 1            |        | 1            |        | 1            | V          |

| Dynamic                                                        |                                                       |                                                                            | •         |        |              |        |              |        | •            | •          |

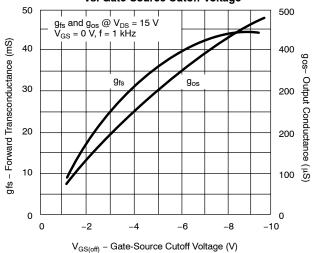

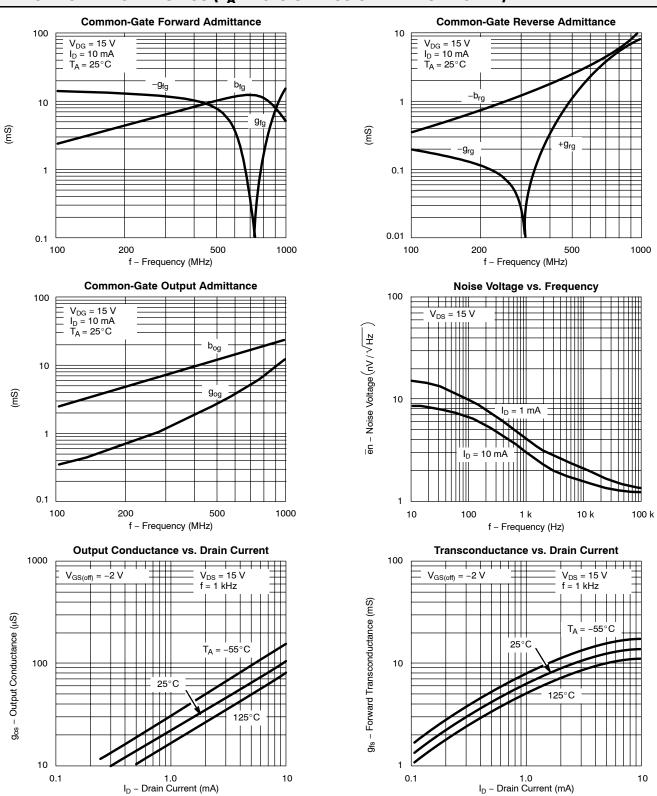

| Common-Source<br>Forward Transconductance                      | 9 <sub>fs</sub>                                       | V <sub>DS</sub> = 15 V, I <sub>D</sub> = 2 mA                              | 9         | 7.5    | 12.5         | 7.5    | 12.5         | 7.5    | 12.5         | mS         |

| Common-Source<br>Output Conductance                            | gos                                                   | f = 1 kHz                                                                  | 35        |        | 45           |        | 45           |        | 45           | μS         |

| Common-Source<br>Forward Transconductance <sup>d</sup>         | 9 <sub>fs</sub>                                       | $V_{DS} = 15 \text{ V}, I_{D} = 2 \text{ mA}$<br>f = 100 MHz               | 8.5       | 7      |              | 7      |              | 7      |              | mS         |

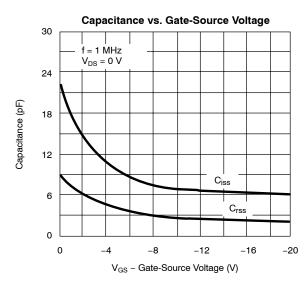

| Common-Source<br>Input Capacitance                             | C <sub>iss</sub>                                      | V 45V1 0 A                                                                 | 10        |        | 12           |        | 12           |        | 12           |            |

| Common-Source<br>Reverse Transfer<br>Capacitance               | C <sub>rss</sub>                                      | $V_{DS}$ = 15 V, $I_D$ = 2 mA f = 1 MHz                                    | 2.5       |        | 3            |        | 3            |        | 3            | pF         |

| Equivalent Input<br>Noise Voltage                              | ē <sub>n</sub>                                        | $V_{DS} = 15 \text{ V}, I_D = 2 \text{ mA}$<br>f = 10 Hz                   | 12        |        | 50           |        | 50           |        | 50           | nV∕<br>√Hz |

| Noise Figure                                                   | NF                                                    | $R_G$ = 10 $M\Omega$                                                       |           |        | 1            |        | 1            |        | 1            | dB         |

| Matching                                                       |                                                       |                                                                            |           |        |              |        |              | -      | -            | -          |

| Differential<br>Gate-Source Voltage                            | V <sub>GS1</sub> -V <sub>GS2</sub>                    | V <sub>DG</sub> = 15 V, I <sub>D</sub> = 2 mA                              |           |        | 5            |        | 10           |        | 20           | mV         |

| Gate-Source Voltage<br>Differential Change<br>with Temperature | $\frac{\Delta  V_{\rm GS1} - V_{\rm GS2} }{\Delta T}$ | $V_{DG}$ = 15 V, $I_{D}$ = 2 mA $T_{A}$ = -55 to 125 °C                    |           |        | 10           |        | 25           |        | 50           | μV/<br>°C  |

| Saturation Drain<br>Current Ratio <sup>c</sup>                 | I <sub>DSS1</sub><br>I <sub>DSS2</sub>                | V <sub>DS</sub> = 15 V, V <sub>GS</sub> = 0 V                              | 0.98      | 0.95   | 1            | 0.95   | 1            | 0.95   | 1            |            |

| Transconductance Ratio                                         | 9 <sub>fs1</sub><br>9 <sub>fs2</sub>                  | $V_{DS} = 15 \text{ V}, I_D = 2 \text{ mA}$<br>f = 1 kHz                   | 0.98      | 0.95   | 1            | 0.90   | 1            | 0.90   | 1            |            |

| Common Mode<br>Rejection Ratio <sup>c</sup>                    | CMRR                                                  | $V_{DG}$ = 10 to 20 V $I_D$ = 2 mA                                         | 76        |        |              |        |              |        |              | dB         |

### Notes

- Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

- b. Pulse test: PW  $\leq$  300  $\mu$ s duty cycle  $\leq$  3%. c. This parameter not registered with JEDEC.

- d. Not a production test.

u. Not a production test.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

NCBD

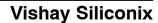

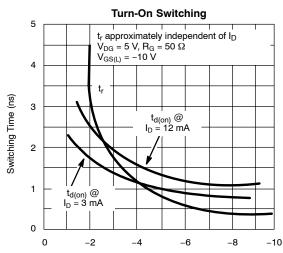

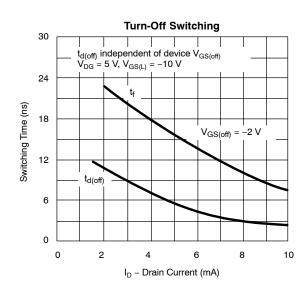

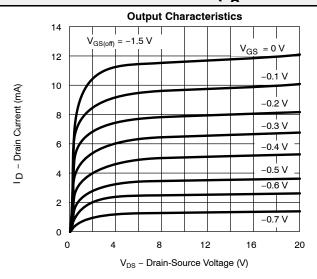

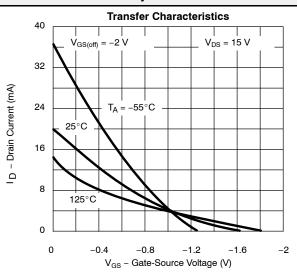

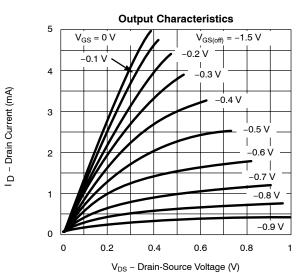

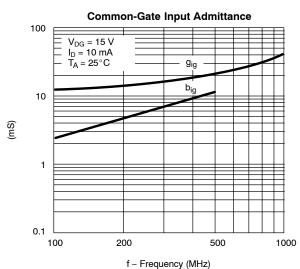

## TYPICAL CHARACTERISTICS (TA = 25°C UNLESS OTHERWISE NOTED)

$V_{GS(off)}$  - Gate-Source Cutoff Voltage (V)

Forward Transconductance and Output Conductance vs. Gate-Source Cutoff Voltage

On-Resistance vs. Drain Current

TA = 25°C

VGS(off) = -2 V

40

1 10 100

I<sub>D</sub> - Drain Current (mA)

V<sub>GS(off)</sub> - Gate-Source Cutoff Voltage (V)

# Vishay Siliconix

## TYPICAL CHARACTERISTICS (T<sub>A</sub> = 25°C UNLESS OTHERWISE NOTED)

## TYPICAL CHARACTERISTICS (T<sub>A</sub> = 25°C UNLESS OTHERWISE NOTED)

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see <a href="http://www.vishay.com/ppg?70254">http://www.vishay.com/ppg?70254</a>.

Vishay

## **Disclaimer**

All product specifications and data are subject to change without notice.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.

Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

Product names and markings noted herein may be trademarks of their respective owners.

Document Number: 91000 www.vishay.com Revision: 18-Jul-08