## 3:1 ActiveEye™ HDMI™ Switch with I2C Control & ARC Transmitter

#### **Features**

- → HDMI 1.4 compliant with fast video switch among each ports

- → I<sup>2</sup>C control 3:1 HDMI active switch Mux with DC coupled or AC coupled Dual mode DisplayPort signals

- Output will maintain its DC coupled, currentsteering

- TMDS compliance input can be AC coupled video or DC coupled

- → 2.5Gbps data rate for TMDS clock up to 250MHz

- → Support up to 36-bits per pixel Deep Color™ modes

- → Programmable equalizer, emphasis and amplitude settings to achieve optimized HDMI signal integrity

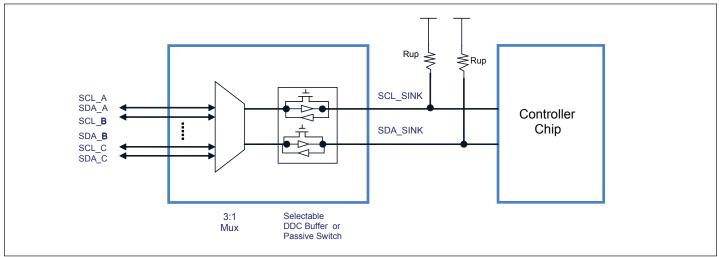

- → Integrated selectable DDC active/ passive switch to connect DDC path

- → Idle clock detection function for output squelch

- → Programmable TMDS termination control

- TMDS input pull-up 50 Ohm termination, pull-down

>120K Ohm resistor when switch is deselected

- Double terminated TMDS output

- → Integrated ESD protection on I/O pins to connector

- □ 8KV contact per IEC61000-4-2, level 3

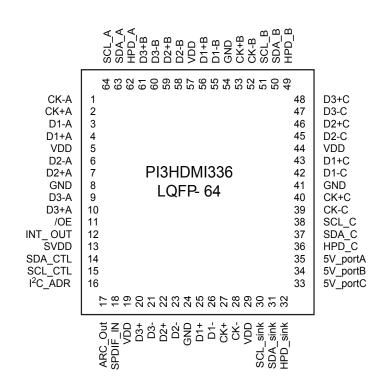

- → Packaging

- 64 pin LQFP (FB), Pb-free and Green

### **Description**

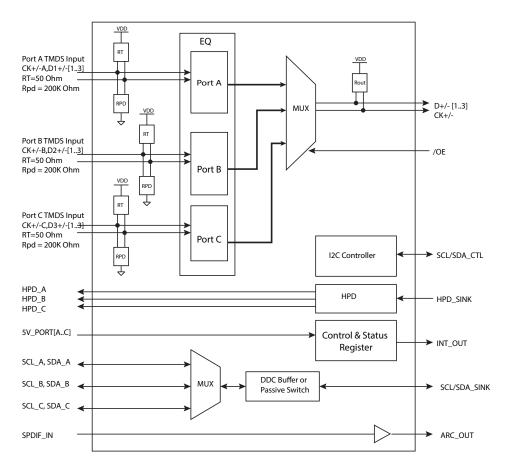

PI3HDMI336 is an I<sup>2</sup>C configurable active switch using Pericom's new ActiveEye<sup>TM</sup> technology to achieve optimized signal integrity for cable or on board transmission.

Through I<sup>2</sup>C interface, system designer can easily program and adjust equalization, emphasis and output swing settings.

With integrated DDC channel Mux, Hot Plug Detection De-Mux, cable plug-unplug detection and HDMI 1.4 ARC transmitter, PI3HDMI336 saves GPIO control pins, provides optimized trace routing, and reduces BOM cost.

Programmable TMDS input termination settings helps designers to avoid the compatibility issue caused by non standard HDMI source.

Programmable output termination setting supports double termination option between PI3HDMI336 and the HDMI receiver chip. This feature minimizes the reflection caused by improper impedance matching and reduces the signal jitter.

PI3HDMI336 is HDMI 1.4 compatible with backward compatibility to the DVI 1.0 standard and can be used for the DP++ application devices.

### **Block Diagram**

12-0237 1 www.pericom.com 07/28/2012

### **Block Diagram**

## **Pin Description**

| Pin #             | Pin Name          | Ю      | Descriptions                                                                                                                     |

|-------------------|-------------------|--------|----------------------------------------------------------------------------------------------------------------------------------|

| 5, 19, 29, 44, 57 | $V_{\mathrm{DD}}$ | Power  | 3.3V power supply. When $V_{\rm DD}$ is off, the TMDS channels and ARC will be powered down.                                     |

| 13                | S <sub>VDD</sub>  | Power  | 3.3V standby power supply. $SV_{DD}$ is for side band signals (HPD, DDC channel and the I <sup>2</sup> C control register unit). |

| 8, 24, 41, 54     | GND               | Ground | Ground connection                                                                                                                |

| 32                | HPD_SINK          | I      | Sink side hot plug detector input; internal pull-down at 120K $\Omega$ .                                                         |

| 62                | HPD_A             | О      | Port A HPD output                                                                                                                |

| 49                | HPD_B             | О      | Port B HPD output                                                                                                                |

| 36                | HPD_C             | О      | Port C HPD output                                                                                                                |

| 2                 | CK+A              |        |                                                                                                                                  |

| 1                 | CK-A              | Ţ      | D (A TIMBS: A D) 50 1 D 1 2001 O                                                                                                 |

| 4                 | D1+A              | I      | Port A TMDS inputs. Rt=50ohm; Rpd=200k $\Omega$ .                                                                                |

| 3                 | D1-A              |        |                                                                                                                                  |

| 7                 | D2+A              |        |                                                                                                                                  |

## Pin Description Cont..

| Pin# | Pin Name | IO  | Descriptions                                      |  |  |  |

|------|----------|-----|---------------------------------------------------|--|--|--|

| 6    | D2-A     |     |                                                   |  |  |  |

| 10   | D3+A     | I   | Port A TMDS inputs. Rt=50ohm; Rpd=200k $\Omega$ . |  |  |  |

| 9    | D3-A     |     |                                                   |  |  |  |

| 53   | CK+B     |     |                                                   |  |  |  |

| 52   | СК-В     |     |                                                   |  |  |  |

| 56   | D1+B     |     |                                                   |  |  |  |

| 55   | D1-B     |     | D ( D TMDC :                                      |  |  |  |

| 59   | D2+B     | I   | Port B TMDS inputs. Rt=50ohm; Rpd=200k $\Omega$ . |  |  |  |

| 58   | D2-B     |     |                                                   |  |  |  |

| 61   | D3+B     |     |                                                   |  |  |  |

| 60   | D3-B     |     |                                                   |  |  |  |

| 40   | CK+C     |     |                                                   |  |  |  |

| 39   | CK-C     |     |                                                   |  |  |  |

| 43   | D1+C     |     | D. (CTMDC) D. To l D. Land O.                     |  |  |  |

| 42   | D1-C     |     |                                                   |  |  |  |

| 46   | D2+C     | I   | Port C TMDS inputs. Rt=50ohm; Rpd=200kΩ.          |  |  |  |

| 45   | D2-C     |     |                                                   |  |  |  |

| 48   | D3+C     |     |                                                   |  |  |  |

| 47   | D3-C     |     |                                                   |  |  |  |

| 27   | CK+      |     |                                                   |  |  |  |

| 28   | CK-      |     |                                                   |  |  |  |

| 25   | D+1      |     |                                                   |  |  |  |

| 26   | D-1      | О О | TMDS outputs Pout-500                             |  |  |  |

| 22   | D+2      |     | TMDS outputs. Rout= $50\Omega$ .                  |  |  |  |

| 23   | D-2      |     |                                                   |  |  |  |

| 20   | D+3      |     |                                                   |  |  |  |

| 21   | D-3      |     |                                                   |  |  |  |

| 64   | SCL_A    | IO  | Port A DDC Clock                                  |  |  |  |

| 51   | SCL_B    | IO  | Port B DDC Clock                                  |  |  |  |

| 38   | SCL_C    | IO  | Port C DDC Clock                                  |  |  |  |

| 63   | SDA_A    | IO  | Port A DDC Data                                   |  |  |  |

| 50   | SDA_B    | IO  | Port B DDC Data                                   |  |  |  |

| 37   | SDA_C    | IO  | Port C DDC Data                                   |  |  |  |

## Pin Description Cont..

| Pin#       | Name                            | IO Type | Descriptions                                                                                                                                                                                        |

|------------|---------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30         | SCL_SINK                        | IO      | Sink side DDC Clock                                                                                                                                                                                 |

| 31         | SDA_SINK                        | IO      | Sink side DDC Data                                                                                                                                                                                  |

| 15         | SCL_CTL                         | IO      | I <sup>2</sup> C Clock, compatible with I <sup>2</sup> C-bus specification, up to 400kb/s.                                                                                                          |

| 14         | SDA_CTL                         | IO      | I <sup>2</sup> C Data, compatible with I <sup>2</sup> C-bus specification, up to 400kb/s.                                                                                                           |

| 12         | INT_OUT                         | О       | Interrupt pin. Logic status output pin of INT Flag. Open drain output, set INT_OUT to high by external pull to $SV_{DD}$ resistor.                                                                  |

| 11         | /OE                             | I       | Output Enable control. Active low. /OE only disables the high speed TMDS channel but not the side band signals and $\rm I^2C$ circuitry supplied by $\rm SV_{DD}$ . Internal pull-down at 100k ohm. |

| 16         | I <sup>2</sup> C_ADR            | I       | $I^2$ C Address LSB; internal pull-down at 100K Ω.                                                                                                                                                  |

| 35, 34, 33 | 5V_PORTA, 5V_PORTB,<br>5V_PORTC | I       | Connector 5V port. Internal pull down resistor at 100k when $V_{\rm DD}$ power on.                                                                                                                  |

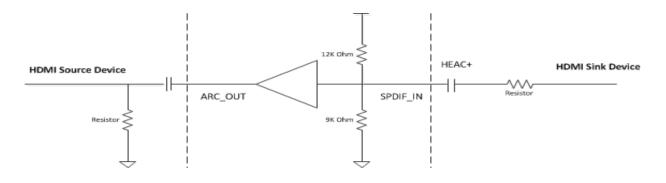

| 18         | SPDIF_IN                        | I       | Single mode ARC signal input. See page 11 in detail.                                                                                                                                                |

| 17         | ARC_OUT                         | О       | Single mode ARC signal output.                                                                                                                                                                      |

## I<sup>2</sup>C Address Byte

|                  | b7(MSB) | b6 | b5 | b4 | b3 | b2 | b1      | b0 (R/W) |

|------------------|---------|----|----|----|----|----|---------|----------|

| Address-<br>Byte | 1       | 0  | 1  | 0  | 1  | 0  | I2C_ADR | 1/0 *    |

## I<sup>2</sup>C Control Register

### Byte 0

| Bit | Descriptions                | Type   | Power Up Condition | Logic Settings                                                                                                  |

|-----|-----------------------------|--------|--------------------|-----------------------------------------------------------------------------------------------------------------|

| 7   | HDMI input port selection   | R/W    | 0                  | b[7:6] = 00 Port A                                                                                              |

|     |                             |        |                    | b[7:6] = 01 Port B                                                                                              |

| 6   | IIDMI imput mont colortion  | D /347 | 0                  | b[7:6] = 10 Port C                                                                                              |

| 0   | 6 HDMI input port selection | R/W    |                    | b[7:6] = 11 no port active                                                                                      |

|     |                             |        |                    | See Port Selection truth table                                                                                  |

|     |                             |        |                    | 0 = Output Disable                                                                                              |

| 5   | TMDS Output Enable          | R/W    | 1                  | Disabled TMDS channel and enter standby mode. Side band signals and I <sup>2</sup> C circuitry are still alive. |

|     |                             |        |                    | 1 = Output Enable                                                                                               |

|     |                             |        |                    | See Output Enable control table                                                                                 |

| Bit | Descriptions               | Type   | Power Up Condition | Logic Settings                                                                                          |

|-----|----------------------------|--------|--------------------|---------------------------------------------------------------------------------------------------------|

|     |                            |        |                    | 0 = HPD_SINK                                                                                            |

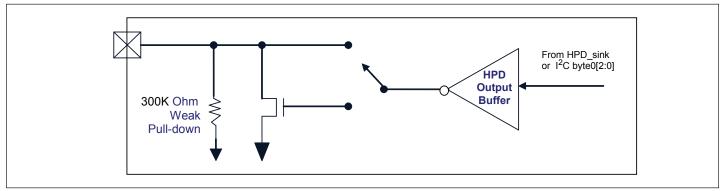

|     | 4 HPD Input Selection      |        |                    | $1 = I^2C$ Register Setting from B0b[0:3]                                                               |

| 4   |                            | R/W    | 0                  | Under I2C register control mode,<br>HPD[A:C] can be individually control by<br>B0b[0:2] for HPD output. |

| 2   | HDD O                      | D /747 | 0                  | 0 = Open Drain                                                                                          |

| 3   | HPD Output Stage selection | R/W    | 0                  | 1 = Output Buffer                                                                                       |

|     |                            |        |                    | I. Byte0 b[4] = 1                                                                                       |

|     |                            |        |                    | When B0b[3] = 0 (open drain mode)                                                                       |

|     |                            |        |                    | B0b[2]=0, set HPD [C] to Low                                                                            |

| 2   | HPD Port C Logic Setting   | R/W    | 0                  | B0b[2]=1, set HPD [C] to High by external pull high resistor                                            |

|     |                            |        |                    | When $B0b[3] = 1$ (output buffer mode)                                                                  |

|     |                            |        |                    | B0b[2]=0, set HPD [C] to High                                                                           |

|     |                            |        |                    | B0b[2]=1, set HPD [C] to Low                                                                            |

|     |                            |        |                    | I. Byte0 b[4] = 1                                                                                       |

|     |                            |        |                    | When B0b[3] = 0 (open drain mode)                                                                       |

|     |                            |        |                    | B0b[1]=0, set HPD [B] to Low                                                                            |

|     | HPD Port B Logic Setting   | R/W    | 0                  | B0b[1]=1, set HPD [B] to High by external pull high resistor                                            |

|     |                            |        |                    | When B0b[3] = 1 (output buffer mode)                                                                    |

|     |                            |        |                    | B0b[1]=0, set HPD [B] to High                                                                           |

|     |                            |        |                    | B0b[1]=1, set HPD [B] to Low                                                                            |

|     |                            |        |                    | I. Byte0 b[4] = 1                                                                                       |

|     |                            |        |                    | When B0b[3] = 0 (open drain mode)                                                                       |

|     |                            |        |                    | B0b[0]=0, set HPD [A] to Low                                                                            |

| 0   | HPD Port A Logic Setting   | R/W    | 0                  | B0b[0]=1, set HPD [A] to High by external pull high resistor                                            |

|     |                            |        |                    | When B0b[3] = 1 (output buffer mode)                                                                    |

|     |                            |        |                    | B0b[0]=0, set HPD [A] to High                                                                           |

|     |                            |        |                    | B0b[0]=1, set HPD [A] to Low                                                                            |

## Byte 1

| Bit | Descriptions                   | Туре | Power Up<br>Condi-<br>tion | Logic Settings                                                                                                                                                                                                                                                |

|-----|--------------------------------|------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Port A RT , Rpd on/off control | R/W  | 1                          | 0 = RT disconnected, Rpd connected<br>1 = RT connected, Rpd disconnected                                                                                                                                                                                      |

| 6   | Port B RT, Rpd on/off control  | R/W  | 1                          | 0 = RT disconnected, Rpd connected<br>1 = RT connected, Rpd disconnected                                                                                                                                                                                      |

| 5   | Port C RT, Rpd on/off control  | R/W  | 1                          | 0 = RT disconnected, Rpd connected<br>1 = RT connected, Rpd disconnected                                                                                                                                                                                      |

| 4   | 5V_PortC connect               | R    | 0                          | 0 = Disconnected<br>1 = Connected<br>INT Flag B1b[1] is set by 5V_PortC edge signal when 5V_PortC<br>changes from 1 to 0, or from 0 to 1.                                                                                                                     |

| 3   | 5V_PortB connect               | R    | 0                          | 0 = Disconnected<br>1 = Connected<br>INT Flag B1b[1] is set by 5V_PortB edge signal when 5V_PortB<br>changes from 1 to 0, or from 0 to 1.                                                                                                                     |

| 2   | 5V_PortA connect               | R    | 0                          | 0 = Disconnected<br>1 = Connected<br>INT Flag B1b[1] is set by 5V_PortA edge signal when<br>5V_PortA changes from 1 to 0, or from 0 to 1                                                                                                                      |

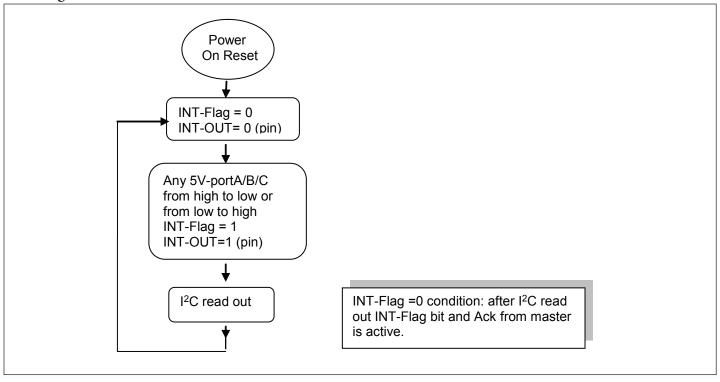

| 1   | INT Flag                       | R    | 0                          | 0 = INT Flag Clear  1 = INT Flag Set  INT Flag will be set from logic Low to High, when any 5V_Port has detected plug or unplug transition action.  INT Flag is cleared to low after I <sup>2</sup> C bus reads the register byte 1.  See INT Flag flowchart. |

| 0   | DDC channel selection          | R/W  | 0                          | 0 = Passive switch 1 = Active switch buffer For power saving operation, passive switch can be selected to further reduce the active power consumption.                                                                                                        |

### Byte 2

| Bit | Descriptions                                 | Type | Power Up<br>Condition | Logic Settings                                                                                                                                 |

|-----|----------------------------------------------|------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TMDS AC swing for CML output setting         | R/W  | 0                     | L[7,c] 00 500mW *Note                                                                                                                          |

| 6   | TMDS AC swing for CML output setting         | R/W  | 0                     | b[7:6] = 00 500mV *Note 1                                                                                                                      |

| 5   | TMDS output pull-up resistor<br>Rout control | R/W  | 0                     | $0$ = Disconnect Rout pull-up to $V_{\rm DD}$ , open drain output $1$ = Connect Rout pull-up to $V_{\rm DD}$ (3.3V), double termination output |

| 4   | Output squelch control                       | R/W  | 1                     | 0 = Output squelch disable<br>1 = Output squelch enable *Note 2, 3                                                                             |

| 3   | TMDS output pre-emphasis setting             | R/W  | 0                     | See OCx truth table                                                                                                                            |

| 2   | TMDS output pre-emphasis setting             | R/W  | 0                     | See OCx truth table                                                                                                                            |

| 1   | TMDS input equalization setting              | R/W  | 1                     | See EQx truth table                                                                                                                            |

| 0   | TMDS input equalization setting              | R/W  | 0                     | See EQx truth table                                                                                                                            |

#### Note:

## **Equalizer (EQx) Truth Table**

TMDS data channel only. TMDS clock channels is 3db fixed

| B2b[1] | B2b[0] | EQ value on TMDS data channels |  |  |  |

|--------|--------|--------------------------------|--|--|--|

| 0      | 0      | 3dB                            |  |  |  |

| 0      | 1      | 6dB                            |  |  |  |

| 1      | 0      | 12dB (default)                 |  |  |  |

| 1      | 1      | 16dB                           |  |  |  |

<sup>1.</sup> B2[7:6]: internal use only

<sup>2.</sup> Output squelch control is used to control TMDS D+/-[0:3], which are set to 'high impedance /or pull-up to  $V^{\rm DD}$  by internal 50 $\Omega$  resistor' when Output squelch is enable if there is no TMDS input signal. When squelch is disable, TMDS D+/-[0:3] will be unknown if there is no TMDS input signal.

<sup>3.</sup> squelch control is using CLK channel signal detection. When TMDS input clock frequency is low or swing is small, it will show no input signal.

### OCx truth table (Swing setting B2b[7:6]=00, 500mv as default)

| TMDS output pre-emphasis setting |        |        | Settin                 | g Value           | Note               |

|----------------------------------|--------|--------|------------------------|-------------------|--------------------|

| B2b[5]                           | B2b[3] | B2b[2] | Single-end Vswing (mV) | Pre-emphasis (dB) | Default Setting    |

| 0                                | 0      | 0      | 500                    | 0                 | Open drain         |

| 0                                | 0      | 1      | 500                    | 1.5               | Open drain         |

| 0                                | 1      | 0      | 500                    | 2.5               | Open drain         |

| 0                                | 1      | 1      | 500                    | 3.5               | Open drain         |

| 1                                | 0      | 0      | 500                    | 0                 | Double termination |

| 1                                | 0      | 1      | 500                    | 1.5               | Double termination |

| 1                                | 1      | 0      | 500                    | 2.5               | Double termination |

| 1                                | 1      | 1      | 500                    | 3.5               | Double termination |

### Port selection truth table

| B0b[7] | B0b[6] | TMDS port                    | DDC port       |

|--------|--------|------------------------------|----------------|

| 0      | 0      | CK+/-A, D1+/-A,D2+/-A,D3+/-A | SCL_A/SDA_A    |

| 0      | 1      | CK+/-B, D1+/-B,D2+/-B,D3+/-B | SCL_B/SDA_B    |

| 1      | 0      | CK+/-C, D1+/-C,D2+/-C,D3+/-C | SCL_C/SDA_C    |

| 1      | 1      | No port active               | No port active |

### Data Channel TMDS input termination resistor RT, Rpd Control

Pull-down resistor Rpd active conditions:

- 1. The Data Channel RT is disconnected controlled by Byte 1 bit[7:5]

- 2. Output enable control /OE is disable(/OE=High), pull down all channels

- 3. No normal operation voltage input (but standby voltage SV<sub>DD</sub> is still On), pull down all channels

### **Output Enable Control**

| /OE  | I2C B0b[5] | Operation      |

|------|------------|----------------|

| Low  | High       | Output Enable  |

| X    | Low        | Output Disable |

| High | X          | Output Disable |

Note: Output disable condition: TMDS channel shut down, output high impedance.

**INT-Flag flowchart**

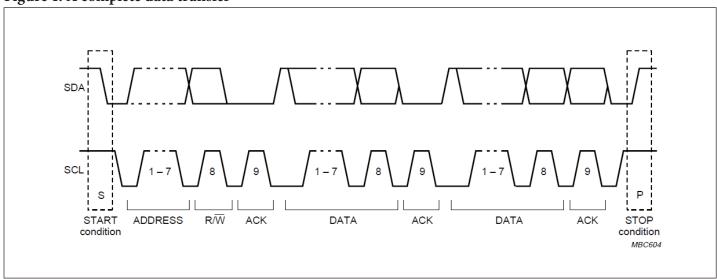

#### I<sup>2</sup>C Bus transactions

Data transfers follow the format shown in Fig.1. After the START condition (S), a slave address is sent. This address is 7 bits long followed by an eighth bit which is a data direction bit (R/W) - a 'zero' indicates a transmission (WRITE), a 'one' indicates a request for data (READ). A data transfer is always terminated by a STOP condition (P) generated by the master. However, if a master still wishes to communicate on the bus, it can generate a repeated START condition (Sr) and address another slave without first generating a STOP condition. Various combinations of read/write formats are then possible within such a transfer.

Figure 1: A complete data transfer

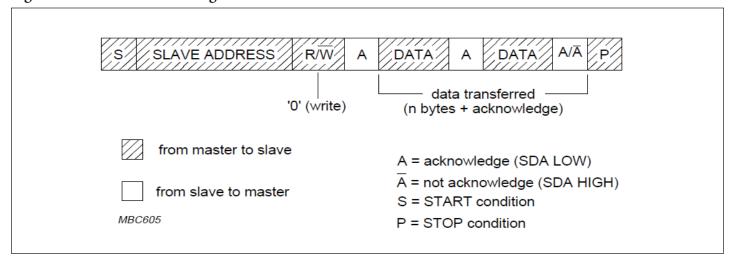

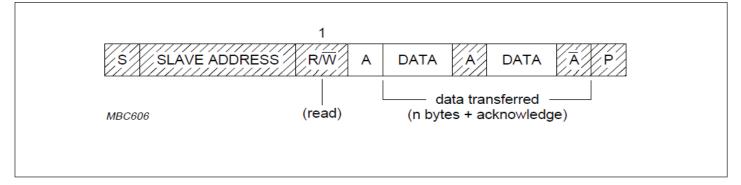

Data is transmitted to the PI3HDMI336 registers using the Write mode as shown in Figure 2. Data is read from the PI3HDMI336 registers using the Read mode as shown in Figure 3

Figure 2: Write to Control Register

Figure 3: Read from Control Register

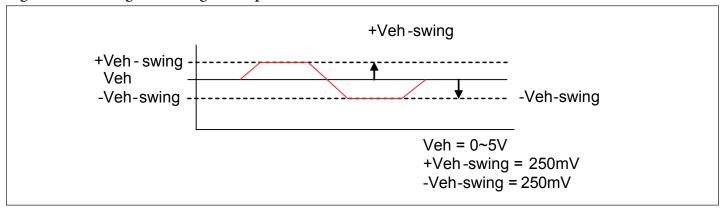

#### Audio Return channel

There are two ARC input modes. They're 'Common mode input' and 'single mode input' but HDMI336 supports 'single mode input' only.

Figure 1: ARC single mode input and output

Figure 2: ARC single mode signal output waveform

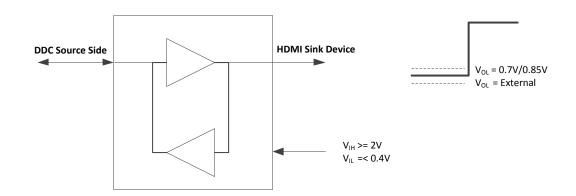

## **DDC Channel Application Diagram**

I2C block uses "low  $V_{_{\rm IL}}$  <= 0.4V and 0.7V <= 0.85V" to define the signal direction, exit from system lock

### HPD[A:C] Output Diagram

#### Note:

- 1. HPD output block support by  $\mathrm{SV}_{\scriptscriptstyle \mathrm{DD}}$  power.

- 2. During normal or standby mode, the HPD block is active. HPD signal output is programmed by the control register.

- 3. Open drain buffer is recommended with a 1Kohm pull-up resistor to 5V. If HPD output buffer is selected, external buffer transistor is required to avoid 5V to 3.3V leakage.

### HPD[A:C] truth table:

### B0b[4]=0, HPD\_Sink input; B0b[3]=0, HPDx open drain output

| Port selection | HPD input select<br>B0b[4]=0 | HPD output select<br>B0b[3]=0 | HPDA     | НРДВ     | НРОС     |

|----------------|------------------------------|-------------------------------|----------|----------|----------|

| Port A         | HPD_Sink                     | Open drain                    | HPD_Sink | L        | L        |

| Port B         | HPD_Sink                     | Open drain                    | L        | HPD_sink | L        |

| Port C         | HPD_Sink                     | Open drain                    | L        | L        | HPD_sink |

| No port active | HPD_Sink                     | Open drain                    | L        | L        | L        |

### B0b[4]=0, HPD\_Sink input; B0b[3]=1, HPDx inverter output

| Port selection | HPD input select<br>B0b[4]=0 | HPD output select<br>B0b[3]=1 | HPDA      | HPDB      | НРДС      |

|----------------|------------------------------|-------------------------------|-----------|-----------|-----------|

| Port A         | HPD_Sink                     | Buffer                        | /HPD_Sink | Н         | Н         |

| Port B         | HPD_Sink                     | Buffer                        | Н         | /HPD_sink | Н         |

| Port C         | HPD_Sink                     | Buffer                        | Н         | Н         | /HPD_sink |

| No port active | HPD_Sink                     | Open drain                    | Н         | Н         | Н         |

### B0b[4]=1, I<sup>2</sup>C register input; B0b[3]=0, HPDx open drain output

| Port selection | HPD input select<br>B0b[4]=1 | HPD output select<br>B0b[3]=0 | HPDA   | HPDB   | HPDC   |

|----------------|------------------------------|-------------------------------|--------|--------|--------|

| B0b[3]=0       | HPDA                         | HPDB                          | HPDC   |        |        |

| Port [A:C]     | B0b[2:0]                     | Open drain                    | B0b[0] | B0b[1] | B0b[2] |

| No port active | B0b[2:0]                     | Open drain                    | B0b[0] | B0b[1] | B0b[2] |

### B0b[4]=1, I2C register input; B0b[3]=1, HPDx inverter output

| Port selection | HPD input select<br>B0b[4]=1 | HPD output select<br>B0b[3]=1 | HPDA    | HPDB    | HPDC    |

|----------------|------------------------------|-------------------------------|---------|---------|---------|

| Port [A:C]     | B0b[2:0]                     | Buffer                        | /B0b[0] | /B0b[1] | /B0b[2] |

| No port active | B0b[2:0]                     | Buffer                        | /B0b[0] | /B0b[1] | /B0b[2] |

## **Absolute Maximum Ratings**

| Supply Voltage to Ground Potential  All Inputs and Outputs  Ambient Operating Temperature  Storage Temperature  Junction Temperature | -0.5V to V <sub>DD</sub> +0.5V<br>-20 to +85°C<br>-65 to +150°C |

|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| Junction Temperature Soldering Temperature                                                                                           |                                                                 |

|                                                                                                                                      |                                                                 |

Note: Stresses greater than those listed under MAXI-MUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## **Recommended Operation Conditions**

| Parameter                  |                          | Min. | Тур. | Max. | Unit |

|----------------------------|--------------------------|------|------|------|------|

| Ambient Operating Temper   | ature                    | -20  |      | +85  | °C   |

| Power Supply Voltage (meas | sured in respect to GND) | +3.0 |      | +3.6 | V    |

### **DC** Specification

$V_{_{

m DD}} = 3.3 {

m V} \pm 10\%,$

| Symbol                                                                    | Parameter                                | Conditions                                                               | Min.                 | Typ. | Max.                 | Unit |

|---------------------------------------------------------------------------|------------------------------------------|--------------------------------------------------------------------------|----------------------|------|----------------------|------|

| $V_{\mathrm{DD}}$                                                         | Operating Voltage                        |                                                                          | 3.0                  | 3.3  | 3.6                  | V    |

| т                                                                         | V Completion                             | Output Enable ( open drain 500mv signal-end 0dB pre-emphasis)            |                      | 80   | 92                   | mA   |

| $I_{DD}$                                                                  | V <sub>DD</sub> Supply Current           | Output Enable ( double termination, 500mv signal-end 0dB pre-emphasis)   |                      | 170  | 210                  | mA   |

| $I_{DDQ}$                                                                 | V <sub>DD</sub> Quiescent Supply Current | TMDS Output Disable, ARC_OUT=0                                           |                      | 3    |                      | mA   |

| Istb                                                                      | Standby mode                             | V <sub>DD</sub> =0V, S <sub>VDD</sub> =3.6V, DDC passive switch, HPD_x=0 |                      | 1    |                      | mA   |

| V <sub>IH</sub> _5V_A,<br>V <sub>IH</sub> _5V_B,<br>V <sub>IH</sub> _5V_C | Input High Voltage of 5V ports           |                                                                          | 0.7*SV <sub>DD</sub> |      |                      | V    |

| V <sub>IL</sub> _5V_A,<br>V <sub>IL</sub> _5V_B,<br>V <sub>IL</sub> _5V_C | Input Low Voltage of 5V ports            |                                                                          |                      |      | 0.3*SV <sub>DD</sub> | V    |

## **DC Specification Cont..**

| Symbol                   | Parameter                                                                           | Conditions                                                       | Min.                  | Тур. | Max. | Unit   |

|--------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------|-----------------------|------|------|--------|

| V <sub>OL_HPD</sub>      | Buffer Output Low<br>Voltage                                                        | $I_{OL} = 4 \text{ mA}$                                          |                       |      | 0.4  | V      |

|                          | Open Drain Output<br>Low Voltage                                                    | $I_{OL} = 4 \text{ mA}$                                          | 0                     |      | 0.4  | V      |

| V <sub>OH_HPD</sub>      | Buffer Output High<br>Voltage                                                       | $I_{OH} = 1 \text{ mA}$                                          | SV <sub>DD</sub> -1.1 |      |      | V      |

| т                        | Officely and automat                                                                | V <sub>DD</sub> =0, SV <sub>DD</sub> =0, V <sub>IN</sub> =3.6V   |                       |      | 10   |        |

| I <sub>OFF_HPD</sub>     | Off leakage current                                                                 | $V_{DD}=0, SV_{DD}=0, V_{IN}=5.5V$                               |                       |      | 20   | uA     |

| T                        | Open drain Output                                                                   | S <sub>VDD</sub> =3.6, V <sub>IN</sub> =3.6V                     |                       |      | 25   | uA     |

| I <sub>OZ_HPD</sub>      | leakage current                                                                     | S <sub>VDD</sub> =3.6, V <sub>IN</sub> =5.5V                     |                       |      | 35   |        |

| HPD_sink                 |                                                                                     |                                                                  |                       |      |      |        |

| $I_{IH}$                 | High level digital input current                                                    | $V_{IH} = V_{DD}$                                                | -10                   |      | 40   | μΑ     |

| $I_{IL}$                 | Low level digital input current                                                     | V <sub>IL</sub> = GND                                            | -10                   |      | 10   | μΑ     |

| $V_{\mathrm{IH}}$        | High level digital input voltage                                                    | CV.                                                              | 2.0                   |      |      | V      |

| V <sub>IL</sub>          | Low level digital input voltage                                                     | $SV_{DD}=3.3v$                                                   | 0                     |      | 0.8  | V      |

| Control pin              | n (/OE)                                                                             |                                                                  |                       |      |      |        |

| ${ m I}_{ m IH}$         | High level digital input current                                                    | $V_{IH} = V_{DD}$                                                | -10                   |      | 40   | μΑ     |

| $I_{IL}$                 | Low level digital input current                                                     | V <sub>IL</sub> = GND                                            | -10                   |      | 10   | μΑ     |

| $V_{\mathrm{IH}}$        | High level digital input voltage                                                    |                                                                  | 2.0                   |      |      | V      |

| $V_{IL}$                 | Low level digital input voltage                                                     |                                                                  | 0                     |      | 0.8  | V      |

| INT_OUT                  |                                                                                     |                                                                  | ·                     |      |      | ·      |

| V <sub>OL_INT_OUT</sub>  | Output open drain<br>Low Voltage                                                    | $I_{OL} = 4 \text{ mA}$                                          |                       |      | 0.4  | V      |

| V <sub>OH_INT_OUT</sub>  | High impedance,<br>depended on external<br>pull high resistor and<br>power supplier | External pull-up Rup to $V_{DD}$ from $1.5k\Omega$ to $5k\Omega$ | $V_{\mathrm{DD}}$ -1  |      |      | V      |

| т                        | Officelyage evenent                                                                 | V <sub>DD</sub> =0, SV <sub>DD</sub> =0, V <sub>IN</sub> =3.6V   |                       |      | 10   | - 11 Λ |

| I <sub>OFF_INT_OUT</sub> | Off leakage current                                                                 | V <sub>DD</sub> =0, SV <sub>DD</sub> =0, V <sub>IN</sub> =5.5V   |                       |      | 20   | uA     |

| DDC Channel                       | Block                                                                    |                                                                                            |                      |      |                      |      |

|-----------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|----------------------|------|----------------------|------|

| Symbol                            | Parameter                                                                | Conditions                                                                                 | Min.                 | Typ. | Max.                 | Unit |

| V <sub>IH_DDC</sub> (source)      | Source Side DDC Buffer Input<br>High Voltage                             |                                                                                            | 0.7*SV <sub>DD</sub> |      |                      | V    |

| V <sub>IL_DDC</sub> (source)      | Source Side DDC Buffer Input<br>Low Voltage                              |                                                                                            |                      |      | 0.3*SV <sub>DD</sub> | V    |

| $V_{\rm OL\_DDC(source)}$         | Source Side DDC Buffer Output Low Voltage,                               | External pull-up Rup to $V_{DD}$ from $1.5k\Omega$ to $5k\Omega$                           |                      |      | 0.4                  | V    |

| $V_{OL\_DDC(sink)}$               | Sink Side DDC Buffer Output<br>Low Voltage,                              | External pull-up Rup to $V_{DD}$ from 1.5k $\!\Omega$ to 5k $\!\Omega$                     | 0.7                  |      | 0.85                 | V    |

| $V_{IH\_DDC(sink)}$               | Sink Side DDC Buffer Input<br>High Voltage,                              |                                                                                            | 2.0                  |      |                      | V    |

| $V_{IL\_DDC(sink)}$               | Sink Side DDC Buffer Input<br>Low Voltage,                               |                                                                                            |                      |      | 0.4                  | V    |

| $I_{LK}$                          | Input leakage current                                                    | DDC switch is off                                                                          | -10                  |      | 10                   | uA   |

| $C_{IO}$                          | Input/Output capacitance when passive switch on                          | VI peak-peak = 1V, 100 KHz                                                                 |                      | 10.5 |                      | pF   |

| R <sub>ON</sub>                   | Passive Switch resistance                                                | $IO = 3mA, V_O = 0.4V$                                                                     |                      | 30   | 50                   | Ω    |

| Vpass                             | Switch Output voltage                                                    | V <sub>I</sub> =3.3V, II=100uA<br>SV <sub>DD</sub> =3.3V                                   | 1.5                  | 2.0  | 2.8                  | V    |

| CI(source)                        | Source side DDC capacitance When active switch on or passive switch off. | V <sub>I</sub> peak-peak = 1V, 100 KHz                                                     |                      | 4.0  |                      | pF   |

| CI(sink)                          | Sink side DDC capacitance when active switch on or passive switch off.   | V <sub>I</sub> peak-peak = 1V, 100 KHz                                                     |                      | 6.0  |                      | pF   |

| V <sub>OH_DDC</sub> (source/sink) | DDC Switch Output High<br>Voltage                                        | $$V_{\rm IN}$=3.3V.$$ External pull-up Rup to $V_{\rm DD}$ from $1.5k\Omega$ to $5k\Omega$ | V <sub>DD</sub> - 1  |      |                      | V    |

## AC Characteristics (over recommended operating conditions unless otherwise noted)

| Symbol                | Parameter                                                       | <b>Test Conditions</b>                                | Min. | Typ.(1)  | Max. | Units |

|-----------------------|-----------------------------------------------------------------|-------------------------------------------------------|------|----------|------|-------|

| TMDS Diff             | ferential Pins                                                  |                                                       | ·    | <u>'</u> |      | \     |

| t <sub>pd</sub>       | Propagation delay                                               | $V_{DD} = 3.3V$ , Rout = $50\Omega$                   |      |          | 2000 |       |

| $t_{\rm r}$           | Differential output signal rise time (20% - 80%)                |                                                       |      | 150      |      |       |

| $t_{\mathrm{f}}$      | Differential output signal fall time (20% - 80%)                |                                                       |      | 150      |      | ps    |

| $t_{sk(p)}$           | Pulse skew                                                      |                                                       |      | 10       | 50   |       |

| t <sub>sk(D)</sub>    | Intra-pair differential skew                                    |                                                       |      | 23       | 50   |       |

| t <sub>sk</sub> (o)   | Inter-pair differential skew <sup>(2)</sup>                     |                                                       |      |          | 100  |       |

| t <sub>jit</sub> (pp) | Peak-to-peak output jitter CLK residual jitter                  | Data Input = 1.65 Gbps HDMI                           |      | 15       | 30   | ps    |

| t <sub>jit</sub> (pp) | Peak-to-peak output jitter DATA<br>Residual Jitter              | data pattern<br>CLK Input = 165 MHz clock             |      | 18       | 50   | ps    |

| t <sub>sx</sub>       | Select to switch output                                         |                                                       |      |          | 10   | ns    |

| t <sub>en</sub>       | Enable time                                                     |                                                       |      |          | 600  | ns    |

| t <sub>dis</sub>      | Disable time                                                    |                                                       |      |          | 10   | ns    |

| DDC I/O P             | ins (SCL, SCL_SINK, SDA, SDA                                    | _SINK)                                                |      |          | 1    |       |

|                       | Propagation delay from SCLn                                     | $C_L = 10$ pF, in passive switch                      |      | 1.5      | 2.5  |       |

| $t_{\mathrm{pd}}$     | ,                                                               | $C_L = 10$ pF, in active switch,<br>SVDD=3.3v, Rup=2k |      | 7.5      |      | ns    |

| DDC I/O               | Pins (HPD_SINK, HPD inverter                                    | output) *Note 1                                       |      | ,        | •    |       |

| t <sub>pd</sub> (HPD) | Propagation delay (from HPD_<br>SINK to the active port of HPD) | $C_L = 10 pF$                                         |      | 2        | 6.0  |       |

| t <sub>sx</sub> (HPD) | Switch time (from port select to the latest )                   |                                                       |      | 3        | 6.5  | ns    |

Note:

<sup>1.</sup>  $t_{\rm plh}$  time of HPD open drain output, depends on external pull high resistor and load capacitor.

| TMDS dif            | TMDS differential pins                                                  |                                      |                      |      |                      |       |  |  |  |

|---------------------|-------------------------------------------------------------------------|--------------------------------------|----------------------|------|----------------------|-------|--|--|--|

| Symbol              | Parameter                                                               | <b>Test Conditions</b>               | Min.                 | Typ. | Max.                 | Units |  |  |  |

| V <sub>OH</sub>     | Single-ended high level output voltage                                  |                                      | V <sub>DD</sub> +10  |      | V <sub>DD</sub> -10  | mV    |  |  |  |

| V <sub>OL</sub>     | Single-ended low level output voltage                                   |                                      | V <sub>DD</sub> -600 |      | V <sub>DD</sub> -400 | mV    |  |  |  |

| Vswing              | Single-ended output swing voltage                                       |                                      | 400                  |      | 600                  | mV    |  |  |  |

| V <sub>OD(O)</sub>  | Overshoot of output differential voltage                                | $V_{DD} = 3.3V$ , Rout=50 $\Omega$   |                      |      | 180 1                | mV    |  |  |  |

| V <sub>OD(U)</sub>  | Undershoot of output differential voltage                               |                                      |                      |      | 200 <sup>2</sup>     | mV    |  |  |  |

| V <sub>OC(SS)</sub> | Change in steady-state common- mode output voltage between logic states |                                      |                      |      | 5                    | mV    |  |  |  |

|                     | Short Circuit output current                                            |                                      | -12                  |      | 12                   | mA    |  |  |  |

| I <sub>OS</sub>     | Short Circuit output current at double termination mode                 |                                      | -24                  |      | 24                   | mA    |  |  |  |

| VI(open)            | Single-ended input voltage under high impedance input or open input     | $I_I = 10uA$                         | V <sub>DD</sub> -10  |      | V <sub>DD</sub> +10  | mV    |  |  |  |

| $R_{\mathrm{T}}$    | Input termination resistance                                            | $V_{\rm IN} = 2.9 \rm V$             | 45                   | 50   | 55                   | Ohm   |  |  |  |

| $I_{OZ}$            | Leakage current with Hi-Z I/O                                           | $V_{DD} = 3.6V,$<br>$SV_{DD} = 3.6V$ |                      |      | 10                   | μΑ    |  |  |  |

#### Note:

- 1. Overshoot of output differential voltage  $V_{\text{OD}}(O)$  = (VSWING(MAX) \* 2) \* 15%,

- 2. Undershoot of output differential voltage  $\rm V_{OD}(O)$  = (VSWING(MIN) \* 2) \* 25%

| SPDIF & ARC            | SPDIF & ARC Pins, See ARC single mode waveform |                                                |      |      |      |       |  |  |  |  |  |

|------------------------|------------------------------------------------|------------------------------------------------|------|------|------|-------|--|--|--|--|--|

| Symbol                 | Parameter                                      | <b>Test Conditions</b>                         | Min. | Typ. | Max. | Units |  |  |  |  |  |

| I <sub>IH</sub> _SPDIF | High level input current                       | $V_{DD} = 3.6 \text{V}, V_{IH} = 3.6 \text{V}$ |      | 500  |      | uA    |  |  |  |  |  |

| I <sub>IL</sub> _SPDIF | Low level input current                        | $V_{DD}$ =3.6V, $V_{IL}$ = GND                 |      | 350  |      | uA    |  |  |  |  |  |

| Vel                    | Single mode input/output Vel DC voltage level  |                                                | 0    |      | 5.0  | V     |  |  |  |  |  |

| Vel swing SPDIF        | Single mode input swing                        |                                                | 0.2  |      | 0.6  | V     |  |  |  |  |  |

| Vel swing ARC_<br>OUT  | Single mode ARC output swing                   |                                                | 0.4  | 0.5  | 0.6  | V     |  |  |  |  |  |

| Ro                     | Output resistance of ARC output stage          |                                                |      | 55   |      | Ohm   |  |  |  |  |  |

| $t_r$                  | ARC output rise time (10% to 90%)              | < 0.4UI (f <sub>clock</sub> = 6.144MHz) **     |      |      | 25   | ns    |  |  |  |  |  |

| tf                     | ARC output fall time (10% to 90%)              | < 0.4UI (f <sub>clock</sub> = 6.144MHz) **     |      |      | 25   | ns    |  |  |  |  |  |

| ТЈрр                   | ARC signal peak to peak jitter                 | < 0.05UI (f <sub>clock</sub> = 6.144MHz)       |      |      | 3    | ns    |  |  |  |  |  |

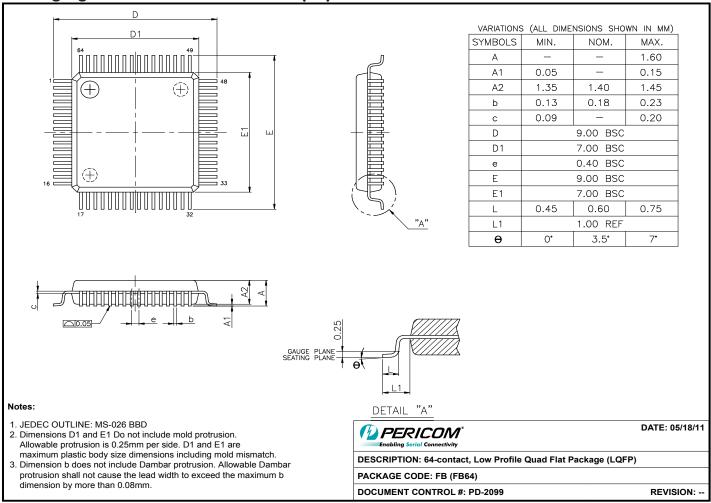

### Packaging Mechanical: 64-Pin LQFP (FB)

11-0064

Pericom Semiconductor Corporation • 1-800-435-2336

### **Related Products**

| Part Number  | Product Description                                                                                    |  |

|--------------|--------------------------------------------------------------------------------------------------------|--|

| PI3HDMI1201  | DisplayPort 1.2 Re-driver with built-in AUX listener                                                   |  |

| PI3VDP1430   | Dual Mode DisplayPort to HDMI Level Shifter and Re-driver                                              |  |

| PI3HDMI511   | 3.4G HDMI1.4 Re-driver for Source-side application, supporting Dual Mode DisplayPort                   |  |

| PI3HDMI611   | 3.4G HDMI1.4 Re-driver for Sink-side application, supporting Dual Mode DisplayPort                     |  |

| PI3VDP3212   | 2-Lane DisplayPort1.2 Compliant Switch                                                                 |  |

| PI3VDP12412  | 4-Lane DisplayPort1.2 Compliant Switch                                                                 |  |

| PI3HDMI412AD | 1:2 Active 3.4Gbps HDMI1.4 compliant Splitter/Re-driver                                                |  |

| PI3HDMI521   | 2:1 3.4Gbps HDMI1.4 Switch/Re-driver with built-in ARC and Fast Switching support for Sink Application |  |

| PI3HDMI621   | 2:1 3.4Gbps HDMI1.4 Switch/Re-driver with built-in ARC and Fast Switching support for Sink Application |  |

| PI3HDMI336   | 3:1 Active 3.4Gbps HDMI Switch/Re-driver with I <sup>2</sup> C control and ARC Transmitter             |  |

### **Reference Information**

| Document | Description                                                                                                         |

|----------|---------------------------------------------------------------------------------------------------------------------|

|          | VESA DisplayPort Standard Version 1 Revision 2, Video Electronics Standards Association, January 5, 2010            |

| VESA     | VESA DisplayPort Dual-Mode Standard Version 1, Video Electronics Standards Association, February 10, 2012           |

|          | VESA DisplayPort Interoperability Guideline Version 1.1a, Video Electronics Standards Association, February 5, 2009 |

| HDMI     | High-Definition Multimedia Interface Specification Version 1.4, HDMI Licensing, LLC, June 5, 2009                   |

# **Ordering Information**

| Ordering Code | Package Code | Package Type                 |

|---------------|--------------|------------------------------|

| PI3HDMI336FBE | FB           | Pb-free & Green, 64-pin LQFP |

<sup>1.</sup> Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

3:1 ActiveEye™ HDMI™ Switch with I²C Control & ARC Transmitter

## **Revision History**

| Date      | Changes                            |

|-----------|------------------------------------|

| 7/28/2012 | Block diagram, Reference Schematic |

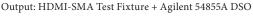

### Appendix: Eye Diagram at 1920x1080p

Input: Quantum Data + HDMI Cable

DUT Setting: Selected Port = Port C; HPD = Open Drain; TMDS = Open Drain/CML, RT connected, 500mV, 0dB Pre-emphasis

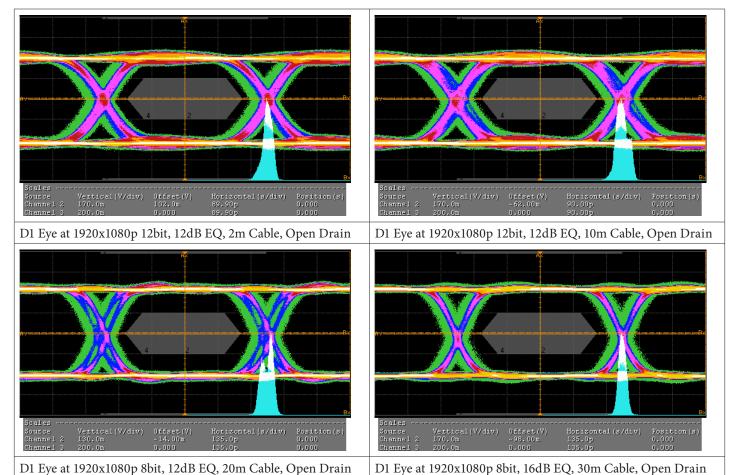

## **Appendix: Reference Schematic**

**Appendix: Evaluation Board Image**