# **LVPECL Clock Buffer with ÷2 Feature**

### **Features**

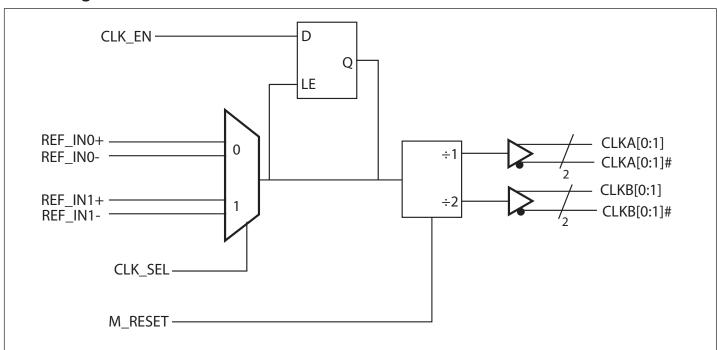

- → 2 pairs of selectable differential inputs

- → 2 divide by 2 differential LVPECL outputs and 2 buffered outputs

- → Maximum operating frequency: 650MHz

- → RMS additive jitter @ 156.25MHz (12kHz 20MHz): 30fs (typical)

- → Output skew: 60ps

- → Part to part skew: 200ps

- → Operating voltage of 2.5V and 3.3V

- → Industrial operating temperature

- → Available in lead-free package

## **Description**

PI6C4911504D2 is a high performance differential buffer with divide by 2 capability. There are also 2 selectable muxed inputs. This device is ideal for systems that need to distribute low jitter clock signals to multiple destinations with a change from the input frequency.

## **Applications**

- → Networking: 10GbE, 25GbE, 40GbE and 100GbE applications

- → Telecom: Basestations and Access Points

## **Block Diagram**

15-0101 1 www.pericom.com PI6C4911504D2 Rev D 07/23/15

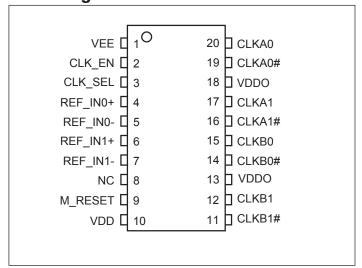

## **Pin Configuration**

## **Pinout Table**

| Pin No. | Pin Name        | I/O Type |           | Description                                                                                                                                |

|---------|-----------------|----------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | V <sub>EE</sub> | Power    |           | Negative supply pin                                                                                                                        |

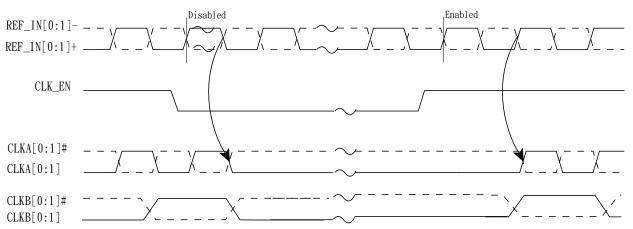

| 2       | CLK_EN          | Input    | Pull up   | Synchronous clock enable. When High, clock outputs follow REF_IN. When low, CLK outputs are forced low, CLK# are forced high               |

| 3       | CLK_SEL         | Input    | Pull-down | Clock Select input. When HIGH, selects REF_IN1. When LOW, selects REF_IN0.                                                                 |

| 4       | REF_IN0+        | Input    | Pull-down | Reference input 0                                                                                                                          |

| 5       | REF_IN0-        | Input    | Pull Up   | Inverted reference input 0                                                                                                                 |

| 6       | REF_IN1+        | Input    | Pull-down | Reference input 1                                                                                                                          |

| 7       | REF_IN1-        | Input    | Pull up   | Inverted reference input 1                                                                                                                 |

| 8       | NC              | -        | -         | No connect                                                                                                                                 |

| 9       | M_RESET         | Input    | Pull-down | Master Reset pin. Active High. When logic High, CLKAn and CLKBn go low and CLKAn# and CLKBn# go high. When logic Low, outputs are enabled. |

| 10      | V <sub>DD</sub> | Power    |           | Core power supply                                                                                                                          |

| 11      | CLKB1#          | Output   |           | Differential output, LVPECL signalling level                                                                                               |

| 12      | CLKB1           | Output   | -         | Differential output, LVPECL signalling level                                                                                               |

| 13, 18  | $V_{ m DDO}$    | Power    |           | Output power supply                                                                                                                        |

| 14      | CLKB0#          | Output   | -         | Differential output, LVPECL signalling level                                                                                               |

| 15      | CLKB0           | Output   |           | Differential output, LVPECL signalling level                                                                                               |

| 16      | CLKA1#          | Output   |           | Differential output, LVPECL signalling level                                                                                               |

| 17      | CLKA1           | Output   |           | Differential output, LVPECL signalling level                                                                                               |

| 19      | CLKA0#          | Output   |           | Differential output, LVPECL signalling level                                                                                               |

| 20      | CLKA0           | Output   |           | Differential output, LVPECL signalling level                                                                                               |

## **Pin Characteristics**

| Symbol                | Parameter               | Min | Тур | Max | Units |

|-----------------------|-------------------------|-----|-----|-----|-------|

| C <sub>IN</sub>       | Input Capacitance       |     | 4   |     | pF    |

| R <sub>PULLUP</sub>   | Input Pullup Resistor   |     | 51  |     | kΩ    |

| R <sub>PULLDOWN</sub> | Input Pulldown Resistor |     | 51  |     | kΩ    |

## **Control Inputs**

|         | Inj    | puts    | Outputs              |                               |                                   |

|---------|--------|---------|----------------------|-------------------------------|-----------------------------------|

| M_RESET | CLK_EN | CLK_SEL | SOURCE               | CLKA0, CLKA1,<br>CLKB0, CLKB1 | CLKA0#, CLKA1#,<br>CLKB0#, CLKB1# |

| 1       | X      | X       | X                    | LOW                           | HIGH                              |

| 0       | 0      | 0       | REF_IN0,<br>REF_IN0# | Disabled, LOW,                | Disabled, HIGH                    |

| 0       | 0      | 1       | REF_IN1,<br>REF_IN1# | Disabled, LOW,                | Disabled, HIGH                    |

| 0       | 1      | 0       | REF_IN0,<br>REF_IN0# | Enabled                       | Enabled                           |

| 0       | 1      | 1       | REF_IN1,<br>REF_IN1# | Enabled                       | Enabled                           |

# **CLK\_EN Timing Diagram**

### **Maximum Ratings** (Over operating free-air temperature range)

| Storage Temperature65°C to+155°C                   |

|----------------------------------------------------|

| Ambient Temperature with Power Applied40°C to+85°C |

| Supply Voltage (relative to VEE)0.5 to +3.7V       |

| ESD Protection (HBM)                               |

|                                                    |

#### Note

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## **DC Electrical Characteristics**

Power Supply DC Characterisitcs,  $(T_A = -40 \, ^{\circ}\text{C} \text{ to } 85 \, ^{\circ}\text{C})$

| Symbol           | Parameter                           | Condition | Min   | Тур | Max   | Units |

|------------------|-------------------------------------|-----------|-------|-----|-------|-------|

| ***              | Cons Summly Walters                 |           | 3.0   | 3.3 | 3.6   | V     |

| V <sub>DD</sub>  | V <sub>DD</sub> Core Supply Voltage |           | 2.375 | 2.5 | 2.625 | V     |

| 3.7              | Output Supply Voltage               |           | 3.0   | 3.3 | 3.6   | V     |

| V <sub>DDO</sub> |                                     |           | 2.375 | 2.5 | 2.625 | v     |

| I <sub>EE</sub>  | Power Supply Current                |           |       |     | 115   | mA    |

| $I_{DD}$         | Power Supply Current                |           |       |     | 100   | mA    |

## LVCMOS/LVTTL DC Characteristics, $(T_A = -40$ °C to 85°C)

| Symbol                       | Parameter          | Condition                                                                                          | Min  | Тур | Max                | Units |  |

|------------------------------|--------------------|----------------------------------------------------------------------------------------------------|------|-----|--------------------|-------|--|

| 37                           | I IIIh W-14        | V <sub>DD</sub> = 3.3 V +/- 10%                                                                    | 2    |     | 3.765              | V     |  |

| $V_{IH}$                     | Input High Voltage | V <sub>DD</sub> = 2.5 V +/- 5%                                                                     | 1.7  |     | $V_{\rm DD} + 0.3$ | V     |  |

| 17                           | Input Low Voltage  | V <sub>DD</sub> = 3.3 V +/- 10%                                                                    | -0.3 |     | 0.8                | V     |  |

| V <sub>IL</sub>              |                    | V <sub>DD</sub> = 2.5 V +/- 5%                                                                     | -0.3 |     | 0.7                | V     |  |

| I <sub>IH</sub> Input High ( | I WILCO            | $\begin{array}{c} \text{CLK\_EN} \\ \text{V}_{\text{DD}} = \text{VIN} = 3.63 \text{V} \end{array}$ |      |     | 30                 | μΑ    |  |

|                              | Input High Current | $M_RESET$ , $IN_SEL$ , $Ref_IN$<br>$V_{DD} = VIN = 3.63V$                                          |      |     | 150                |       |  |

| $I_{1L}$                     | Input Low Current  | $\begin{array}{c} CLK\_EN \\ V_{DD} = 3.63V, V_{IN} = 0V \end{array}$                              | -150 |     |                    | 4     |  |

|                              |                    | $M\_RESET, IN\_SEL, Ref\_IN$ $V_{DD} = 3.63V, V_{IN} = 0V$                                         | -30  |     |                    | μΑ    |  |

**Differential input DC Characteristics**  $(T_A = -40^{\circ}\text{C to } 85^{\circ}\text{C})$

| Symbols                         | Parai                          | neters                                                        | Test Conditions                                         | Min.           | Тур | Max.                   | Units |

|---------------------------------|--------------------------------|---------------------------------------------------------------|---------------------------------------------------------|----------------|-----|------------------------|-------|

| _                               | Input High                     | REF_IN-                                                       | $V_{DD} = V_{IN} = 3.465V$                              |                |     | 5                      | 4     |

| I <sub>IH</sub>                 | Current                        | REF_IN+                                                       | $V_{DD} = V_{IN} = 3.465V$                              |                |     | 150                    | uA    |

| Input Low<br>Current            | REF_IN-                        | $V_{DD} = 3.465 \text{V or}$<br>2.625 V $V_{IN} = 0 \text{V}$ | -150                                                    |                |     | uA                     |       |

|                                 | Current                        | REF_IN+                                                       |                                                         | -5             |     |                        | uA    |

| V                               | Peak-to-Peak Input Voltage (1) |                                                               | $V_{DD} = 3.3V$                                         | 0.15           |     | 1.3                    | V     |

| V <sub>PP</sub> Peak-to-Peak In |                                | iput voitage                                                  | $V_{DD} = 2.5V$                                         | 0.25           |     | 1.3                    | v     |

| $V_{\rm CMR}$                   | Common Mode Input Voltage      |                                                               | $V_{\rm DD} = 3.3  \text{V} \text{ and } 2.5  \text{V}$ | $V_{EE} + 0.5$ |     | V <sub>DD</sub> - 0.85 | V     |

### **Notes:**

- 1. For single ended applications,  $V_{\rm IH}$  =  $V_{\rm DD}$  + 0.3V. 2. Common mode voltage is defined as  $V_{\rm IH}$ .

## **LVPECL Output DC Characterisitcs,** $(T_A = -40 \, ^{\circ}\text{C} \text{ to } 85 \, ^{\circ}\text{C})$

| Symbol          | Parameter                                          | Condition             | Min | Тур | Max | Units |  |

|-----------------|----------------------------------------------------|-----------------------|-----|-----|-----|-------|--|

| 17              | V <sub>OH</sub> Output High Voltage <sup>(1)</sup> | $V_{\rm DDO} = 3.3 V$ | 1.9 |     | 2.4 | 3.7   |  |

| VOH             |                                                    | $V_{\rm DDO} = 2.5 V$ | 1.5 |     | 1.7 | V     |  |

| 17              | V <sub>OL</sub> Output Low Voltage <sup>(1)</sup>  | $V_{\rm DDO} = 3.3 V$ | 1.3 |     | 1.8 | 17    |  |

| V <sub>OL</sub> |                                                    | $V_{\rm DDO} = 2.5 V$ | 0.8 |     | 1.1 | V     |  |

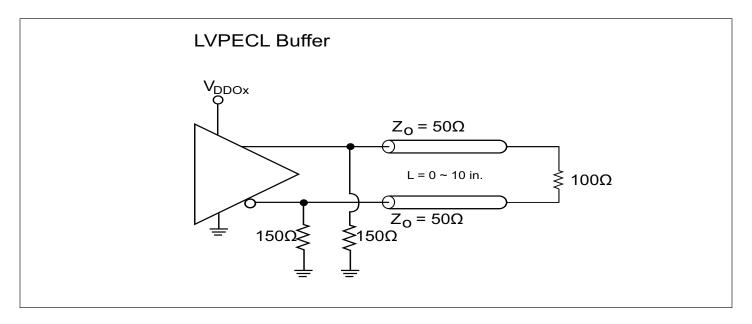

Note: 1. LVPECL Termination: Source 150ohm to GND and 100ohm across CLK and CLK#.

## AC Electrical Characteristics, $(T_A = -40 \, ^{\circ}\text{C} \text{ to } 85 \, ^{\circ}\text{C})$

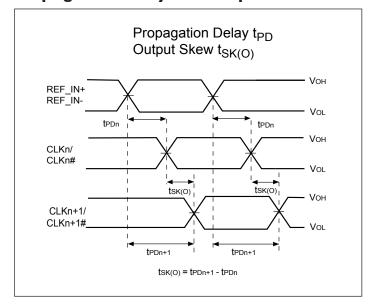

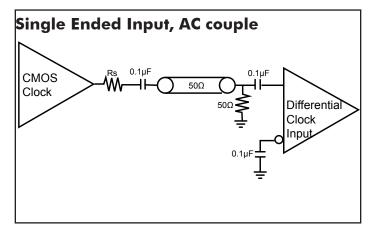

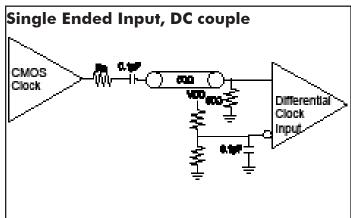

Under the test configurations shown in figures

| Symbol                                    | Parameter                 | Condition                                                            | Min. | Тур. | Max  | Units |  |

|-------------------------------------------|---------------------------|----------------------------------------------------------------------|------|------|------|-------|--|

| $f_{ m OUT}$                              | Output Frequency          |                                                                      |      |      | 650  | MHz   |  |

|                                           | Outroot Diss/Fall Time    | 20% to 80%, 3.3V operation, ≤ 312.5MHz                               | 200  |      | 700  | ps    |  |

| $t_{ m R}$ / $t_{ m F}$                   | Output Rise/Fall Time     | 20% to 80%, 2.5V operation, ≤ 312.5MHz                               | 160  |      | 700  | ps    |  |

| t <sub>SK(O)</sub>                        | Output Skew               | Outputs at the same loading, same bank @ 156.25MHz                   |      |      | 65   | ps    |  |

| $t_{	ext{PD}}$                            | Propagation Delay         | From differential input to the differential output cross point, CLKA | 0.8  |      | 2.0  | ns    |  |

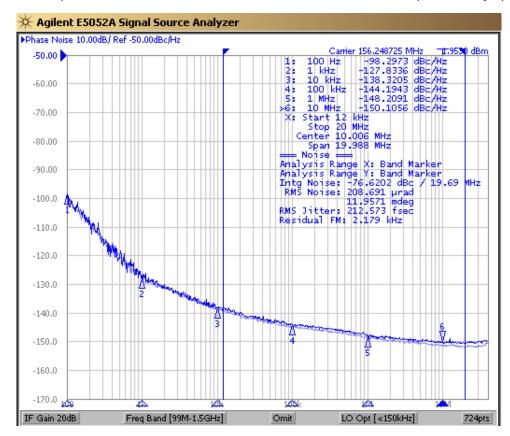

| ,                                         | Additive Phase Jitter,    | 156.25MHz, (12kHz - 20MHz)                                           |      | 30   |      | fs    |  |

| $t_{\rm jit(AØ)}$ (Random) <sup>(1)</sup> | 312.5MHz, (12kHz - 20MHz) |                                                                      | 30   |      | fs   |       |  |

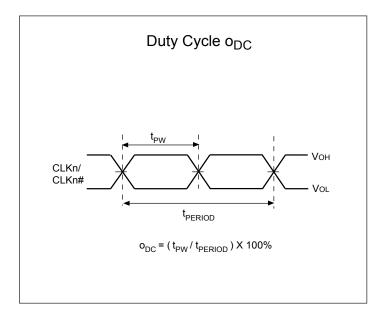

| $o_{_{ m DC}}$                            | Output Duty Cycle         | Measured at 156.25MHz                                                | 48   | 50   | 52   | %     |  |

| $V_{ m pp}$                               | Output Swing              | LVPECL outputs, Single-ended, 3.3V operation                         | 0.55 |      | 1.1  | V     |  |

|                                           |                           | LVPECL outputs, Single-ended, 2.5V operation                         | 0.5  |      | 0.75 |       |  |

### Note:

<sup>1.</sup> Please refer to the Phase Noise Plots.

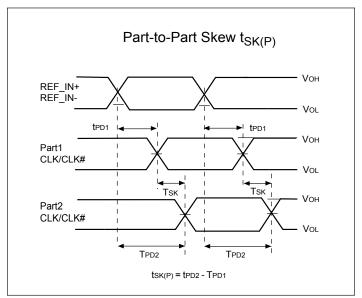

# **Propagation Delay and Output Skew**

### **Part to Part Skew**

# **Output Duty Cycle**

### **Phase Noise Plots**

$f_{\rm OUT} = 156.25 {\rm MHz}$

Output phase noise (Dark Blue) vs Input Phase noise (light blue)

Additive jitter is calculated at 156.25MHz~23fs RMS (12kHz to 20MHz). Additive jitter =  $\sqrt{\text{(Output jitter}^2 - Input jitter}^2)}$

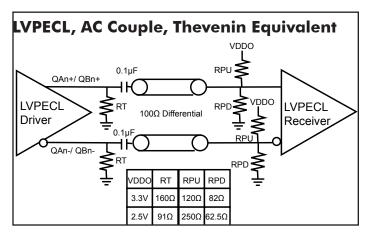

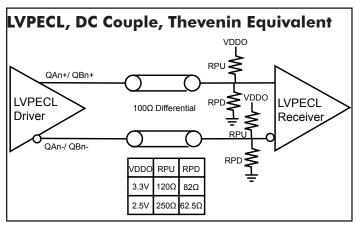

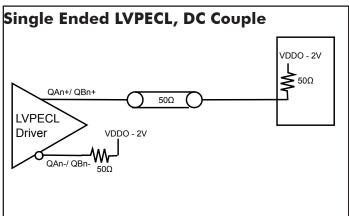

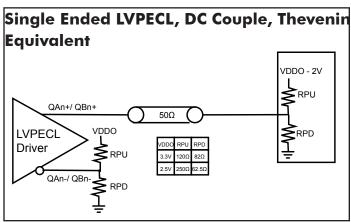

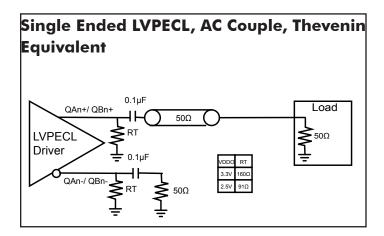

## **LVPECL Test Circuit**

## **Application Information**

### **Power Supply Filtering Techniques**

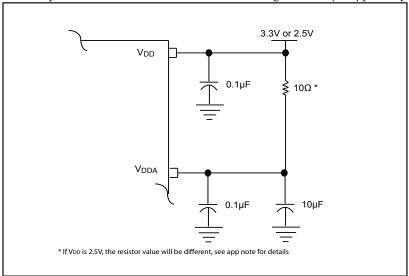

As in any high speed analog circuitry, the power supply pins are vulnerable to random noise. To achieve optimum jitter performance, power supply isolation is required. The PI6C4911504D2 provides separate power supplies to isolate any high switching noise from the outputs to the internal PLL.  $V_{DD}$ ,  $V_{DDA}$  and  $V_{DDO}$  should be individually connected to the power supply plane through vias, and  $0.1\mu F$  bypass capacitors should be used for each pin. Figure below illustrates this for a generic  $V_{DD}$  pin and also shows that  $V_{DDA}$  requires that an additional  $10\Omega$  resistor along with a  $10\mu F$  bypass capacitor be connected to the  $V_{DDA}$  pin.

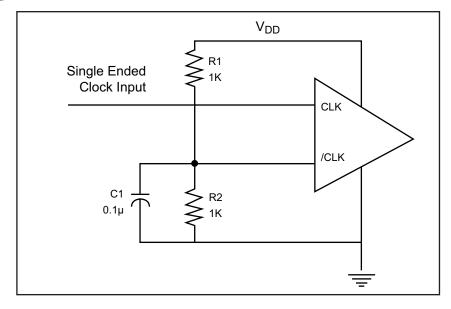

### Wiring the differential input to accept single ended levels

Figure 1 shows how the differential input can be wired to accept single ended levels. The reference voltage  $V\_REF = V_{DD}/2$  is generated by the bias resistors R1, R2 and C1. This bias circuit should be located as close as possible to the input pin. The ratio of R1 and R2 might need to be adjusted to postion the  $V\_REF$  in the center of the input voltage swing. For example, if the input clock swing is only 2.5V and  $V_{DD} = 3.3V$ ,  $V\_REF$  should be 1.25V and R1/R2 = 0.609.

Figure 1. Single-ended input to Differential input device

### Recommendations for Unused Input and Output Pins

### **Inputs:**

CRef\_IN Input:

For applications not requiring the use of the clock, it can be left floating. A  $1k\Omega$  resistor tied from the Ref\_IN to ground can provide additional protection.

LVCMOS Control Pins:

All control pins have internal pulldowns; A  $1k\Omega$  resistor tied from each control pin to ground can provide additional protection.

### **Outputs:**

LVPECL Outputs:

All unused LVPECL outputs can be left floating. We recommend that there is no trace attached. Both sides of the differential output pair should either be left floating or terminated.

## **Thermal Information**

| Symbol              | Description                            | Condition |           |

|---------------------|----------------------------------------|-----------|-----------|

| $\Theta_{_{ m JA}}$ | Junction-to-ambient thermal resistance | Still air | 84.0 °C/W |

| $\Theta_{ m JC}$    | Junction-to-case thermal resistance    |           | 17.0 °C/W |

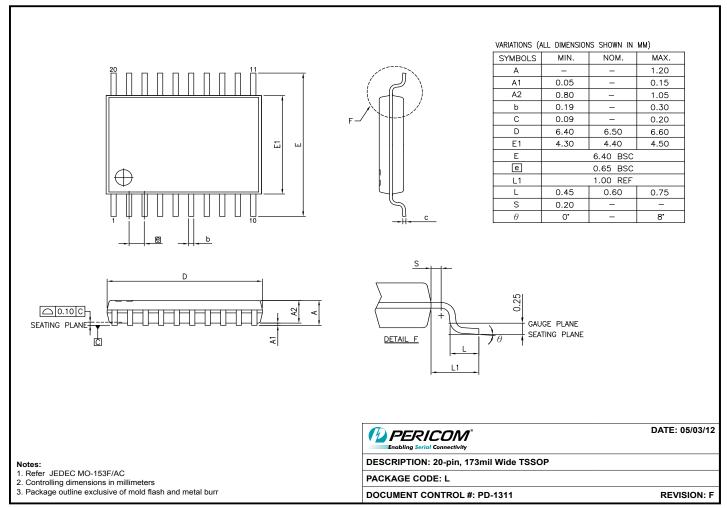

## Packaging Mechanical: 20-Contact TSSOP (L)

12-0373

# **Ordering Information**

| Ordering Code     | Packaging Type | Package Description                        | Operating Temperature |

|-------------------|----------------|--------------------------------------------|-----------------------|

| PI6C4911504D2LIE  | L              | Pb-free & Green, 20-pin TSSOP              | Industrial            |

| PI6C4911504D2LIEX | L              | Pb-free & Green, 20-pin TSSOP, Tape & reel | Industrial            |

#### Notes:

- Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

- "E" denotes Pb-free and Green

- Adding an "X" at the end of the ordering code denotes tape and reel packaging

Pericom Semiconductor Corporation • 1-800-435-2336 • www.pericom.com