#### 2-bit Bidirectional Low Voltage Translator

## **Features**

- → 2-bit bidirectional translator

- → Less than 1.5 ns maximum propagation delay to accommodate Standard mode and Fast mode I2C-bus devices and multiple masters

- → Allows voltage level translation between 0.8V, 1.2 V, 1.5 V, 1.8 V, 2.5 V, 3.3 V and 5 V buses, which allows direct interface with GTL, GTL+, LVTTL/TTL and 5 V CMOS levels

- ➔ Provides bidirectional voltage translation with no direction pin

- → Low 3.5 ohm ON-state connection between input and output ports provides less signal distortion

- → Supports hot insertion

- → 5 V tolerant inputs

- → Flow through pin out for ease of printed-circuit board trace routing

- → ESD protection exceeds 4KV HBM per JESD22-A114

- → Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- → Halogen and Antimony Free. "Green" Device (Note 3)

- → Package: UQFN1.6\*1.6-8L, MSOP-8L, SOIC-8L

## Description

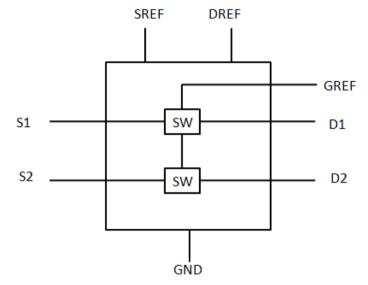

The Gunning Transceiver Logic - Transceiver Voltage Clamps (GTL-TVC) provide high-speed voltage translation with low ON-state resistance and minimal propagation delay. The GTL2002 provides 2 NMOS pass transistors (Sn and Dn) with a common gate (GREF) and a reference transistor (SREF and DREF). The device allows bidirectional voltage translations between 0.8 V and 5.0 V without use of a direction pin.

When the Sn or Dn port is LOW the clamp is in the ON-state and a low resistance connection exists between the Sn and Dn ports. Assuming the higher voltage is on the Dn port, when the Dn port is HIGH, the voltage on the Sn port is limited to the voltage set by the reference transistor (SREF). When the Sn port is HIGH, the Dn port is pulled to VCC by the pull-up resistors. This functionality allows a seamless translation between higher and lower voltages selected by the user, without the need for directional control.

All transistors have the same electrical characteristics and there is minimal deviation from one output to another in voltage or propagation delay. This is a benefit over discrete transistor voltage translation solutions, since the fabrication of the transistors is symmetrical. Because all transistors in the device are identical, SREF and DREF can be located on any of the other two matched Sn/Dn transistors, allowing for easier board layout. The translator's transistors provide excellent ESD protection to lower voltage devices and at the same time protect less ESD-resistant devices.

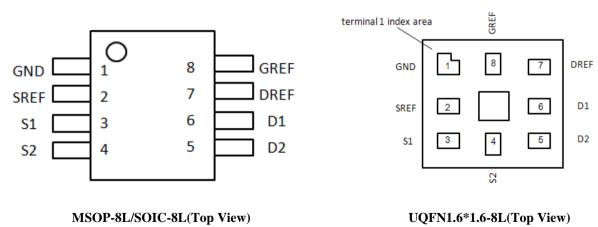

# **Pin Configuration**

Notes:

1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

2. See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free. 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

#### PI4GTL2002

# **Pin Description**

| Pin No | Name | Description                                                                |  |  |  |

|--------|------|----------------------------------------------------------------------------|--|--|--|

| 1      | GND  | ground (0 V)                                                               |  |  |  |

| 2      | SREF | voltage side reference supply voltage for S1 and D1                        |  |  |  |

| 3      | S1   | l clock, low-voltage side; connect to SREF through a pull-up resistor      |  |  |  |

| 4      | S2   | al data, low-voltage side; connect to SREF through a pull-up resistor      |  |  |  |

| 5      | D2   | serial data, high-voltage side; connect to DREF through a pull-up resistor |  |  |  |

| 6      | D1   | al clock, high-voltage side; connect to DREF through a pull-up resistor    |  |  |  |

| 7      | DREF | h-voltage side reference supply voltage for S2 and D2                      |  |  |  |

| 8      | GREF | switch enable input; connect to DREF and pull-up through a high resistor   |  |  |  |

# **Block Diagram**

Figure.1 Block Diagram

Function selection, HIGH to LOW translation

Assuming Dn is at the higher voltage level.

H = HIGH voltage level; L = LOW voltage level; X = Don't care.

| GREF | DREF | SREF   | Input Dn | Output Sn | Transistor |

|------|------|--------|----------|-----------|------------|

| Н    | Н    | 0V     | Х        | Х         | off        |

| Н    | Н    | VTT    | Н        | VTT       | on         |

| Н    | Н    | VTT    | L        | L         | on         |

| L    | L    | 0V-VTT | Х        | Х         | off        |

[1] GREF should be at least 1.5 V higher than SREF for best translator operation.

[2] Sn is not pulled up or pulled down.

[3] Sn follows the Dn input LOW.

[4] VTT is equal to the SREF voltage.

Function selection, LOW to HIGH translation

Assuming Dn is at the higher voltage level.

H = HIGH voltage level; L = LOW voltage level; X = Don't care.

| GREF | DREF | SREF   | Input Sn | Output Dn | Transistor |

|------|------|--------|----------|-----------|------------|

| Н    | Н    | 0V     | Х        | Х         | off        |

| Н    | Н    | VTT    | VTT      | Н         | nearly off |

| Н    | Н    | VTT    | L        | L         | on         |

| L    | L    | 0V-VTT | Х        | Х         | off        |

[1] GREF should be at least 1.5 V higher than SREF for best translator operation.

- [2] Sn is not pulled up or pulled down.

- [3] Sn follows the Dn input LOW.

- [4] VTT is equal to the SREF voltage.

## **Maximum Ratings**

| Storage Temperature              | $-65^{\circ}C$ to $+150^{\circ}C$ |

|----------------------------------|-----------------------------------|

| Reference Voltage <sup>(2)</sup> | -0.5V to +6.0V                    |

| Reference bias voltage           | -0.5V to+6.0V                     |

| DC Input Voltage                 | -0.5V to +6.0V                    |

| Control Input Votage(EN)         |                                   |

| channel current (DC)             | 128mA                             |

| Input clamping Current           | 50mA                              |

| ESD: HBM Mode                    |                                   |

|                                  |                                   |

#### Note:

1. Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

2. The input and input/output negative voltage ratings may be exceeded if the input and input/output clamp current ratings are observed.

## **Recommended Operation Conditions**

VCC = 2.7 V to 5.5 V;  $\overline{\text{GND}}$  = 0 V;  $T_A$  = -40 °C to +85 °C; unless otherwise specified

| Symbol              | Parameter                      | Test Conditions | Min. | Тур. | Max. | Unit |

|---------------------|--------------------------------|-----------------|------|------|------|------|

| V <sub>I/O</sub>    | Voltage on an input/output pin | S1, D1, S2, D2  | 0    | -    | 5    | V    |

| SREF                | Reference voltage (1)          | SREF            | 0    | -    | 5    | V    |

| DREF                | Reference bias voltage (2)     | DREF            | 0    | -    | 5    | V    |

| V <sub>GREF</sub>   | Input voltage on pin GREF      | -               | 0    | -    | 5    | V    |

| I <sub>(pass)</sub> | Pass switch current            | -               | -    | -    | 64   | mA   |

| T <sub>A</sub>      | Ambient temperature            | -               | -40  | -    | 85   | °C   |

## **DC Electrical Characteristics**

$_{\star} = -40 \ ^{\circ}C$  to  $+85 \ ^{\circ}C$ : unless otherwise specified т

|                      | -85 °C; unless otherwise specified              | Test Condition                    | · ~(1)                            | Min | <b>T</b> (2)               | Man  | T Int 14 |

|----------------------|-------------------------------------------------|-----------------------------------|-----------------------------------|-----|----------------------------|------|----------|

| Parameter            | Description                                     | Test Condition                    | 18                                | Min | <b>Typ.</b> <sup>(2)</sup> | Max  | Unit     |

| Input and out        | tput DB and SB                                  |                                   |                                   |     |                            |      |          |

| V <sub>IK</sub>      | input clamping voltage                          | $I_I = -18 \text{mA}; V_G$        | $_{\rm REF} = 0  {\rm V}$         | -   | -                          | -1.2 | V        |

| I <sub>IH</sub>      | HIGH-level input current                        | $V_{I} = 5 V; V_{GREI}$           | $_{\rm F} = 0  {\rm V}$           | -   | -                          | 5    | μA       |

| C <sub>GREF</sub>    | input capacitance on pin GREF                   | $V_I = 3 V \text{ or } 0 V$       | r                                 | -   | 11                         | -    | pF       |

| C <sub>io(off)</sub> | off-state input/output capacitance (Sn, Dn)     | $V_0 = 3 V \text{ or } 0 V$       | V; $V_{\text{GREF}} = 0$ V        | -   | 4                          | -    | pF       |

| C <sub>io(on)</sub>  | on-state input/output capacitance (Sn, Dn)      | $V_0 = 3 V \text{ or } 0 V$       | V; $V_{GREF} = 3 V$               | -   | 10.5                       | -    | pF       |

|                      |                                                 |                                   | $V_{GREF} = 4.5 V$                | -   | 3.5                        | 5.5  | Ω        |

|                      |                                                 | $V_I = 0V;$                       | $V_{GREF} = 3 V$                  | -   | 4.7                        | 7.0  | Ω        |

|                      |                                                 | $I_0 = 64 \text{mA}$              | $V_{GREF} = 2.3 V$                | -   | 6.3                        | 9.5  | Ω        |

| Ron                  | ON-state resistance <sup><math>(2)</math></sup> |                                   | $V_{GREF} = 1.5 V$                | -   | 60                         | 140  | Ω        |

|                      | (Sn, Dn)                                        | $V_{I} = 2.4V; I_{O}$             | $V_{GREF} = 4.5 V$                | 1   | 6                          | 15   | Ω        |

|                      |                                                 | = 15mA                            | $V_{\text{GREF}} = 3 \text{ V}$   | 20  | 60                         | 140  | Ω        |

|                      |                                                 | $V_{I} = 1.7V;$<br>$I_{O} = 15mA$ | $V_{\text{GREF}} = 2.3 \text{ V}$ | 20  | 60                         | 140  | Ω        |

Notes:

1) All typical values are at  $T_A = 25$  °C. 2) Measured by the voltage drop between the S1 and S2, or D1 and D2 terminals at the indicated current through the switch. ON-state resistance is determined by the lowest voltage of the two terminals.

### **Dynamic Characteristics**

$T_A = -40$  °C to +85 °C; unless otherwise specified. Values guaranteed by design.

| Symbol                  | Donomotor                                                                   | Conditions -                                                                                                     | C <sub>L</sub> = | 50 pF | $C_L = 30 \text{ pF}$ |     | $C_L = 15 \text{ pF}$ |     | Unit |

|-------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------------------|-------|-----------------------|-----|-----------------------|-----|------|

| Symbol                  | Parameter                                                                   | Conditions                                                                                                       | Min              | Max   | Min                   | Max | Min                   | Max | Umt  |

| $V_{\text{GREF}} = 3.3$ | $3 V; V_{\rm H} = 3.3 V; V_{\rm L} =$                                       | $0 \text{ V}; \text{ V}_{\text{M}} = 1.15 \text{ V}$                                                             |                  | •     |                       |     |                       |     |      |

| t <sub>PLH</sub>        | LOW-to-HIGH<br>propagation delay                                            | from (input) S2 or D2<br>to (output) S1 or D1                                                                    | 0                | 0.8   | 0                     | 0.6 | 0                     | 0.3 | ns   |

| t <sub>PHL</sub>        | HIGH-to-LOW<br>propagation delay                                            | from (input) S2 or D2<br>to (output) S1 or D1                                                                    | 0                | 1.2   | 0                     | 1   | 0                     | 0.5 | ns   |

| $V_{\text{GREF}} = 2.5$ | $5 \text{ V}; \text{ V}_{\text{H}} = 2.5 \text{ V}; \text{ V}_{\text{L}} =$ | $0 \text{ V}; \text{ V}_{\text{M}} = 0.75 \text{ V}$                                                             |                  |       |                       |     |                       |     |      |

| t <sub>PLH</sub>        | LOW-to-HIGH<br>propagation delay                                            | from (input) S2 or D2<br>to (output) S1 or D1                                                                    | 0                | 1     | 0                     | 0.7 | 0                     | 0.4 | ns   |

| t <sub>PHL</sub>        | HIGH-to-LOW<br>propagation delay                                            | from (input) S2 or D2<br>to (output) S1 or D1                                                                    | 0                | 1.3   | 0                     | 1   | 0                     | 0.6 | ns   |

| $V_{GREF} = 3.3$        | $3 \text{ V}; \text{ V}_{\text{H}} = 2.3 \text{ V}; \text{ V}_{\text{L}} =$ | $0 \text{ V}; \text{ V}_{\text{T}} = 3.3 \text{ V}; \text{ V}_{\text{M}} = 1.15 \text{ V}; \text{ R}_{\text{L}}$ | = 300 Ω          |       |                       |     |                       |     |      |

| t <sub>PLH</sub>        | LOW-to-HIGH<br>propagation delay                                            | ffrom (input) S1 orD1<br>to (output) S2 or D2                                                                    | 0                | 0.9   | 0                     | 0.6 | 0                     | 0.4 | ns   |

| t <sub>PHL</sub>        | HIGH-to-LOW propagation delay                                               | from (input) S1 or D1<br>to (output) S2 or D2                                                                    | 0                | 1.4   | 0                     | 1.1 | 0                     | 0.7 | ns   |

| $V_{\text{GREF}} = 2.5$ | $5 \text{ V}; \text{ V}_{\text{H}} = 1.5 \text{ V}; \text{ V}_{\text{L}} =$ | 0 V; $V_T = 2.5$ V; $V_M = 0.75$ V; $R_L$                                                                        | $= 300 \Omega$   |       |                       |     |                       |     |      |

| t <sub>PLH</sub>        | LOW-to-HIGH propagation delay                                               | from (input) S1 orD1<br>to (output) S2 or D2                                                                     | 0                | 1     | 0                     | 0.6 | 0                     | 0.4 | ns   |

| t <sub>PHL</sub>        | HIGH-to-LOW<br>propagation delay                                            | from (input) S1 or D1<br>to (output) S2 or D2                                                                    | 0                | 1.3   | 0                     | 1.3 | 0                     | 0.8 | ns   |

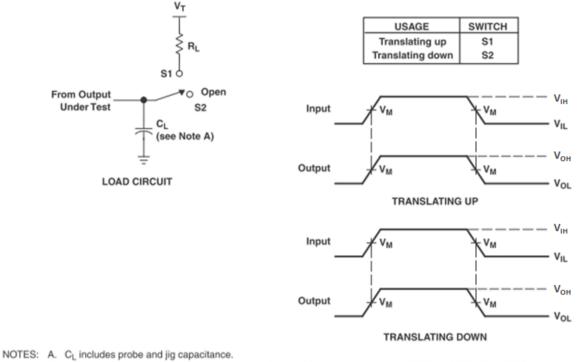

#### PARAMETER MEASUREMENT INFORMATION

B. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz, Z<sub>O</sub> = 50 Ω, t<sub>t</sub>  $\leq$  2 ns, t<sub>t</sub>  $\leq$  2 ns.

C. The outputs are measured one at a time, with one transition per measurement.

Figure.2 Load Circuit for Outputs

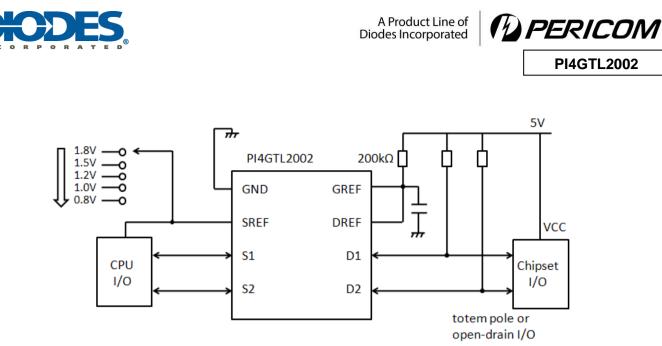

# **Application Information**

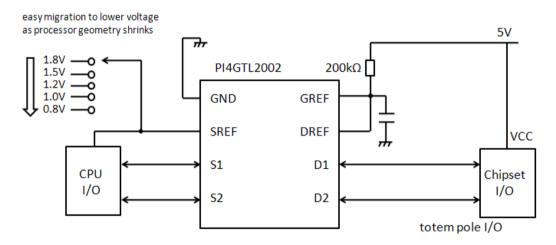

For the bidirectional clamping configuration, higher voltage to lower voltage or lower voltage to higher voltage, the GREF input must be connected to DREF and both pins pulled to HIGH side VCC through a pull-up resistor (typically 200 k $\Omega$ ). A filter capacitor on DREF is recommended. The processor output can be totem pole or open-drain (pull-up resistors may be required) and the chip set output can be totem pole or open-drain (pull-up resistors are required to pull the Dn outputs to VCC). However, if either output is totem pole, data must be unidirectional or the outputs must be 3-stateable and the outputs must be controlled by some direction control mechanism to prevent HIGH-to-LOW contentions in either direction. If both outputs are open-drain, no direction control is needed. The opposite side of the reference transistor (SREF) is connected to the processor core power supply voltage. When DREF is connected through a 200 k $\Omega$  resistor to a 3.3 V to 5.5 V VCC supply and SREF is set between 0.8 V to (VCC -1.5 V), the output of each Sn has a maximum output voltage equal to SREF and the output of each Dn has a maximum output voltage equal to VCC.

Figure.3 Bidirectional translation to multiple higher voltage levels such as an I2C-bus application

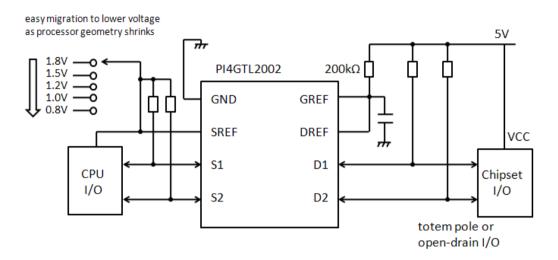

For unidirectional clamping, higher voltage to lower voltage, the GREF input must be connected to DREF and both pins pulled to the higher side VCC through a pull-up resistor (typically 200 k $\Omega$ ). A filter capacitor on DREF is recommended. Pull-up resistors are required if the chip set I/O are open-drain. The opposite side of the reference transistor (SREF) is connected to the processor core supply voltage. When DREF is connected through a 200 k $\Omega$  resistor to a 3.3 V to 5.5 V VCC supply and SREF is set between 0.8 V to (VCC-1.5 V), the output of each Sn has a maximum output voltage equal to SREF.

Figure.4 Unidirectional down translation to protect low voltage processor pins

For unidirectional up translation, lower voltage to higher voltage, the reference transistor is connected the same as for a down translation. A pull-up resistor is required on the higher voltage side (Dn or Sn) to get the full HIGH level, since the GTL-TVC device will only pass the reference source (SREF) voltage as a HIGH when doing an up translation. The driver on the lower voltage side only needs pull-up resistors if it is open-drain.

Figure.5 Unidirectional down translation to protect higher voltage processor pins

# **Pull-up Resistors and Minimum Values**

Sizing the pull-up resistor on an open-drain bus is specific to the individual application and is dependent on the following driver characteristics:

- The driver sink current

- The V<sub>OL</sub> of driver

- The  $V_{OL}$  of the PI4GTL2002

- The V<sub>IL</sub> of the driver

- Frequency of operation

The following tables can be used to estimate the pull-up resistor value in different use cases so that the minimum resistance for the pull-up resistor can be found.

Tables in bellow contain suggested minimum values of pull-up resistors for the PI4GTL2002 with typical voltage translation levels and drive currents.

The calculated values assume that both drive currents are the same.

$V_{OL} = V_{IL} = 0.1$ \*VCC and accounts for a 10 % VCC tolerance of the supplies, 1 % resistor values. It should be noted that the resistor chosen in the final application should be equal to or larger than the values shown in the tablew to ensure that the pass voltage is less than 10 % of the VCC voltage, and the external driver should be able to sink the total current from both pull-up resistors.

|           | minimum values, 3       | mA driver /sink curr       |                            |                            |                            |

|-----------|-------------------------|----------------------------|----------------------------|----------------------------|----------------------------|

| SREF Side |                         |                            | DREF side                  |                            |                            |

|           | 1.5V                    | 1.8V                       | 2.5V                       | 3.3V                       | 5.0V                       |

| 0.8V      | $R_{PU(S)} = 825\Omega$ | $R_{PU(S)} = 936\Omega$    | $R_{PU(S)} = none$         | $R_{PU(S)} = none$         | $R_{PU(S)} = none$         |

|           | $R_{PU(D)} = 825\Omega$ | $R_{PU(D)} = 936\Omega$    | $R_{PU(D)} = 899\Omega$    | $R_{PU(D)} = 1.20k\Omega$  | $R_{PU(D)} = 1.83 k\Omega$ |

|           |                         |                            | Or both $1.20k\Omega$      | Or both $1.49k\Omega$      | Or both $2.12k\Omega$      |

| 1.0V      | $R_{PU(S)} = 892\Omega$ | $R_{PU(S)} = 1k\Omega$     | $R_{PU(S)} = none$         | $R_{PU(S)} = none$         | $R_{PU(S)} = none$         |

|           | $R_{PU(D)} = 892\Omega$ | $R_{PU(D)} = 1k\Omega$     | $R_{PU(D)} = 892\Omega$    | $R_{PU(D)} = 1.19k\Omega$  | $R_{PU(D)} = 1.82k\Omega$  |

|           |                         |                            | Or both $1.26k\Omega$      | Or both $1.56k\Omega$      | Or both 2.19k $\Omega$     |

| 1.2V      |                         | $R_{PU(S)} = 1.07 k\Omega$ | $R_{PU(S)} = none$         | $R_{PU(S)} = none$         | $R_{PU(S)} = none$         |

|           |                         | $R_{PU(D)}\!=1.07k\Omega$  | $R_{PU(D)} = 886\Omega$    | $R_{PU(D)} = 1.18k\Omega$  | $R_{PU(D)} = 1.81 k\Omega$ |

|           |                         |                            | Or both $1.33k\Omega$      | Or both $1.63k\Omega$      | Or both 2.26k $\Omega$     |

| 1.5V      |                         |                            | $R_{PU(S)} = none$         | $R_{PU(S)} = none$         | $R_{PU(S)} = none$         |

|           |                         |                            | $R_{PU(D)}\!=875\Omega$    | $R_{PU(D)} = 1.17 k\Omega$ | $R_{PU(D)} = 1.8k\Omega$   |

|           |                         |                            | Or both $1.43k\Omega$      | Or both $1.73k\Omega$      | Or both 2.36k $\Omega$     |

| 1.8V      |                         |                            | $R_{PU(S)} = 1.53k\Omega$  | $R_{PU(S)} = none$         | $R_{PU(S)} = none$         |

|           |                         |                            | $R_{PU(D)} = 1.53 k\Omega$ | $R_{PU(D)} = 1.16 k\Omega$ | $R_{PU(D)} = 1.79 k\Omega$ |

|           |                         |                            |                            | Or both $1.82k\Omega$      | Or both 2.46k $\Omega$     |

| 2.5V      |                         |                            |                            | $R_{PU(S)} = 2.06 k\Omega$ | $R_{PU(S)} = none$         |

|           |                         |                            |                            | $R_{PU(D)} = 2.06 k\Omega$ | $R_{PU(D)} = 1.77 k\Omega$ |

|           |                         |                            |                            |                            | Or both 2.69k $\Omega$     |

| 3.3V      |                         |                            |                            |                            | $R_{PU(S)} = none$         |

|           |                         |                            |                            |                            | $R_{PU(D)} = 1.74 k\Omega$ |

|           |                         |                            |                            |                            | Or both 2.96k $\Omega$     |

Pull-up resistor minimum values, 3 mA driver /sink current for PI4GTL2002

| Pull-up | resistor | minimum | values, | 10 mA | driver/ | sink | current | for | PI4GT | L2002 |

|---------|----------|---------|---------|-------|---------|------|---------|-----|-------|-------|

|         |          |         |         |       |         |      |         |     |       |       |

| SREF Side |                           |                         | DREF side                 |                         |                         |

|-----------|---------------------------|-------------------------|---------------------------|-------------------------|-------------------------|

|           | 1.5V                      | 1.8V                    | 2.5V                      | 3.3V                    | 5.0V                    |

| 0.8V      | $R_{PU(S)} = 247\Omega$   | $R_{PU(S)} = 281\Omega$ | $R_{PU(S)} = none$        | $R_{PU(S)} = none$      | $R_{PU(S)} = none$      |

|           | $R_{PU(D)}\!=247\Omega$   | $R_{PU(D)} = 281\Omega$ | $R_{PU(D)} = 270\Omega$   | $R_{PU(D)} = 359\Omega$ | $R_{PU(D)}\!=547\Omega$ |

|           |                           |                         | Or both $359\Omega$       | Or both $447\Omega$     | Or both $636\Omega$     |

| 1.0V      | $R_{PU(S)} = 268\Omega$   | $R_{PU(S)}=300\Omega$   | $R_{PU(S)} = none$        | $R_{PU(S)} = none$      | $R_{PU(S)} = none$      |

|           | $R_{PU(D)}\!=\!268\Omega$ | $R_{PU(D)} = 300\Omega$ | $R_{PU(D)}\!=\!268\Omega$ | $R_{PU(D)} = 357\Omega$ | $R_{PU(D)}\!=545\Omega$ |

|           |                           |                         | Or both $379\Omega$       | Or both $468\Omega$     | Or both $657\Omega$     |

| 1.2V      |                           | $R_{PU(S)} = 321\Omega$ | $R_{PU(S)} = none$        | $R_{PU(S)} = none$      | $R_{PU(S)} = none$      |

|           |                           | $R_{PU(D)} = 321\Omega$ | $R_{PU(D)}\!=\!266\Omega$ | $R_{PU(D)} = 355\Omega$ | $R_{PU(D)} = 543\Omega$ |

|           |                           |                         | Or both $399\Omega$       | Or both $488\Omega$     | Or both $677\Omega$     |

| 1.5V      |                           |                         | $R_{PU(S)} = none$        | $R_{PU(S)} = none$      | $R_{PU(S)} = none$      |

|           |                           |                         | $R_{PU(D)}\!=\!263\Omega$ | $R_{PU(D)} = 352\Omega$ | $R_{PU(D)}\!=540\Omega$ |

|           |                           |                         | Or both $429\Omega$       | Or both $518\Omega$     | Or both $707\Omega$     |

| 1.8V      |                           |                         | $R_{PU(S)} = 460\Omega$   | $R_{PU(S)} = none$      | $R_{PU(S)} = none$      |

|           |                           |                         | $R_{PU(D)}\!=\!460\Omega$ | $R_{PU(D)} = 348\Omega$ | $R_{PU(D)}\!=537\Omega$ |

|           |                           |                         |                           | Or both $548\Omega$     | Or both $737\Omega$     |

| 2.5V      |                           |                         |                           | $R_{PU(S)} = 619\Omega$ | $R_{PU(S)} = none$      |

|           |                           |                         |                           | $R_{PU(D)} = 619\Omega$ | $R_{PU(D)} = 521\Omega$ |

|           |                           |                         |                           |                         | Or both $808\Omega$     |

| 3.3V      |                           |                         |                           |                         | $R_{PU(S)} = none$      |

|           |                           |                         |                           |                         | $R_{PU(D)}\!=522\Omega$ |

|           |                           |                         |                           |                         | Or both $889\Omega$     |

| SREF Side |                         |                           | DREF side                 |                         |                           |

|-----------|-------------------------|---------------------------|---------------------------|-------------------------|---------------------------|

|           | 1.5V                    | 1.8V                      | 2.5V                      | 3.3V                    | 5.0V                      |

| 0.8V      | $R_{PU(S)} = 165\Omega$ | $R_{PU(S)} = 187\Omega$   | $R_{PU(S)} = none$        | $R_{PU(S)} = none$      | $R_{PU(S)} = none$        |

|           | $R_{PU(D)} = 165\Omega$ | $R_{PU(D)} \!= 187\Omega$ | $R_{PU(D)} = 180\Omega$   | $R_{PU(D)} = 239\Omega$ | $R_{PU(D)} = 365\Omega$   |

|           |                         |                           | Or both $239\Omega$       | Or both $298\Omega$     | Or both $424\Omega$       |

| 1.0V      | $R_{PU(S)} = 178\Omega$ | $R_{PU(S)} = 200\Omega$   | $R_{PU(S)} = none$        | $R_{PU(S)} = none$      | $R_{PU(S)} = none$        |

|           | $R_{PU(D)}\!=178\Omega$ | $R_{PU(D)}\!=\!200\Omega$ | $R_{PU(D)} = 178\Omega$   | $R_{PU(D)} = 237\Omega$ | $R_{PU(D)}\!=\!364\Omega$ |

|           |                         |                           | Or both $253\Omega$       | Or both $312\Omega$     | Or both $438\Omega$       |

| 1.2V      |                         | $R_{PU(S)} = 214\Omega$   | $R_{PU(S)} = none$        | $R_{PU(S)} = none$      | $R_{PU(S)} = none$        |

|           |                         | $R_{PU(D)} = 214\Omega$   | $R_{PU(D)} \!= 177\Omega$ | $R_{PU(D)} = 236\Omega$ | $R_{PU(D)} = 362\Omega$   |

|           |                         |                           | Or both $266\Omega$       | Or both $325\Omega$     | Or both $451\Omega$       |

| 1.5V      |                         |                           | $R_{PU(S)} = none$        | $R_{PU(S)} = none$      | $R_{PU(S)} = none$        |

|           |                         |                           | $R_{PU(D)} \!= 175\Omega$ | $R_{PU(D)} = 234\Omega$ | $R_{PU(D)} = 360\Omega$   |

|           |                         |                           | Or both $286\Omega$       | Or both $345\Omega$     | Or both $471\Omega$       |

| 1.8V      |                         |                           | $R_{PU(S)} = 306\Omega$   | $R_{PU(S)} = none$      | $R_{PU(S)} = none$        |

|           |                         |                           | $R_{PU(D)} = 306\Omega$   | $R_{PU(D)} = 232\Omega$ | $R_{PU(D)}=358\Omega$     |

|           |                         |                           |                           | Or both $366\Omega$     | Or both $492\Omega$       |

| 2.5V      |                         |                           |                           | $R_{PU(S)} = 413\Omega$ | $R_{PU(S)} = none$        |

|           |                         |                           |                           | $R_{PU(D)} = 413\Omega$ | $R_{PU(D)}\!=354\Omega$   |

|           |                         |                           |                           |                         | Or both $539\Omega$       |

| 3.3V      |                         |                           |                           |                         | $R_{PU(S)} = none$        |

|           |                         |                           |                           |                         | $R_{PU(D)} = 348\Omega$   |

|           |                         |                           |                           |                         | Or both $593\Omega$       |

Pull-up resistor minimum values, 15 mA driver/ sink current for PI4GTL2002

## **Part Marking**

U Package

Z: Die Rev Y: Date Code (Year) W: Date Code (Workweek) 1st X: Assembly Site Code 2nd X: Wafer Fab Site Code Bar above fab code means Cu wire

XT Package

Y: Date Code (Year) W: Date Code (Workweek) W Package

PI4GTL 2002WE ZYWXX 0

Z: Die Rev Y: Date Code (Year) W: Date Code (Workweek) 1st X: Assembly Site Code 2nd X: Wafer Fab Site Code Bar above fab code means Cu wire

# **Packaging Mechanical**

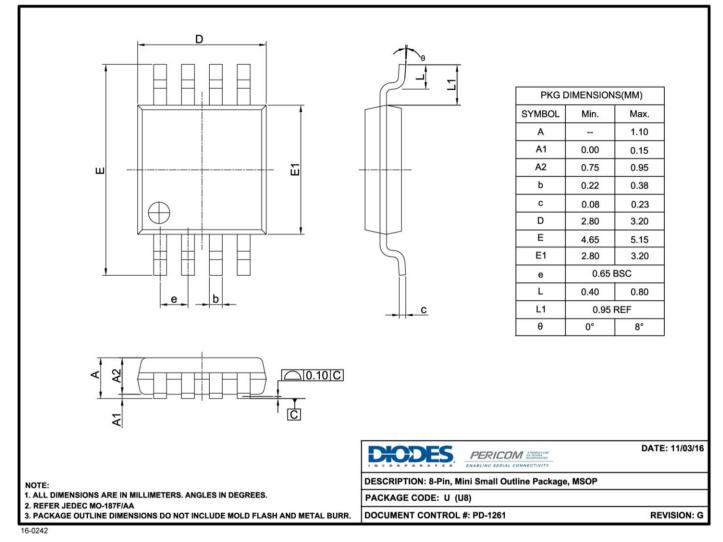

8-MSOP (U)

A Product Line of Diodes Incorporated

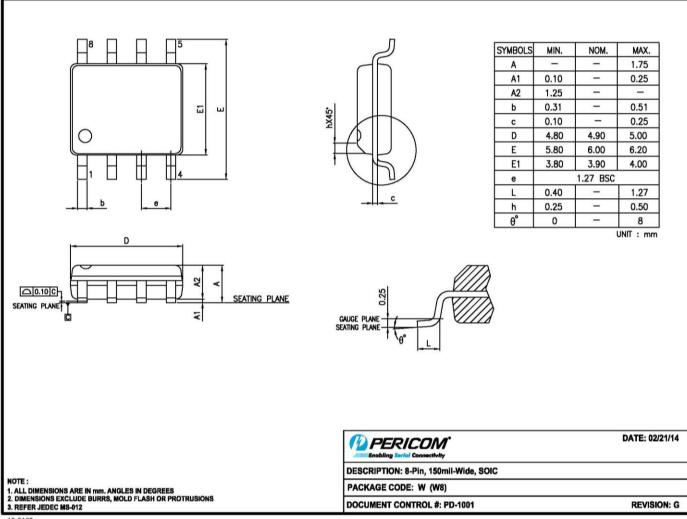

8-SOIC (W)

15-0103

A Product Line of Diodes Incorporated

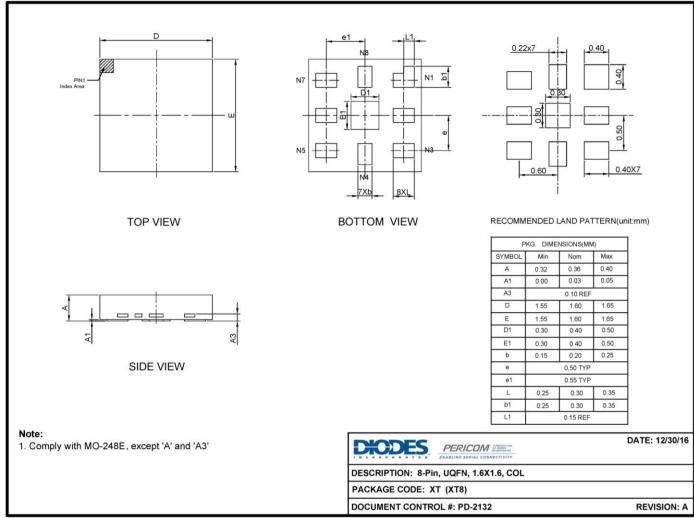

8-UQFN (XT)

16-0286

#### For latest package info.

please check: http://www.diodes.com/design/support/packaging/pericom-packaging/packaging-mechanicals-and-thermal-characteristics/

### **Ordering Information**

| Part Numbers   | Package Code | Package                                  |

|----------------|--------------|------------------------------------------|

| PI4GTL2002UEX  | U            | 8-Pin, Mini Small Outline Package (MSOP) |

| PI4GTL2002WEX  | W            | 8-Pin,150 mil-Wide (SOIC)                |

| PI4GTL2002XTEX | XT           | 8-Pin, 1.6x1.6, COL (UQFN)               |

Notes:

1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

2. See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

4. E = Pb-free and Green

5. X suffix = Tape/Reel

**PI4GTL2002**

#### IMPORTANT NOTICE

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

A. Life support devices or systems are devices or systems which:

1. are intended to implant into the body, or

2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the

failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2016, Diodes Incorporated www.diodes.com