### HiFlex<sup>TM</sup> Network Clock Generator

#### **Features**

- → 3.3V supply voltage

- → 3 HCSL and 1 LVCMOS 100MHz outputs with OE/ function

- → 1 LVCMOS 100/50MHz selectable

- → 25MHz crystal or differential input

- → Low 1ps RMS max integrated phase noise design

- → PLL Bypass mode for test

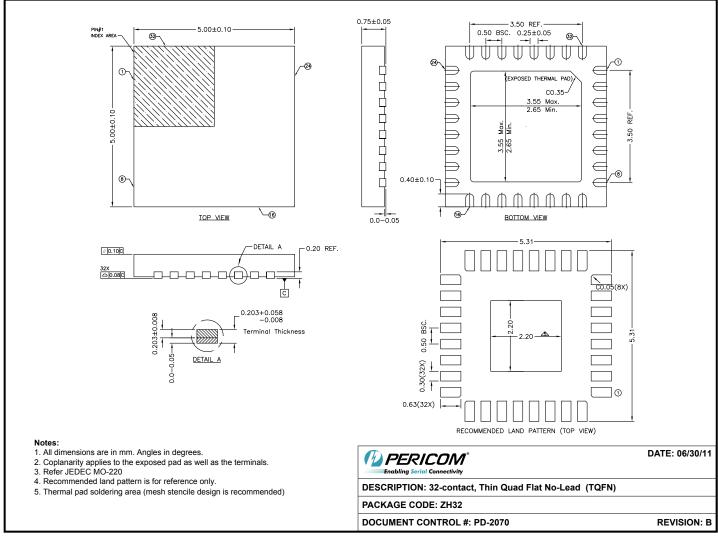

- → 32 lead 5x5mm TQFN package

### **Description**

The PI6LC4830 is an LC VCO based low phase noise design intended for the most demanding PCIe\* 2.0 applications. Use of the ultra-low noise LC VCO allows for much greater noise margins than traditional solutions. This is ideal for noisy environments.

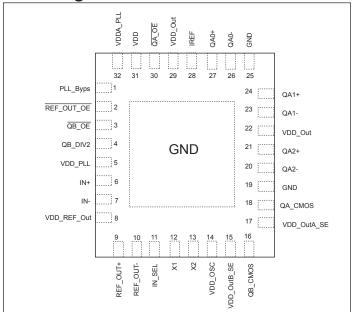

### **Pin Configuration**

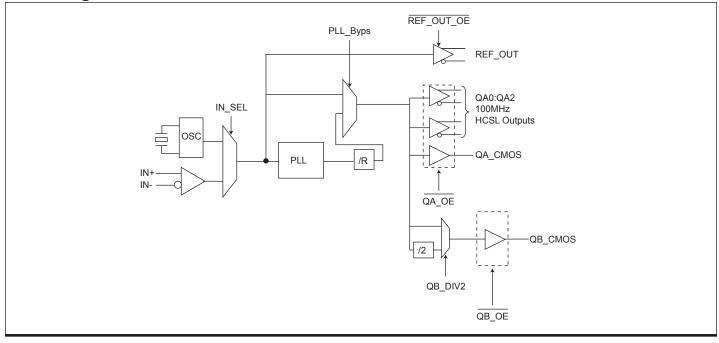

### **Block Diagram**

12-0238 1 PI6LC4830 Rev B 08/17/12

# Pin Description

| Pin Number                | Pin Name                              | Туре                 | Description                                                                                                                        |

|---------------------------|---------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------|

| 20, 21, 23, 24,<br>26, 27 | QA0+, QA0-, QA1+,<br>QA1-, QA2+, QA2- | Output (HCSL)        | 100MHz HCSL Outputs                                                                                                                |

| 9, 10                     | REF_Out+, REF_Out-                    | Output (LVPECL)      | 25MHz LVPECL output from fundamental oscillator core                                                                               |

| 12                        | X1                                    | Input                | Crystal input pin                                                                                                                  |

| 13                        | X2                                    | Output               | Oscillator output pin                                                                                                              |

| 6, 7                      | IN+, IN-                              | Input (Differential) | HCSL/LVPECL/LVDS inputs                                                                                                            |

| 11                        | IN_SEL                                | Input (LVCMOS)       | Low selects X1 and X2, High selects In+, In Internal pull up is 100k Ohms                                                          |

| 1                         | PLL_Byps                              | Input (LVCMOS)       | If Low, output buffers are switched to the PLL. If High, output buffers are switched to the input mux. Internal 100K-Ohm pulldown. |

| 30, 3                     | QA_OE, QB_OE                          | Input (LVCMOS)       | Low enables outputs, High selects high impedance mode. Internal 100K-Ohm pulldown                                                  |

| 14                        | V <sub>DD</sub> _OSC                  | Power                | Power for xtal Osc core                                                                                                            |

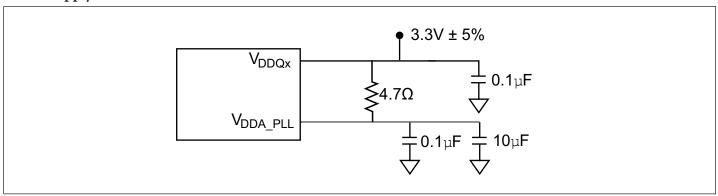

| 5                         | V <sub>DD</sub> _PLL                  | Power                | Power for digital portion of PLL circuitry                                                                                         |

| 22, 29                    | V <sub>DD</sub> _Out                  | Power                | Power for output buffers                                                                                                           |

| 32                        | V <sub>DDA</sub> _PLL                 | Power                | Power for analog core of PLL                                                                                                       |

| 19, 25                    | GND                                   | Power                | Ground                                                                                                                             |

| 18                        | QA_CMOS                               | Output (LVCMOS)      | 100MHz LVCMOS Output                                                                                                               |

| 16                        | QB_CMOS                               | Output (LVCMOS)      | 100/50MHz Selectable LVCMOS Output                                                                                                 |

| 17                        | V <sub>DD</sub> _OutA_SE              | Power                | Bank A LVCMOS Power                                                                                                                |

| 15                        | V <sub>DD</sub> _OutB_SE              | Power                | Bank B LVCMOS Power                                                                                                                |

| 4                         | QB_DIV2                               | Input (LVCMOS)       | High selects 50MHz, Low selects 100MHz. Internal 100K-Ohm pull-up                                                                  |

| 28                        | $I_{REF}$                             | Output               | External resistor connection for internal current reference                                                                        |

| 8                         | V <sub>DD</sub> _REF_OUT              | Power                | Power for reference output                                                                                                         |

| 2                         | REF_OUT_OE                            | Input (LVCMOS)       | Low enables outputs, High selects high impedance mode. Internal 100K-Ohm pull-down.                                                |

| 31                        | $V_{\mathrm{DD}}$                     | Power                | Power for Core                                                                                                                     |

### Maximum Ratings (Above which the useful life may be impaired. For user guidelines, not tested)

| Storage temperature        | -65°C to +155°C |

|----------------------------|-----------------|

| 3.3V Analog Supply Voltage | 0.5 to +4.6V    |

| ESD Protection (HBM)       | 2000V           |

#### Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **Operating Conditions** (Over Operating Conditions)

| Symbol                      | Parameters                                 | Conditions                                       | Min. | Max. | Units |

|-----------------------------|--------------------------------------------|--------------------------------------------------|------|------|-------|

| V <sub>DD_PLL</sub>         | PLL Power Supply Voltage                   |                                                  | 2.8  | 3.6  |       |

| V <sub>DD_REF_Out</sub>     | Power Supply for Reference Out             |                                                  | 2.9  | 3.6  |       |

| V <sub>DD_OSC</sub>         | Power Supply Voltage for oscillator core   |                                                  | 2.8  | 3.6  |       |

| V <sub>DD_OutA</sub> , OutB | Power Supply Voltage for Bank A and Bank B |                                                  | 2.9  | 3.6  | V     |

| V <sub>DD_Out</sub>         | Power Supply Voltage for Output<br>Buffer  |                                                  | 2.9  | 3.6  |       |

| $V_{\mathrm{DD}}$           | 3.3V General Power Supply Voltage          |                                                  | 2.9  | 3.6  |       |

| V <sub>DDA_PLL</sub>        | Analog PLL Power Supply Voltage            |                                                  | 2.8  | 3.6  |       |

| $T_{A}$                     | Ambient Temperature                        |                                                  | -40  | 85   | °C    |

| $I_{\mathrm{DD\_PLL}}$      | PLL Power Supply Current                   | At 3.6V, loaded                                  |      | 10   |       |

| I <sub>DD_REF_OUT</sub>     | Current for Reference Out                  | At 3.6V, loaded                                  |      | 36   |       |

| I <sub>DD_OSC</sub>         | Current for Oscillator                     | At 3.6V, loaded                                  |      | 12   |       |

| I <sub>DD_OUTA</sub> , OUTB | Current for Bank A and Bank B              | At 3.6V, loaded                                  |      | 11   |       |

| I <sub>DD_OUT</sub>         | Current for Output Buffer                  | At 3.6V, loaded                                  |      | 76   | mA    |

| I <sub>DDA</sub> _PLL       | Analog PLL Current, V <sub>DDA_PLL</sub>   | At 3.6V, loaded                                  |      | 35   |       |

|                             |                                            | No load (Analog PLL Current Included)            |      | 85   |       |

| $I_{DD}$                    | Total Power Supply Current                 | All outputs loaded (Analog PLL Current Included) |      | 180  |       |

| P <sub>Diss</sub>           | Power Dissipation                          | All outputs loaded                               |      | 0.65 | W     |

## **LVCMOS DC Electrical Characteristics** (Over Operating Conditions)

| Symbol          | Parameters                                                | Conditions        | Min.                  | Тур. | Max.               | Units |

|-----------------|-----------------------------------------------------------|-------------------|-----------------------|------|--------------------|-------|

| V <sub>IH</sub> | Input High Voltage                                        |                   | 2                     |      | $V_{\rm DD} + 0.3$ |       |

| $V_{\rm IL}$    | Input Low Voltage                                         |                   | -0.3                  |      | 0.8                | 37    |

| V <sub>OH</sub> | Output High Voltage                                       | $I_{OH} = -8mA$   | V <sub>DD</sub> - 0.4 |      |                    | V     |

| V <sub>OL</sub> | Output Low Voltage                                        | $I_{OL} = 8mA$    |                       |      | 0.4                |       |

| $I_{IH}$        | Input High Current for QA_OE, QB_OE, REF_OUT_OE, PLL_Byps | $V_{IN} = V_{DD}$ |                       |      | 45                 |       |

|                 | IN_SEL, QB_DIV2                                           |                   |                       |      | 5                  |       |

| $I_{IL}$        | Input Low Current for QA_OE, QB_OE, REF_OUT_OE, PLL_Byps  | $V_{IN} = 0V$     | -5                    |      |                    | μΑ    |

|                 | IN_SEL, QB_DIV2                                           |                   | -45                   |      |                    |       |

| R <sub>pu</sub> | Internal pull up resistance                               |                   |                       | 105  |                    | kOhm  |

| R <sub>dn</sub> | Internal pull down resistance                             |                   |                       | 105  |                    | kOhm  |

| Zo              | Output Impedance                                          |                   |                       | 30   |                    | Ohm   |

| C <sub>IN</sub> | Input Capacitance for X1, X2 inputs                       |                   |                       | 4    |                    | pF    |

## **LVCMOS AC Characteristics** (Over Operating Conditions)

| Symbol                         | Parameter                           | Conditions                                                                                                   | Min. | Тур. | Max. | Units |

|--------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| f <sub>error</sub>             | Frequency Synthesis Error           |                                                                                                              |      |      | 0    | ppm   |

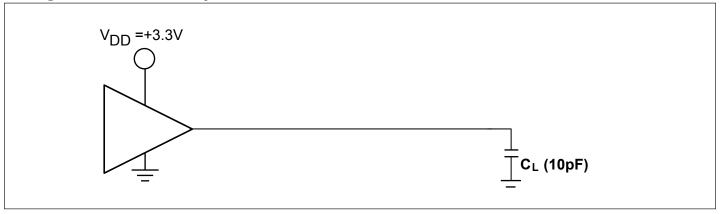

| T <sub>r</sub> /T <sub>f</sub> | Output Rise/Fall time               | $20\%$ to $80\%$ , $C_L = 10$ pF                                                                             |      | 1.2  | 2    | ns    |

| $T_{DC}$                       | Output Duty Cycle                   | $t_{DC} = t_H/t_{CY}$ , $t_H = \text{High Pulse Width}$ , $t_{CY} = \text{Output Cycle Time}$ , @ $V_{DD}/2$ | 45   | 50   | 55   | %     |

| Jcc                            | Jitter, Cycle-to-Cycle              |                                                                                                              |      |      | 175  |       |

| J <sub>phase</sub>             | Rms Phase jitter from 12kHz - 20MHz |                                                                                                              |      | 0.4  | 1    | ps    |

| T <sub>EN/DIS</sub>            | Output enable/disable time          |                                                                                                              |      |      | 80   | ns    |

| $T_{LOCK}$                     | PLL Lock Time                       |                                                                                                              |      |      | 5    | ms    |

### **Differential DC Input Characteristics** (Over Operating Conditions)

| Symbol           | Parameters      |                           | Conditions                 | Min. | Тур. | Max.                       | Units |

|------------------|-----------------|---------------------------|----------------------------|------|------|----------------------------|-------|

| т                | Input High      | IN-                       | $V_{IN} = V_{DD} = 3.465V$ |      |      | 5                          |       |

| $I_{IH}$         | Current         | IN+                       | $V_{IN} = V_{DD} = 3.465V$ |      |      | 45                         | 4     |

| Input Low        | IN-             | $V_{IN} = 0V$             | -45                        |      |      | uA                         |       |

| $I_{IL}$         | Current         | IN+                       | $V_{IN} = 0V$              | -5   |      |                            |       |

| V <sub>CMR</sub> | Common Mode     | Common Mode Voltage Range |                            | 0.5  |      | V <sub>DD</sub> -<br>0.85V | V     |

| V <sub>PP</sub>  | Peak-to-Peak Ir | nput Voltage Swing        |                            | 0.15 |      | 1.3                        | V     |

### **HCSL DC Electrical Characteristics** (Over Operating Conditions)

| Symbol               | Parameters                                                                     | Condition                                 | Min. | Тур. | Max. | Units |

|----------------------|--------------------------------------------------------------------------------|-------------------------------------------|------|------|------|-------|

| V <sub>OH</sub>      | Output High Voltage                                                            | $VDD_OUT = V_{DD} - 0.15V$ <sup>(1)</sup> | 660  |      | 900  |       |

| V <sub>OL</sub>      | Output Low Voltage                                                             |                                           |      |      | 150  |       |

| V <sub>CROSS</sub>   | Absolute Crossing Point Voltages                                               |                                           | 250  |      | 550  | mV    |

| D V <sub>CROSS</sub> | Total variation of V <sub>CROSS</sub> overall edges                            |                                           |      |      | 140  |       |

| ЮН                   | Output High Current w/ 475-Ohm resistor.<br>Connected between IREF pin and GND |                                           |      | 14   |      | mA    |

#### Note:

## HCSL AC Output Switching Characteristics(1,2,3) (Over Operating Conditions)

| Symbol                                | Parameters                                                          | Min | Тур | Max. | Units | Notes |

|---------------------------------------|---------------------------------------------------------------------|-----|-----|------|-------|-------|

| f <sub>error</sub>                    | Frequency Synthesis Error                                           |     |     | 0    | ppm   |       |

| T <sub>rise</sub> / T <sub>fall</sub> | Rise and Fall Time (measured between 0.175V to 0.525V)              | 175 | 250 | 700  |       | 2     |

| $\Delta T_{rise}$ / $\Delta T_{fall}$ | Rise and Fall Time Variation                                        |     | 7   | 125  | ps    | 2     |

| T <sub>skew</sub>                     | Output-to-Output Skew                                               |     | 20  | 100  |       | 3     |

| $T_{DC}$                              | Duty Cycle (Measured at 100 MHz)                                    | 47  | 50  | 53   | %     | 3     |

| J <sub>phase</sub>                    | RMS phase jitter from 12kHz - 20MHz                                 |     | 0.4 | 1    |       | 2     |

| T <sub>HF-RMS</sub>                   | >1.5MHz - 50MHz RMS jitter applying PCIE G2 jitter mask             |     | 2.2 | 3.1  | ps    | 3     |

| PSR                                   | Power Supply Rejection with -30dBm input sine wave 100kHz to 600kHz |     | -46 |      | dBc   | 2     |

| T <sub>EN/DIS</sub>                   | Output enable/disable time                                          |     |     | 80   | ns    |       |

| $T_{LOCK}$                            | PLL Lock Time                                                       |     |     | 5    | ms    |       |

#### Notes:

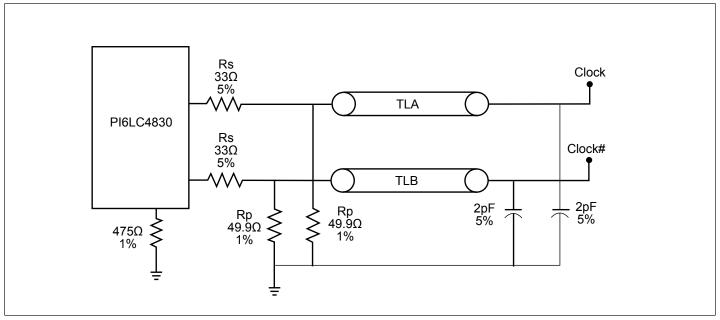

- 1. Test configuration is RS =  $33\Omega$ , Rp =  $49.9\Omega$  with 2pF load.

- 2. Measurement taken from Single Ended waveform.

- 3. Measurement taken from Differential waveform.

12-0238 PI6LC4830 Rev B 08/17/12

<sup>1.</sup> This voltage drop is to account for the voltage across the series resistor in the layout guidelines.

### LVPECL DC Electrical Characteristics (Over Operating Conditions)

| Symbol          | Parameters               | Condition                         | Min.                 | Тур. | Max.                 | Units |

|-----------------|--------------------------|-----------------------------------|----------------------|------|----------------------|-------|

| $V_{PP}$        | Output peak-peak Voltage | V <sub>DD_REF_Out</sub> = 3.3± 5% | 0.4                  | 0.7  | 1                    |       |

| V <sub>OH</sub> | Output High Voltage      | $V_{DD\_REF\_Out} = 3.3 \pm 5\%$  | V <sub>DD</sub> -1.4 |      | V <sub>DD</sub> -0.9 | V     |

| V <sub>OL</sub> | Output Low Voltage       | V <sub>DD_REF_Out</sub> = 3.3± 5% | V <sub>DD</sub> -2.0 |      | V <sub>DD</sub> -1.7 |       |

### **AC LVPECL Switching Characteristics**

| Symbol                                | Parameters                 | Condition                    | Min. | Тур. | Max. | Units |

|---------------------------------------|----------------------------|------------------------------|------|------|------|-------|

| T <sub>rise</sub> / T <sub>fall</sub> | Rise and Fall Time         | 20% to 80%, single-<br>ended | 200  | 320  | 450  | ps    |

| $T_{DC}$                              | Duty Cycle                 | Differential                 | 47   | 50   | 53   | %     |

| T <sub>EN/DIS</sub>                   | Output enable/disable time |                              |      |      | 100  | ns    |

### **Crystal Characteristic** (link to "http://www.pericom.com/saronix" for more detailed crystal specifications)

|                    | ·                            |             |     |      |       |

|--------------------|------------------------------|-------------|-----|------|-------|

| Parameters         | Description                  | Min         | Тур | Max. | Units |

| OSCmode            | Mode of Oscillation          | Fundamental |     |      |       |

| FREQ               | Frequency                    |             | 25  |      | MHz   |

| ESR <sup>(1)</sup> | Equivalent Series Resistance |             |     | 50   | Ohm   |

| Cload              | Load Capacitance             |             | 18  |      | E     |

| Cshunt             | Shunt Capacitance            |             |     | 7    | pF    |

| DRIVE level        |                              |             |     | 1    | mW    |

Note: 1. ESR value is dependent upon frequency of oscillation

## **Application Notes**

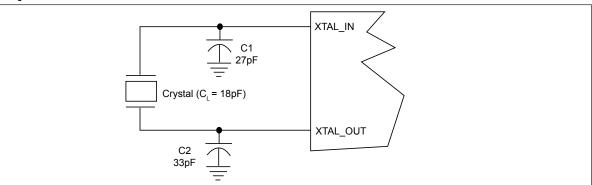

### **Crystal circuit connection**

The following diagram shows PI6LC4830 crystal circuit connection with a parallel crystal. For the CL=18pF crystal, it is suggested to use C1= 27pF, C2= 33pF. C1 and C2 can be adjusted to fine tune to the target ppm of crystal oscillator according to different board layouts.

## **Crystal Oscillator Circuit**

### **Recommended Crystal Specification**

#### Pericom recommends:

- a) GC2500003 XTAL 49S/SMD(4.0 mm), 25M, CL=18pF, +/-30ppm, http://www.pericom.com/pdf/datasheets/se/GC GF.pdf

- b) FY2500081, SMD 5x3.2(4P), 25M, CL=18pF, +/-30ppm, http://www.pericom.com/pdf/datasheets/se/FY F9.pdf

- c) FL2500047, SMD 3.2x2.5(4P), 25M, CL=18pF, +/-20ppm, http://www.pericom.com/pdf/datasheets/se/FL.pdf

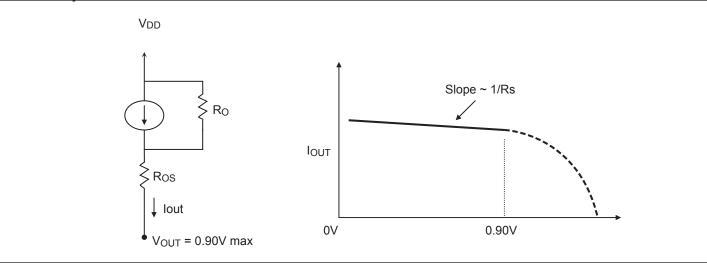

**HCSL** output buffer characteristics

Figure 9. Simplified diagram of current-mode output buffer

#### **HCSL Buffer characteristics**

| Symbol           | Minimum     | Maximum     |

|------------------|-------------|-------------|

| RO               | 3000Ω       | N/A         |

| R <sub>OS</sub>  | unspecified | unspecified |

| V <sub>OUT</sub> | N/A         | 900mV       |

### **Current Accuracy (IREF pin)**

| Symbol           | Conditions                  | Configuration                                          | Load                                      | Min.                      | Max.                      |

|------------------|-----------------------------|--------------------------------------------------------|-------------------------------------------|---------------------------|---------------------------|

| I <sub>OUT</sub> | $V_{\rm DD} = 3.30 \pm 5\%$ | $R_{REF} = 475\Omega \ 1\%$ $I_{REF} = 2.32 \text{mA}$ | Nominal test load for given configuration | -12% I <sub>NOMINAL</sub> | +12% I <sub>NOMINAL</sub> |

#### Note:

### **Differential Clock Output Current**

| Board Target Trace/Term Z                | Reference R, Iref = $V_{DD}/(3xRr)$ | Output Current              | V <sub>OH</sub> @ Z |

|------------------------------------------|-------------------------------------|-----------------------------|---------------------|

| 100Ω                                     | $R_{REF} = 475\Omega 1\%,$          | I 6 v I                     | 0.7V @ 50           |

| (100Ω differential ≈ 15% coupling ratio) | $I_{REF} = 2.32 \text{mA}$          | $I_{OH} = 6 \times I_{REF}$ |                     |

<sup>1.</sup> I<sub>NOMINAL</sub> refers to the expected current based on the configuration of the device.

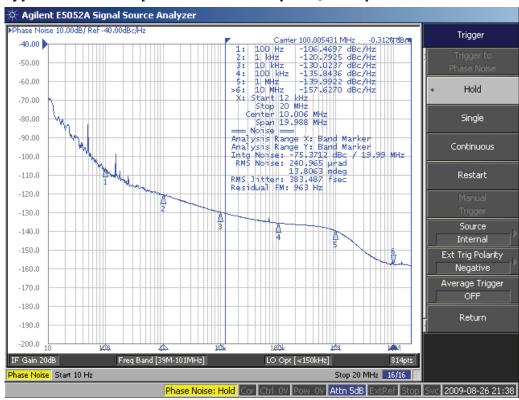

### Typical HCSL Output Phase Noise (3.3V, 25°C)

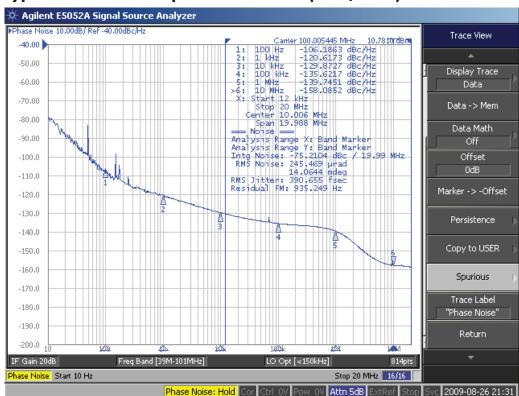

### Typical LVCMOS Output Phase Noise (3.3V, 25°C)

12-0238 PI6LC4830 Rev B 08/17/12

## **Configuration Test Load Board Termination for HCSL outputs**

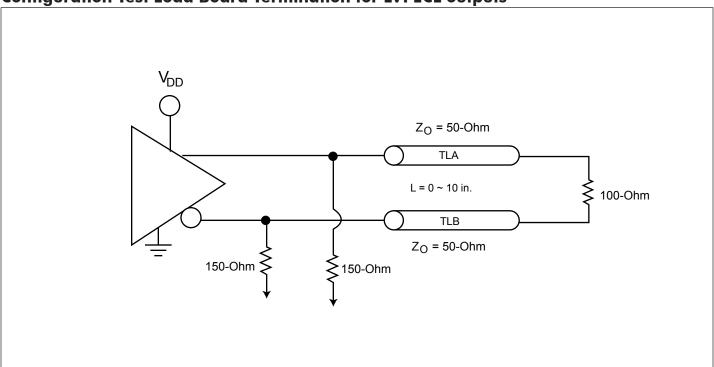

## **Configuration Test Load Board Termination for LVPECL outputs**

## **Configuration CMOS Output**

## **Power Supply Filter**

### Packaging Mechanical: 32-Pin TQFN (ZH)

11-0147

#### Note:

• For latest package info, please check: http://www.pericom.com/products/packaging/mechanicals.php

# Ordering Information<sup>(1-3)</sup>

| Ordering Code | Package Code | Package Description            |

|---------------|--------------|--------------------------------|

| PI6LC4830ZHE  | ZH           | 32-Pin, Pb-free & Green (TQFN) |

#### Notes

- 1. Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

- 2. E = Pb-free and Green

- 3. Adding an X suffix = Tape/Reel

Pericom Semiconductor Corporation • 1-800-435-2336 • www.pericom.com