### **Bridge Driver IC**

#### **Features**

- High Power 3 Phase Bridge Driver for low RDSON N-channel FETs

- 0...100% duty cycle, adjustable without restrictions

- Specified supply voltage range of 5.5 V to 60 V

- Logic operation down to 3 V supply voltage

- High robustness of motor connection pins of -15 V to 90 V

- · Extended protection and supervision functionality

- Serial Peripheral Interface (SPI), control of supervision

- Supervision read out by SPI

- Reverse diode measurement of external FET for temperature detection

- Limp-home functionality of diagnostic and failure behavior with SPI configurable content

- 3 current sense amplifiers for shunt signal conditioning

- 2 switch off paths by pins ENA and SOFF

- Low quiescent current mode by pin INH

- Compatible to 3.3 V μCs and TTL logic

- Phase voltage feedback with SPI programmable voltage thresholds

- Output for phase cut off circuit activation

- Green Product (RoHS compliant)

#### **Product validation**

Qualified for Automotive Applications.

Product validation according to AEC-Q100/101.

#### **Bridge Driver IC**

**Description**

### **Description**

The TLE9180D-310K is an advanced gate driver IC dedicated to control 6 external N-channel MOSFETs forming an inverter for high current 3 phase motor drives application in the automotive sector.

A sophisticated high voltage technology allows the TLE9180D-31QK to support applications for single and mixed battery systems with battery voltages of 12 V, 24 V and 48 V even within tough automotive environments in combination with high motor currents. Therefore bridge, motor and supply related pins can withstand voltages of up to 90 V. Motor related pins can even withstand negative voltage transients down to - 15 V without damage.

All low- and high-side output stages are based on a floating concept and its driver strength allows to drive lowest RDSON MOSFETs common on the market. In 12 V applications the gate driver IC is capable of driving 6 MOSFETs, each with a max. total gate charge of QgTOT = 300 nC, at a frequency of up to 20 kHz.

An integrated SPI interface is used to configure the TLE9180D-310K for the application after power-up. After successful power-up parameters can be adjusted by SPI, monitoring data, configuration and error registers can be read. Cyclic redundancy check over data and address bits ensures safe communication and data integrity.

GND related bridge currents can be measured with 3 integrated current sense amplifiers. The outputs of the current sense amplifiers support 5 V ADCs and the robust inputs can withstand negative transients down to -10 V without damage. Gain and zero current voltage offset can be adjusted by SPI. The offset can be calibrated.

Diagnostic coverage and redundancy have increased steadily in recent years in automotive drive applications. Therefore the TLE9180D-31QK offers a wide range of diagnostic features, like monitoring of power supply voltages as well as system parameters. A testability of safety relevant supervision functions has been integrated. Failure behavior, threshold voltages and filter times of the supervisions of the device are adjustable via SPI.

The TLE9180D-31QK is integrated in a LQFP64 package with an exposed pad. Due to its exposed pad the gate driver IC provides an excellent thermal characteristic.

Table 1 **Device Marking**

| Туре          | Package | Marking       |

|---------------|---------|---------------|

| TLE9180D-31QK | LQFP-64 | TLE9180D-31QK |

# TLE9180D-31QK Bridge Driver IC

# infineon

### Table of contents

### **Table of contents**

|     | Features                          | . 1  |

|-----|-----------------------------------|------|

|     | Product validation                | . 1  |

|     | Description                       | 2    |

|     | Table of contents                 | . 3  |

| 1   | Block Diagram                     | 4    |

| 2   | Pin Configuration                 | 5    |

| 2.1 | Pin Assignment                    | 5    |

| 2.2 | Pin Definitions and Functions     | . 5  |

| 3   | General Product Characteristics   | 8    |

| 3.1 | Absolute Maximum Ratings          | 8    |

| 3.2 | Thermal Resistance                | . 12 |

| 3.3 | Functional Range                  | . 13 |

| 4   | Input and Output Characteristics  | . 15 |

| 5   | Serial Peripheral Interface - SPI | 16   |

| 6   | Power Supply                      | 17   |

| 7   | Floating MOSFET Driver            | .18  |

| 8   | Shunt Signal Conditioning         | 19   |

| 9   | Protection and Diagnostics        | .20  |

| 9.1 | Supervision Overview              | .20  |

| 10  | Digital Phase Voltage Feedback    | 23   |

| 11  | Operation Modes                   | 24   |

| 12  | Application Information           | 25   |

| 13  | Package Outlines                  | 26   |

|     | Revision History                  | . 27 |

|     | Disclaimer                        | 28   |

#### **Block Diagram**

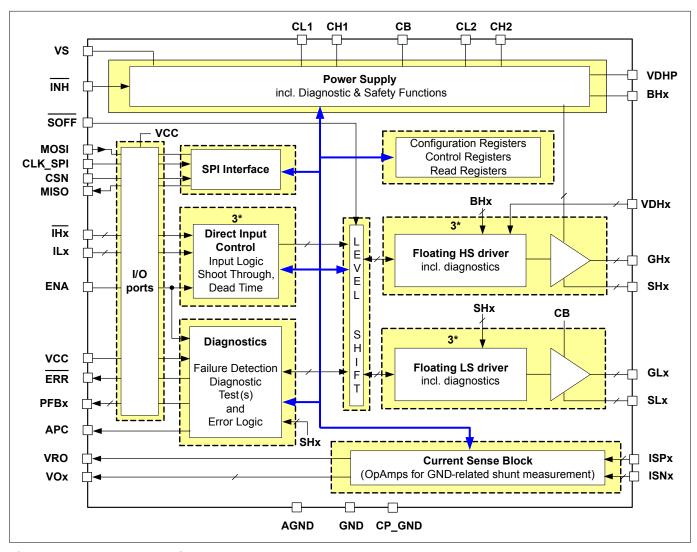

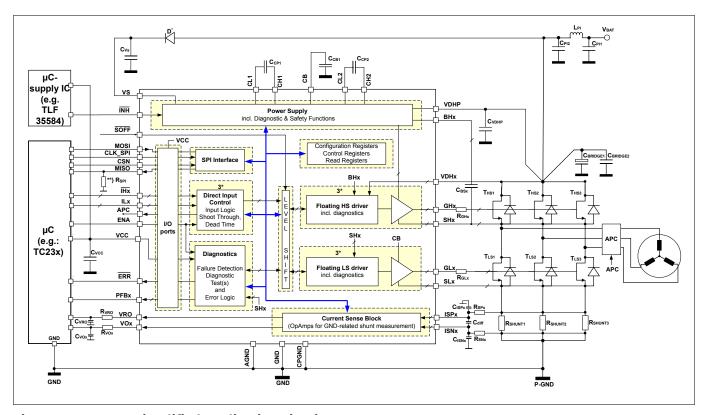

## 1 Block Diagram

Figure 1 Block Diagram

**Pin Configuration**

#### **Pin Configuration** 2

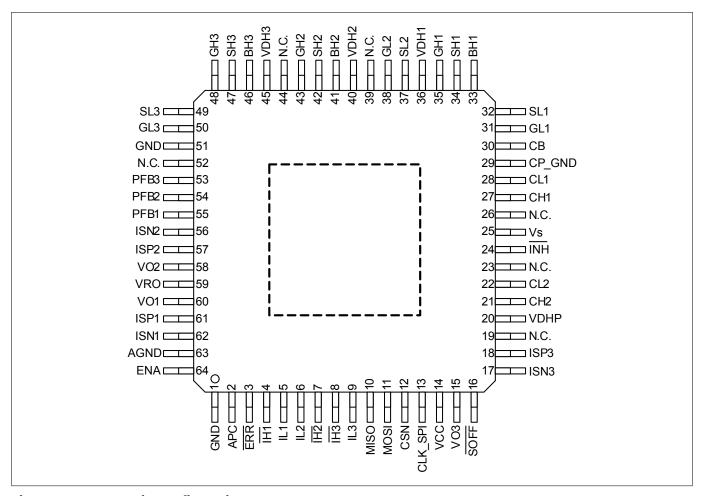

#### **Pin Assignment** 2.1

Figure 2 **Pin Configuration**

#### 2.2 **Pin Definitions and Functions**

| Pin | Symbol | Function                         |

|-----|--------|----------------------------------|

| 1   | GND    | Ground                           |

| 2   | APC    | Activation Phase Cut off Circuit |

| 3   | ERR    | Error Not                        |

| 4   | ĪH1    | Input High-side 1 Not            |

| 5   | IL1    | Input Low-side 1                 |

| 6   | IL2    | Input Low-side 2                 |

| 7   | ĪH2    | Input High-side 2 Not            |

| 8   | ĪH3    | Input High-side 3 Not            |

| 9   | IL3    | Input Low-side 3                 |

| 10  | MISO   | Master In Slave Out              |

# TLE9180D-31QK Bridge Driver IC

### **Pin Configuration**

| Symbol  | Function                                                                                                                                                                                       |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOSI    | Master Out Slave In                                                                                                                                                                            |

| CSN     | Chip Select Not                                                                                                                                                                                |

| CLK_SPI | Clock Serial Peripheral Interface                                                                                                                                                              |

| VCC     | VCC Supply Voltage                                                                                                                                                                             |

| VO3     | Voltage Output of CSA 3                                                                                                                                                                        |

| SOFF    | Safe Off Not                                                                                                                                                                                   |

| ISN3    | Input Shunt Negative of CSA 3                                                                                                                                                                  |

| ISP3    | Input Shunt Positive of CSA 3                                                                                                                                                                  |

| N.C.    | Not Connected                                                                                                                                                                                  |

| VDHP    | Voltage Drain High-side Power                                                                                                                                                                  |

| CH2     | Charge Pump 2 High                                                                                                                                                                             |

| CL2     | Charge Pump 2 Low                                                                                                                                                                              |

| N.C.    | Not Connected                                                                                                                                                                                  |

| ĪNH     | Inhibit Not                                                                                                                                                                                    |

| Vs      | Voltage Supply                                                                                                                                                                                 |

| N.C.    | Not Connected                                                                                                                                                                                  |

| CH1     | Charge Pump 1 High                                                                                                                                                                             |

| CL1     | Charge Pump 1 Low                                                                                                                                                                              |

| CP_GND  | Charge Pump Ground                                                                                                                                                                             |

| СВ      | Charge Pump Buffer                                                                                                                                                                             |

| GL1     | Gate Low-side 1                                                                                                                                                                                |

| SL1     | Source Low-side 1                                                                                                                                                                              |

| BH1     | Bootstrap High-side 1                                                                                                                                                                          |

| SH1     | Source High-side 1                                                                                                                                                                             |

| GH1     | Gate High-side 1                                                                                                                                                                               |

| VDH1    | Voltage Drain High-side 1                                                                                                                                                                      |

| SL2     | Source Low-side 2                                                                                                                                                                              |

| GL2     | Gate Low-side 2                                                                                                                                                                                |

| N.C.    | Not Connected                                                                                                                                                                                  |

| VDH2    | Voltage Drain High-side 2                                                                                                                                                                      |

| BH2     | Bootstrap High-side 2                                                                                                                                                                          |

| SH2     | Source High-side 2                                                                                                                                                                             |

| GH2     | Gate High-side 2                                                                                                                                                                               |

| N.C.    | Not Connected                                                                                                                                                                                  |

| VDH3    | Voltage Drain High-side 3                                                                                                                                                                      |

|         | MOSI  CSN  CLK_SPI  VCC  VO3  SOFF  ISN3  ISP3  N.C.  VDHP  CH2  CL2  N.C.  INH  Vs  N.C.  CH1  CL1  CP_GND  CB  GL1  SL1  BH1  SH1  SH1  GH1  VDH1  SL2  GL2  N.C.  VDH2  BH2  SH2  SH2  N.C. |

# TLE9180D-31QK Bridge Driver IC

### **Pin Configuration**

| Pin            | Symbol | Function                      |  |  |  |  |

|----------------|--------|-------------------------------|--|--|--|--|

| 46             | ВН3    | Bootstrap High-side 3         |  |  |  |  |

| 47             | SH3    | Source High-side 3            |  |  |  |  |

| 48             | GH3    | Gate High-side 3              |  |  |  |  |

| 49             | SL3    | Source Low-side 3             |  |  |  |  |

| 50             | GL3    | Gate Low-side 3               |  |  |  |  |

| 51             | GND    | Ground                        |  |  |  |  |

| 52             | N.C.   | Not Connected                 |  |  |  |  |

| 53             | PFB3   | Phase Voltage Feedback 3      |  |  |  |  |

| 54             | PFB2   | Phase Voltage Feedback 2      |  |  |  |  |

| 55             | PFB1   | Phase Voltage Feedback 1      |  |  |  |  |

| 56             | ISN2   | Input Shunt Negative of CSA 2 |  |  |  |  |

| 57             | ISP2   | Input Shunt Positive of CSA 2 |  |  |  |  |

| 58             | VO2    | Voltage Output of CSA 2       |  |  |  |  |

| 59             | VRO    | Voltage Reference Output      |  |  |  |  |

| 60             | VO1    | Voltage Output of CSA 1       |  |  |  |  |

| 61             | ISP1   | Input Shunt Positive of CSA 1 |  |  |  |  |

| 62             | ISN1   | Input Shunt Negative of CSA 1 |  |  |  |  |

| 63             | AGND   | Analog Ground                 |  |  |  |  |

| 64             | ENA    | Enable                        |  |  |  |  |

| Cooling<br>Tab | GND    | Cooling Tab                   |  |  |  |  |

## **Bridge Driver IC**

#### **General Product Characteristics**

#### **General Product Characteristics** 3

#### 3.1 **Absolute Maximum Ratings**

#### Table 2 **Absolute Maximum Ratings**

$T_i = -40$ °C to +150°C; all voltages with respect to GND, positive current flowing into pin (unless otherwise specified)

| Parameter                              | Symbol               | Values |      |      | Unit | Note or Test                                | Number   |

|----------------------------------------|----------------------|--------|------|------|------|---------------------------------------------|----------|

|                                        |                      | Min.   | Тур. | Max. |      | Condition                                   |          |

| Power Supply                           | 1                    | II.    | 1    |      |      | 1                                           |          |

| Supply Voltage                         | V <sub>Vs1</sub>     | -0.3   | _    | 60   | V    | -                                           | P_4.1.1  |

| Supply Voltage for Power-up            | V <sub>Vs6</sub>     | _      | _    | 40   | V    | -                                           | P_4.1.7  |

| Supply Voltage                         | V <sub>Vs2</sub>     | -5     | _    | _    | V    | Reverse polarity $R_{VS} \ge 10 \Omega^{1}$ | P_4.1.2  |

| Voltage Range VDHP                     | V <sub>VDHP1</sub>   | -5     | _    | 85   | V    | 2)                                          | P_4.1.3  |

| Voltage Difference Vs-VDHP             | $V_{\rm dVsVDHP}$    | -85    | _    | 60   | V    | _                                           | P_4.1.5  |

| Voltage Range VDH1, VDH2, VDH3         | V <sub>VDHx1</sub>   | -5     | _    | 90   | V    | _                                           | P_4.1.6  |

| Voltage Difference Vs-VDH1, VDH2, VDH3 | $V_{ m dVsVDHx}$     | -90    | _    | 60   | V    | _                                           | P_4.1.8  |

| Voltage Range CL1                      | V <sub>CL1</sub>     | -0.3   | _    | 60   | V    | _                                           | P_4.1.9  |

| Voltage Range CH1                      | V <sub>CH1</sub>     | -0.3   | _    | 28   | V    | -                                           | P_4.1.10 |

| Voltage Range CB                       | $V_{CB}$             | -0.3   | _    | 28   | V    | _                                           | P_4.1.11 |

| Voltage Range CL2, CH2                 | V <sub>CHL2</sub>    | -0.3   | _    | 90   | V    | _                                           | P_4.1.12 |

| Voltage Difference CH2-CL2             | V <sub>dCH2CL2</sub> | -0.3   | _    | 28   | V    | _                                           | P_4.1.62 |

| Maximum Peak Pulse Current CB to CH2   | I <sub>CBCH2</sub>   | -      | _    | 1    | A    | t = 5 μs                                    | P_4.1.61 |

| Maximum Peak Pulse Current CB to BHx   | I <sub>CBBHx</sub>   | -      | -    | 1    | A    | t = 0.8 μs                                  | P_4.1.66 |

| Floating Driver Stages                 |                      |        | •    |      |      |                                             |          |

| Voltage Range SLx                      | V <sub>SLx1</sub>    | -7     | _    | 10   | V    | _                                           | P_4.1.13 |

| Voltage Range SLx                      | V <sub>SLx2</sub>    | -10    | _    | _    | V    | 5)                                          | P_4.1.14 |

| Voltage Range SLx                      | V <sub>SLx3</sub>    | -15    | _    | -    | V    | 3)                                          | P_4.1.15 |

| Voltage Range GLx                      | V <sub>GLx1</sub>    | -7     | _    | 28   | V    | -                                           | P_4.1.16 |

| Voltage Range GLx                      | V <sub>GLx2</sub>    | -10    | _    | _    | V    | 5)                                          | P_4.1.17 |

| Voltage Range GLx                      | V <sub>GLx3</sub>    | -15    | _    | _    | V    | 3)                                          | P_4.1.18 |

<sup>1</sup> Voltage drop via resistor has be to taken into account for applications operating at low battery voltage

<sup>2</sup> Minimum limit of -5 V valid only for a limited time frame

<sup>5</sup> For a duration of t\_on = 500ns; t\_on/t\_off = 1% per 20 kHz PWM frequency

<sup>3</sup> For a duration of t\_on = 250ns; t\_on/t\_off = 0.5% per 20 kHz PWM frequency

#### **Bridge Driver IC**

#### **General Product Characteristics**

#### **Absolute Maximum Ratings (continued)** Table 2

$T_i = -40$ °C to +150°C; all voltages with respect to GND, positive current flowing into pin (unless otherwise specified)

| Parameter                        | Symbol                 |      | Values |      | Unit | Note or Test<br>Condition                                      | Number   |

|----------------------------------|------------------------|------|--------|------|------|----------------------------------------------------------------|----------|

|                                  |                        | Min. | Тур.   | Max. | -    |                                                                |          |

| Voltage Range SHx                | V <sub>SHx1</sub>      | -7   | _      | 90   | V    | -                                                              | P_4.1.19 |

| Voltage Range SHx                | V <sub>SHx2</sub>      | -10  | _      | _    | V    | 5)                                                             | P_4.1.20 |

| Voltage Range SHx                | V <sub>SHx3</sub>      | -15  | _      | _    | V    | 3)                                                             | P_4.1.21 |

| Max. Voltage Transients at SHx   | V <sub>fSH_tr1</sub>   | _    | _      | 20   | V    | Slew rate ≤ 1 V/ns                                             | P_4.3.31 |

| Voltage Range GHx                | V <sub>GHx1</sub>      | -7   | _      | 90   | V    | -                                                              | P_4.1.22 |

| Voltage Range GHx                | V <sub>GHx2</sub>      | -10  | _      | _    | V    | 5)                                                             | P_4.1.23 |

| Voltage Range GHx                | V <sub>GHx3</sub>      | -15  | -      | _    | V    | 3)                                                             | P_4.1.24 |

| Voltage Range BHx                | $V_{BH}$               | -0.3 | _      | 90   | V    | -                                                              | P_4.1.25 |

| Voltage Difference Gxx-Sxx       | $V_{GS2}$              | -0.3 | _      | 28   | V    | 4)                                                             | P_4.1.26 |

| Voltage Difference BHx-SHx       | V <sub>BS2</sub>       | -0.3 | _      | 28   | V    | 4)                                                             | P_4.1.27 |

| Voltage Difference CB-SLx        | V <sub>CBSLx</sub>     | -0.3 | _      | 28   | V    | 4)                                                             | P_4.1.28 |

| Voltage Difference SHx-SLx       | V <sub>SSx1</sub>      | -12  | _      | 90   | V    | -                                                              | P_4.1.29 |

| Voltage Difference VDHP-SHx      | V <sub>dVDHPSHx2</sub> | -90  | _      | 90   | V    | -                                                              | P_4.1.32 |

| Voltage Difference VDHx-SHx      | V <sub>dVDHxSHx</sub>  | -90  | _      | 90   | V    | -                                                              | P_4.1.33 |

| Inputs and Outputs               |                        | •    | •      |      |      |                                                                |          |

| Voltage Range ĪHx, ILx, ENA      | V <sub>DIP1</sub>      | -0.3 | -      | 60   | V    | _                                                              | P_4.1.34 |

| Voltage Range VCC                | V <sub>VCC1</sub>      | -0.3 | -      | 60   | V    | -                                                              | P_4.1.35 |

| Voltage Range INH                | $V_{INH}$              | -0.3 | _      | 90   | V    | -                                                              | P_4.1.36 |

| Voltage Range SOFF               | V <sub>SOFF</sub>      | -0.3 | -      | 90   | V    | _                                                              | P_4.1.37 |

| Voltage Range PFBx, ERR          | V <sub>DOP1</sub>      | -0.3 | -      | 60   | V    | _                                                              | P_4.1.38 |

| Voltage Range APC                | V <sub>AOP1</sub>      | -0.3 | -      | 60   | V    | -                                                              | P_4.1.39 |

| SPI Interface                    |                        |      |        |      |      |                                                                |          |

| Voltage Range CLK_SPI, CSN, MOSI | V <sub>SPI1</sub>      | -0.3 | _      | 60   | V    | _                                                              | P_4.1.40 |

| Voltage Range MISO               | V <sub>SPI2</sub>      | -0.3 | _      | 60   | V    | -                                                              | P_4.1.41 |

| Shunt Signal Conditioning        |                        | •    | •      |      |      |                                                                |          |

| Voltage Range ISPx, ISNx         | V <sub>ISx1</sub>      | -3.0 | _      | 3.0  | V    | -                                                              | P_4.1.42 |

| Voltage Range ISPx, ISNx         | V <sub>ISx2</sub>      | -10  | -      | 10   | V    | $R_{\rm ISP} \ge 18 \Omega$<br>$R_{\rm ISN} \ge 18 \Omega^{5}$ | P_4.1.43 |

<sup>5</sup> For a duration of t\_on = 500ns; t\_on/t\_off = 1% per 20 kHz PWM frequency

<sup>3</sup> For a duration of t\_on = 250ns; t\_on/t\_off = 0.5% per 20 kHz PWM frequency

For a duration of  $t = 50 \mu s$  with 400 mA

#### **Bridge Driver IC**

#### **General Product Characteristics**

#### **Absolute Maximum Ratings (continued)** Table 2

$T_i = -40$ °C to +150°C; all voltages with respect to GND, positive current flowing into pin (unless otherwise specified)

| Parameter                                                                                | Symbol               |      | Values |      |    | Note or Test               | Number   |

|------------------------------------------------------------------------------------------|----------------------|------|--------|------|----|----------------------------|----------|

|                                                                                          |                      | Min. | Тур.   | Max. |    | Condition                  |          |

| Voltage Difference ISPx-ISNx                                                             | V <sub>dISx</sub>    | -5.0 | _      | 5.0  | V  | _                          | P_4.1.44 |

| Voltage Range VOx                                                                        | V <sub>VOx1</sub>    | -0.3 | _      | 3.0  | V  | _                          | P_4.1.45 |

| Voltage Range VOx                                                                        | V <sub>VOx3</sub>    | -0.3 | _      | 5.5  | V  | INH = High;<br>Vs supplied | P_4.1.46 |

| Voltage Range VOx                                                                        | V <sub>VOx2</sub>    | -0.3 | -      | 18   | V  | 1 kΩ in series             | P_4.1.47 |

| Current Range VOx                                                                        | I <sub>VOx</sub>     | -10  | _      | 18   | mA | _                          | P_4.1.48 |

| Voltage Range VRO                                                                        | V <sub>VRO1</sub>    | -0.3 | -      | 3    | V  | _                          | P_4.1.49 |

| Voltage Range VRO                                                                        | $V_{\rm VRO3}$       | -0.3 | _      | 5.5  | V  | INH = High;<br>Vs supplied | P_4.1.50 |

| Voltage Range VRO                                                                        | V <sub>VRO2</sub>    | -0.3 | -      | 18   | V  | 1 kΩ in series             | P_4.1.51 |

| Current Range VRO                                                                        | I <sub>VRO</sub>     | -10  | _      | 18   | mA | _                          | P_4.1.52 |

| GND                                                                                      |                      |      |        |      | •  |                            |          |

| Voltage Range CP_GND, AGND, GND, EPAD                                                    | V <sub>ISx</sub>     | -0.3 | _      | 0.3  | V  | -                          | P_4.1.53 |

| Temperatures                                                                             | ·                    | ·    | •      |      | •  |                            |          |

| Storage Temperature                                                                      | $T_{\rm stg}$        | -55  | -      | 150  | °C | _                          | P_4.1.54 |

| Junction Temperature                                                                     | $T_{J1}$             | -40  | -      | 150  | °C | _                          | P_4.1.55 |

| Junction Temperature                                                                     | $T_{J2}$             | -40  | _      | 175  | °C | 200 h over lifetime        | P_4.1.56 |

| ESD Susceptibility                                                                       |                      |      |        |      |    |                            |          |

| ESD Resistivity HBM all Pins excluded Pin SHx, BHx, GHx, CB, ISNx and ISPx <sup>6)</sup> | V <sub>ESDHBM1</sub> | -2   | _      | 2    | kV | -                          | P_4.1.57 |

| ESD Resistivity HBM all Pins excluded Pin CB, ISNx and ISPx <sup>6)</sup>                | V <sub>ESDHBM3</sub> | -1.5 | -      | 1.5  | kV | -                          | P_4.1.65 |

| ESD Resistivity HBM all Pins <sup>6)</sup>                                               | V <sub>ESDHBM2</sub> | -1   | _      | 1    | kV | -                          | P_4.1.58 |

| ESD Resistivity all Pins (charged device model) <sup>7)</sup>                            | V <sub>ESDCDM</sub>  | -    | -      | 500  | V  | -                          | P_4.1.59 |

| ESD Resistivity Corner Pins (charged device model) <sup>7)</sup>                         | V <sub>ESDCDMc</sub> | -    | -      | 750  | V  | -                          | P_4.1.60 |

<sup>6</sup> ESD robustness according to Human Body Model (HBM) ANSI/ESDA/JEDEC JS-001

<sup>7</sup> ESD robustness according to Charged Device Model (CDM) JESD22-C101

#### **Bridge Driver IC**

#### **General Product Characteristics**

#### Notes:

- 1. Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- Integrated protection functions are designed to prevent IC destruction under fault conditions described in 2. the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

#### **Bridge Driver IC**

#### **General Product Characteristics**

#### **Thermal Resistance** 3.2

Note: This thermal data was generated in accordance with JEDEC JESD51 standards. For more information,

go to www.jedec.org.

#### Table 3 **Thermal Resistance**

| Parameter                         | Symbol             |      | Values | ;    | Unit | Note or Test                                                                                                                                                                                                     | Number  |

|-----------------------------------|--------------------|------|--------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|                                   |                    | Min. | Тур.   | Max. |      | Condition                                                                                                                                                                                                        |         |

| Junction to Case <sup>8)</sup>    | R <sub>thJC</sub>  | -    | 5      | -    | K/W  | $V_{\rm VS} = V_{\rm VDH} = 14  \rm V;$<br>$T_{\rm a} = 85^{\circ} \rm C;  6  \rm FETs$<br>toggling:<br>$Q_{\rm gTOT} = 200  \rm nC;$<br>$f_{\rm PWM} = 20  \rm kHz;$<br>inhomogeneous<br>power distribution     | P_4.2.1 |

| Junction to Top <sup>8)</sup>     | R <sub>thJCT</sub> | -    | 18     | -    | K/W  | $V_{\rm VS} = V_{\rm VDH} = 14  \rm V;$<br>$T_a = 85^{\circ} \rm C;  6  FETs$<br>toggling:<br>$Q_{\rm gTOT} = 200  \rm nC;$<br>$f_{\rm PWM} = 20  \rm kHz;$<br>inhomogeneous<br>power distribution               | P_4.2.2 |

| Junction to Ambient <sup>8)</sup> | $R_{thJA}$         | -    | 28     | -    | K/W  | $V_{VS} = V_{VDH} = 14 \text{ V};$<br>$T_a = 85^{\circ}\text{C}; 6 \text{ FETs}$<br>toggling:<br>$Q_{gTOT} = 200 \text{ nC};$<br>$f_{PWM} = 20 \text{kHz};$<br>inhomogeneous<br>power distribution <sup>9)</sup> | P_4.2.3 |

<sup>8</sup> Not subject to production test, specified by design

Specified  $R_{\rm thJA}$  value is according to Jedec JESD51-2,-5,-7 at natural convection on FR4 2s2p board; The product (chip + package) was simulated on a 76.2 × 114.3 ×1.5 mm board with 2 inner copper layers (2 ×  $70 \, \mu m \, Cu$ ,  $2 \times 35 \, \mu m \, Cu$ ). Where applicable a thermal via array under the exposed pad contacted the first inner copper layer

# infineon

#### **General Product Characteristics**

### 3.3 Functional Range

#### Table 4 Functional Range

$T_j$  = -40°C to +150°C; all voltages with respect to GND, positive current flowing into pin (unless otherwise specified)

| Parameter                                                | Symbol            |                                   | Value | S                           | Unit |                                            | Number   |

|----------------------------------------------------------|-------------------|-----------------------------------|-------|-----------------------------|------|--------------------------------------------|----------|

|                                                          | Min. Typ. Max.    |                                   |       | Condition                   |      |                                            |          |

| Supply Voltage                                           | V <sub>Vs3</sub>  | 5.5                               | _     | 60                          | V    | Thermally limited                          | P_4.3.1  |

| Supply Voltage for Startup                               | V <sub>Vs4</sub>  | $V_{VsWU}$                        | -     | _                           | V    | Startup                                    | P_4.3.2  |

| Supply Voltage Reduced Operation Range Vs <sup>10)</sup> | V <sub>Vs5</sub>  | 3.0                               | -     | $V_{\rm VsROP}$             | V    | Logic operational;<br>I/Os turned off      | P_4.3.3  |

| Voltage Range VCC                                        | V <sub>VCC4</sub> | V <sub>VCCROP</sub>               | -     | $V_{VCCxOVx}$               | V    | -                                          | P_4.3.4  |

| Supply Voltage Reduced Operation Range VCC               | V <sub>VCC5</sub> | -0.3                              | -     | V <sub>VCCROP</sub>         | V    | Logic operational;<br>I/Os turned off      | P_4.3.5  |

| Voltage Range CB <sup>11)</sup>                          | $V_{fCB}$         | V <sub>CBUVSD</sub>               | -     | 15.0                        | V    | -                                          | P_4.3.6  |

| Voltage Difference CH1-CL1 <sup>11)</sup>                | V <sub>CP1</sub>  | V <sub>CBx</sub> - V <sub>s</sub> | -     | $V_{CBd}$                   | V    | INH = High; CP1 and CP2 operative          | P_4.3.7  |

| Voltage Difference CH2-CL2 <sup>11)</sup>                | V <sub>CP2</sub>  | -0.3                              | -     | $V_{CBd}$                   | V    | INH = High; CP1 and CP2 operative          | P_4.3.8  |

| Voltage Difference CH1-CL1 <sup>11)</sup>                | V <sub>CP1b</sub> | -0.3                              | _     | $V_{CBd}$                   | V    | INH = Low or CP1 off                       | P_3.3.2  |

| Voltage Difference CH2-CL2 <sup>11)</sup>                | V <sub>CP2b</sub> | -0.3                              | _     | $V_{CBd}$                   | V    | INH = Low or CP2 off                       | P_3.3.3  |

| Voltage Range VDHP, VDH1, VDH2, VDH3                     | V <sub>VDH3</sub> | 4.0                               | -     | $V_{\text{VDHOVSD}}$        | V    | PFBx- operational                          | P_4.3.27 |

| Voltage Range VDHP, VDH1, VDH2, VDH3                     | V <sub>VDH4</sub> | 2.0                               | _     | $V_{\rm VDHOVSD}$           | V    | VDHP readout-<br>operational               | P_4.3.28 |

| Voltage Range VDHP, VDH1, VDH2, VDH3                     | V <sub>VDH5</sub> | 0.0                               | -     | V <sub>VDHOVSD</sub>        | V    | CP2 and SCD-<br>operational <sup>12)</sup> | P_4.3.29 |

| Voltage Range SHx                                        | $V_{fSHx}$        | -V <sub>BHSHxx</sub>              | -     | 90V-<br>V <sub>BHSHxx</sub> | V    | -                                          | P_4.3.9  |

| Voltage Difference BHx-SHx                               | $V_{fBS1}$        | $V_{BSUV}$                        | _     | $V_{fCB}$                   | V    | Bootstrap charging                         | P_4.3.10 |

| Voltage Difference BHx-SHx                               | $V_{fBS2}$        | $V_{BSUV}$                        | _     | V <sub>BHSHxlim</sub>       | V    | CP2 charging                               | P_4.3.30 |

| Voltage Difference Gxx-Sxx                               | $V_{fGS1}$        | -0.3                              | _     | 15.0                        | V    | -                                          | P_4.3.11 |

| Duty Cycle Range Output Stages                           | D.C.              | 0                                 | _     | 100                         | %    | _                                          | P_4.3.12 |

| Voltage Range INH                                        | V <sub>AIP1</sub> | -0.3                              | _     | V <sub>VCCxOVx</sub>        | V    | -                                          | P_4.3.13 |

| Voltage Range SOFF                                       | V <sub>AIP2</sub> | -0.3                              | -     | $V_{VCCxOVx}$               | V    | _                                          | P_4.3.14 |

<sup>10</sup> Power-up to be completed first

Max. value will not be exceeded under normal operation condition, voltage class of charge pump capacitor can be selected accordingly

At minimum limit charge pumps are operational even if freewheeling current flows via the reverse diode of the external high-side FET

#### **Bridge Driver IC**

#### **General Product Characteristics**

#### **Functional Range (continued)** Table 4

$T_i = -40$ °C to +150°C; all voltages with respect to GND, positive current flowing into pin (unless otherwise specified)

| Parameter                                       | Symbol                |                                        | Values |                                          |    | Note or Test | Number   |

|-------------------------------------------------|-----------------------|----------------------------------------|--------|------------------------------------------|----|--------------|----------|

|                                                 |                       | Min.                                   | Тур.   | Max.                                     |    | Condition    |          |

| Voltage Range IHx, ILx, ENA, CLK_SPI, CSN, MOSI | V <sub>DIP2</sub>     | -0.3                                   | -      | $V_{\text{VCC} \times \text{OV} \times}$ | V  | -            | P_4.3.15 |

| Voltage Range PFBx, ERR, MISO                   | V <sub>DOP2</sub>     | V <sub>ERRL</sub><br>V <sub>SPIL</sub> | -      | V <sub>ERRHx</sub><br>V <sub>SPIHx</sub> | V  | -            | P_4.3.16 |

| Output Impedance PFBx, ERR                      | R <sub>DOP</sub>      | _                                      | 50     | _                                        | Ω  | -            | P_4.3.17 |

| Output Impedance MISO                           | R <sub>DOPMISO</sub>  | _                                      | 130    | _                                        | Ω  | _            | P_3.3.1  |

| Voltage Range APC                               | V <sub>AOP2</sub>     | -0.3                                   | _      | V <sub>AOPHx</sub>                       | V  | -            | P_4.3.18 |

| Current Range APC                               | I <sub>AOP2</sub>     | -1                                     | _      | 1                                        | mA | -            | P_4.3.19 |

| Input Voltage Range ISPx, ISNx                  | $V_{fISx}$            | V <sub>SSC_CM</sub>                    | _      | V <sub>SSC_CM</sub>                      | V  | -            | P_4.3.20 |

| Differential Voltage Range ISPx, ISNx           | V <sub>fdiffISx</sub> | V <sub>SSC_Idiff</sub>                 | -      | V <sub>SSC_Idiff</sub>                   | mV | -            | P_4.3.21 |

| Voltage Range VOx                               | $V_{fVOx}$            | V <sub>SSC_OVR</sub>                   | _      | V <sub>SSC_OVR</sub>                     | V  | _            | P_4.3.22 |

| Voltage Range VRO                               | $V_{fVRO}$            | V <sub>SSC_OVRO</sub>                  | _      | V <sub>SSC_OVRO</sub>                    | V  | _            | P_4.3.24 |

Note:

Within the functional or operating range, the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the Electrical Characteristics table.

## Input and Output Characteristics

### 4 Input and Output Characteristics

The input and output pins of the TLE9180D-31QK drive the output stages and give feedback to the  $\mu$ C about the state of the gate driver IC, the  $\mu$ C and the state of the inverter stage. Digital in- and outputs are supplied out of VCC and refer to the VCC voltage, general in- and outputs have fixed input threshold and fixed output high levels. Every output stage driving an external FET has its own input pin. Additionally there are 3 different pins to activate or deactivate the output stages. The impact of the 3 pins ENA,  $\overline{\text{INH}}$  and  $\overline{\text{SOFF}}$  differs from each other regarding to the gate driver IC's reaction. With the SPI interface the TLE9180D-31QK can be configured and diagnostics can be read out by the  $\mu$ C. The  $\overline{\text{ERR}}$  pin indicates a failure of the TLE9180D-31QK or the system.

Table 5 I/Os functionality

| Name of I/O | Definition     | Functionality                 | Default State                                                                   |

|-------------|----------------|-------------------------------|---------------------------------------------------------------------------------|

| ĪNH         | General Input  | Sleep Mode                    | Internal pull-down, FETs off passive clamping, Power up/down of device          |

| SOFF        | General Input  | Safe switch off               | Internal pull-down, FETs off without reset of error registers, SOFF mode        |

| ILx         | Digital Input  | Driver input for LS FETs      | Internal pull-down, Affected FET off                                            |

| ĪHx         | Digital Input  | Driver input for HS FETs      | Internal pull-up to VCC, Affected FET off                                       |

| ENA         | Digital Input  | Enable and Reset              | Internal pull-down, All FETs off                                                |

| CLK_SPI     | Digital Input  | SPI                           | Internal pull-down                                                              |

| MOSI        | Digital Input  | SPI                           | Internal pull-down                                                              |

| CSN         | Digital Input  | SPI                           | Internal pull-up to VCC                                                         |

| MISO        | Digital Output | SPI                           | Push-pull stage to VCC, Tri-state (Hi-Z) in case of no supply or if deactivated |

| PFBx        | Digital Output | Phase Feedback                | Push-pull stage to VCC with internal pull-down                                  |

| APC         | General Output | Driving Phase Cut Off Circuit | Push-pull stage to 5 V with internal pull-down                                  |

| ERR         | Digital Output | Diagnostic Output             | Push-pull stage to VCC with internal pull-down                                  |

#### Serial Peripheral Interface - SPI

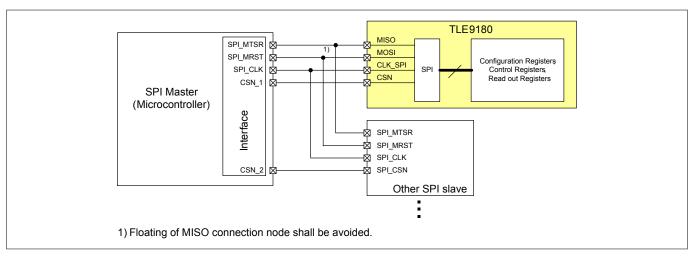

## **5** Serial Peripheral Interface - SPI

The 24-bit Serial Peripheral Interface (SPI) enables a communication link of the  $\mu$ C as SPI-master and the TLE9180D-31QK. The SPI interface is used to configure and to control the gate driver IC and to read out of the status registers.

The SPI interface in the TLE9180D-31QK is a SPI-Slave. It always requires a SPI-Master. This is usually a  $\mu$ C. The master generates the CLK\_SPI and CSN signals used for data transfer and its synchronization.

The SPI interface can operate in bus application mode with additional SPI-Slave devices. Daisy Chain is not possible, as incoming data is not passed directly to the output port. The transmission format of incoming and outcoming SPI frames differ.

Figure 3 Principle for SPI-Bus Architecture

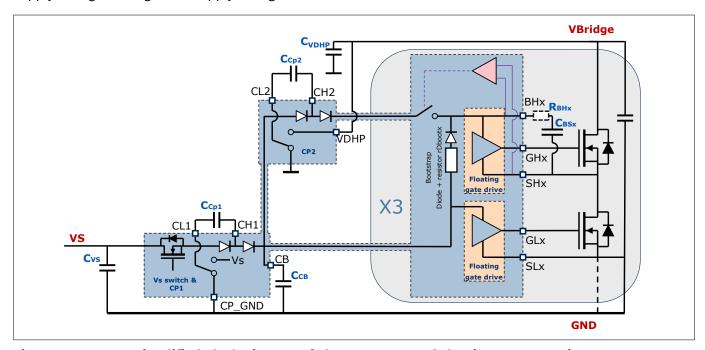

### 6 Power Supply

Power to the TLE9180D-31QK is supplied by pins Vs and VCC. The VCC supplies the digital I/O ports. All other supply voltages for the low- and high-side output stages, the digital and analog circuits and the gate voltage to drive the external MOSFETs are generated internally.

Additionally the TLE9180D-31QK is designed to operate with different supply voltages for the gate driver IC pin Vs and the power inverter stage at pin VDHP. Functional limitation of supply voltage differences between pin VDHP and the Vs supply is only their respective maximum ratings. Next to single supply systems typical environment is a boosted system for the power inverter while the gate driver is running with single battery supply voltage or a regulated supply voltage.

Figure 4 Simplified Block Diagram of Charge Pumps and Floating MOSFET Driver

## **Bridge Driver IC**

**Floating MOSFET Driver**

#### **Floating MOSFET Driver** 7

The TLE9180D-31QK provides 6 identical output stages to drive external N-channel MOSFETs in a brushless DC motor configuration. The driving signal for each FET given by the μC will be referenced to the source of every single FET by the integrated level shifters. The pins SLx/SHx are the reference for the floating gate driver output stages. A shoot through protection and dead time control is integrated into the logic. Violation of the input patterns and the correct conversion of the GND related input signal into floating signal by the level shifter will be monitored. Additionally the design and layout of the 6 internal signal paths for gate driving are integrated similar to each other to minimize switching and propagation delay time differences.

#### **Shunt Signal Conditioning**

## 8 Shunt Signal Conditioning

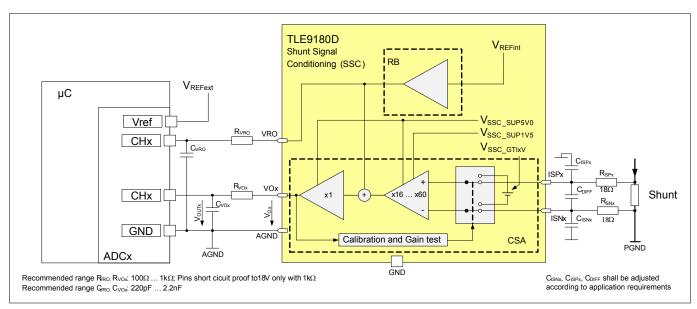

The shunt signal conditioning (SSC) incorporates 3 precise current sense amplifiers (CSAs) to amplify the voltage drop at the shunt resistors caused by the motor currents and a voltage reference output buffer (RB), see *Figure 5*.

The signal conditioning refers to GND. Due to high common mode input voltage range it is robust against sense voltage ringing caused by stray inductances during fast PWM current switching. Due to high common mode functional input voltage range it is robust against high common mode shifts between the GNDs of the shunts and the common GND of the ECU.

High equivalent input resistances, low input offset voltages and low gain error provide an excellent DC performance of the CSAs and therefore minimizes the total error of the shunt signal conditioning.

Additionally, high common mode rejection ratio, high power supply rejection ratio and a low noise figure of the CSAs contribute to minimize the total error of the SSC.

In order to optimize the shunt signal conditioning - especially in systems designed for a wide motor current range with high accuracy requirements at high and low motor currents - different gains can be programmed.

The DC output voltage at the outputs of the CSAs (VOx) for zero differential input voltage is defined by the output of the reference buffer at pin VRO. Therefore, positive and negative currents through the shunt resistor can be amplified by the CSAs and thus measured by the ADC of  $\mu$ C. Three different VRO voltages can be set at the reference buffer RB. Each of the three VRO voltage settings can be fine tuned.

Figure 5 Simplified Block- and Application Diagram of the Shunt Signal Conditioning

# TLE9180D-31QK Bridge Driver IC

**Protection and Diagnostics**

## 9 Protection and Diagnostics

The TLE9180D-31QK provides extended protection and monitoring functions. All detected errors and warnings can be read by SPI, most of the thresholds are selectable by SPI configuration or SPI command. Safety relevant diagnostics can be tested during operation in a dedicated self-test mode.

#### 9.1 Supervision Overview

The following diagnostics and read out functions are available.

Table 6 Diagnostic overview

| Diagnostic                                       | Availability in<br>Configuration | Availability in reduced operation | Availability with SOFF=low | Test of Diagnosis Function |

|--------------------------------------------------|----------------------------------|-----------------------------------|----------------------------|----------------------------|

| Power Supply Supervision a                       | and Diagnostics                  | ,                                 | '                          |                            |

| Overvoltage VS<br>(Programmable Threshold)       | yes (default value)              | no                                | yes                        | no                         |

| Overvoltage VS shutdown                          | yes                              | no                                | yes                        | no                         |

| Undervoltage VS<br>(Programmable Threshold)      | yes (default value)              | no                                | yes                        | no                         |

| VS Read Out                                      | yes                              | no                                | yes                        | no                         |

| Overvoltage VDHP<br>(Programmable Threshold)     | yes (default value)              | no                                | yes                        | no                         |

| Overvoltage LD VDHP                              | yes (default value)              | no                                | yes                        | no                         |

| Overvoltage VDHP<br>Shutdown                     | yes                              | no                                | yes                        | no                         |

| Undervoltage VDHP<br>(Programmable Threshold)    | yes (default value)              | no                                | yes                        | no                         |

| VDHP Read Out                                    | yes                              | no                                | yes                        | no                         |

| VCC Under- and Over<br>Monitoring                | yes                              | no                                | yes                        | yes                        |

| VCC Read Out                                     | yes                              | no                                | yes                        | no                         |

| Output Stage Power Supply                        | Supervision                      |                                   |                            | •                          |

| Undervoltage Charge Pump<br>CB Shutdown          | yes                              | no                                | yes                        | no                         |

| Undervoltage Charge Pump<br>CB (prog. threshold) | yes (default value)              | no                                | yes                        | no                         |

| CB Read Out                                      | yes                              | no                                | yes                        | no                         |

| Overvoltage Charge Pump 1                        | yes                              | no                                | yes                        | no                         |

| Overvoltage Charge Pump 2<br>CH2-CL2             | yes                              | no                                | yes                        | no                         |

| Overload Vs                                      | yes                              | no                                | yes                        | no                         |

| Overload Charge Pump 1                           | yes                              | no                                | yes                        | no                         |

### **Bridge Driver IC**

### **Protection and Diagnostics**

#### **Diagnostic overview (continued)** Table 6

| Diagnostic                                            | Availability in Configuration | Availability in reduced operation | Availability with SOFF=low | Test of<br>Diagnosis<br>Function |

|-------------------------------------------------------|-------------------------------|-----------------------------------|----------------------------|----------------------------------|

| Overload Charge Pump 2                                | yes                           | no                                | yes                        | no                               |

| Undervoltage High-side<br>Buffer Capacitor BHx-SHx    | yes                           | no                                | yes                        | no                               |

| Overvoltage High-side Buffer<br>Capacitor BHx-SHx     | yes                           | no                                | yes                        | no                               |

| Gate Driver Internal Superv                           | isions                        |                                   |                            |                                  |

| nternal Power Supply<br>Monitoring                    | yes                           | no                                | yes                        | no                               |

| Clock Supervision (internal clock)                    | yes                           | no                                | yes                        | no                               |

| Overtemperature Shutdown                              | yes                           | no                                | yes                        | no                               |

| Overtemperature Detection<br>(Programmable Threshold) | yes (default value)           | no                                | yes                        | no                               |

| Temperature Read out                                  | yes                           | no                                | yes                        | no                               |

| CSA Diagnostics                                       | no                            | no                                | no                         | n.a.                             |

| Output Stage Status<br>Feedback Information           | no                            | no                                | yes                        | no                               |

| Digital Driving Path<br>Monitoring                    | yes                           | no                                | yes                        | no                               |

| Latent Fault Warning<br>Monitoring                    | yes                           | no                                | yes                        | no                               |

| Bridge and FET Diagnostics                            | and Protection                |                                   |                            |                                  |

| Shoot Through Protection                              | n.a.                          | n.a.                              | n.a.                       | n.a.                             |

| SCD Failure                                           | no                            | no                                | no                         | yes                              |

| FET Drain Source Voltage<br>Read out                  | n.a.                          | n.a.                              | n.a.                       | n.a.                             |

| FET Reverse Diode Forward<br>Voltage Read out         | n.a.                          | n.a.                              | n.a.                       | n.a.                             |

| Overcurrent Detection                                 | yes                           | no                                | yes                        | no                               |

| Drain Source Measurement                              | no                            | no                                | no                         | n.a.                             |

| nterface to μC Supervision                            |                               |                                   |                            |                                  |

| nput Pattern Violation<br>Monitoring                  | n.a.                          | n.a.                              | n.a.                       | no                               |

| Overload Digital Output Pins                          | yes                           | no                                | yes                        | no                               |

| Configuration Signature<br>Invalid                    | yes                           | yes                               | yes                        | no                               |

### **Bridge Driver IC**

### **Protection and Diagnostics**

#### **Diagnostic overview (continued)** Table 6

| Diagnostic                       | Availability in Configuration | Availability in reduced operation | Availability with SOFF=low | Test of<br>Diagnosis<br>Function |

|----------------------------------|-------------------------------|-----------------------------------|----------------------------|----------------------------------|

| Configuration Time-out           | yes                           | no                                |                            | no                               |

| SPI Frame Error                  | yes                           | n.a.                              | yes                        | no                               |

| SPI Frame Time-out               | yes                           | n.a.                              | yes                        | no                               |

| SPI Window Watchdog Time-<br>out | no                            | no                                | yes                        | n.a.                             |

| CRC error (incoming data)        | yes                           | n.a.                              | yes                        | no                               |

| Invalid Address Access           | yes                           | n.a.                              | yes                        | no                               |

#### **Bridge Driver IC**

**Digital Phase Voltage Feedback**

#### **Digital Phase Voltage Feedback** 10

The TLE9180D-31QK incorporates a fast conversion of the phase voltages into logic level signals. Its threshold values are proportional to the voltage at pin VDHP as long as the VDHP voltage is below 60 V and stays above 4.0 V. The outputs are VCC push-pull stages with an internal pull down resistor. The phase voltage feedback is realized functional independent to the core logic. If the digital phase feedback is not used the output pins shall be open.

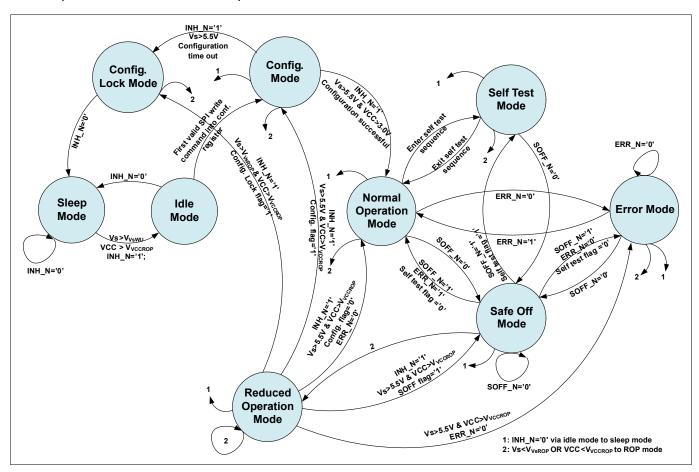

## 11 Operation Modes

This chapter describes the different operation modes.

Figure 6 Overview of Digital Operation Modes

#### **Application Information**

## 12 Application Information

In this application 3 phase motors, synchronous and asynchronous, are used, combining high output performance, low space requirements and high reliability.

Note: The following information is given as a hint for the implementation of the device only and shall not be regarded as a description or warranty of a certain functionality, condition or quality of the device.

Figure 7 Simplified Application Circuit

Note: This is a very simplified example of an application circuit. The function must be verified in the real application.

#### **Package Outlines**

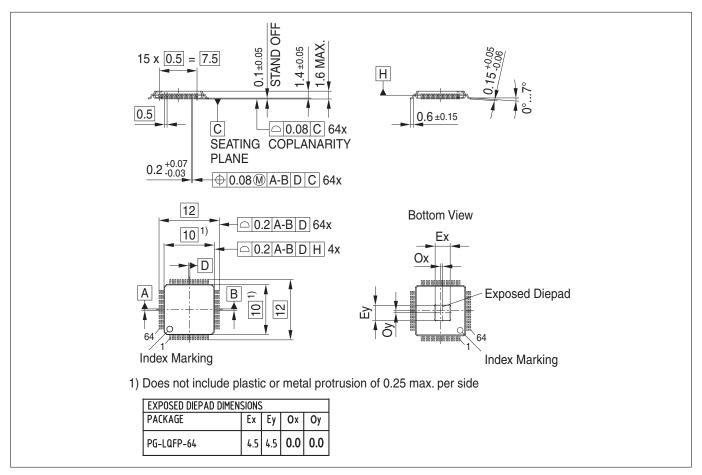

## 13 Package Outlines

Figure 8 PG-LQFP-64

#### **Green Product (RoHS compliant)**

To meet the world-wide customer requirements for environmentally friendly products and to be compliant with government regulations the device is available as a green product. Green products are RoHS-Compliant (i.e Pbfree finish on leads and suitable for Pb-free soldering according to IPC/JEDEC J-STD-020).

For further information on alternative packages, please visit our website: <a href="http://www.infineon.com/packages">http://www.infineon.com/packages</a>.

Dimensions in mm

### **Bridge Driver IC**

**Revision History**

## **Revision History**

| Revision | Date       | Changes                 |

|----------|------------|-------------------------|

| 1.0      | 2019-03-15 | Initial product summary |

#### **Trademarks**

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2019-03-15 **Published by Infineon Technologies AG** 81726 Munich, Germany

© 2019 Infineon Technologies AG. All Rights Reserved.

Visit us:

www.infineon.com

**Document reference** IFX-meu1487946927954 Z8F65076121

#### IMPORTANT NOTICE

THIS DOCUMENT IS FOR INFORMATION PURPOSES ONLY AND ANY INFORMATION GIVEN HEREIN SHALL IN NO EVENT BE REGARDED AS A WARRANTY, GUARAN-TEE OR DESCRIPTION OF ANY FUNCTIONALITY. CONDITIONS AND/OR QUALITY OF OUR PRODUCTS OR ANY SUITABILITY FOR A PARTICULAR PURPOSE.

WITH REGARD TO THE TECHNICAL SPECIFICATIONS OF OUR PRODUCTS, WE KINDLY ASK YOU TO EX-CLUSIVELY REFER TO THE RELEVANT PRODUCT DATA SHEETS PROVIDED BY US ON REQUEST. OUR CUSTOMERS AND THEIR TECHNICAL DEPARTMENTS ARE REQUIRED TO EVALUATE THE SUITABILITY OF OUR PRODUCTS FOR THE INTENDED APPLICATION. WE RESERVE THE RIGHT TO CHANGE THIS DOCUMENT

AND/OR THE INFORMATION GIVEN HEREIN AT ANY TIMF.

#### **Additional information**

For further information on technologies, our products, the application of our products, delivery terms and conditions and/or prices please contact your nearest Infineon Technologies office (www.infineon.com).

#### WARNINGS

Due to technical requirements, our products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by us in a written document signed by authorized representatives of Infineon Technologies, our products may not be used in any life endangering applications, including but not limited to medical, nuclear, military, life critical or any other applications where a failure of the product or any consequences of the use thereof can result in personal injury.