2.2 MHz Step-Down Regulator 500 mA, 5 V, low quiescent current

# Data Sheet

Rev. 1.0, 2013-06-19

# Automotive Power

## 2.2 MHz Step-Down Regulator 500 mA, 5 V Low quiescent current TLF50211EL

## TLF50211EL

1

## Overview

- 500 mA step down voltage regulator

- 5 V Output voltage

- ± 2% output voltage tolerance

- Low quiescent current (less than 45µA at nominal battery voltage)

- Integrated power transistor

- Current mode PWM regulation

- · PFM mode for light load current

- Input voltage range from 4.75V to 45V

- 2.2 MHz switching frequency

- 100% Duty cycle

- Synchronization input

- Very low shutdown current consumption (<2 μA)

- Soft-start function

- Input undervoltage lockout

- Suited for automotive applications: T<sub>i</sub> = -40 °C to +150 °C

- Green Product (RoHS compliant)

- AEC Qualified

PG-SSOP-14

#### Description

The TLF50211EL is a high frequency PWM step-down DC/DC converter with an integrated PMOS power switch, packaged in a small PG-SSOP-14 with exposed pad. The wide input voltage range from 4.75 to 45 V makes the TLF50211EL suitable for a wide variety of applications. The device is designed to be used under harsh automotive environmental conditions.

The switching frequency of nominal 2.2 MHz allows the use of small and cost-effective inductors and capacitors, resulting in a low, predictable output voltage ripple and in minimized consumption of board space.

In light load condition the device operates in Pulse Frequency Modulation (PFM) to optimize the efficiency. Between the single pulses, all internal controlling circuitry is switched off to reduce the internal power consumption.

| Туре       | Package    | Marking  |

|------------|------------|----------|

| TLF50211EL | PG-SSOP-14 | TLF50211 |

#### Overview

The TLF50211EL includes protection features such as a cycle-by-cycle current limitation, over-temperature shutdown and input under voltage lockout. The enable function, in shutdown mode with less than 2  $\mu$ A current consumption, enables easy power management in battery-powered systems.

The voltage regulation loop provides an excellent line and load regulation, the stability of the loop is ensured by an internal compensation network. This compensation network combined with a current mode regulation control guarantees a highly effective line transient rejection. During start-up the integrated soft-start limits the inrush current peak and prevents from an output voltage overshoot.

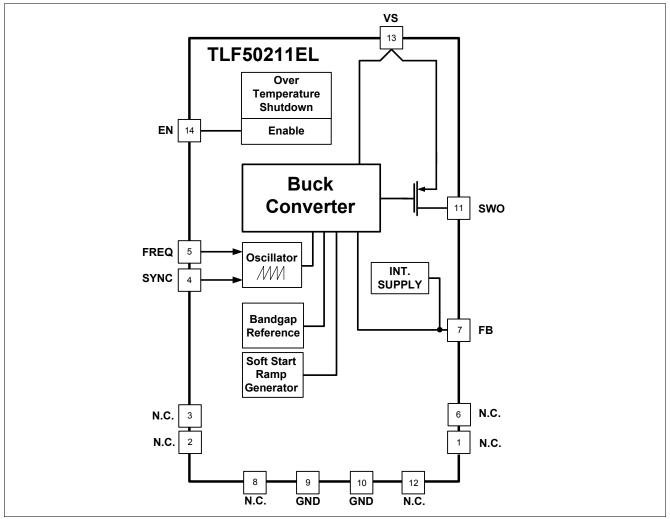

**Block Diagram**

# 2 Block Diagram

Figure 1 Block Diagram

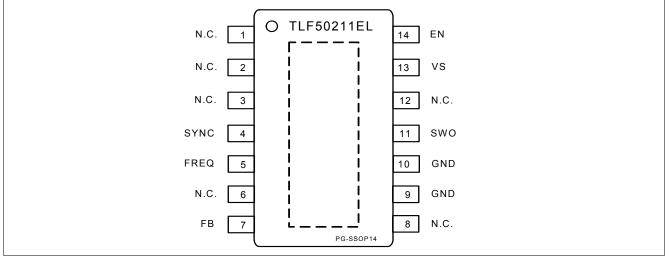

**Pin Configuration**

# 3 Pin Configuration

## 3.1 Pin Assignment

Figure 2 Pin Configuration

## 3.2 Pin Definitions and Functions

| Pin | Symbol | Function                                                                                                                                  |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | N.C.   | Not Connected.                                                                                                                            |

|     |        | Internally not connected. Leave open or connect to GND.                                                                                   |

| 2   | N.C.   | Not Connected.                                                                                                                            |

|     |        | Internally not connected. Leave open or connect to GND.                                                                                   |

| 3   | N.C.   | Not Connected.                                                                                                                            |

|     |        | Internally not connected. Leave open or connect to GND.                                                                                   |

| 4   | SYNC   | Synchronization Input                                                                                                                     |

|     |        | Connect to an external clock signal in order to synchronize/adjust the switching frequency. This feature is not functionally in PFM mode. |

| 5   | FREQ   | Frequency Adjustment Pin                                                                                                                  |

|     |        | Connect an external resistor to GND to adjust the switching frequency, do not leave open. In                                              |

|     |        | case the synchronization option is used, the resistor must be dimensioned close to the desired synchronization frequency.                 |

| 6   | N.C.   | Not Connected.                                                                                                                            |

|     |        | Internally not connected. Leave open or connect to GND.                                                                                   |

| 7   | FB     | Feedback Input                                                                                                                            |

|     |        | Connect this pin directly to the output capacitor. Also input for internal power supply. The internal                                     |

|     |        | power supply is taken from the output voltage.                                                                                            |

| 8   | N.C.   | Not Connected.                                                                                                                            |

|     |        | Internally not connected. Leave open or connect to GND.                                                                                   |

| 9   | GND    | Ground                                                                                                                                    |

| -   |        | Connect this pin directly with low inductive and broad trace to ground, do not leave open.                                                |

| 10  | GND    | Ground                                                                                                                                    |

|     |        | Connect this pin directly with low inductive and broad trace to ground, do not leave open.                                                |

## **Pin Configuration**

| Pin  | Symbol  | Function                                                                                                                                                        |

|------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11   | SWO     | <b>Buck Switch Output</b><br>Drain of the integrated power-PMOS transistor. Connect directly to the cathode of the catch diode and the buck circuit inductance. |

| 12   | N.C.    | Not Connected.<br>Internally not connected. Leave open or connect to GND.                                                                                       |

| 13   | VS      | Supply Voltage Input<br>Connect to supply voltage source.                                                                                                       |

| 14   | EN      | <b>Enable Input</b><br>Switch to high level to enable the device, switch to low level to disable the device.                                                    |

| Expo | sed Pad | Connect to heatsink area and GND by low inductance wiring.                                                                                                      |

## 4 General Product Characteristics

## 4.1 Absolute Maximum Ratings

### Absolute Maximum Ratings<sup>1)</sup>

$T_i$  = -40 °C to +150 °C; all voltages with respect to ground (unless otherwise specified)

| Pos.    | Parameter                          | Symbol            | Lim  | it Values             | Unit | Conditions                   |

|---------|------------------------------------|-------------------|------|-----------------------|------|------------------------------|

|         |                                    |                   | Min. | Max.                  |      |                              |

| Voltage | S                                  | k                 |      | <b>I</b>              |      |                              |

| 4.1.1   | Enable input                       | $V_{\sf EN}$      | -40  | 45                    | V    | -                            |

| 4.1.2   | Synchronization input              | V <sub>SYNC</sub> | -0.3 | 5.5                   | V    | -                            |

| 4.1.3   |                                    |                   |      | 6.2                   | V    | <i>t</i> < 10s <sup>2)</sup> |

| 4.1.4   | Feedback Input                     | V <sub>FB</sub>   | -0.3 | 5.5                   | V    | -                            |

| 4.1.5   |                                    |                   |      | 6.2                   | V    | $t < 10s^{2}$                |

| 4.1.6   | Frequency adjustment pin           | $V_{FREQ}$        | -0.3 | 5.5                   | V    | -                            |

| 4.1.7   |                                    |                   |      | 6.2                   | V    | <i>t</i> < 10s <sup>2)</sup> |

| 4.1.8   | Buck switch output                 | V <sub>SWO</sub>  | -2.0 | V <sub>VS</sub> + 0.3 | V    | -                            |

| 4.1.9   | Supply voltage input               | V <sub>VS</sub>   | -0.3 | 45                    | V    | -                            |

| Temper  | atures                             | ŧ                 | *    | +                     | -    | +                            |

| 4.1.10  | Junction temperature               | Tj                | -40  | 150                   | °C   | -                            |

| 4.1.11  | Storage temperature                | T <sub>stg</sub>  | -55  | 150                   | °C   | -                            |

| ESD Su  | sceptibility                       |                   |      |                       |      | ·                            |

| 4.1.12  | ESD resistivity                    | $V_{ESD}$         | -2   | 2                     | kV   | HBM                          |

| 4.1.13  | ESD resistivity to GND             | $V_{ESD}$         | -500 | 500                   | V    | CDM <sup>3)</sup>            |

| 4.1.14  | ESD resistivity corner pins to GND | V <sub>ESD</sub>  | -750 | 750                   | V    | CDM <sup>3)</sup>            |

1) Not subject to production test, specified by design

2) ESD susceptibility HBM according to ANSI/ESDA/JEDEC JS-001.

3) ESD susceptibility, Charged Device Model "CDM" EIA/JESD22-C101 or ESDA STM5.3.1

Note: Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note: Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

### **General Product Characteristics**

## 4.2 Functional Range

| Pos.  | Parameter            | Symbol             | Lin   | nit Values | Unit | Conditions      |

|-------|----------------------|--------------------|-------|------------|------|-----------------|

|       |                      |                    | Min.  | Max.       |      |                 |

| 4.2.1 | Supply voltage       | Vs                 | 4.75  | 45         | V    | -               |

| 4.2.2 | Buck inductor        | L <sub>BU</sub>    | 3.3   | 22         | μH   | -               |

| 4.2.3 | Buck capacitor       | $C_{BU1}$          | 10    | 50         | μF   | -               |

| 4.2.4 | Buck capacitor ESR   | ESR <sub>BU1</sub> | 0.015 | 0.100      | Ω    | - <sup>1)</sup> |

| 4.2.5 | Junction temperature | Ti                 | -40   | 150        | °C   | _               |

1) See section ""Application Information" on Page 22" for loop compensation requirements and refer to Application Note for dimensioning the output filter.

Note: Within the functional range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

### 4.3 Thermal Resistance

| Pos.  | Parameter                            | Symbol              | Limit Values |      |      | Unit | Conditions                 |

|-------|--------------------------------------|---------------------|--------------|------|------|------|----------------------------|

|       |                                      |                     | Min.         | Тур. | Max. |      |                            |

| 4.3.1 | Junction to case <sup>1)</sup>       | $R_{\mathrm{thJC}}$ | _            | 10   | _    | K/W  | -                          |

| 4.3.2 | Junction to ambient <sup>1) 2)</sup> | $R_{thJA}$          | _            | 47   | _    | K/W  | 2s2p                       |

| 4.3.3 |                                      | $R_{thJA}$          | -            | 54   | _    | K/W  | 1s0p + 600 mm <sup>2</sup> |

| 4.3.4 |                                      | $R_{thJA}$          | -            | 64   | -    | K/W  | 1s0p + 300 mm <sup>2</sup> |

1) Not subject to production test, specified by design.

2) Specified *R*<sub>thJA</sub> value is according to JEDEC 2s2p (JESD 51-7) + (JESD 51-5) and JEDEC 1s0p (JESD 51-3) + heatsink area at natural convection on FR4 board.

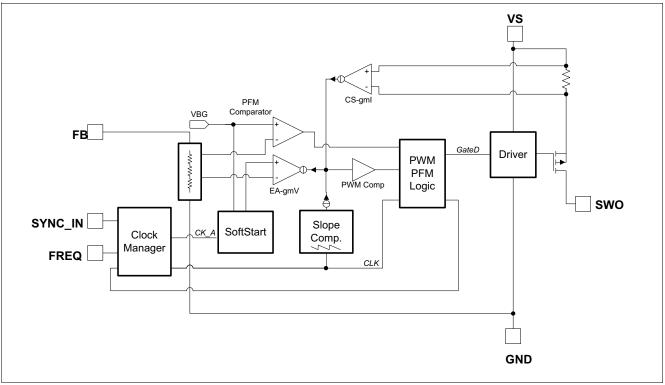

## 5 Buck Regulator

### 5.1 Description

The TLF50211EL is a monolithic current mode step down converter with adjustable switching frequency  $f_{OSC}$ . It is capable to operate either in Pulse Width Modulation (PWM) or in Pulse Frequency Modulation (PFM) Mode.

### 5.1.1 Regulator Loop

### Power stage:

The supply voltage is connected to pin VS. Between pin VS and pin SWO there is an internal shunt resistor and the internal PMOS power stage. The PMOS is driven by the driver stage.

### **Regulator Block:**

The feedback signal  $V_{FB}$  is connected to pin FB. Between pin FB and pin GND is an internal resistor divider. An error amplifier and a comparator are connected to this resistor divider: the error amplifier EA-gmV, which is controlling the output voltage in PWM mode, and the PFM comparator, which will switch the TLF50211EL into PFM mode and trigger the pulses. The error amplifier EA-gmV is connected to the PWM comparator. The regulation loop operates in current mode: the output current of EA-gmV is subtracted from the sum of the current loop CS-gmI and the slope compensation I<sub>SLOPE</sub>. The result is evaluated by PWM Comp (a current comparator). The output of PWM Comp defines duty cycle (pulse-width-modulated signal) in PWM mode.

The Slope Compensation added to the signal from the error amplifier EA-gmV to the PWM Comparator ensures that no sub harmonics will occur on the input current.

The PWM comparator output and the PFM comparator output are connected to the PWM /PFM logic.

An external resistor at pin FREQ is required to set the switching frequency (for details please refer to chapter 7 Module Oscillator). The TLF50211EL may also be synchronized to an external frequency. In this case an external clock signal should be connected to pin SYNC. The frequency setting resistor at pin FREQ is still necessary, it has to be selected according to the desired synchronization frequency (for details please refer to chapter 7 Oscillator).

The TLF50211EL can only be synchronized to an external frequency source in PWM mode, this function does not work in PFM mode.

The clock manager is clocking the PWM/PFM logic. The PWM/PFM logic is triggering the driver to apply pulses to the internal PMOS power stage.

### Safety Features:

The shunt resistor in line with the internal PMOS power stage (between pin VS and the power stage) is connected to a current sense amplifier CS-gml. It detects the voltage above the shunt resistor. The amplifier creates a signal which shuts the pulse down in case that the shunt voltage exceeds the reference limit. The current limitation acts as a cycle-by-cycle limitation. Cycle-by-cycle limitation means, that every pulse is switched off as soon as the current through the PMOS exceeds the buck peak over current limit  $I_{BUOC}$ . The next pulse starts and will also be switched off as soon as the current limit is exceeded again. This results in a lowered output voltage whilst the output current is limited to a certain value.

Input undervoltage shutdown: if the input voltage is below the input undervoltage shutdown threshold  $V_{S,off}$  the device will shut down.

Data Sheet

### **Buck Regulator**

Output overvoltage protection: If the output voltage exceeds the PFM threshold the device will switch from PWM to PFM. Pulses will then be generated only depending on the value of the output voltage  $V_{\rm CC}$ .

Soft start function: an integrated soft start function of duration  $t_{\text{start}}$  ensures, that the inrush current will be limited. After an over-temperature shutdown the regulator always restarts with a soft start.

Over-temperature shutdown: an internal temperature sensor detects the temperature of the device. It will be switched off if the junction temperature exceeds the over temperature shutdown threshold  $T_{j,sd}$  and restart with a certain hysteresis  $T_{i,sd}$  hyst (for details please refer to **Chapter 6, Enable and Thermal Shutdown**).

### **Biasing:**

The internal biasing is taken from pin VS as well as from pin FB (connected to  $V_{CC}$ ) (for details please refer to **Chapter 6, Enable and Thermal Shutdown**). Thus the power consumption from the supply voltage  $V_{S}$  can be minimized.

Figure 3 Block Diagram Buck Regulator

## 5.1.2 PWM (Pulse Width Modulation) Mode

Under normal conditions the TLF50211EL will operate with a constant switching frequency  $f_{OSC}$  in PWM mode. The ratio between switch-on-time  $T_{ON}$  and switch-off-time  $T_{OFF}$  is mainly determined by the ratio between the input voltage  $V_{S}$  and the output voltage  $V_{CC}$  and is influenced by the output current  $I_{CC}$ .

In PWM mode the device may operate with 100% duty cycle, in this case the internal PMOS is constantly conducting current. The current limitation feature is operating under this condition.

If the switch-on-time  $T_{\rm ON}$  should theoretically be below the minimum threshold  $T_{\rm ON,min}$  (due to low load or due to the ratio between input voltage  $V_{\rm S}$  and output voltage  $V_{\rm CC}$  depending on the switching frequency), it will be reduced to the minimum value switch-on-time  $T_{\rm ON,min}$  and stay there. As a consequence the output voltage  $V_{\rm CC}$  will increase. The PFM comparator detects the PFM threshold and will then switch the device into PFM mode. There is no possibility to disable the PFM function.

## 5.1.3 PFM (Pulse Frequency Modulation) Mode

To optimize the efficiency and to reduce the current consumption, the TLF50211EL automatically switches to PFM mode under low load conditions. In PFM mode the internal power stage including the driver stage is switched off and will only be switched on for applying pulses to charge the output capacitor. The pulses will be created by monitoring the voltage of the output filter capacitor  $C_{\rm OUT}$ . Thus in PFM mode the repetition time of pulses depend on the output current and/or the ratio between input voltage  $V_{\rm S}$  and output voltage  $V_{\rm CC}$ .

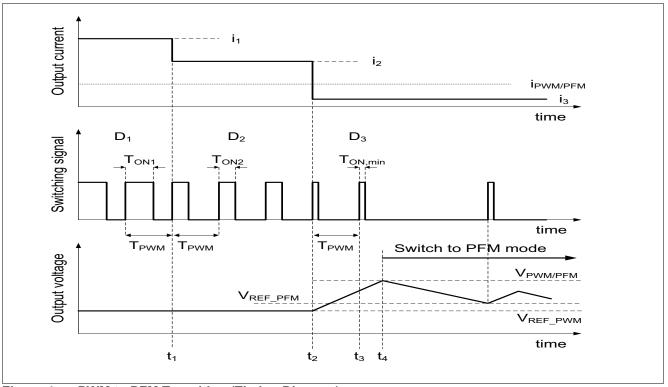

### Transition from PWM to PFM:

**Figure 4** is showing the transition from Pulse Width Modulation to Pulse Frequency Modulation under the assumption, that the input voltage  $V_{\rm S}$  will be constant and only the output current  $I_{\rm CC}$  will vary. The diagram shows the principle, in reality the signals might look slightly different. The diagram is without scale in respect of time, voltage and current values.

Starting from left of the figure a certain output current, here named  $i_1$ , is applied to the regulator output. This results in a duty cycle  $D_1$  with the on-time  $T_{ON1}$  of the internal power stage. The switching frequency  $f_{OSC}$  is constant as set by the frequency setting resistor  $R_{FREQ}$ . The regulator is in PWM mode, the output voltage is  $V_{REF_PWM}$  which is equal to  $V_{FB}$  in PWM mode.

At point  $t_1$  the output current decreases from  $i_1$  to a lower  $i_2$ . This results in a duty cycle  $D_2$  with the on-time  $T_{ON2}$  of the internal power stage. Due to the reduced output load the on-time  $T_{ON2}$  is shorter (the regulator is in Discontinuous Conduction Mode DCM) than  $T_{ON1}$ . The switching frequency  $f_{OSC}$  is constant as set by the frequency setting resistor  $R_{FREQ}$ . The regulator is still in PWM mode, the output voltage is  $V_{REF_PWM}$  which is equal to  $V_{FB}$  in PWM mode. In Continuous Conduction Mode CCM the variation from  $T_{ON1}$  to  $T_{ON2}$  will be very small due to smaller conduction losses.

At point  $t_2$  the output current decreases again from  $i_2$  to a lower  $i_3$ . As a consequence the on-time  $T_{ON}$  will be reduced also. The output current  $i_3$  is so low, that the on-time  $T_{ON3}$  would be smaller than the  $T_{ON,min}$ . The regulator does not allow a on-time smaller than  $T_{ON,min}$ . Therefore we can say that the output current  $i_3$  is under the imaginary current threshold for transition from PWM to PFM  $i_{PWM/PFM}$ . With the pulse staying at on-time  $T_{ON,min}$  the output voltage  $V_{CC}$  will rise. The regulator is still in PWM mode, but the output voltage rises.

At point  $t_3$  after a normal time period  $T_{PWM}$  as adjusted by the frequency setting resistor  $R_{FREQ}$ , a further pulse of the duration  $T_{ON,min}$  is applied, the output voltage  $V_{CC}$  keeps on rising. The regulator is still in PWM mode.

At point  $t_4$  the output voltage  $V_{CC}$  touches (or exceeds) the voltage threshold for transition from PWM to PFM  $V_{PWM/PFM}$ . The regulator is now switching internally from PWM to PFM. In PFM mode the power consumption of the internal blocks is reduced. The reference for the output voltage  $V_{CC}$  is switched from  $V_{REF_PWM}$  (which is equal to  $V_{FB}$  in PWM mode) to  $V_{REF_PFM}$  (which is equal to  $V_{FB}$  in PFM mode). The reference for  $\overline{V}_{FB}$  in PFM mode is higher than the reference in PWM mode to avoid voltage dumps at the output voltage  $V_{CC}$  due to sudden load steps and to give the regulator more reaction time to switch back to PWM mode.

The regulator is now in PFM mode, the output voltage is  $V_{\text{REF}_{PFM}}$  which is equal to  $V_{FB}$  (or slightly higher) in PFM mode.

The output voltage  $V_{\rm CC}$  is monitored and as soon as it touches the PFM reference voltage  $V_{\rm REF\_PFM}$  a pulse of the on-time  $T_{\rm ON,min}$  is triggered. The time between two pulses is depending on the discharging of the output capacitor  $C_{\rm OUT}$ .

Figure 4 PWM to PFM Transition (Timing Diagram)

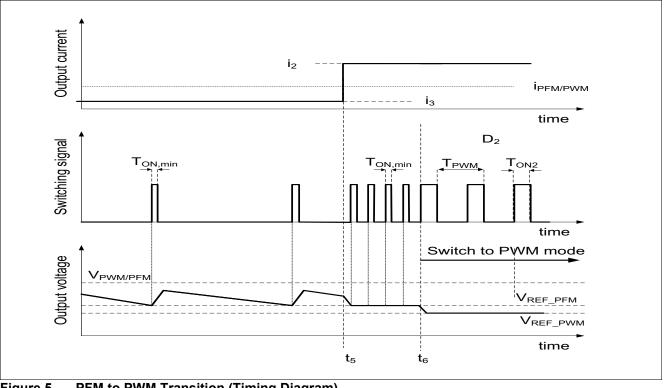

### Transition from PFM to PWM:

Figure 5 is showing the transition from Pulse Frequency Modulation to Pulse Width Modulation under the assumption, that the input voltage  $V_{\rm S}$  will be constant, and only the output current  $I_{\rm cc}$  will vary. The diagram shows the principle, in reality the signals might look slightly different. The diagram is without scale in respect of time, voltage and current values.

Starting from left of the figure a certain output current, here named  $i_3$ , is applied to the regulator output.  $i_3$  shall be below the imaginary current threshold for transition from PFM to PWM *i*<sub>PFM/PWM</sub>. The regulator is in PFM mode, the output voltage is  $V_{\text{REF PFM}}$ , which is equal to  $V_{\text{FB}}$  in PFM mode (or slightly higher).

Pulses of the duration  $T_{ON,min}$  are triggered whenever the output voltage  $V_{CC}$  touches the PFM reference voltage V<sub>REF PFM</sub>.

At point  $t_5$  the output current increases from  $i_3$  to a higher  $i_2$ , that shall be above the imaginary current threshold for transition from PFM to PWM  $i_{PFM/PWM}$ . Due to the higher output current more pulses of the duration  $T_{ON,min}$  have to be triggered, the frequency of these pulses is monitored. The frequency of these pulses increases until it is higher than the switching frequency  $f_{OSC}$  set by the frequency setting resistor  $R_{FREO}$ . The regulator is still in PFM mode

At point  $t_6$  the frequency monitoring detects that the frequency of the PFM pulses is being higher than the frequency threshold for transition from PFM to PWM  $f_{\rm PFM/PWM}$ . Therefore the regulator switches back to PWM mode. This results in a certain duty cycle  $D_2$  with the on-time  $T_{ON2}$  of the internal power stage. The time period  $T_{\rm PWM}$  is as adjusted by the frequency setting resistor  $R_{\rm FREQ}$ .

PFM to PWM Transition (Timing Diagram) Figure 5

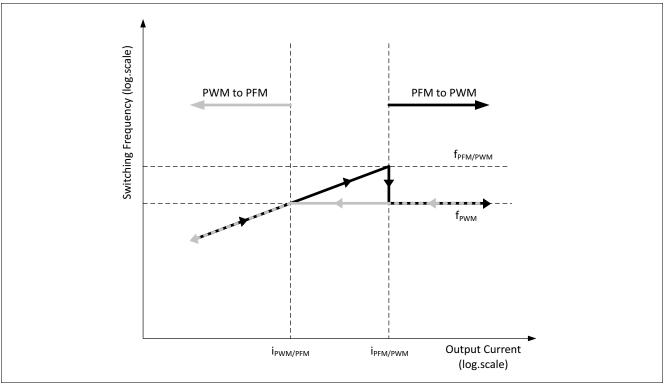

### Frequency Variation during PWM/PFM Transition:

**Figure 6** is showing the transition from Pulse Frequency Modulation to Pulse Width Modulation (and vice versa) in relation to output current and switching frequency. The diagram shows the principle, in reality the signals might be slightly different. The diagram is without scale in respect of frequency and current values.

The transition from PWM to PFM is shown in a grey line. Starting from right the switching frequency  $f_{PWM}$  is constant as set by the frequency setting resistor  $R_{FREQ}$ . The output current  $I_{cc}$  is decreasing.

As soon as the output current  $I_{cc}$  is below the imaginary current threshold for transition from PWM to PFM  $i_{PWM/PFM}$ , the regulator will be switched from PWM to PFM mode depending on the output voltage  $V_{cc}$ . With the output current  $I_{cc}$  decreasing, the switching frequency will also decrease, as the pulses are triggered by monitoring the output voltage  $V_{cc}$  at capacitor  $C_{out}$ .

The transition from PFM to PWM is shown in a black line. Starting from left the switching frequency is increasing with the increasing output current  $I_{cc}$ .

As soon as the switching frequency is crossing the frequency threshold for transition from PFM to PWM  $f_{\text{PFM/PWM}}$  (which is above the switching frequency  $f_{\text{OSC}}$  set by the frequency setting resistor  $R_{\text{FREQ}}$ ) the regulator will switch from PFM to PWM.

Figure 6 PWM <-> PFM Transitions

## 5.2 Electrical Characteristics

### **Electrical Characteristics: Buck Regulator**

$V_{\rm S}$  = 6.0 V to 40 V,  $T_{\rm j}$  = -40 °C to +150 °C, all voltages with respect to ground (unless otherwise specified)

| Pos.   | Parameter                                           | Symbol                        | Limit Values |      |      | Unit  | Conditions                                             |  |

|--------|-----------------------------------------------------|-------------------------------|--------------|------|------|-------|--------------------------------------------------------|--|

|        |                                                     |                               | Min.         | Тур. | Max. |       |                                                        |  |

| 5.2.1  | Output voltage                                      | V <sub>FB</sub>               | 4.90         | 5.00 | 5.10 | V     | V <sub>EN</sub> = 5.0V                                 |  |

|        |                                                     |                               |              |      |      |       | 7 V < V <sub>S</sub> < 12V                             |  |

|        |                                                     |                               |              |      |      |       | 100 mA < <i>I</i> <sub>CC</sub> < 610 mA<br>PWM Mode   |  |

| 5.2.2  | Output voltage                                      | $V_{FB}$                      | 4.90         | 5.10 | 5.30 | V     | V <sub>EN</sub> = 5.0V                                 |  |

|        |                                                     |                               |              |      |      |       | 10V < V <sub>S</sub> < 35V                             |  |

|        |                                                     |                               |              |      |      |       | I <sub>CC</sub> = 100 μA                               |  |

|        |                                                     |                               |              |      |      |       | PFM Mode                                               |  |

| 5.2.3  | Power stage on-resistance                           | R <sub>on</sub>               | -            | 1.5  | 2.3  | Ω     | tested at 100 mA,                                      |  |

|        |                                                     |                               |              |      |      |       | V <sub>S</sub> = 7.0V                                  |  |

| 5.2.4  | Buck peak over current limit                        | I <sub>BUOC</sub>             | 0.85         | -    | 1.7  | А     | -                                                      |  |

| 5.2.5  | Current transition rise/fall time                   | t <sub>R</sub>                | -            | 100  | _    | mA/ns | 1)                                                     |  |

| 5.2.6  | Maximum duty cycle                                  | $D_{\max}$                    | -            | -    | 100  | %     | 2)                                                     |  |

| 5.2.7  | Minimum switch on-time                              | $T_{\rm ON,min}$              | -            | 100  | -    | ns    | 1)                                                     |  |

| 5.2.8  | Minimum switch off- Time                            | $T_{\rm OFF,min}$             | -            | 200  | -    | ns    | <sup>1)</sup> PFM mode                                 |  |

| 5.2.9  | Soft start ramp                                     | t <sub>start</sub>            | 300          | 450  | 750  | μs    | $V_{\rm FB}$ rising from 5% to 95% of $V_{\rm FB,nom}$ |  |

| 5.2.10 | Input under voltage shutdown threshold              | V <sub>S,off</sub>            | 3.75         | -    | -    | V     | $V_{\rm S}$ decreasing                                 |  |

| 5.2.11 | Input voltage startup threshold                     | V <sub>S,on</sub>             | -            | _    | 4.75 | V     | $V_{\rm S}$ increasing                                 |  |

| 5.2.12 | Input under voltage shutdown hysteresis             | $V_{\rm S,hyst}$              | 130          | 300  | -    | mV    | -                                                      |  |

| 5.2.13 | Voltage threshold for transition<br>from PWM to PFM | $V_{\rm PWM/PFM}$             | -            | -    | 5.3  | V     | 1)                                                     |  |

| 5.2.14 | Frequency ratio for transition from PFM to PWM      | $f_{\rm PFM/PWM}/f_{\rm osc}$ | -            | 1.20 | -    | -     | 1)                                                     |  |

1) Specified by design. Not subject to production test.

2) Consider "Chapter 4.2, Functional Range".

## 5.3 Performance Graphs

### **Typical Performance Characteristics**

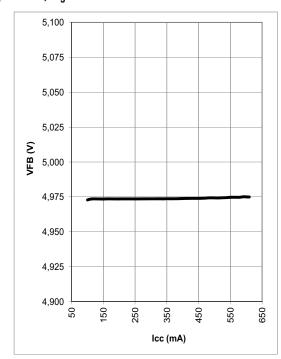

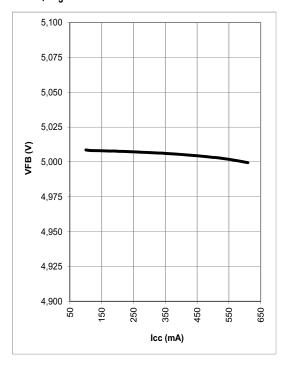

# Load Regulation PWM Mode $V_{\rm S}$ = 12 V; $T_{\rm J}$ = - 43 °C

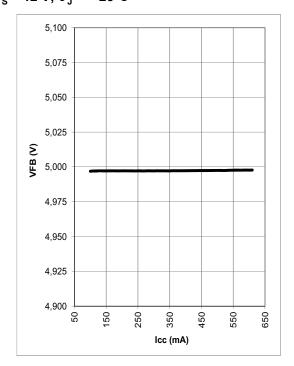

# Load Regulation PWM Mode $V_{\rm S}$ = 12 V; $T_{\rm J}$ = + 150°C

Load Regulation PWM Mode  $V_{\rm S}$  = 12 V;  $T_{\rm J}$  = + 25°C

Data Sheet

Downloaded from Arrow.com.

### **Typical Performance Characteristics**

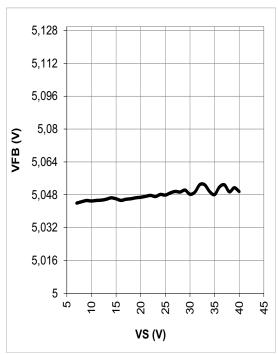

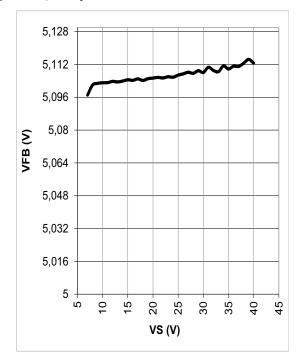

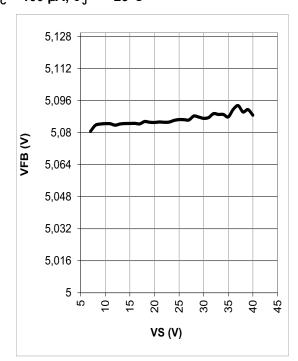

# Line Regulation PFM Mode $I_{CC}$ = 100 µA; $T_{J}$ = - 43°C

Line Regulation PFM Mode  $I_{CC}$  = 100 µA;  $T_{J}$  = + 150°C

Line Regulation PFM Mode  $I_{\rm CC}$  = 100 µA;  $T_{\rm J}$  = + 25°C

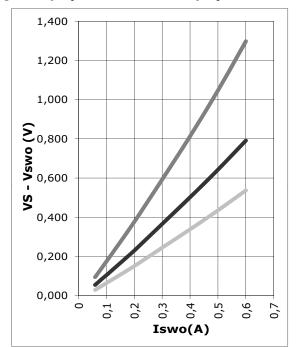

Power Stage On Resistance: Black  $T_J$  = + 25°C Light Grey  $T_J$  = - 43 °C, Dark Grey  $T_J$  = + 150 °C

Data Sheet

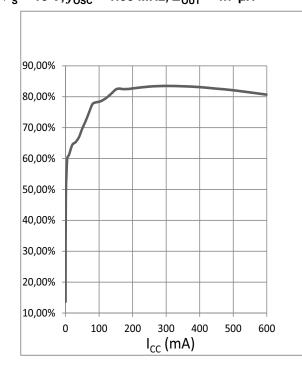

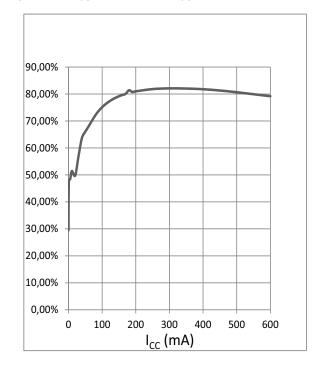

Efficiency for

$V_{\rm S} =$  13 V,  $f_{\rm OSC}$  = 1.65 MHz,  $L_{\rm OUT}$  = 4.7  $\mu$ H

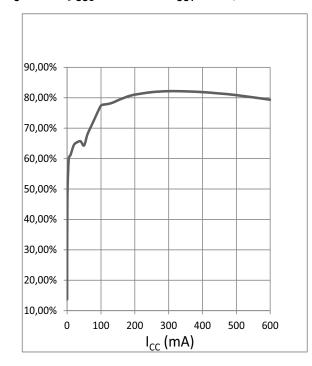

Efficiency for

$V_{\rm S}$  = 13 V,  $f_{\rm OSC}$  = 2.2 MHz,  $L_{\rm OUT}$  = 4.7  $\mu$ H

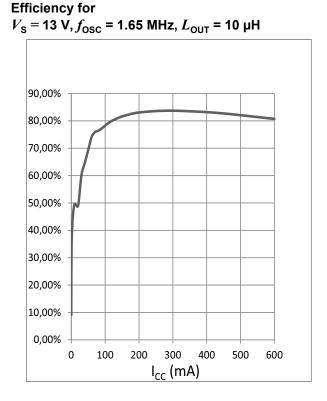

Efficiency for  $V_{\rm S}$  = 13 V,  $f_{\rm OSC}$  = 2.2 MHz,  $L_{\rm OUT}$  = 10 µH

### **Enable and Thermal Shutdown**

# 6 Enable and Thermal Shutdown

## 6.1 Description

A valid high level at pin EN ( $V_{\text{EN,hi}}$ ) turns the regulator on, a valid low level at pin EN ( $V_{\text{EN,lo}}$ ) turns the regulator off. In off state the current consumption of the device is less than 2µA. An integrated pull down resistor at pin EN ( $R_{\text{EN,INT}}$ ) ensures, that the device is switched off, if pin EN is left open.

The integrated thermal shutdown function turns off the power switch in case of overtemperature. The typ. junction shutdown temperature is 175°C, with a min. of 155°C. After cooling down, the IC will automatically restart with a soft start into normal operation. The thermal shutdown is an integrated protection function designed to prevent IC destruction when operating under fault conditions. It should not be used for normal operation.

## 6.2 Electrical Characteristics Module Enable, Bias and Thermal Shutdown

| Pos.     | Parameter                            | Symbol                 | Limit Values |      |      | Unit | Conditions                                                                                          |  |

|----------|--------------------------------------|------------------------|--------------|------|------|------|-----------------------------------------------------------------------------------------------------|--|

|          |                                      |                        | Min.         | Тур. | Max. |      |                                                                                                     |  |

| Enable   | EN                                   | 1                      | 1            |      |      |      |                                                                                                     |  |

| 6.2.1    | Current consumption, shut down mode  | $I_{\rm q,OFF}$        | -            | 0.1  | 2    | μA   | $V_{\rm EN}$ = 0V;<br>$T_{\rm j}$ < 105°C; $V_{\rm S}$ = 16V                                        |  |

| 6.2.2    | Current consumption of $V_{\rm CC}$  | $I_{q,ON,V\_CC}$       | _            | -    | 60   | μA   | $V_{\rm EN}$ = 5.0V; $V_{\rm S}$ = 16V;<br>$V_{\rm CC}$ = 5.4V;<br>$T_{\rm j}$ < 105°C;<br>PFM mode |  |

| 6.2.3    | Current consumption of $V_{\rm S}$   | $I_{q,ON,V\_S}$        | _            | 15   | 20   | μA   | $V_{\rm EN}$ = 5.0V; $V_{\rm S}$ = 16V;<br>$V_{\rm CC}$ = 5.4V;<br>$T_{\rm j}$ < 105°C;<br>PFM mode |  |

| 6.2.4    | Enable high signal valid             | $V_{\rm EN,hi}$        | 3.0          | _    | _    | V    | -                                                                                                   |  |

| 6.2.5    | Enable low signal valid              | $V_{\rm EN,lo}$        | -            | _    | 0.8  | V    | -                                                                                                   |  |

| 6.2.6    | Enable hysteresis                    | V <sub>EN,HY</sub>     | 50           | 200  | 400  | mV   | -                                                                                                   |  |

| 6.2.7    | Enable high input current            | $I_{\rm EN,hi}$        | _            | -    | 3    | μA   | V <sub>EN</sub> = 16V                                                                               |  |

| 6.2.8    | Enable low input current             | $I_{\rm EN,lo}$        | _            | 0.1  | 1    | μA   | V <sub>EN</sub> = 0.5V                                                                              |  |

| 6.2.9    | Enable, internal resistor to GND     | R <sub>EN,INT</sub>    | 7            | 12   | 20   | ΜΩ   | <i>V</i> <sub>EN</sub> = 3V                                                                         |  |

| Internal | Over Temperature Protection          | on                     | ļ            |      |      |      | _ !                                                                                                 |  |

| 6.2.10   | Over temperature shutdown            | $T_{j,sd}$             | 155          | 175  | 195  | °C   | 1)                                                                                                  |  |

| 6.2.11   | Over temperature shutdown hysteresis | T <sub>j,sd_hyst</sub> | -            | 15   | -    | К    | 1)                                                                                                  |  |

### Electrical Characteristics: Enable, Bias and Thermal Shutdown

$V_{\rm S}$  = 6.0 V to 40 V,  $T_{\rm i}$  = -40 °C to +150 °C, all voltages with respect to ground (unless otherwise specified)

1) Specified by design. Not subject to production test.

Oscillator

## 7 Oscillator

### 7.1 Description

The oscillator supplies the device with a constant frequency. The power switch will be switched on and off with a constant frequency  $f_{\text{OSC}}$ . The time period  $T_{\text{PWM}}$  is derived from this frequency and some safety functions are synchronized to this frequency.

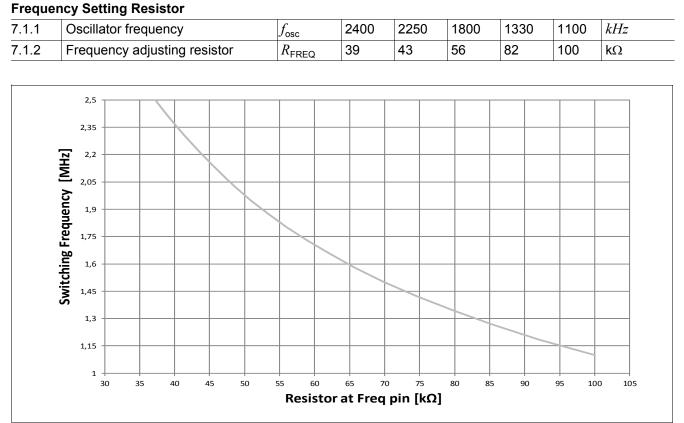

The oscillator frequency can be set by connecting an external resistor  $R_{FREQ}$  between pin FREQ and GND using the following table (selected values, for more precise setting please refer to **Figure 7** below).

Figure 7 Switching Frequency  $f_{OSC}$  versus Frequency setting Resistor  $R_{FREQ}$ .

The turn-on frequency can optionally be set externally via the SYNC pin. In this case the synchronization of the PWM-on signal refers to the falling edge of the SYNC-pin input signal. In case the synchronization to an external clock signal is not needed, the SYNC pin should be connected to ground. The frequency setting resistor  $R_{FREQ}$  is also necessary for SYNC option and must be dimensioned according to the desired synchronization frequency (the ratio between synchronization and internal frequency has to be less than or equal to 1).

The synchronization function is not available in PFM mode.

Data Sheet

Oscillator

## 7.2 Electrical Characteristics Module Oscillator

### **Electrical Characteristics: Module Oscillator**

$V_{\rm S}$  = 6.0 V to 40 V,  $T_{\rm j}$  = -40 °C to +150 °C, all voltages with respect to ground (unless otherwise specified)

| Pos.   | Parameter                     | Symbol                   | Limit Values |      |      | Unit | Conditions                                                       |

|--------|-------------------------------|--------------------------|--------------|------|------|------|------------------------------------------------------------------|

|        |                               |                          | Min.         | Тур. | Max. |      |                                                                  |

| Freque | ency Setting FREQ             | <del> </del>             |              | -+   |      |      |                                                                  |

| 7.2.1  | Oscillator frequency spread   | $f_{\sf osc}$            | 2025         | 2250 | 2475 | kHz  | $V_{\text{SYNC}} = 0V;$<br>$R_{\text{FREQ}} = 43 \text{k}\Omega$ |

| Synch  | ronization SYNC               | <u>1</u>                 | <u> </u>     |      |      |      | - L                                                              |

| 7.2.2  | Synchronization capture range | $f_{\sf sync}$           | 1500         | -    | 2200 | kHz  | -                                                                |

| 7.2.3  | SYNC signal high level valid  | V <sub>SYNC,H</sub>      | 2.9          | -    | -    | V    | 1)                                                               |

| 7.2.4  | SYNC signal low level valid   | $V_{\rm SYNC,L}$         | -            | -    | 0.8  | V    | 1)                                                               |

| 7.2.5  | SYNC input internal pull-down | R <sub>SYNC,INT</sub>    | 0.15         | 0.25 | 0.40 | MΩ   | $V_{\rm SYNC}$ = 5V                                              |

| 7.2.6  | SYNC signal minimum high time | t <sub>SYNC,H, min</sub> | 25           | -    | -    | ns   | -                                                                |

| 7.2.7  | SYNC signal minimum low time  |                          |              | -    | -    | ns   | -                                                                |

|        |                               |                          |              |      |      |      |                                                                  |

1) Synchronization of PWM-on signal to falling edge.

### **Application Information**

## 8 Application Information

Note: The following information is given as a hint for the implementation of the device only and shall not be regarded as a description or warranty of a certain functionality, condition or quality of the device.

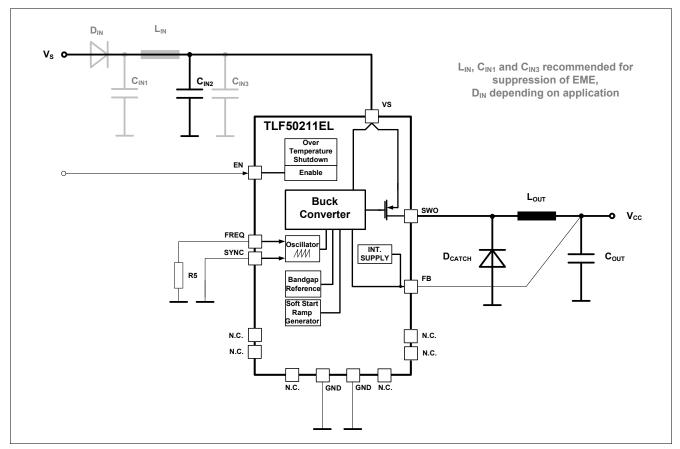

### Figure 8 Application Diagram

Note: This is a very simplified example of an application circuit. The function must be verified in the real application

| Part-No.           | Value     | Туре             | Manufacturer            | Remark                          |

|--------------------|-----------|------------------|-------------------------|---------------------------------|

| C <sub>IN2</sub>   | 47µF/50V  | electrolytic     | AVX                     |                                 |

| C <sub>IN3</sub>   | 100nF/50V | ceramic          | AVX                     | For improving EME               |

| C <sub>OUT</sub>   | 10µF/25V  | ceramic          | AVX                     |                                 |

| D <sub>CATCH</sub> | 1A/100V   | 10BQ100 Schottky | International Rectifier | 1 A current capability          |

| L <sub>OUT</sub>   | 10µH      | MSS1278T         | Coilcraft               | 4.7 µH also possible            |

| -                  | -         | -                | -                       |                                 |

| -                  | -         | -                | -                       |                                 |

| -                  | -         | -                | -                       |                                 |

| -                  | -         | -                | -                       |                                 |

| R5                 | 43 kΩ     | 0.25 W           | Panasonic               | f <sub>OSC</sub> set to 2.2 MHz |

Figure 9 Bill of Material for Application Diagram

### **Application Information**

## 8.1 General Layout recommendations

### Introduction:

A switch mode step down converter is a potential source of electromagnetic disturbances which may affect the environment as well as the device itself and cause sporadic malfunction up to damages depending on the amount of noise.

In principal we may consider the following basic effects:

- radiated magnetic fields caused by circular currents, occurring mostly with the switching frequency and their harmonics;

- radiated electric fields, often caused by (voltage) oscillations;

- conducted disturbances (voltage spikes or oscillations) on the lines, mostly input and output lines.

### Radiated magnetic fields:

Radiated magnetic fields are caused by circular currents occurring in so called "current windows". These circular currents are alternating currents which are driven by the switching transistor. The alternating current in these windows are driving magnetic fields. The amount of magnetic emissions is mainly depending on the amplitude of the alternating current and the size of the so-called "window" (this is the area, which is defined by the circular current paths.

We can divide into two windows:

- the input current "window" (path consisting of C<sub>IN2</sub>, C<sub>IN3</sub>, L<sub>OUT</sub> and C<sub>OUT</sub>): Only the alternate content of the input current I<sub>S</sub> is considered;

- the output current "window" (path consisting of  $D_{CATCH}$ ,  $L_{OUT}$  and  $C_{OUT}$ ): Output current ripple  $\Delta I$ .

The area of these "windows" has to be kept as small as possible, with the relating elements placed next to each others as close as possible. It is highly recommended to use a ground plane as a single layer which covers the complete regulator area with all components shown in the application diagram. All connections to ground shall be as short as possible.

### Radiated electric fields:

Radiated electric fields are caused by voltage oscillations occurring by stray inductances and stray capacitances at the connection between internal power stage (pin SWO), freewheeling diode  $D_{CATCH}$ , and output capacitor  $C_{OUT}$ . They are also of course influenced by the commutation of the current from the internal power stage to the freewheeling diode  $D_{CATCH}$ . Their frequencies might be above 100 MHz. Therefore, it is recommended to use a fast Schottky diode and to keep the connections in this area as low inductive as possible. This can be achieved by using short and broad connections and by arranging the related parts as close as possible. Following the recommendation of using a ground layer these low inductive connections will form together with the ground layer small capacitances which are desirable to damp the slope of these oscillations. The oscillations use connections or wires as antennas, this effect can also be minimized by the short and broad connections.

### **Application Information**

### Conducted disturbances:

Conducted disturbances are voltage spikes or voltage oscillations, occurring permanently or by occasion mostly on the input or output connections. Comparable to the radiated electric fields they are caused by voltage stage, freewheeling diode  $D_{CATCH}$ , and output capacitor  $C_{OUT}$ .

Their frequencies might be above 100 MHz. They are super positioned to the input and output voltage and might therefore disturb other components of the application.

The countermeasures against conducted disturbances are similar to the radiated electric fields:

- it is recommended to use short and thick connections between the single parts of the converter;

- all parts shall be mounted close together;

- additional filter capacitors (ceramic, with low ESR i.e C<sub>IN3</sub> in the application diagram) in parallel to the output and input capacitor and as close as possible to the switching parts. Input and load current must be forced to pass these devices, do not connect them via thin lines. Recommended values from 10nF to 220nF;

- for the input filter a so called π Filter for maximum suppression might be necessary, which requires additional capacitors on the input.

### 8.1.1 Additional information

Please contact us:

- for information regarding the Pin FMEA;

- for existing application notes with more detailed information about the possibilities of this device;

- for further information you may contact http://www.infineon.com/

**Package Outlines**

## 9 Package Outlines

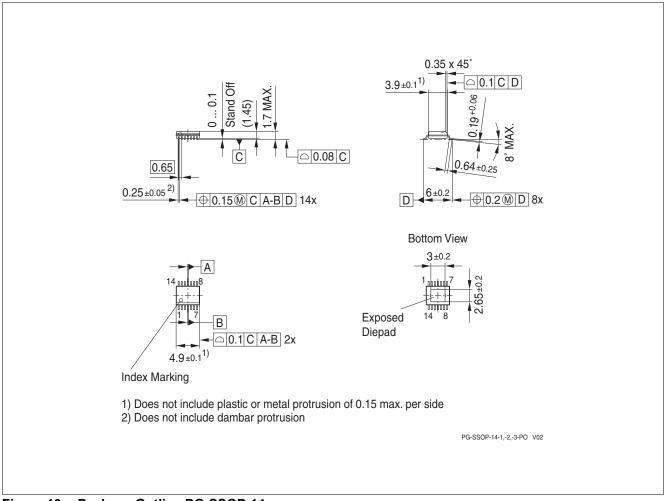

Figure 10 Package Outline PG-SSOP-14

### **Green Product (RoHS compliant)**

To meet the world-wide customer requirements for environmentally friendly products and to be compliant with government regulations the device is available as a green product. Green products are RoHS-Compliant (i.e Pb-free finish on leads and suitable for Pb-free soldering according to IPC/JEDEC J-STD-020).

For further package information, please visit our website: http://www.infineon.com/packages.

Dimensions in mm

Data Sheet

### **Revision History**

# 10 Revision History

| Rev     |            |                    |

|---------|------------|--------------------|

| Version | Date       | Changes            |

| Rev 1.0 | 2013-06-19 | Initial data sheet |

Edition 2013-06-19

Published by Infineon Technologies AG 81726 Munich, Germany © 2016 Infineon Technologies AG All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in guestion, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.