# BF1005S...

#### Silicon N-Channel MOSFET Tetrode

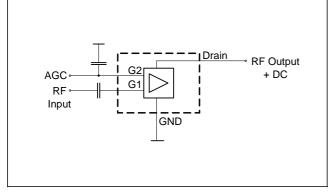

- For low noise, high gain controlled input stages up to 1 GHz

- Operating voltage 5 V

- Integrated biasing network

- Pb-free (RoHS compliant) package<sup>1)</sup>

- Qualified according AEC Q101

ESD (Electrostatic discharge) sensitive device, observe handling precaution!

| Туре     | Package | Pin Configuration |     |      |      |   |   | Marking |

|----------|---------|-------------------|-----|------|------|---|---|---------|

| BF1005S  | SOT143  | 1=S               | 2=D | 3=G2 | 4=G1 | - | - | NZs     |

| BF1005SR | SOT143R | 1=D               | 2=S | 3=G1 | 4=G2 | - | - | NZs     |

#### **Maximum Ratings**

| Symbol                       | Value                                                              | Unit                                                                                  |  |

|------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------|--|

| V <sub>DS</sub>              | 8                                                                  | V                                                                                     |  |

| I <sub>D</sub>               | 25                                                                 | mA                                                                                    |  |

| ± <i>I</i> <sub>G1/2SM</sub> | 10                                                                 |                                                                                       |  |

| +V <sub>G1SE</sub>           | 3                                                                  | V                                                                                     |  |

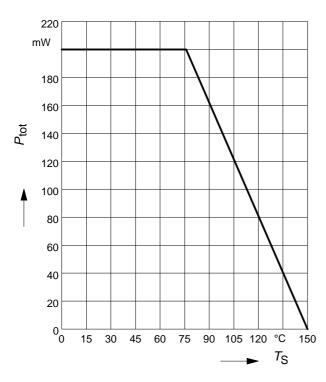

| P <sub>tot</sub>             | 200                                                                | mW                                                                                    |  |

|                              |                                                                    |                                                                                       |  |

| T <sub>stg</sub>             | -55 150                                                            | °C                                                                                    |  |

| T <sub>ch</sub>              | 150                                                                |                                                                                       |  |

|                              | $V_{DS}$ $I_{D}$ $\pm I_{G1/2SM}$ $+ V_{G1SE}$ $P_{tot}$ $T_{stg}$ | $V_{DS}$ 8 $I_D$ 25 $\pm I_{G1/2SM}$ 10 $+V_{G1SE}$ 3 $P_{tot}$ 200 $T_{stg}$ -55 150 |  |

<sup>1</sup>Pb-containing package may be available upon special request

Note:

It is not recommended to apply external DC-voltage on Gate 1 in active mode.

#### **Thermal Resistance**

| Parameter                               | Symbol             | Value | Unit |

|-----------------------------------------|--------------------|-------|------|

| Channel - soldering point <sup>1)</sup> | R <sub>thchs</sub> | ≤ 370 | K/W  |

# **Electrical Characteristics** at $T_A = 25^{\circ}$ C, unless otherwise specified

| Parameter                                                                              | Symbol                 | Values |      |      | Unit |  |

|----------------------------------------------------------------------------------------|------------------------|--------|------|------|------|--|

|                                                                                        |                        |        | typ. | max. | 1    |  |

| DC Characteristics                                                                     |                        |        | •    | •    | •    |  |

| Drain-source breakdown voltage                                                         | V <sub>(BR)DS</sub>    | 12     | -    | -    | V    |  |

| $I_{\rm D} = 650 \ \mu {\rm A}, \ V_{\rm G1S} = 0$ , $V_{\rm G2S} = 0$                 |                        |        |      |      |      |  |

| Gate1-source breakdown voltage                                                         | +V <sub>(BR)G1SS</sub> | 8      | -    | 12   |      |  |

| $+I_{G1S} = 10 \text{ mA}, V_{G2S} = 0, V_{DS} = 0$                                    |                        |        |      |      |      |  |

| Gate2 source breakdown voltage                                                         | ±V <sub>(BR)G2SS</sub> | 8      | -    | 13   |      |  |

| $\pm I_{G2S} = 10 \text{ mA}, V_{G1S} = 0, V_{DS} = 0$                                 |                        |        |      |      |      |  |

| Gate1-source leakage current                                                           | +I <sub>G1SS</sub>     | -      | 100  | -    | μA   |  |

| $V_{G1S} = 6 V, V_{G2S} = 0$                                                           |                        |        |      |      |      |  |

| Gate 2 source leakage current                                                          | ±I <sub>G2SS</sub>     | -      | -    | 50   | nA   |  |

| $\pm V_{G2S} = 8 \text{ V}, V_{G1S} = 0 \text{ , } V_{DS} = 0$                         |                        |        |      |      |      |  |

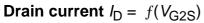

| Drain current                                                                          | I <sub>DSS</sub>       | -      | -    | 800  | μA   |  |

| $V_{\text{DS}} = 5 \text{ V}, \ V_{\text{G1S}} = 0 \ , \ V_{\text{G2S}} = 4 \text{ V}$ |                        |        |      |      |      |  |

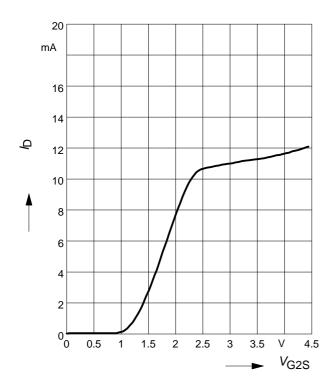

| Operating current (selfbiased)                                                         | I <sub>DSO</sub>       | 8      | 13   | 16   | mA   |  |

| $V_{\text{DS}} = 5 \text{ V}, V_{\text{G2S}} = 4 \text{ V}$                            |                        |        |      |      |      |  |

| Gate2-source pinch-off voltage                                                         | V <sub>G2S(p)</sub>    | -      | 1    | -    | V    |  |

| $V_{\rm DS} = 5 \text{ V}, I_{\rm D} = 100 \mu\text{A}$                                |                        |        |      |      |      |  |

<sup>1</sup>For calculation of  $R_{\text{thJA}}$  please refer to Application Note Thermal Resistance

| Parameter                                                                                          | Symbol            | Values |      |      | Unit |

|----------------------------------------------------------------------------------------------------|-------------------|--------|------|------|------|

|                                                                                                    |                   | min.   | typ. | max. |      |

| AC Characteristics (verified by random sa                                                          | ampling)          |        |      |      |      |

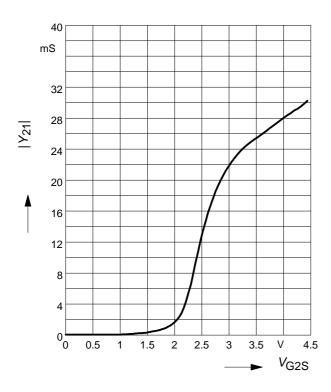

| Forward transconductance                                                                           | g <sub>fs</sub>   | 26     | 30   | -    | mS   |

| $V_{\rm DS} = 5 \text{ V}, \ V_{\rm G2S} = 4.5 \text{ V}$                                          |                   |        |      |      |      |

| Gate1 input capacitance                                                                            | C <sub>g1ss</sub> | -      | 2.4  | 2.7  | pF   |

| $V_{\text{DS}} = 5 \text{ V}, V_{\text{G2S}} = 4 \text{ V}, f = 1 \text{ MHz}$                     | -                 |        |      |      |      |

| Output capacitance                                                                                 | C <sub>dss</sub>  | -      | 1.3  | -    |      |

| $V_{\text{DS}} = 5 \text{ V}, V_{\text{G2S}} = 4 \text{ V}, f = 100 \text{ MHz}$                   |                   |        |      |      |      |

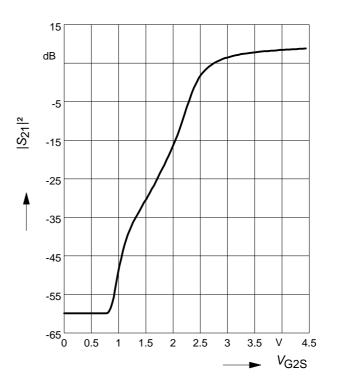

| Power gain (self biased)                                                                           | Gp                | 20     | 22   | -    | dB   |

| $V_{\text{DS}} = 5 \text{ V}, V_{\text{G2S}} = 4 \text{ V}, f = 800 \text{ MHz}$                   |                   |        |      |      |      |

| Noise figure                                                                                       | F                 | -      | 1.6  | 2.1  | dB   |

| $V_{\text{DS}} = 5 \text{ V}, V_{\text{G2S}} = 4 \text{ V}, f = 800 \text{ MHz}$                   |                   |        |      |      |      |

| Gain control range                                                                                 | $\Delta G_{p}$    | 40     | 50   | -    |      |

| $V_{\text{DS}} = 5 \text{ V}, V_{\text{G2S}} = 4 \text{ V} \dots 0 \text{ V}, f = 800 \text{ MHz}$ |                   |        |      |      |      |

# **Electrical Characteristics** at $T_A = 25^{\circ}$ C, unless otherwise specified

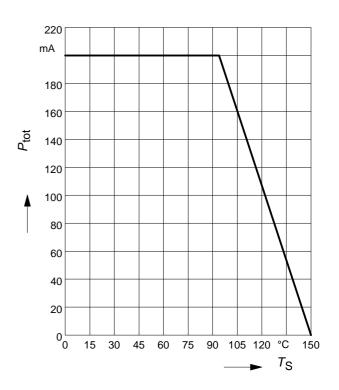

Total power dissipation  $P_{tot} = f(T_S)$ BF1005S, BF1005SR

Total power dissipation  $P_{tot} = f(T_S)$ BF1005SW

Insertion power gain  $|S_{21}|^2 = f(V_{G2S})$

Forward transfer admittance

$|Y_{21}| = f(V_{G2S})$

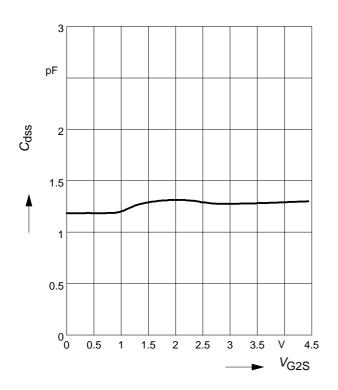

**Output capacitance**  $C_{dss} = f(V_{G2S})$ f = 200 MHz

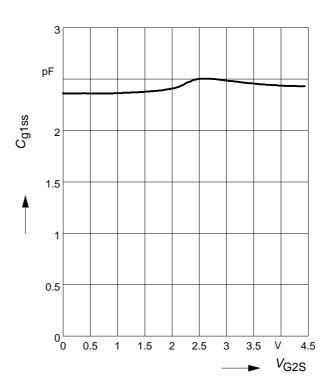

Gate 1 input capacitance  $C_{g1ss}=f(V_{g2s})$ f = 200MHz

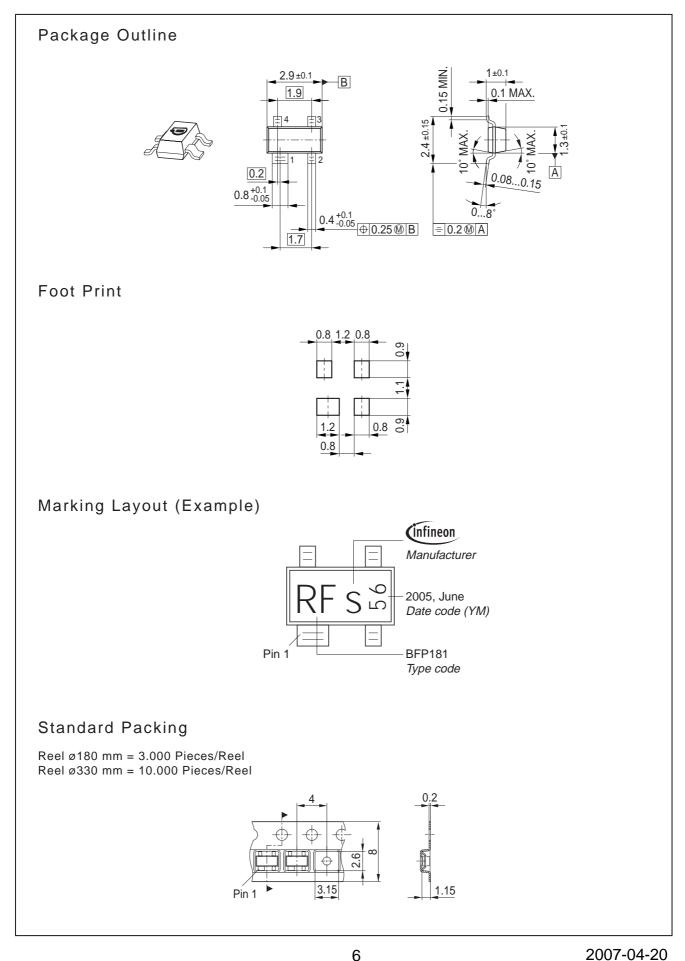

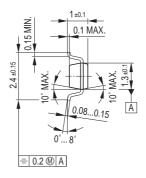

# Package SOT143R

### Package Outline

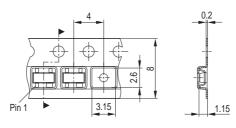

# Foot Print

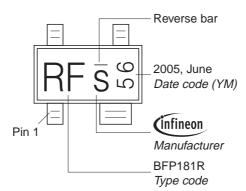

### Marking Layout (Example)

# Standard Packing

Reel ø180 mm = 3.000 Pieces/Reel Reel ø330 mm = 10.000 Pieces/Reel

Edition 2006-02-01 Published by Infineon Technologies AG 81726 München, Germany © Infineon Technologies AG 2007. All Rights Reserved.

#### Attention please!

The information given in this dokument shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie"). With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system.

Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.