# L9912

### Automotive vehicle conform car alternator regulator IC

### Features

- AEC-Q100 qualified

- System in package smart power alternator regulator and 8-bit microcontroller (nonmonolithic approach)

- Protected high/low side field pre-driver for external MOS

- Field short circuit protection

- Regulated voltage driven by ECU (programmable protocol driven)

- Regulated voltage thermally compensated (without protocol)

#### Datasheet - production data

- Lamp driver (wake up and warning detection)

- Self start function

- Load response control (LRC)

- Field monitor (FM) output

- Thermal shutdown

- Package TQFP44EP (10 x 10 mm)

### Description

The L9912 is a controlled multifunctional alternator regulator intended to be used in cars, commercial and agricultural vehicles. It supports 12 V system. The control can be achieved through different communication protocols: RCV, PCM, C\_term. It is a System-In-Package solution with smart power alternator regulator IC coupled with a 8-bit microcontroller (non-monolithic approach). It includes the control section, fault diagnostic circuit which drives a warning lamp, and the protection against short circuits.

This device regulates in closed loop the output of an automotive generator by controlling the field winding current by means of a Pulse-Width Modulation (PWM) of an external high side or low side driver at fixed frequency.

February 2017

This is information on a product in full production.

## Contents

| 1 | Com   | patibilit        | y to 24 V system and the LIN/BSS function                                          |

|---|-------|------------------|------------------------------------------------------------------------------------|

| 2 | Appl  | lication         | schematics                                                                         |

| 3 | Bloc  | k diagra         | ım                                                                                 |

| 4 | Pin c | descript         | ion                                                                                |

| 5 | Elect | trical sp        | ecifications                                                                       |

|   | 5.1   | Absolu           | te maximum ratings 14                                                              |

|   |       | 5.1.1            | EEPROMs parameters                                                                 |

|   | 5.2   | Therma           | al data                                                                            |

|   | 5.3   | Electric         | al characteristics                                                                 |

|   |       | 5.3.1            | Pin "A+/B+"                                                                        |

|   |       | 5.3.2            | Pin "SENSE"                                                                        |

|   |       | 5.3.3            | Pin "IGNIT"                                                                        |

|   |       | 5.3.4            | Pin "PROT_SEL"                                                                     |

|   |       | 5.3.5            | Pin "LIN/BSS"                                                                      |

|   |       | 5.3.6            | Pin "DFM"                                                                          |

|   |       | 5.3.7            | Pin "PH"                                                                           |

|   |       | 5.3.8            | Pin "AUX_IN"                                                                       |

|   |       | 5.3.9            | Pin "GATE"                                                                         |

|   |       | 5.3.10           | Pin "DRAIN" and "SOURCE" 29                                                        |

|   |       | 5.3.11           | Pin "F"                                                                            |

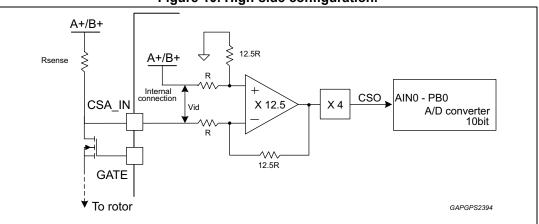

|   |       | 5.3.12           | Pin "CSA_IN"                                                                       |

|   |       | 5.3.13           | Pin "L"                                                                            |

|   |       | 5.3.14           | Pin "GHS" and "GLS"                                                                |

|   |       | 5.3.15           | Pin "LHC"                                                                          |

|   |       | 5.3.16           | Pin "RC"                                                                           |

|   |       | 5.3.17<br>5.3.18 | VREF_ADC                                                                           |

|   |       | 5.3.18<br>5.3.19 | Pin "PH_OUT"         43           Charge pump output         43                    |

|   |       | 5.3.19           | 5-V (VDD) voltage regulator                                                        |

|   |       | 5.3.20<br>5.3.21 | S-V (VDD) voltage regulator         44           Reset output (nRST_SP)         45 |

|   |       | 0.J.Z I          | 1                                                                                  |

2/84

|    |        | 5.3.22     | ēmperature sensor                        |

|----|--------|------------|------------------------------------------|

| 6  | Warni  | ng, alarn  | ns and faults                            |

|    | 6.1    | System e   | rror flags                               |

|    | 6.2    | Lamp       |                                          |

| 7  | Watch  | ndog       |                                          |

|    | 7.1    | Power sta  | age watchdog handling 50                 |

|    | 7.2    | Watchdog   | g error                                  |

|    | 7.3    | Watchdog   | g freeze                                 |

|    | 7.4    | Persisten  | t watchdog failure                       |

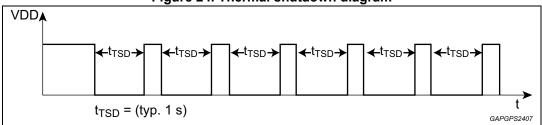

| 8  | Therm  | nal shutd  | own                                      |

| 9  | Turbo  | mode .     |                                          |

| 10 | Comn   | nunicatio  | on configurations 54                     |

| 11 | ADC o  | channels   |                                          |

| 12 | Micro  | controlle  | r non volatile memories 56               |

| 13 | SPI in | terface .  |                                          |

|    | 13.1   | SPI proto  | col                                      |

|    | 13.2   | SPI elect  | ical characteristics                     |

|    |        | 13.2.1 (   | CSN input                                |

|    |        | 13.2.2     | SCK, MOSI input                          |

|    |        | 13.2.3 N   | /ISO output                              |

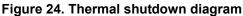

|    | 13.3   | SPI timing | g59                                      |

|    | 13.4   | SPI regis  | ters                                     |

|    |        | 13.4.1 F   | Register read operation61                |

|    |        | 13.4.2 F   | Register write operation62               |

|    |        | 13.4.3 (   | GSW: global status word                  |

|    |        | 13.4.4     | SPI errors                               |

|    |        | 13.4.5 \   | VAKEUP SOURCE register [0x11]63          |

|    |        | 13.4.6 L   | AMP LIN GENERAL STATUS register [0x12]65 |

|    |        | 13.4.7 F   | PH-SENSE register [0x13]                 |

|    |       | 13.4.8   | WATCHDOG / THERMAL SHUTDOWN RESET COUNT register [0x14] 67 |

|----|-------|----------|------------------------------------------------------------|

|    |       | 13.4.9   | DEVICE ID register [0x1F]68                                |

|    |       | 13.4.10  | SYSTEM / UNLOCK register [0x01]68                          |

|    |       | 13.4.11  | SYSTEM OPERATION register [0x02]69                         |

|    |       | 13.4.12  | External POWER MOS register [0x03]70                       |

|    |       | 13.4.13  | WAKE-UP sources and DFM GEN setup register [0x04]71        |

|    |       | 13.4.14  | DFM PWM DUTY CYCLE register [0x05]73                       |

|    |       | 13.4.15  | WATCHDOG CONFIG register [0x06]74                          |

|    |       | 13.4.16  | CP-SPREAD-SPECTRUM & LIN SETTING register [0x08]75         |

|    |       | 13.4.17  | DRV SETTINGS register [0x09]76                             |

|    |       | 13.4.18  | TEST MODE STATUS register [0x0B]76                         |

|    |       | 13.4.19  | WATCHDOG REFRESH register [0x0F]77                         |

|    | 13.5  | SPI seq  | uence example                                              |

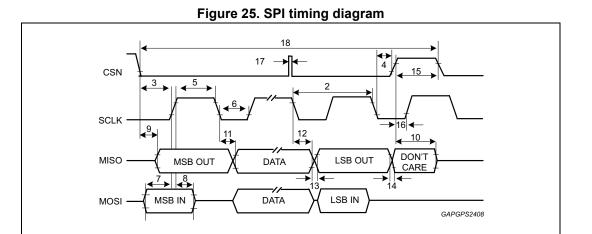

| 14 | Packa | age info | rmation                                                    |

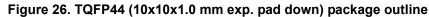

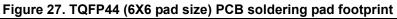

|    | 14.1  | TQFP44   | (10x10x1.0 mm exp. pad down) package information 80        |

| 15 | Order | codes    |                                                            |

| 16 | Revis | ion hist | ory                                                        |

## List of tables

L9912

| Table 1.  | Summary of the information related to 24 V and LIN/BSS present in this specification | 8    |

|-----------|--------------------------------------------------------------------------------------|------|

| Table 2.  | Pin function                                                                         | . 11 |

| Table 3.  | Group of pins externally connected                                                   | . 13 |

| Table 4.  | Absolute maximum ratings                                                             | . 14 |

| Table 5.  | Maximum ratings                                                                      | . 14 |

| Table 6.  | Flash program memory                                                                 | . 16 |

| Table 7.  | Data memory                                                                          | . 16 |

| Table 8.  | Thermal data                                                                         | . 16 |

| Table 9.  | Pin "A+/B+" electrical characteristics                                               | . 17 |

| Table 10. | Electrical characteristics pin "SENSE"                                               | . 19 |

| Table 11. | Electrical characteristics pin "IGNIT".                                              |      |

| Table 12. | Electrical characteristics pin "PROT_SEL"                                            | . 19 |

| Table 13. | Electrical characteristics pin PROT_SEL and RC pin protocol                          |      |

| Table 14. | Electrical characteristics pin "LIN/BSS"                                             | . 22 |

| Table 15. | DFM output configuration                                                             | . 26 |

| Table 16. | Electrical characteristics pin "DFM"                                                 | . 26 |

| Table 17. | Electrical characteristics pin "PH"                                                  | . 27 |

| Table 18. | Electrical characteristics pin "AUX_IN"                                              | . 27 |

| Table 19. | Electrical characteristics pin "GATE"                                                |      |

| Table 20. | Electrical characteristics pin "DRAIN" and "SOURCE"                                  |      |

| Table 21. | Electrical characteristics pin "F"                                                   |      |

| Table 22. | Electrical characteristics pin "CSA_IN"                                              |      |

| Table 23. | Electrical characteristics pin "L"                                                   |      |

| Table 24. | Electrical characteristics pin "GHS" and "GLS"                                       |      |

| Table 25. | Electrical characteristics pin "LHC"                                                 |      |

| Table 26. | Electrical characteristics pin "RC"                                                  |      |

| Table 27. | Electrical characteristics "VREF_ADC"                                                |      |

| Table 28. | Electrical characteristics pin "PH_OUT"                                              |      |

| Table 29. | Charge pump output electrical characteristics                                        |      |

| Table 30. | 5-V (VDD) voltage regulator electrical characteristics                               |      |

| Table 31. | Reset output (nRST_SP) electrical characteristics                                    |      |

| Table 32. | Temperature sensor (TEMP_OUT)                                                        |      |

| Table 33. | System error flags.                                                                  |      |

| Table 34. | Thermal shutdown electrical characteristics                                          |      |

| Table 35. | How to configure the system                                                          |      |

| Table 36. | ADC channels                                                                         |      |

| Table 37. | CSN input electrical characteristics                                                 |      |

| Table 38. | SCK, MOSI input electrical characteristics                                           |      |

| Table 39. | MISO output electrical characteristics                                               |      |

| Table 40. | SPI timing characteristics                                                           |      |

| Table 41. | SPI register                                                                         |      |

| Table 42. | Register read operation                                                              |      |

| Table 43. | Register write operation                                                             |      |

| Table 44. | GSW: global status word                                                              |      |

| Table 45. | WAKEUP SOURCE register [0x11]                                                        |      |

| Table 46. | LAMP LIN GENERAL STATUS register [0x12]                                              |      |

| Table 47. | PH-SENSE register [0x13]                                                             |      |

| Table 48. | Example in a system with 6 pole pairs at 3000 rpm                                    |      |

|           |                                                                                      |      |

| Table 49. | RPM ranges corresponding to different pole pairs values     | 67 |

|-----------|-------------------------------------------------------------|----|

| Table 50. | WATCHDOG / THERMAL SHUTDOWN RESET COUNT register [0x14]     | 67 |

| Table 51. | DEVICE ID register [0x1F]                                   |    |

| Table 52. | SYSTEM / UNLOCK register [0x01]                             |    |

| Table 53. | SYSTEM OPERATION register [0x02]                            |    |

| Table 54. | EXTERNAL POWER MOS register [0x03]                          |    |

| Table 55. | WAKE-UP sources and DFM GEN setup register [0x04]           | 71 |

| Table 56. | DFM PWM DUTY CYCLE register [0x05].                         |    |

| Table 57. | Duty cycle resolution changes according to the frequency.   |    |

| Table 58. | WATCHDOG CONFIG register [0x06]                             |    |

| Table 59. | CP-SPREAD-SPECTRUM & LIN SETTING register [0x08]            | 75 |

| Table 60. | DRV SETTINGS register [0x09]                                |    |

| Table 61. | WATCHDOG REFRESH register [0x0F]                            |    |

| Table 62. | SPI sequence examples                                       |    |

| Table 63. | TQFP44 (10x10x1.0 mm exp. pad down) package mechanical data | 81 |

| Table 64. | Device summary                                              | 82 |

| Table 65. | Document revision history                                   | 83 |

|           |                                                             |    |

# List of figures

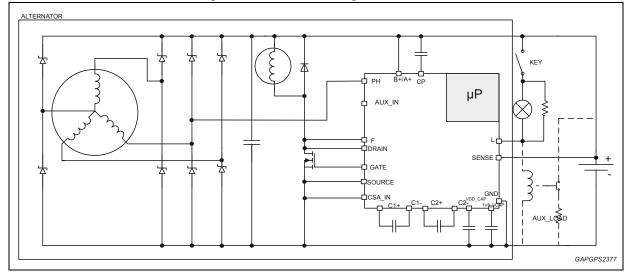

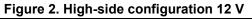

| Figure 1.  | Low-side configuration 12 V                                   | . 9 |

|------------|---------------------------------------------------------------|-----|

| Figure 2.  | High-side configuration 12 V.                                 | . 9 |

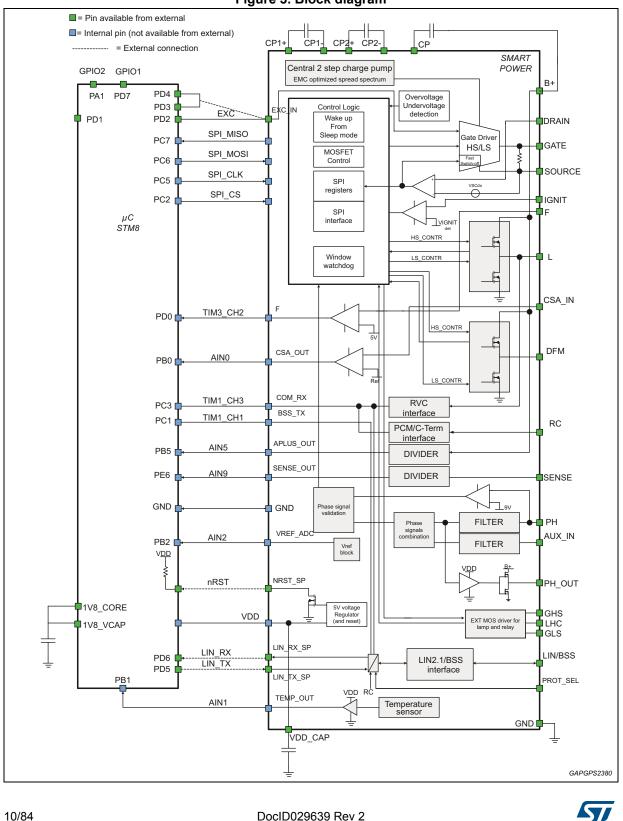

| Figure 3.  | Block diagram                                                 | 10  |

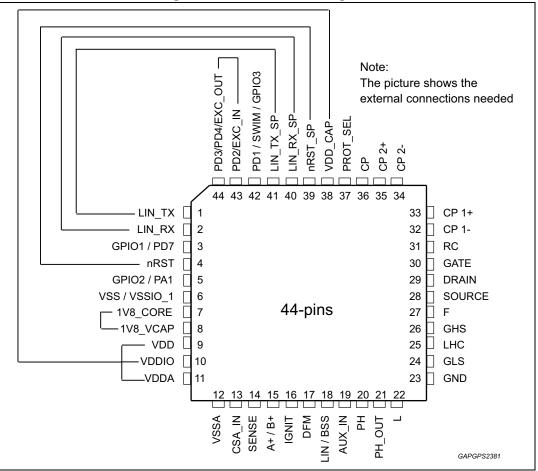

| Figure 4.  | Pin connection diagram                                        |     |

| Figure 5.  | Internal resistor ladder on pin A+                            | 17  |

| Figure 6.  | VB overvoltage protection.                                    | 18  |

| Figure 7.  | Internal resistor ladder on pin SENSE                         | 18  |

| Figure 8.  | LIN/BSS transmit, receive timing                              |     |

| Figure 9.  | External MOS short circuit protection                         | 29  |

| Figure 10. | High-side configuration.                                      |     |

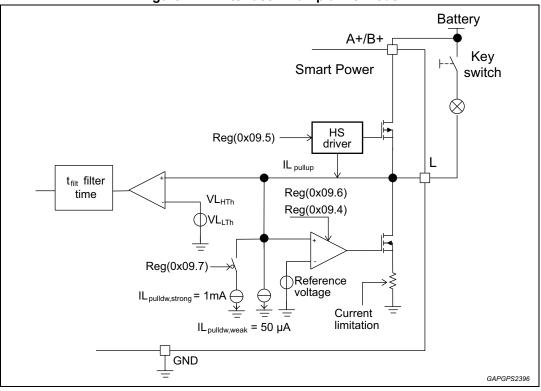

| Figure 11. | L interface in lamp drive mode                                |     |

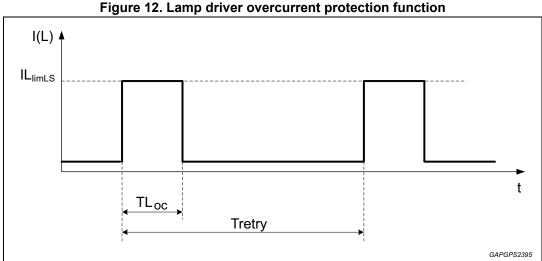

| Figure 12. | Lamp driver overcurrent protection function                   |     |

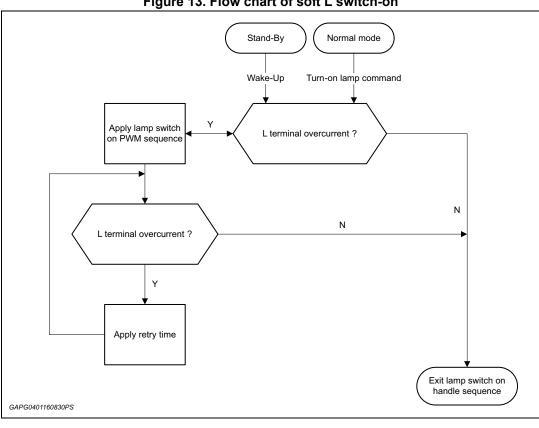

| Figure 13. | Flow chart of soft L switch-on                                |     |

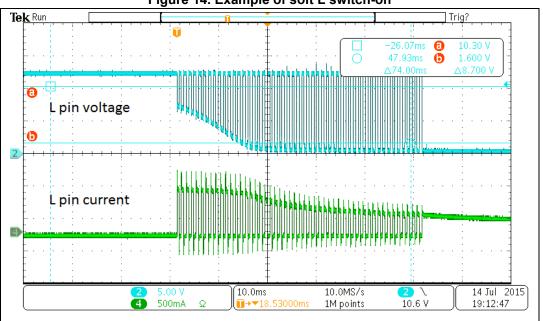

| Figure 14. | Example of soft L switch-on                                   |     |

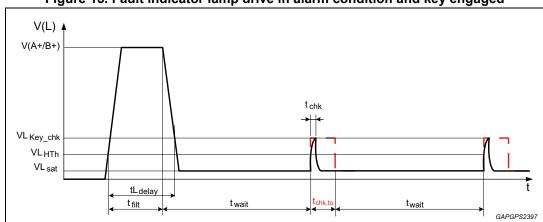

| Figure 15. | Fault indicator lamp drive in alarm condition and key engaged |     |

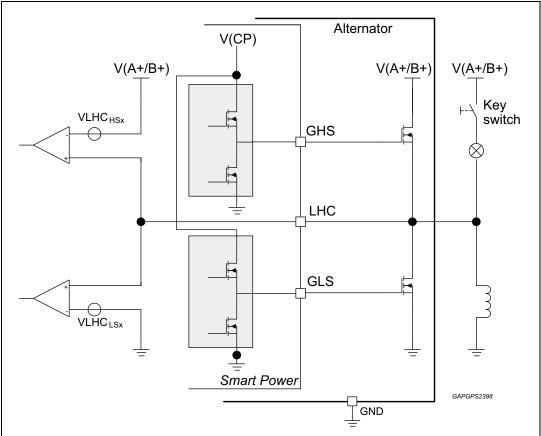

| Figure 16. | External high current lamp pre-driver circuitry               |     |

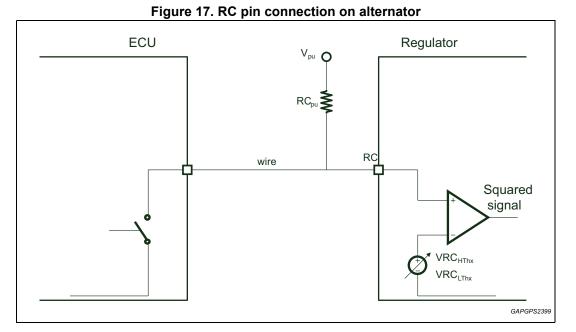

| Figure 17. | RC pin connection on alternator                               | 41  |

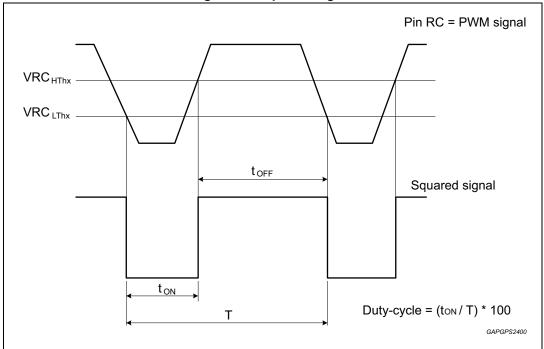

| Figure 18. | Squared signal                                                |     |

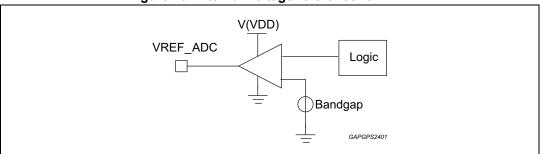

| Figure 19. | Internal voltage reference for ADC                            |     |

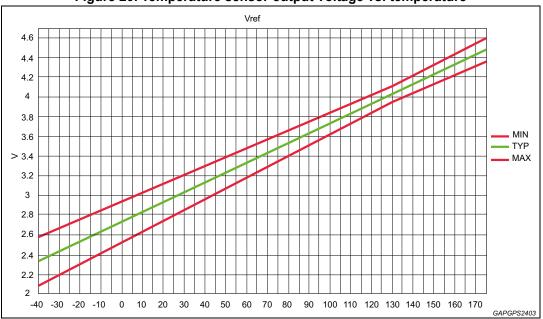

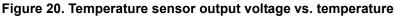

| Figure 20. | Temperature sensor output voltage vs. temperature             |     |

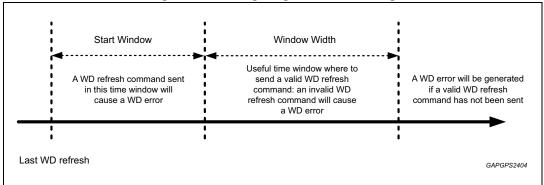

| Figure 21. | Timing diagram of watchdog                                    |     |

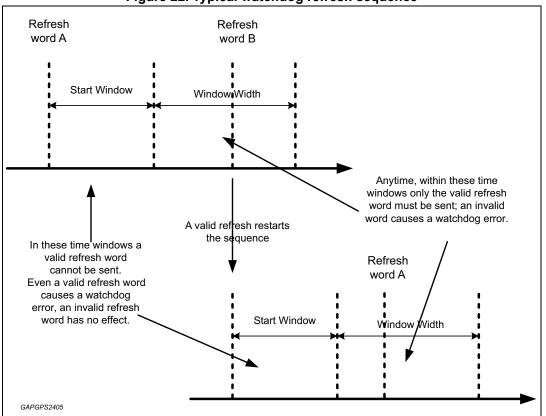

| Figure 22. | Typical watchdog refresh sequence                             |     |

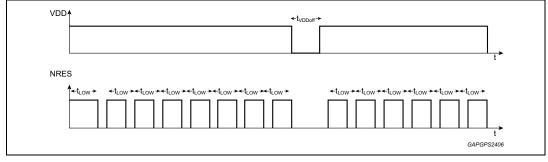

| Figure 23. | Persistent watchdog failure diagram.                          |     |

| Figure 24. | Thermal shutdown diagram                                      |     |

| Figure 25. | SPI timing diagram                                            |     |

| Figure 26. | TQFP44 (10x10x1.0 mm exp. pad down) package outline.          |     |

| Figure 27. | TQFP44 (6X6 pad size) PCB soldering pad footprint             | 81  |

|            |                                                               |     |

### 1 Compatibility to 24 V system and the LIN/BSS function

The compatibility to 24 V system and the LIN/BSS function are available depending on the device version selected: L9912, L9912L, L9924, and L9924L.

The below table summarizes whether the information related to 24 V and LIN/BSS present in this specification are applicable or not:

| specification |                  |                           |  |  |  |

|---------------|------------------|---------------------------|--|--|--|

| Part number   | LIN/BSS function | 24 V system compatibility |  |  |  |

| L9912         | Not applicable   | Not applicable            |  |  |  |

| L9912L        | Applicable       | Not applicable            |  |  |  |

| L9924         | Not applicable   | Applicable                |  |  |  |

| L9924L        | Applicable       | Applicable                |  |  |  |

# Table 1. Summary of the information related to 24 V and LIN/BSS present in this specification

## 2 Application schematics

Figure 1. Low-side configuration 12 V

#### **Block diagram** 3

DocID029639 Rev 2

10/84

### 4 Pin description

#### Figure 4. Pin connection diagram

#### Table 2. Pin function

| N° | Pin name      | Function                                                 |

|----|---------------|----------------------------------------------------------|

| 1  | LIN_TX        | LIN transmitter (µC output)                              |

| 2  | LIN_RX        | LIN receiver (µC input)                                  |

| 3  | PD7/TLI/GPIO1 | General purpose Input/output (PD7) / Top level interrupt |

| 4  | nRST          | Reset (µC)                                               |

| 5  | PA1/GPIO2     | General purpose Input/output (PA1)                       |

| 6  | VSS / VSSIO_1 | Digital ground / I/O ground                              |

| 7  | 1V8_CORE      | 1.8 V Core                                               |

| 8  | 1V8_VCAP      | 1.8 V regulator capacitor(470 to 3300nF)                 |

| 9  | VDD           | Digital power supply                                     |

| 10 | VDDIO         | I/O power supply                                         |

| N° | Pin name       | Function                                                                                |  |

|----|----------------|-----------------------------------------------------------------------------------------|--|

| 11 | VDDA           | Analog power supply (connect to 100nF//1uF for decoupling)                              |  |

| 12 | VSSA           | Analog ground                                                                           |  |

| 13 | CSA_IN         | Current sense ampl. Input                                                               |  |

| 14 | SENSE          | Battery sensing with dedicated wire                                                     |  |

| 15 | A+ /B+         | Battery sense / Device power supply                                                     |  |

| 16 | IGNIT          | Ignition terminal                                                                       |  |

| 17 | DFM            | Field Monitor (PWM signal going to ECU)                                                 |  |

| 18 | LIN/BSS        | LIN / BSS (coming from ECU)                                                             |  |

| 19 | AUX_IN         | Auxiliary input                                                                         |  |

| 20 | PH             | Phase sense input                                                                       |  |

| 21 | PH_OUT         | Filtered Phase signal                                                                   |  |

| 22 | L              | Key sensing and Warning Lamp terminal output                                            |  |

| 23 | GND            | Regulator ground                                                                        |  |

| N° | PIN            | Function                                                                                |  |

| 24 | GLS            | Gate driver of ext Low Side MOS used for Lamp                                           |  |

| 25 | LHC            | Key sensing and Warning Lamp terminal output in case of ext MOS used for lamp driving   |  |

| 26 | GHS            | Gate driver of ext High Side MOS used for Relay                                         |  |

| 27 | F              | Field activity monitor (for High side and low side configuration)                       |  |

| 28 | SOURCE         | External MOS Source                                                                     |  |

| 29 | DRAIN          | External MOS Drain                                                                      |  |

| 30 | GATE           | External MOS Gate                                                                       |  |

| 31 | RC             | C-Terminal / PCM (PWM signal input coming from ECU)                                     |  |

| 32 | CP1-           | Charge pump pin for capacitor 1, negative side                                          |  |

| 33 | CP1+           | Charge pump pin for capacitor 1, positive side                                          |  |

| 34 | CP2-           | Charge pump pin for capacitor 2, negative side                                          |  |

| 35 | CP2+           | Charge pump pin for capacitor 2, positive side                                          |  |

| 36 | CP             | Charge pump output                                                                      |  |

| 37 | PROT_SEL       | Protocol selection                                                                      |  |

| 38 | VDD_CAP        | 5V capacitor(5V regulator output)                                                       |  |

| 39 | nRST_SP        | Reset (Smart Power)                                                                     |  |

| 40 | LIN_RX_SP      | LIN receiver (smart power output)                                                       |  |

| 41 | LIN_TX_SP      | LIN transmitter (smart power input)                                                     |  |

| 42 | PD1/SWIM/GPIO3 | Single Wire Interface Module (for µC programming)<br>General purpose Input/output (PD1) |  |

As shown in the picture, the following pin groups must be connected through external wiring.

Table 3. Group of pins externally connected

Excitation output: connect to PD2/EXC\_IN

| Signal | Pins         |                 |            |              |

|--------|--------------|-----------------|------------|--------------|

| VDD    | 9 (VDD)      | 10 (VDDIO)      | 11 (VDDA)  | 38 (VDD_CAP) |

| GND    | 23 (GND)     | 6 (VSS/VSSIO_1) | 12 (VSS_A) | Exposed PAD  |

| V18    | 7 (1V8_CORE) | 8 (V8_VCAP)     |            |              |

| nRST   | 4 (nRST)     | 39 (nRST_SP)    |            |              |

| LIN_TX | 1 (LIN_TX)   | 41 (LIN_TX_SP)  |            |              |

| LIN_RX | 2 (LIN_RX)   | 40 (LIN_RX_SP)  |            |              |

VDD and GND pins in the block diagram are generic references to the relevant pin groups of the above table.

44

PD3/PD4/EXC\_OUT

## 5 Electrical specifications

### 5.1 Absolute maximum ratings

$T_i$  = -40 to 155 °C, unless otherwise specified.

| Table 4. Absolute maximum ratings | Table 4. | Absolute | maximum | ratings |

|-----------------------------------|----------|----------|---------|---------|

|-----------------------------------|----------|----------|---------|---------|

| Symbol                               | Parameter                                                | Value      | Unit |

|--------------------------------------|----------------------------------------------------------|------------|------|

| VB <sub>DC</sub>                     | DC supply voltage                                        | 48         | V    |

| VB <sub>LD</sub>                     | Transient supply voltage (load dump) t < 500 ms          | 65         | V    |

| Тj                                   | Junction temperature range                               | -40 to 155 | °C   |

| T <sub>stg</sub> , T <sub>case</sub> | Storage and case temperature range                       | -40 to 155 | °C   |

| P <sub>TOT</sub>                     | Total power dissipation                                  | 1.25       | W    |

| VB <sub>R</sub>                      | Reverse battery voltage @ 25 °C, T = 15 sec              | -2.5       | V    |

| VPH <sub>min</sub>                   | Normal working condition reverse voltage (PH Bplus. GND) | -1.5       | V    |

| ESD <sub>HBM</sub>                   | ESD HBM (Internal pins)                                  | ±2         | kV   |

| ESD <sub>HBM</sub>                   | ESD HBM (All global pins)                                | ±4         | kV   |

| ESD <sub>HBM</sub>                   | LIN pin                                                  | ±6         | kV   |

#### Table 5. Maximum ratings

| N° | Pin           | Condition                                    | Min. | Max.                 | Unit |

|----|---------------|----------------------------------------------|------|----------------------|------|

| 1  | LIN_TX        | -                                            | -0.2 | V <sub>DD</sub> +0.2 | V    |

| 2  | LIN_RX        | -                                            | -0.2 | V <sub>DD</sub> +0.2 | V    |

| 3  | PD7/TLI/GPIO1 | -                                            | -0.2 | V <sub>DD</sub> +0.2 | V    |

| 4  | nRST          | -                                            | -0.2 | V <sub>DD</sub> +0.3 | V    |

| 5  | PA1/GPIO2     | -                                            | -0.2 | V <sub>DD</sub> +0.2 | V    |

| 6  | VSS / VSSIO_1 | -                                            | -    | -                    | V    |

| 7  | 1V8_CORE      | -                                            | -0.2 | 2.7                  |      |

| 8  | 1V8_VCAP      | -                                            | -0.2 | 2.0                  | V    |

| 9  | VDD           | -                                            | -0.2 | 6.5                  | V    |

| 10 | VDDIO         | -                                            | -0.2 | 6.5                  | V    |

| 11 | VDDA          | -                                            | -0.3 | 6.5                  | V    |

| 12 | VSSA          | -                                            | -    | -                    | -    |

| 13 | CSA_IN        | -                                            | -0.3 | +48                  | V    |

| 14 | SENSE         | -                                            | -20  | +48                  | V    |

| 15 | A+/B+         | Reverse battery voltage @<br>25 °C, T = 15 s | -2.5 | +48                  | V    |

| 16 | IGNIT         | -                                            | -20  | +48                  | V    |

| 17 | DFM           | -                                            | -0.3 | +48                  | V    |

|    | Table 5. Maximum ratings (continued) |           |                            |                                   |      |  |  |  |  |  |

|----|--------------------------------------|-----------|----------------------------|-----------------------------------|------|--|--|--|--|--|

| N° | Pin                                  | Condition | Min.                       | Max.                              | Unit |  |  |  |  |  |

| 18 | LIN/BSS                              | -         | -20                        | +40                               | V    |  |  |  |  |  |

| 19 | AUX_IN                               | -         | -20                        | +48                               | V    |  |  |  |  |  |

| 20 | PH                                   | -         | -20                        | +48                               | V    |  |  |  |  |  |

| 21 | PH_OUT                               | -         | -0.3                       | +48                               | V    |  |  |  |  |  |

| 22 | L                                    | -         | -0.3                       | +48                               | V    |  |  |  |  |  |

| 23 | GND                                  | -         | -                          | -                                 | -    |  |  |  |  |  |

| 24 | GLS                                  | -         | -0.3                       | +13.5                             | V    |  |  |  |  |  |

| 25 | LHC                                  | -         | -0.3                       | +48                               | V    |  |  |  |  |  |

| 26 | GHS                                  | -         | max[-0.3;<br>V(LHC)-0.6]   | min[+48;<br>V(LHC)+13.5]          | V    |  |  |  |  |  |

| 27 | F                                    | -         | -2                         | +48                               | V    |  |  |  |  |  |

| 28 | SOURCE                               | -         | -2                         | +48                               | V    |  |  |  |  |  |

| 29 | DRAIN                                | -         | -2.5                       | +48                               | V    |  |  |  |  |  |

| 30 | GATE                                 | -         | V(SOURCE)-<br>0.6          | min[+48;<br>V(SOURCE)+13<br>.5]   | V    |  |  |  |  |  |

| 31 | RC                                   | -         | -1.5                       | +48                               | V    |  |  |  |  |  |

| 32 | CP1-                                 | -         | -0.3                       | +48                               | V    |  |  |  |  |  |

| 33 | CP1+                                 | -         | max[-0.3;<br>V(A+/B+)-0.3] | V(A+/B+)+20                       | V    |  |  |  |  |  |

| 34 | CP2-                                 | -         | -0.3                       | +48                               | V    |  |  |  |  |  |

| 35 | CP2+                                 | -         | max[-0.3;<br>V(A+/B+)-0.6] | V(A+/B+)+20                       | V    |  |  |  |  |  |

| 36 | СР                                   | -         | max[-0.3;<br>V(A+/B+)-0.3] | V(A+/B+)+20                       | V    |  |  |  |  |  |

| 37 | PROT_SEL                             | -         | -0.3                       | 6.5                               | V    |  |  |  |  |  |

| 38 | VDD_CAP                              | -         | -0.2                       | 6.5                               | V    |  |  |  |  |  |

| 39 | nRST_SP                              | -         | -0.3                       | V <sub>DD</sub> +0.3              | V    |  |  |  |  |  |

| 40 | LIN_RX_SP                            | -         | -0.3                       | V <sub>DD</sub> +0.3              | V    |  |  |  |  |  |

| 41 | LIN_TX_SP                            | -         | -0.3                       | 6.5                               | V    |  |  |  |  |  |

| 42 | PD1/SWIM/GPIO<br>3                   | -         | -0.2                       | V <sub>DD</sub> +0.2              | V    |  |  |  |  |  |

| 43 | PD2/EXC_IN                           | -         | -0.2                       | min[6.5;<br>V <sub>DD</sub> +0.3] | V    |  |  |  |  |  |

| 44 | PD3/PD4/EXC_O<br>UT                  | -         | -0.2                       | V <sub>DD</sub> +0.2              | V    |  |  |  |  |  |

Table 5. Maximum ratings (continued)

### 5.1.1 EEPROMs parameters

| Table | 6. | Flash   | program | memory      |

|-------|----|---------|---------|-------------|

| Tuble | ν. | 1 10311 | program | inclusion y |

| # | Parameter          | Test condition            | Value | Unit   |

|---|--------------------|---------------------------|-------|--------|

| 1 |                    | T <sub>amb</sub> = 25 °C  | 2500  |        |

| 2 | Erase/Write cycles | T <sub>amb</sub> = 55 °C  | 1500  | Cycles |

| 3 |                    | T <sub>amb</sub> = 125 °C | 300   |        |

| 4 | Retention          | T <sub>amb</sub> = 55 °C  | 20    | Years  |

#### Table 7. Data memory

| # | Parameter          | Test condition            | Value  | Unit   |

|---|--------------------|---------------------------|--------|--------|

| 1 |                    | T <sub>amb</sub> = 25 °C  | 280000 | Cycles |

| 2 | Erase/Write cycles | T <sub>amb</sub> = 55 °C  | 170000 |        |

| 3 |                    | T <sub>amb</sub> = 125 °C | 10000  |        |

| 4 | Retention          | T <sub>amb</sub> = 55 °C  | 2      | Years  |

### 5.2 Thermal data

#### Table 8. Thermal data

| # | Symbol                 | Parameter                           | Max. | Unit |

|---|------------------------|-------------------------------------|------|------|

| 1 | R <sub>th_j-case</sub> | Thermal resistance junction-to-case | 1    | °C/W |

| 2 | T <sub>pad</sub>       | Exposed pad temperature             | 140  | °C   |

### 5.3 Electrical characteristics

#### 5.3.1 Pin "A+/B+"

This pin is both the primary power supply (B+) and the default battery sense (A+)

The device is supplied by the battery through A+/B+ pin and it remains in stand-by condition with a current consumption of  $IB_{stby12V/24V}$  until there is activity on one or more wake-up sources.

L9912

| # | Symbol                | Parameter                                           | Test condition                                                                                                                                      | Min.  | Тур. | Max.  | Unit |

|---|-----------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|

| 1 | VB <sub>OVR</sub>     | Operating Voltage Range                             | -                                                                                                                                                   | 6     | -    | 40    | V    |

| 2 | IB <sub>stby12V</sub> | 12-V stand-by current consumption                   | V(A+/B+) = 12.6 V<br>6 wake-up sources active<br>V(PH)=V(AUX_IN)=V(GND)<br>LIN_BSS tied to A+/B+<br>RC pin tied to A+/B+ through a<br>resistor      | -     | -    | 255   | μΑ   |

| 3 | IB <sub>stby24∨</sub> | 24-V stand-by current consumption                   | V(A+/B+) = 25.2 V<br>6 wake-up sources active<br>V(PH)=V(AUX_IN)=V(GND)<br>LIN_BSS pin tied to A+/B+;<br>RC pin tied to A+/B+ through a<br>resistor | -     | -    | 265   | μΑ   |

| 4 | VP                    | Over-voltage protection threshold (12-V systems)    | [0x2].12 = SEL24V_EN = b0                                                                                                                           | 16.5  | 17.6 | 19    | V    |

| 4 | VB <sub>IntOvp</sub>  | Over-voltage protection<br>threshold (24-V systems) | [0x2].12 = SEL24V_EN = b1                                                                                                                           | 33    | 35.5 | 38    | V    |

| 5 | VBlow                 | A+/B+ under-voltage                                 | -                                                                                                                                                   | 4.5   | 5.3  | 6     | V    |

| 6 | αB                    | Resistor divider attenuation                        | [0x2].12 = SEL24V_EN = 0                                                                                                                            | 3.96  | 4    | 4.04  | V/V  |

| 0 | ub                    |                                                     | [0x2].12 = SEL24V_EN = 1                                                                                                                            | 7.925 | 8    | 8.069 | V/V  |

| 7 | εВ                    | Resistor divider accuracy                           | [0x2].12 = SEL24V_EN = 1                                                                                                                            | -     | -    | 0.9   | %    |

| 8 | fBp                   | Pole frequency                                      | -                                                                                                                                                   | 520   | 860  | 1570  | Hz   |

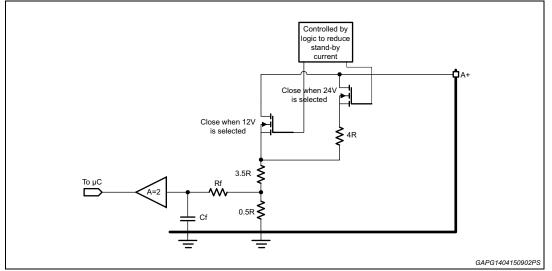

Figure 5. Internal resistor ladder on pin A+

When the A+ voltage drops below  $\mathsf{VB}_{\mathsf{low}}$  the whole device is turned-off and could be initialized by a Power-On Reset (PORn).

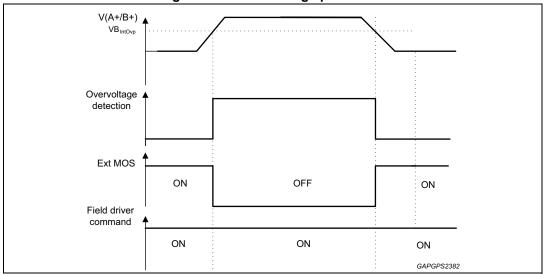

If A+/B+ voltage overcomes the VB<sub>IntOvp</sub> value, the system switches the field excitation off and sets bit 7 of SPI read register 0x12 [13.4.6]: it's up to the application software to take the appropriate actions (lamp on, drivers off, etc.).

A+/B+ signal, suitably conditioned and filtered by an 'active' divider equipped with a low-pass filter, is forwarded to  $\mu$ C pin AIN5.

Figure 6. VB overvoltage protection

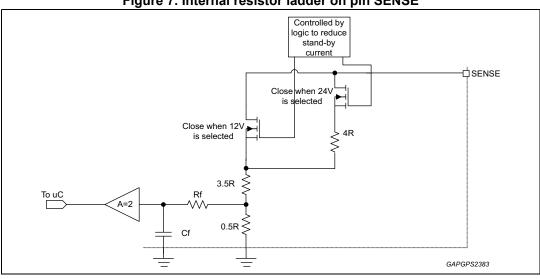

#### 5.3.2 Pin "SENSE"

The system battery can be alternatively sensed using the SENSE input, instead of A+ sensing path.

A suitable resistor ladder can be selected by means of bit 12 of SPI write register 0x02, depending on the device operating mode (12 V or 24 V [13.4.11]).

The signal, before being forwarded to  $\mu C$  pin AIN9, is filtered through single pole low-pass filter.

Figure 7. Internal resistor ladder on pin SENSE

18/84

A similar block is used to bring A+ pin voltage to AIN5 microcontroller analog input.

| # | Symbol          | Parameter                    | Test Condition           | Min.  | Тур. | Max.  | Unit |

|---|-----------------|------------------------------|--------------------------|-------|------|-------|------|

| 4 | αS              | Resistor divider attenuation | [0x2].12 = SEL24V_EN = 0 | 3.96  | 4    | 4.04  | V/V  |

| 1 | us              |                              | [0x2].12 = SEL24V_EN = 1 | 7.925 | 8    | 8.069 | V/V  |

| 2 | εS              | Resistor divider accuracy    | [0x2].12 = SEL24V_EN = 1 | -     | -    | 0.9   | %    |

| 3 | fS <sub>p</sub> | Pole frequency               | -                        | 520   | 860  | 1570  | Hz   |

Table 10. Electrical characteristics pin "SENSE"

#### 5.3.3 Pin "IGNIT"

The IGNIT pin is an input used as additional signal to wake-up the device. The signal applied to IGNIT is compared to a threshold  $VIGNIT_{detx}$  to manage the device wake-up. If not used this pin must be tied to GND.

| # | Symbol                   | Parameter                    | Test condition                        | Min. | Тур. | Max. | Unit |

|---|--------------------------|------------------------------|---------------------------------------|------|------|------|------|

| 1 | VIGNIT <sub>det1</sub>   | 24-V threshold input voltage | [0x2].12 = SEL24V_EN = b1             | 11   | 13   | 15   | V    |

| 2 | VIGNIT <sub>det2</sub>   | 12-V threshold input voltage | [0x2].12 = SEL24V_EN = b0             | 6    | 8    | 10   | V    |

| 3 | IGNIT <sub>pull-dw</sub> | Pull-down current            | 28 V<(IGNIT) ≤ VIGNIT <sub>det2</sub> | -    | 20   | 250  | μA   |

Table 11. Electrical characteristics pin "IGNIT"

#### 5.3.4 Pin "PROT\_SEL"

This pin is used together with RC to select the used protocol. The pull-up resistor present in Active mode is turned into pull-down one in power stand-by mode to limit current consumption.

| - |                       |                            |                                                                                                           |      |      |          |      |

|---|-----------------------|----------------------------|-----------------------------------------------------------------------------------------------------------|------|------|----------|------|

| # | Symbol                | Parameter                  | Test condition                                                                                            | Min. | Тур. | Max.     | Unit |

| 1 | VPSELL                | Low level input voltage    | -                                                                                                         | -    | -    | 1.3      | V    |

| 2 | VPSEL <sub>H</sub>    | High level input voltage   | -                                                                                                         | 2.3  | -    | $V_{DD}$ | V    |

| 3 | VPSEL <sub>Hyst</sub> | Input hysteresis           | -                                                                                                         | -    | 0.4  | -        | V    |

| 4 | RPSEL                 | Pull-up/pull-down resistor | Active mode<br>Pull-up to internal 3.3-V power rail<br>V(PROT_SEL) = V(GND)<br>RPSEL = -3.3 V/I(PROT_SEL) | -    | 100  | -        | kΩ   |

Table 12. Electrical characteristics pin "PROT\_SEL"

| # | Symbol              | Parameter         | Test condition                                                                                  | Min. | Тур. | Max. | Unit |

|---|---------------------|-------------------|-------------------------------------------------------------------------------------------------|------|------|------|------|

| 5 | IPSEL <sub>PU</sub> | Pull-up current   | Active mode<br>RPSEL current when pull-up to<br>internal 3.3-V power rail<br>V(PROT_SEL)=V(GND) | -    | -33  | -    | μΑ   |

| 6 | IPSEL <sub>PD</sub> | Pull-down current | Power Stand-by mode<br>RPSEL current when pull-down to<br>GND<br>V(PROT_SEL) = V <sub>DD</sub>  | -    | 33   | -    | μA   |

Table 12. Electrical characteristics pin "PROT\_SEL" (continued)

#### 5.3.5 Pin "LIN/BSS"

This pin can be used for both LIN and BSS communication protocols. In order to allow the pin sharing between LIN and BSS protocol (the internal pull-up resistor necessary for LIN is not used by BSS protocol), it is necessary to select the desired protocol using the PROT\_SEL pin, RC pin and control internal pull-up resistor by bit 4 of SPI register 0x08.

| PROT_SEL PIN level | RC PIN level                                                               | PROTOCOL SELECTED   |

|--------------------|----------------------------------------------------------------------------|---------------------|

| Low                | Low                                                                        | LIN                 |

| Low                | High (through ext pull-up resistor)                                        | BSS                 |

| High               | High (through ext pull-up resistor<br>for PCM and C-Term)<br>Low (for RVC) | All other protocols |

| High               | High                                                                       | Reserved            |

Because of the internal pull-up resistor, when not used (no LIN or BSS protocol) the pin should be left open and the "wake-up by LIN" function must be disabled by SPI.

#### LIN general requirements:

- Speed communication up to 20 kbit/s (100 kbit/s for Flash).

- LIN 2.1 compliant (SAEJ2602 compatible) transceiver.

- Functional range from +40 V to -18 V DC at LIN/BSS pin.

- GND disconnection fail safe at module level.

- Off mode: does not disturb network.

- GND shift operation at system level.

- Micro controller interface with CMOS compatible I/O pins.

- ESD: Immunity against automotive transients per ISO7637 specification

- Matched output slopes and propagation delay

- In order to further reduce the current consumption in standby mode, the integrated LIN bus interface offers an ultra low current consumption.

Pins involved in both LIN and BSS protocols management are:

- LIN\_RX\_SP: smart power output, which stands for RxD

- LIN\_TX\_SP: smart power input, which stands for TxD

- LIN/BSS: transceiver bus from ECU

- LIN\_RX: µC input to be connected to LIN\_RX\_SP

- LIN\_TX: µC output to be connected to LIN\_TX\_SP

#### LIN Error Handling

The device provides the following 3 error handling features which aren't described in the LIN Spec. V2.1, but implemented in several stand-alone LIN transceivers/microcontrollers to switch the application back to normal operation mode.

• Dominant TxD time out

In case TxD is in dominant state (i.e. low level) for more than  $t_{dom(TXD)}$ =12ms (typical value) the transmitter will be disabled. The status won't be latched and can be read through bit 12 (read only) of 0x12 SPI register. The transmitter remains disabled until TxD changes to recessive state (i.e. high level) for more than 12µs. This error detection can be enabled by setting bit 1 of 0x08 SPI register.

• Permanent recessive LIN/BSS bus

In case TxD changes to dominant (i.e. low level) state and RxD signal does not follow within  $t_{rec(LIN)} = 40 \ \mu s$  (typical value) the transmitter will be disabled. The status bit won't be latched and can be read through bit 11 (read only) of 0x12 SPI register. The transmitter remains disabled until TxD changes to recessive state (i.e. high level) for more than 12  $\mu s$ .

• Permanent dominant LIN/BSS bus

In case the bus state is dominant (i.e. LIN/BSS at low level) for more than  $t_{dom(LIN)} = 12 \text{ ms}$  (typical value) a permanent dominant status will be detected. The status won't be latched and can be read through bit 13 (read only) of 0x12 SPI register. The transmitter will not be switched off. This error detection can be enabled by setting bit 1 of 0x08 SPI register.

*Note:* a normal wake up caused by a message on the bus will start the voltage regulator and the microcontroller to switch the application back to normal operation mode.

#### Wake-up by LIN/BSS bus

In power standby mode the device can receive a wake-up from LIN/BSS bus. Two different conditions can be differentiated:

Normal wake-up

A normal wake-up occurs when the device was previously asked to enter Power Standby mode while LIN/BSS bus was in recessive (i.e. high level) state. A level at LIN bus crossing V<sub>Thwkup</sub> longer than t<sub>linbus</sub> = 5  $\mu$ s (typical value) will switch the device into Active mode and will turn the LIN/BSS receiver on as well to process coming message frames. An event is generated at the RxD pin.

• Wake-up from LIN/BSS bus in short-to-GND condition

This wake-up condition isn't supported by the device and must be carefully avoided into application. In case the device was asked to enter Power Stand-by mode while LIN/BSS bus was recognized in dominant (i.e. low level) state, the command must be preceded by the LIN/BSS wake-up disable command (bit 12 in 0x04 SPI register).

When the device is in Active mode through any other available wake-up source, the LIN/BSS wake-up can be restored.

Compatible to LIN 2.1 for Baud rates up to 20 kBit/s (Up to 100 kbit/s for Flash Mode).

| Table 14. Electrical characteristics pin "LIN/BSS" |                       |                                                              |                                                                                                              |                       |                  |                   |      |

|----------------------------------------------------|-----------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------|------------------|-------------------|------|

| ١                                                  | Symbol                | Parameter                                                    | Test condition                                                                                               | Min.                  | Тур.             | Max.              | Unit |

| LIN/                                               | BSS receive           | r                                                            |                                                                                                              |                       |                  |                   |      |

| 1                                                  | V <sub>TXDLOW</sub>   | TxD input voltage<br>dominant level                          | -                                                                                                            | -                     | -                | 1.3               | ۷    |

| 2                                                  | V <sub>TXDHIGH</sub>  | Input voltage<br>recessive level                             | -                                                                                                            | 2.3                   | -                | V <sub>DD</sub>   | V    |

| 3                                                  | V <sub>TXDHYS</sub>   | TxD input hysteresis                                         | -                                                                                                            | -                     | 0.5              | -                 | V    |

| 4                                                  | I <sub>TXDPU</sub>    | TxD input pull-up<br>current                                 | Active mode<br>Pull-up to internal 3.3-V<br>power rail<br>V(TxD)=V(GND)<br>I <sub>TXDPU</sub> =-3.3 V/100 kΩ | -60                   | -33              | -5                | μΑ   |

| 5                                                  | I <sub>TXDPD</sub>    | TxD input pull-down<br>current                               | Power Stand-by mode $V(TxD) = V_{DD}$                                                                        | 5                     | 33               | 60                | μA   |

| 6                                                  | V <sub>RXDLOW</sub>   | TxD output voltage<br>dominant level                         | l(RxD) = 2 mA                                                                                                | -                     | 0.2              | 0.5               | V    |

| 7                                                  | V <sub>RXDHIGH</sub>  | TxD output voltage recessive level                           | l(RxD) = 2 mA                                                                                                | V <sub>DD</sub> -0.4V | -                | -                 | V    |

| 8                                                  | V <sub>Thdom</sub>    | Receiver threshold<br>voltage recessive to<br>dominant state | V(A+/B+) =12 V                                                                                               | 0.4<br>V(A+/B+)       | 0.45<br>V(A+/B+) | 0.5<br>V(A+/B+)   | V    |

| 9                                                  | V <sub>Threc</sub>    | Receiver threshold<br>voltage dominant to<br>recessive state | V(A+/B+) =12 V                                                                                               | 0.5<br>V(A+/B+)       | 0.55<br>V(A+/B+) | 0.6<br>V(A+/B+)   | V    |

| 10                                                 | V <sub>Thhys</sub>    | Receiver threshold hysteresis                                | V(B+/A+) =12 V,<br>V <sub>Threc –</sub> V <sub>Thdom</sub>                                                   | 0.07<br>V(A+/B+)      | 0.1<br>V(A+/B+)  | 0.175<br>V(A+/B+) | V    |

| 11                                                 | V <sub>Thcnt</sub>    | Receiver tolerance center value                              | V(B+/A+) =12 V,<br>(V <sub>Threc</sub> + V <sub>Thdom</sub> )/2                                              | 0.475<br>V(A+/B+)     | 0.5<br>V(A+/B+)  | 0.525<br>V(A+/B+) | V    |

| 12                                                 | V <sub>Thwkup</sub>   | Receiver wakeup<br>threshold voltage                         | Wake-up by LIN/BSS active,<br>Power Stand-by mode,<br>recessive-to-dominant edge,<br>V(A+/B+)-3.5 V<40 V     | V(A+/B+)<br>-3.5      | V(A+/B+)<br>-2.5 | V(A+/B+)<br>-1.5  | V    |

| 13                                                 | t <sub>linbus</sub>   | Time for wakeup via<br>bus                                   | Wake-up by LIN/BSS active,<br>Power Stand-by mode,<br>recessive-to-dominant edge                             | -                     | 5                | -                 | μs   |

| LIN/                                               | BSS DC para           | ameters                                                      |                                                                                                              |                       |                  | •                 |      |

| 14                                                 | I <sub>LINDomSC</sub> | Transmitter input<br>current limit in<br>dominant state      | V(TxD)=V <sub>TXDLOW</sub><br>V(LIN/BSS) =V(A+/B+) =33 V                                                     | 40                    | 100              | 180               | mA   |

| Table 14. | Electrical | characteristics | pin  | "LIN/BSS" |

|-----------|------------|-----------------|------|-----------|

|           | LICOLIIOUI | onaraotoristios | PIII |           |

22/84

| ١   | Symbol                            | Parameter                                                                     | Test condition                                                                                                                                                                                                                                                                                                                                                                                                                                    | Min.            | Тур. | Max. | Unit |

|-----|-----------------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|------|------|

| 15  | I <sub>bus_PAS_do</sub><br>m      | Input leakage current<br>at the receiver with<br>pull-up resistor             | V(A+/B+) =12 V<br>[0x08].4 = LIN_PU_DIS = b0<br>V(TxD) = V <sub>TXDHIGH</sub><br>V(LIN/BSS) = V(GND)                                                                                                                                                                                                                                                                                                                                              | -1              | _    | -    | mA   |

| 16  | I <sub>bus_PAS_No</sub><br>PU_dom | Input leakage current<br>at the receiver w/o<br>pull-up resistor              | V(A+/B+) =12 V<br>[0x08].4 = LIN_PU_DIS = b1<br>V(TxD) = V <sub>TXDHIGH</sub><br>V(LIN/BSS) = V(GND)                                                                                                                                                                                                                                                                                                                                              | -0.85           | -    | -    | mA   |

| 17  | I <sub>bus_PAS_rec</sub>          | Transmitter input<br>current in recessive<br>state                            | V(TxD) = V <sub>TXDHIGH</sub><br>V(LIN/BSS) > 8 V<br>V(A+/B+) < 33 V<br>V(A+/B+)≤V(LIN/BSS) <v(a+ <br="">B+)+0.3</v(a+>                                                                                                                                                                                                                                                                                                                           | -               | -    | 20   | μA   |

| 18  | I <sub>bus_NO_GND</sub>           | Input current in case<br>of device GND loss                                   | V(A+/B+)=V(GND) = 12 V<br>0 V < V(LIN/BSS) < 33 V                                                                                                                                                                                                                                                                                                                                                                                                 | 0               | -    | 2    | mA   |

| 19  | I <sub>bus</sub>                  | Input current in case<br>of device A+/B+ loss                                 | V(A+/B+) = V(GND)<br>0 V < V(LIN/BSS) < 33 V                                                                                                                                                                                                                                                                                                                                                                                                      | -               | -    | 3.5  | mA   |

| LIN | /BSS transmit                     | tter                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |      |      | •    |

| 20  | V <sub>LINdom</sub>               | LIN/BSS bus voltage level in dominant state                                   | V(TxD)=V <sub>TXDLOW</sub><br>I(LIN/BSS) = 40 mA                                                                                                                                                                                                                                                                                                                                                                                                  | -               | -    | 1.35 | V    |

| 21  | V <sub>LINrec</sub>               | LIN/BSS bus voltage<br>level in recessive<br>state                            | V(A+/B+) =12 V<br>V(TxD) = V <sub>TXDHIGH</sub><br>I(LIN/BSS) = -10 μA                                                                                                                                                                                                                                                                                                                                                                            | 0.8<br>V(A+/B+) | _    | -    | V    |

| 22  | R <sub>LINup</sub>                | LIN/BSS bus pull up resistor                                                  | V(LIN/BSS) = V(GND)                                                                                                                                                                                                                                                                                                                                                                                                                               | 20              | 40   | 60   | kΩ   |

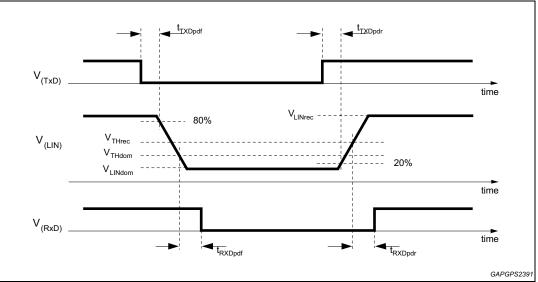

| LIN | /BSS timing                       |                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ·               |      | •    |      |

| 23  | SRf                               | LIN/BSS bus slew rate falling edge                                            | V(A+/B+)=12V<br>From 20% to 80% of<br>V(LIN/BSS)<br>(Rbus,Cbus) = (1 kΩ, 1 nF)                                                                                                                                                                                                                                                                                                                                                                    | 1               | 2    | 3    | V/µs |

| 24  | t <sub>RXpd</sub>                 | LIN/BSS-to-RxD<br>receiver                                                    | $\begin{array}{l} t_{\text{RXDpdf}} = t[0,5^* V(\text{RxD})] - \\ t[0,45^* V(\text{LIN/BSS})] \\ t_{\text{RXDpdr}} = t[0,5^* V(\text{RxD})] - \\ t[0,55^* V(\text{LIN/BSS})] \\ t_{\text{RXDpd}} = max(t_{\text{RXDpdr}}, t_{\text{RXDpdf}}) \\ C\text{RXD} = 20 \text{ pF} \\ V(\text{A+/B+}) = 12 \text{ V} \\ (\text{Rbus,Cbus}) = (1 \text{ k}\Omega, 1 \text{ nF}), \\ (660 \Omega, 6.8 \text{ nF}), (500 \Omega, 10 \text{nF}) \end{array}$ | -               | -    | 6    | μs   |

| 25  | t <sub>RXDpd_sym</sub>            | t <sub>RXDpd</sub> symmetry<br>(t <sub>RXDpdr</sub> Vs. t <sub>RXDpdf</sub> ) | tRXpd_sym = tRXpdr –<br>tRXpdf                                                                                                                                                                                                                                                                                                                                                                                                                    | -4              | -    | 4    | μs   |

| ١  | Symbol                 | Parameter                                                                     | Test condition                                                                                                                                                                                                                                                                                                                                                                                                                                           | Min.  | Тур. | Max.  | Unit |

|----|------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|

| 26 | t <sub>LINpd</sub>     | TxD-to-LIN/BBS<br>transmitter<br>propagation delay<br>time                    | $\begin{split} t_{\text{LINpdf}} &= t[0,45^*\text{V}(\text{LIN/BSS})] - \\ t[0,5^*\text{V}(\text{TxD})] \\ t_{\text{LINpdr}} &= t[0,55^*\text{V}(\text{LIN/BSS})] - \\ t[0,5^*\text{V}(\text{TxD})] \\ t_{\text{LINpd}} &= \max(t_{\text{LINpdr},t\text{LINpdf}}) \\ \text{V}(\text{A+/B+}) &= 12 \text{ V} \\ (\text{Rbus,Cbus}) &= (1 \text{ k}\Omega, 1 \text{ nF}), \\ (660 \ \Omega, 6.8 \text{ nF}), \\ (500 \ \Omega, 10 \text{ nF}) \end{split}$ | _     | -    | 10    | μs   |

| 27 | t <sub>LINpd_sym</sub> | t <sub>LINpd</sub> symmetry<br>(t <sub>LINpdr</sub> Vs. t <sub>LINpdf</sub> ) | t <sub>LINpd_sym</sub> =t <sub>LINpdr</sub> -t <sub>LINpdf</sub>                                                                                                                                                                                                                                                                                                                                                                                         | -4    | -    | 4     | μs   |

| 28 | D1                     | Duty cycle 1                                                                  | THRec(max)=0,744*V(A+/B+)<br>THDom(max)=0,581*V(A+/B+)<br>V(A+/B+)={7, 18}V<br>$t_{bit} = 50 \ \mu s$<br>D1= $t_{bus\_rec(min)}/(2*t_{bit})$<br>(Rbus,Cbus) = (1 kΩ,1 nF),<br>(660 Ω,6.8 nF), (500 Ω,10nF)                                                                                                                                                                                                                                               | 0.396 | -    | -     | _    |

| 29 | D2                     | Duty cycle 2                                                                  | TTHRec(min)=0,284*V(A+/B+)<br>THDom(min)=0,422*V(A+/B+)<br>V(A+/B+) = {7.6, 18} V<br>$t_{bit}$ =50 µs<br>D2= $t_{bus_rec}$ (max)/(2* $t_{bit}$ )<br>(Rbus,Cbus) = (1 kΩ,1 nF),<br>(660 Ω,6.8 nF), (500 Ω,10nF)                                                                                                                                                                                                                                           | -     | -    | 0.581 | -    |

| 30 | D3                     | Duty cycle 3                                                                  | THRec(max)=0,778*V(A+/B+)<br>THDom(max)=0,616*V(A+/B+)<br>V(A+/B+) = {7, 18}V<br>$t_{bit}$ = 96 µs;<br>D3 = $t_{bus\_rec(min)}/(2*t_{bit})$ ;<br>(Rbus,Cbus) = (1 kΩ,1 nF),<br>(660 Ω,6.8 nF), (500 Ω,10nF)                                                                                                                                                                                                                                              | 0.417 | -    | -     | -    |

| 31 | D4                     | Duty cycle 4                                                                  | THRec(min)=0,251*V(A+/B+)<br>THDom(min)=0,389*V(A+/B+)<br>V(A+/B+) = {7.6, 18}V;<br>$t_{bit} = 96 \ \mu s;$<br>D4 = $t_{bus\_rec(max)}/(2^{*}t_{bit});$<br>(Rbus,Cbus) = (1 k $\Omega$ ,1 nF),<br>(660 $\Omega$ ,6.8 nF), (500 $\Omega$ ,10nF)                                                                                                                                                                                                           | -     | -    | 0.590 | -    |

| 32 | t <sub>dom(TXD)</sub>  | TXD input dominant time-out                                                   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -     | 12   | -     | ms   |

24/84

|    | Table 14. Electrical characteristics pin Elin/B55 (continued) |                                   |                |      |      |      |      |

|----|---------------------------------------------------------------|-----------------------------------|----------------|------|------|------|------|

| ١  | Symbol                                                        | Parameter                         | Test condition | Min. | Тур. | Max. | Unit |

| 33 | t <sub>dom(LIN)</sub>                                         | LIN/BSS bus<br>dominant time-out  | -              | -    | 12   | -    | ms   |

| 34 | t <sub>rec(LIN)</sub>                                         | LIN/BSS bus<br>recessive time-out | -              | -    | 40   | -    | μs   |

Table 14. Electrical characteristics pin "LIN/BSS" (continued)

Figure 8. LIN/BSS transmit, receive timing

#### 5.3.6 Pin "DFM"

DFM is an output pin used to export a copy of the field PWM signal to external devices to allow a better system control. The DFM is internally connected to a low-side and to a highside that can be independently configured by the µC by properly setting SPI write registers 0x04 and 0x05 [13.4.13] [13.4.14].

Bits 4 and 5 of SPI register 0x04 are available to set DFM output configuration:

| DFM bit1 | DFM bit 0 | DFM output configuration |

|----------|-----------|--------------------------|

| 0        | 0         | DFM output disabled      |

| 0        | 1         | Low side driver enabled  |

| 1        | 0         | High side driver enabled |

| 1        | 1         | Push-pull enabled        |

#### Table 15. DFM output configuration

| # | Symbol                  | Parameter                                   | Test condition                             | Min. | Тур. | Max. | Unit |

|---|-------------------------|---------------------------------------------|--------------------------------------------|------|------|------|------|

| 1 | VML                     | Low-side saturation voltage                 | I(DFM) = 5 mA                              | 0.90 | 1.15 | 1.40 | V    |

| 2 | IML <sub>lim</sub>      | Low-side current<br>limitation              | -                                          | 25   | 50   | 75   | mA   |

| 3 | VMH                     | High side saturation voltage                | I(DFM) = -5 mA.Charge pump in<br>OFF state | 0.20 | 0.35 | 0.60 | V    |

| 4 | IMH <sub>lim</sub>      | High-side current<br>limitation             | -                                          | -75  | -50  | -25  | mA   |

| 5 | tML <sub>OCfilter</sub> | Low-side current<br>limitation filter time  | -                                          | -    | 30   | -    | μs   |

| 6 | tMH <sub>OCfilter</sub> | High-side current<br>limitation filter time | -                                          | -    | 30   | -    | μs   |

| 7 | VM <sub>TM</sub>        | Turbo mode threshold voltage                | -                                          | 42   | 46   | 50   | V    |

#### ----. . . . . ..

This pin can be used to notify the TURBO mode selection; TURBO mode bit (bit 4 of register 0x14, [13.4.8]) is set when the voltage on DFM pin goes above the VM<sub>TM</sub> and V(A+/B+)< VBIntOvp.

TURBO mode can be used by the application SW to skip all the delays to accelerate test procedures.

#### 5.3.7 Pin "PH"

The PH pin is an input for the phase signal coming from alternator's stator output. The internal comparator detects the presence of the phase signal when  $V(PH) > VP_{HTh}$ . The squared signal is forwarded to a period measurement unit that provides suitable timing data to the  $\mu$ C to compute the rotor speed.

If the phase signal falls below the  $VP_{prTh1}/VP_{prTh2}$  threshold the phase regulation request (bit 12 of SPI register 0x13 is set [13.4.7]).

The device exits the stand-by mode when an activity is detected on PH pin (i.e.  $V(PH)>VP_{HTh}$ ) independently on the status of other wake-up sources.

| # | Symbol                | Parameter                               | Test condition          | Min. | Тур. | Max. | Unit |  |

|---|-----------------------|-----------------------------------------|-------------------------|------|------|------|------|--|

| 1 | VP <sub>HTh</sub>     | High voltage comparator threshold       | V(AUX_IN)=V(GND)        | 200  | 280  | 360  | mV   |  |

| 2 | VP <sub>LTh</sub>     | Low voltage comparator threshold        | V(AUX_IN)=V(GND)        | 120  | 190  | 260  | mV   |  |

| 3 | tP <sub>SR</sub>      | Spike rejection time                    | Analogue filter         | -    | 30   | -    | μs   |  |

| 4 | IP <sub>pull-dw</sub> | Pull-down current                       | V(PH) = 28 V            | -    | 2    | -    | mA   |  |

| 5 | RP <sub>pull-dw</sub> | Passive pull-down resistance            | -                       | I    | 20   | -    | kΩ   |  |

| 6 | VP <sub>prTh1</sub>   | 12-V phase regulation voltage threshold | [0x2].12 = SEL24V_EN=b0 | 7    | 8    | 9    | V    |  |

| 7 | VP <sub>prTh2</sub>   | 24-V phase regulation voltage threshold | [0x2].12 = SEL24V_EN=b1 | 20   | 22.5 | 25   | V    |  |

Table 17. Electrical characteristics pin "PH"

#### 5.3.8 Pin "AUX\_IN"

The AUX\_IN pin can be used as auxiliary phase input signal in addition to PH pin. If not used, AUX\_IN pin must be tied to ground. It's forbidden to replace AUX\_IN pin with PH pin.

| # | Symbol                  | Parameter                         | Test condition   | Min. | Тур. | Max. | Unit |  |  |

|---|-------------------------|-----------------------------------|------------------|------|------|------|------|--|--|

| 1 | VAUX <sub>HTh</sub>     | High voltage comparator threshold | V(PH) = 1.150 V  | 200  | 280  | 360  | mV   |  |  |

| 2 | VAUX <sub>LTh</sub>     | Low voltage comparator threshold  | V(PH) = 1.150 V  | 120  | 190  | 260  | mV   |  |  |

| 3 | tAUX <sub>SR</sub>      | Spike rejection time              | Analogue filter  | -    | 30   | -    | μs   |  |  |

| 4 | IAUX <sub>pull-dw</sub> | Pull-down current                 | V(AUX_IN) = 28 V | -    | 50   | -    | μΑ   |  |  |

Table 18. Electrical characteristics pin "AUX\_IN"

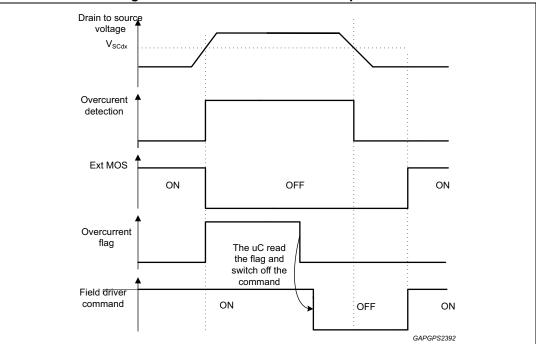

### 5.3.9 Pin "GATE"

The external power MOS provides a PWM regulated current to flow from the system battery into the field coil for system voltage regulation. The GATE pin provides the necessary current to turn-on and turn-off the external power MOS.

The gate-source-voltage of the external power MOS is limited by the driver circuit.

In order to drive different kinds of external power MOS and to adjust the gate currents according to environmental changes (e.g. temperature, emission levels, excitation signal edges duration) the gate charging and discharging currents are programmable via SPI, register 0x03 [13.4.12].

When the voltage between DRAIN an SOURCE pins become greater than  $V_{SCdx}$  the device switches the external power MOS off, activating a fast gate discharging current.