# L5962

## Multiple linear/switching voltage regulator for car-radio

### Features

- Step-down synchronous switching voltage regulator

- Internal high-side/ Low-side NDMOS

- 1.2 < V<sub>out</sub> < 8 V selectable through external resistors</li>

- 1.2/2.5 A load current selected through dedicated pin

- 185 kHz free-run frequency

- SYNC function (220 <  $f_{sw}$  < 400 kHz)

- Linear regulators

- 3.3/5 V @ 150 mA standby regulator selected through dedicated pin (VSTBYSEL)

- 5/8.5 V @ 350 mA switched linear regulator enabled and selected through I<sup>2</sup>C bus (VLR1)

- 3.3/10 V @ 1 A switched linear regulator enabled and selected through I<sup>2</sup>C bus (VLR2)

- 2 High side drivers (0.5 V max drop @ 0.5 A) enabled through I<sup>2</sup>C bus and equipped with protection circuit against:

- short to ground and battery

- loss of ground and battery

- unsupplied short to battery

- Reset function with configurable delay (RST, RSTDLY)

- I<sup>2</sup>C bus

#### Table 1. Device summary

- Enable pin to drive switching regulator and I<sup>2</sup>C bus logic

- Under/over voltage battery detector (VBATVW)

- Under voltage threshold adjustable through dedicated pin (LVWIN)

- Load dump protection

- Independent thermal protection on all regulators

## Description

L5962 is a very versatile device exploiting BCD technology characteristics to provide a complete set of regulated voltages covering all the needs of a car-radio set.

In standby condition the device guarantees extremely low quiescent current (90  $\mu$ A max - 40 °C < T < 85 °C) and minimum operating voltage (4.5 V using an external Schottky diode for the back-up function).

| Order code | Package   | Packing       |  |  |

|------------|-----------|---------------|--|--|

| L5962      | PowerSO36 | Tray          |  |  |

| L5962TR    | PowerSO36 | Tape and reel |  |  |

www.st.com

# Contents

| 1 | Block               | and application diagram5     |

|---|---------------------|------------------------------|

| 2 | Pin de              | escription                   |

| 3 | Electi              | rical specification          |

|   | 3.1                 | Absolute maximum ratings     |

|   | 3.2                 | Thermal data                 |

|   | 3.3                 | Electrical characteristics   |

| 4 | Devic               | e description                |

|   | 4.1                 | Regulators                   |

|   |                     | 4.1.1 Linear regulators      |

|   |                     | 4.1.2 Switching regulator    |

|   | 4.2                 | High side drivers 17         |

| 5 | Opera               | ating mode                   |

|   | 5.1                 | Battery detection            |

| 6 | l <sup>2</sup> C bu | us interface                 |

|   | 6.1                 | Data validity                |

|   | 6.2                 | Start and stop conditions 19 |

|   | 6.3                 | Byte format                  |

|   | 6.4                 | Acknowledge 19               |

| 7 | Softw               | are specifications           |

| 8 | Packa               | age information              |

| 9 | Revis               | ion history                  |

# List of tables

| Table 1. | Device summary              | l |

|----------|-----------------------------|---|

| Table 2. | Pin description 7           | 7 |

| Table 3. | Absolute maximum ratings    | ) |

|          | Thermal data                | ) |

| Table 5. | Electrical characteristics  | ) |

| Table 6. | Chip address                | l |

| Table 7. | IB1 data byte               | l |

| Table 8. | VLR2 output level selection | l |

| Table 9. | Document revision history   | 3 |

|          |                             |   |

| Figure 1. | Block diagram                                              | 5 |

|-----------|------------------------------------------------------------|---|

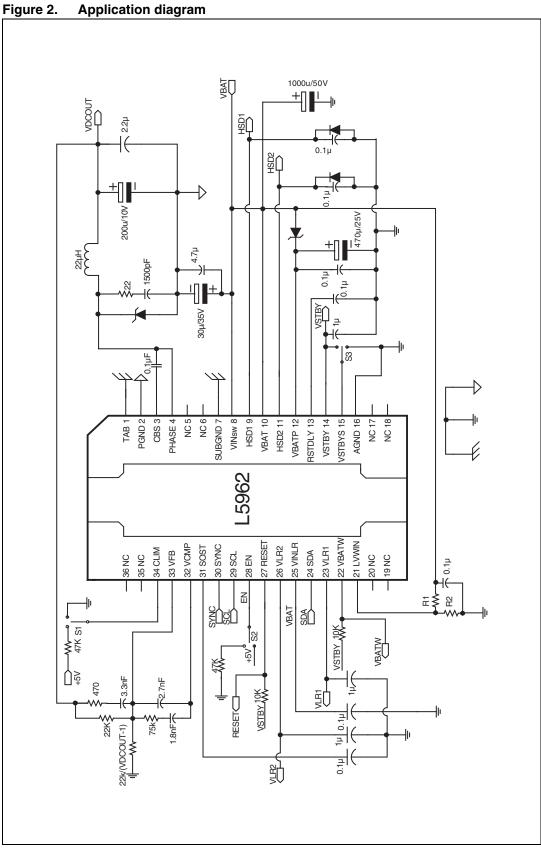

| Figure 2. | Application diagram                                        | 6 |

|           | Pin connection (top view)                                  |   |

| Figure 4. | Low voltage warning high level block diagram1              | 8 |

|           | Data validity on the I <sup>2</sup> C bus1                 |   |

| Figure 6. | Timing diagram on the I <sup>2</sup> C bus                 | 0 |

| Figure 7. | Acknowledge on the I <sup>2</sup> C bus                    | 0 |

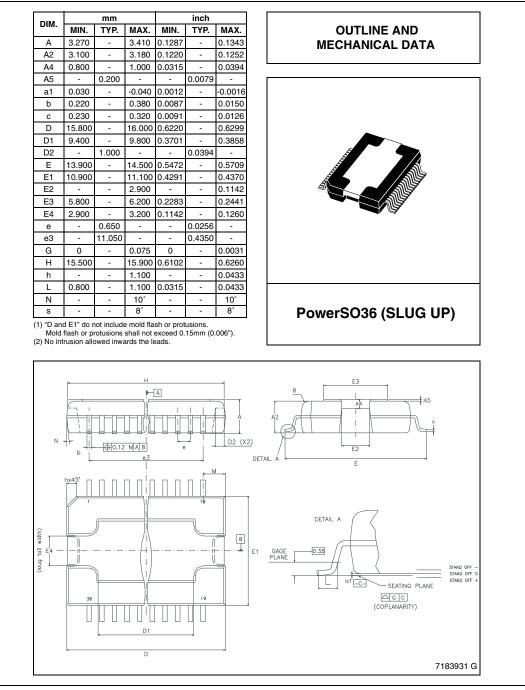

| Figure 8. | PowerSO36 (slug-up) mechanical data and package dimensions | 2 |

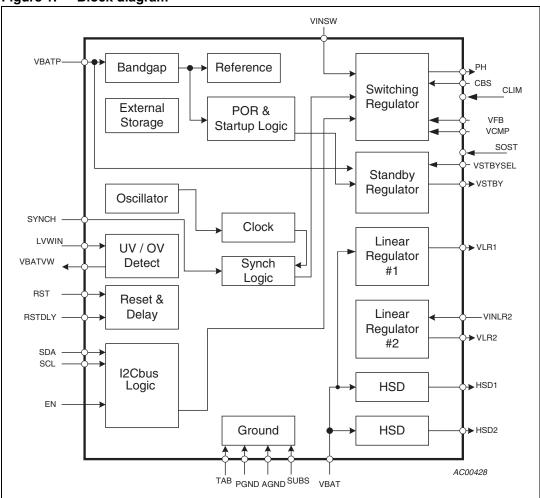

## **1** Block and application diagram

Figure 1. Block diagram

# 2 Pin description

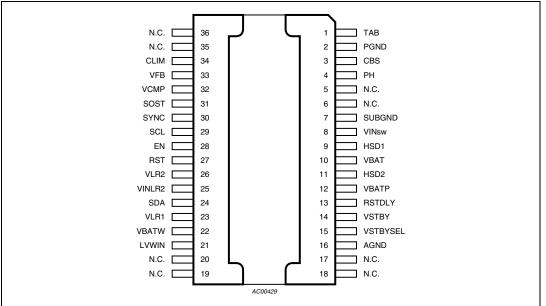

#### Figure 3. Pin connection (top view)

#### Table 2. Pin description

| Pin # | Pad name | Function                           | Description                                                                                                                |

|-------|----------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| 1     | TAB      |                                    | This pin must be connected to GND                                                                                          |

| 2     | PGND     | Switching regulator ground         | It is the power ground reference                                                                                           |

| 3     | CBS      | Bootstrap for switching regulator  | Bootstrap capacitor Input for the switching regulator                                                                      |

| 4     | PH       | Switching stage output             | Phase output. It is the switching output of the switching regulator. It also provides phase reference for bootstrap drive. |

| 5     | N.C.     | Not connected                      | -                                                                                                                          |

| 6     | N.C.     | Not connected                      | -                                                                                                                          |

| 7     | SUBGND   | Substrate ground                   | Substrate ground                                                                                                           |

| 8     | VINsw    | Switching regulator supply voltage | Battery voltage for the switching regulator                                                                                |

| 9     | HSD1     | High side driver 1                 | Output of the 1 <sup>st</sup> high side driver                                                                             |

| 10    | VBAT     | VLR1/HSD1/HSD2 supply voltage      | Voltage input for linear regulator #1 high side driver and battery warnings                                                |

| 11    | HSD2     | High side driver 2                 | Output of the 2 <sup>nd</sup> high side driver                                                                             |

| 12    | VBATP    | Standby regulator supply voltage   | Protected battery input for bias, bandgap, oscillator, and VSTBY regulator                                                 |

| 13    | RSTDLY   | Reset delay function               | Input                                                                                                                      |

| 14    | VSTBY    | Standby regulator output           | Output of the standby regulator                                                                                            |

| Pin # | Pad name | Function                                   | Description                                                 |

|-------|----------|--------------------------------------------|-------------------------------------------------------------|

| 15    | VSTBYSEL | Standby regulator selector                 | Selection input for standby regulator output (3.3 V or 5 V) |

| 16    | AGND     | Analog ground                              | Analog voltage reference                                    |

| 17    | N.C.     | Not connected                              | -                                                           |

| 18    | N.C.     | Not connected                              | -                                                           |

| 19    | N.C.     | Not connected                              | -                                                           |

| 20    | N.C.     | Not connected                              | -                                                           |

| 21    | LVWIN    | Battery detector adjustment input          | Low-voltage warning input                                   |

| 22    | VBATW    | Battery detector output (open-drain)       | Battery voltage warning output                              |

| 23    | VLR1     | Switched linear regulator 1                | Output of the 1 <sup>st</sup> linear regulator              |

| 24    | SDA      | I <sup>2</sup> C bus data                  | I <sup>2</sup> C data line                                  |

| 25    | VINLR2   | VLR2 supply voltage                        | Battery supply for the 2 <sup>nd</sup> linear regulator     |

| 26    | VLR2     | Switched linear regulator 2                | Output of the 2 <sup>nd</sup> linear regulator              |

| 27    | RST      | Reset                                      | Output                                                      |

| 28    | EN       | Enable                                     | Active mode enable input. Active high                       |

| 29    | SCL      | I <sup>2</sup> C bus clock                 | I <sup>2</sup> C clock source supplied by the master device |

| 30    | SYNC     | Switching regulator SYNC function          | Synchronization Input                                       |

| 31    | SOST     | Switching regulator soft-start             | Soft start external capacitor                               |

| 32    | VCMP     | Switching regulator compensation           | Feedback compensation input.                                |

| 33    | VFB      | Switching regulator feedback               | Regulated output voltage sense                              |

| 34    | CLIM     | Switching regulator current limit selector | Choose between two current limits                           |

| 35    | N.C.     | Not connected                              | -                                                           |

| 36    | N.C.     | Not connected                              | -                                                           |

Table 2.

Pin description (continued)

# 3 Electrical specification

## 3.1 Absolute maximum ratings

| Pin name/Symbol            | Parameter                                                                                 | Value                | Unit |

|----------------------------|-------------------------------------------------------------------------------------------|----------------------|------|

| Vs <sub>MAX</sub>          | Operating supply voltage (VBAT,<br>VBATP, VINSW, VINLR2)                                  | -0.3 to 27           | V    |

|                            | Transient supply voltage (VBAT,<br>VBATP, VINSW, VINLR2) -0.3 to 50                       |                      | V    |

| Vpin <sub>MAX</sub>        | Input pin voltage<br>(EN, RSTDLY, VSTBYSEL, SYNCH,<br>SCL, SDA, VCMP, VFB, CLIM,<br>SOST) | LY, VSTBYSEL, SYNCH, |      |

| agnd, pgnd,<br>Subgnd, tab | Ground pin voltage                                                                        | -0.3 to +0.3         | V    |

| T <sub>op</sub>            | Operating temperature range                                                               | -40 to 85            | °C   |

| T <sub>stg</sub>           | Storage temperature range                                                                 | -55 to 150           | °C   |

#### Table 3. Absolute maximum ratings

### 3.2 Thermal data

#### Table 4. Thermal data

| Symbol                 | Parameter                                 | Value | Unit |

|------------------------|-------------------------------------------|-------|------|

| R <sub>th j-case</sub> | Thermal resistance junction-to-case (max) | 2     | °C/W |

### 3.3 Electrical characteristics

VBAT= VINSW = VINLR2 = 14.4 V,  $T_{amb}$  = 25 °C unless otherwise specified.

| Table 5. Electrical characteristic | 5 |

|------------------------------------|---|

|------------------------------------|---|

| Symbol            | Parameter                     | Test conditions                                                           | Min. | Тур. | Max.     | Unit |  |  |  |

|-------------------|-------------------------------|---------------------------------------------------------------------------|------|------|----------|------|--|--|--|

| Input supplies    | Input supplies                |                                                                           |      |      |          |      |  |  |  |

| V <sub>min</sub>  | VBATP operating voltage       | -                                                                         | 4.1  | -    | -        | V    |  |  |  |

| ۱ <sub>q</sub>    | Total quiescent current       | EN = 0; I <sub>VSTBY</sub> =100 μA<br>@ T = -40 °C<br>@ 25 °C < T < 85 °C | -    | -    | 90<br>75 | μA   |  |  |  |

| V <sub>OV</sub>   | Overvoltage shut-down         | VBAT rising                                                               | 27   | 29   | 31       | V    |  |  |  |

| HYS <sub>OV</sub> | Hysteresis on V <sub>OV</sub> | -                                                                         | -    | 400  | -        | mV   |  |  |  |

| V <sub>UV</sub>   | VBAT undervoltage threshold   | VBAT falling;<br>VBATVW transition to 0 V                                 | 7    | 7.5  | 8        | V    |  |  |  |

| Symbol                       | Parameter                                       | Test conditions                                                                            | Min. | Тур. | Max. | Unit |

|------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------|------|------|------|------|

| HYS <sub>UV</sub>            | Hysteresis on V <sub>UV</sub>                   | -                                                                                          | -    | 1    | -    | V    |

| VSTBY (3.3 V)                |                                                 |                                                                                            |      |      |      |      |

| Vout <sub>VSTBY3</sub>       | Output voltage                                  | 0 < I <sub>load</sub> < 150 mA                                                             | 3.2  | 3.3  | 3.4  | V    |

| LnR <sub>VSTBY3</sub>        | Line regulation                                 | 4.1 <vbatp<18v<br>I<sub>load</sub>=150mA</vbatp<18v<br>                                    | -10  | -    | +50  | mV   |

| LdR <sub>VSTBY3</sub>        | Load regulation                                 | 0 <i<sub>load&lt;150mA</i<sub>                                                             | -    | -    | 20   | mV   |

| Vdo <sub>VSTBY3</sub>        | Drop out voltage                                | I <sub>load</sub> =150mA                                                                   | -    | -    | 600  | mV   |

| Ishort <sub>VSTBY3</sub>     | Short circuit current limit                     | -                                                                                          | 250  | -    | 450  | mA   |

| OS/US <sub>VSTBY3</sub>      | Overshoot/Undershoot                            | $I_{load} 0 \leftrightarrow 150 \text{ mA, t} > 50 \mu \text{s}$<br>C = 1 $\mu$ F ceramic  | -    | -    | ±5   | %    |

| PSRR <sub>VSTBY3</sub>       | Power supply rejection ratio                    | $I_{load} = 50 \text{ mA}$<br>120 Hz < f < 10 kHz<br>VBATP <sub>ac</sub> = 1 Vpp           | 70   | -    | -    | dB   |

| n <sub>VSTBY3</sub>          | Output noise                                    | A-weighted filter<br>20 Hz < f < 20 kHz<br>I <sub>load</sub> = 5 mA                        | -    | -    | 200  | μV   |

| TS <sub>VSTBY3</sub>         | Thermal shut-down temperature                   | Temperature rising                                                                         | 150  | -    | 190  | °C   |

| HYS <sub>TS-VSTBY3</sub>     | Hysteresis on thermal shut-<br>down temperature | -                                                                                          | 5    | -    | 15   | °C   |

| ESR <sub>VSTBY3</sub>        | External filtering capacitor ESR                | C > 0.5 µF                                                                                 | -    | -    | 0.2  | Ω    |

| VSTBY (5 V)                  |                                                 | · · · · · · · · · · · · · · · · · · ·                                                      |      |      |      |      |

| Vout <sub>VSTBY5</sub>       | Output voltage                                  | 0 < I <sub>load</sub> < 150 mA                                                             | 4.80 | 5    | 5.15 | V    |

| LnR <sub>VSTBY5</sub>        | Line regulation                                 | 6 <vbatp<18v i<sub="">load=150mA</vbatp<18v>                                               | -10  | -    | +60  | mV   |

| LdR <sub>VSTBY5</sub>        | Load regulation                                 | 0 < I <sub>load</sub> < 150 mA                                                             | -    | -    | 25   | mV   |

| Vdo <sub>VSTBY5</sub>        | Drop out voltage                                | I <sub>load</sub> = 150 mA                                                                 | -    | -    | 600  | mV   |

| Ishort <sub>VSTBY5</sub>     | Short circuit current limit                     | -                                                                                          | 250  | -    | 450  | mA   |

| OS/US <sub>VSTBY5</sub>      | Overshoot/Undershoot                            | $I_{load} 0 \leftrightarrow 150 \text{ mA, } t > 50 \mu \text{s}$<br>C = 1 $\mu$ F ceramic | -    | -    | ±5   | %    |

| PSRR <sub>VSTBY5</sub>       | Power supply rejection ratio                    | $I_{load} = 50 \text{ mA}$<br>120 Hz < f < 10 kHz<br>VBATP <sub>ac</sub> =1 Vpp            | 70   | -    | -    | dB   |

| n <sub>VSTBY5</sub>          | Output noise                                    | A-weighted filter<br>20 Hz < f < 20 kHz<br>I <sub>load</sub> = 5 mA                        | -    | -    | 200  | μV   |

| TS <sub>VSTBY5</sub>         | Thermal shut-down temperature                   | Temperature rising                                                                         | 150  | -    | 190  | °C   |

| HYS <sub>TS-</sub><br>vstby5 | Hysteresis on thermal shut-<br>down temperature | -                                                                                          | 5    | -    | 15   | °C   |

| ESR <sub>VSTBY5</sub>        | External filtering capacitor ESR                | C > 0.5 μF                                                                                 | -    | -    | 0.2  | Ω    |

Table 5. Electrical characteristics (continued)

10/24

| Symbol                   | Parameter                                       | Test conditions                                                                            | Min. | Тур. | Max. | Unit |

|--------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------|------|------|------|------|

| VLR1 (5 V)               |                                                 |                                                                                            |      |      |      |      |

| Vout <sub>VLR1-5</sub>   | Output voltage                                  | 0 < I <sub>load</sub> < 350 mA                                                             | 4.85 | 5    | 5.15 | V    |

| LnR <sub>VLR1-5</sub>    | Line regulation                                 | 6 <vbat<18 i<sub="" v="">load =350 mA</vbat<18>                                            | -25  | -    | +25  | mV   |

| LdR <sub>VLR1-5</sub>    | Load regulation                                 | 0 < I <sub>load</sub> < 350 mA                                                             | -90  | -    | -    | mV   |

| Vdo <sub>VLR1-5</sub>    | Drop out voltage                                | I <sub>load</sub> = 350 mA                                                                 | -    | -    | 650  | mV   |

| Ishort <sub>VLR1-5</sub> | Short circuit current limit                     | -                                                                                          | 500  | 650  | 850  | mA   |

| OS/US <sub>VLR1-5</sub>  | Overshoot/Undershoot                            | $I_{load} 0 \leftrightarrow 350 \text{ mA, } t > 50 \mu \text{s}$<br>C = 1 $\mu$ F ceramic | -    | -    | ±3   | %    |

| PSRR <sub>VLR1-5</sub>   | Power supply rejection ratio                    | I <sub>load</sub> = 170 mA<br>120 Hz < f < 10 kHz<br>VBAT <sub>ac</sub> =1 Vpp             | 60   | -    | -    | dB   |

| n <sub>VLR1-5</sub>      | Output noise                                    | A-weighted filter<br>20 Hz < f < 20 kHz<br>I <sub>load</sub> = 5 mA                        | -    | -    | 350  | μV   |

| TS <sub>VLR1-5</sub>     | Thermal shut-down<br>temperature                | Temperature rising                                                                         | 150  | -    | 190  | °C   |

| HYS <sub>TS-VLR1-5</sub> | Hysteresis on thermal shut-<br>down temperature | -                                                                                          | 5    | -    | 15   | °C   |

| ESR <sub>VLR1-5</sub>    | External filtering capacitor ESR                | C > 0.5 μF                                                                                 | -    | -    | 0.2  | Ω    |

| VLR1 (8.5 V)             |                                                 |                                                                                            |      |      |      |      |

| Vout <sub>VLR1-8</sub>   | Output voltage                                  | 0 < I <sub>load</sub> < 350 mA                                                             | 8.3  | 8.5  | 8.7  | V    |

| LnR <sub>VLR1-8</sub>    | Line regulation                                 | 9.6 <vbat<18vi<sub>load=350mA</vbat<18vi<sub>                                              | -25  | -    | +25  | mV   |

| LdR <sub>VLR1-8</sub>    | Load regulation                                 | 0 < I <sub>load</sub> < 350 mA                                                             | -90  | -    | -    | mV   |

| Vdo <sub>VLR1-8</sub>    | Drop out voltage                                | I <sub>load</sub> = 350 mA                                                                 | -    | -    | 650  | mV   |

| Ishort <sub>VLR1-8</sub> | Short circuit current limit                     | -                                                                                          | 500  | 650  | 850  | mA   |

| OS/US <sub>VLR1-8</sub>  | Overshoot / undershoot                          | $I_{load} 0 \leftrightarrow 350 \text{ mA, t} > 50 \mu \text{s}$<br>C = 1 $\mu$ F ceramic  | -    | -    | ±3   | %    |

| PSRR <sub>VLR1-8</sub>   | Power supply rejection ratio                    | l <sub>load</sub> = 170 mA<br>120 Hz < f < 10 kHz<br>VBAT <sub>ac</sub> =1 Vpp             | 60   | -    | -    | dB   |

| n <sub>VLR1-8</sub>      | Output noise                                    | A-weighted filter<br>20 Hz < f < 20 kHz<br>I <sub>load</sub> = 5 mA                        | -    | -    | 350  | μV   |

| TS <sub>VLR1-8</sub>     | Thermal shut-down<br>temperature                | Temperature rising                                                                         | 150  | -    | 190  | °C   |

| HYS <sub>TS-VLR1-8</sub> | Hysteresis on thermal shut-<br>down temperature | -                                                                                          | 5    | -    | 15   | °C   |

| ESR <sub>VLR1-8</sub>    | External filtering capacitor ESR                | C > 0.5 µF                                                                                 | -    | -    | 0.2  | Ω    |

Table 5. Electrical characteristics (continued)

| Symbol                    | Electrical characteristics (co<br>Parameter     | Test conditions                                                                       | Min. | Тур. | Max. | Unit |

|---------------------------|-------------------------------------------------|---------------------------------------------------------------------------------------|------|------|------|------|

| VLR2 (3.3 V)              |                                                 |                                                                                       |      |      |      |      |

|                           | Output voltage                                  | 0.1.1.1.0                                                                             | 3.2  | 2.0  | 3.4  | V    |

| Vout <sub>VLR2-3</sub>    | Output voltage                                  | $0 < I_{load} < 1 \text{ A}$                                                          | 3.2  | 3.3  | 3.4  | V    |

| LnR <sub>VLR2-3</sub>     | Line regulation                                 | 4.5 < VINLR2 < 18 V<br>I <sub>load</sub> = 1 A                                        | -20  | -    | +20  | mV   |

| LdR <sub>VLR2-3</sub>     | Load regulation                                 | 0 < I <sub>load</sub> < 1 A                                                           | -70  | -    | -    | mV   |

| Vdo <sub>VLR2-3</sub>     | Drop out voltage                                | I <sub>load</sub> = 1 A                                                               | -    | -    | 1.2  | V    |

| Ishort <sub>VLR2-3</sub>  | Short circuit current limit                     |                                                                                       | 1.5  | -    | 2.5  | Α    |

| OS/US <sub>VLR2-3</sub>   | Overshoot / undershoot                          | $I_{load} 0 \leftrightarrow 1A, t > 50 \mu s$<br>C = 1 $\mu$ F ceramic                | -    | -    | ±3   | %    |

| PSRR <sub>VLR2-3</sub>    | Power supply rejection ratio                    | l <sub>load</sub> = 500 mA<br>120 Hz < f < 10 kHz<br>VINLR2 <sub>ac</sub> =1 Vpp      | 60   | -    | -    | dB   |

| n <sub>VLR2-3</sub>       | Output noise                                    | A-weighted filter<br>20Hz <f<20khz<br>I<sub>load</sub>=5mA</f<20khz<br>               | -    | -    | 350  | μV   |

| TS <sub>VLR2-3</sub>      | Thermal shut-down<br>temperature                | Temperature rising                                                                    | 150  | -    | 190  | °C   |

| HYS <sub>TS-VLR2-3</sub>  | Hysteresis on thermal shut-<br>down temperature | -                                                                                     | 5    | -    | 15   | °C   |

| ESR <sub>VLR2-3</sub>     | External filtering capacitor ESR                | C>0.5µF                                                                               | -    | -    | 0.2  | Ω    |

| VLR2 (10 V)               |                                                 |                                                                                       | ·    |      |      |      |

| Vout <sub>VLR2-10</sub>   | Output voltage                                  | 0 <i<sub>load&lt;1 A</i<sub>                                                          | 9.7  | 10   | 10.3 | V    |

| LnR <sub>VLR2-10</sub>    | Line regulation                                 | 11.4 <vbat<18 v<br="">I<sub>load</sub>=1 A</vbat<18>                                  | -25  | -    | +25  | mV   |

| LdR <sub>VLR2-10</sub>    | Load regulation                                 | 0 <i<sub>load&lt;1 A</i<sub>                                                          | -70  | -    | -    | mV   |

| Vdo <sub>VLR2-10</sub>    | Drop out voltage                                | I <sub>load</sub> =1 A                                                                | -    | -    | 0.75 | V    |

| Ishort <sub>VLR2-10</sub> | Short circuit current limit                     |                                                                                       | 1.5  | -    | 2.5  | Α    |

| OS/US <sub>VLR2-10</sub>  | Overshoot / undershoot                          | $I_{load} 0 \leftrightarrow 1 A, t > 50 \ \mu s$<br>C = 1 \mu F ceramic               | -    | -    | ±3   | %    |

| PSRR <sub>VLR2-10</sub>   | Power supply rejection ratio                    | I <sub>load</sub> = 500 mA<br>120 Hz <f<10 khz<br="">VINLR2<sub>ac</sub>=1 Vpp</f<10> | 60   | -    | -    | dB   |

| n <sub>VLR2-10</sub>      | Output noise                                    | A-weighted filter<br>20 Hz < f < 20 kHz<br>I <sub>load</sub> = 5 mA                   | -    | -    | 350  | μV   |

| TS <sub>VLR2-10</sub>     | Thermal shut-down<br>temperature                | Temperature rising                                                                    | 150  | -    | 190  | °C   |

| HYS <sub>TS-VLR2-10</sub> | Hysteresis on thermal shut-<br>down temperature | -                                                                                     | 5    | -    | 15   | °C   |

| ESR <sub>VLR2-10</sub>    | External filtering capacitor ESR                | C > 0.5 µF                                                                            | -    | -    | 0.2  | Ω    |

Table 5.

Electrical characteristics (continued)

12/24

| Symbol                 | Parameter                                       | Test conditions                                                                       | Min.       | Тур. | Max.   | Unit |

|------------------------|-------------------------------------------------|---------------------------------------------------------------------------------------|------------|------|--------|------|

| HSD1                   |                                                 |                                                                                       |            |      |        |      |

| Vdrop <sub>HSD1</sub>  | Output saturation                               | $I_{load} = 0.5 A$                                                                    | -          | -    | 500    | mV   |

| lleak <sub>HSD1</sub>  | Leakage current                                 | HSD off<br>output shorted to GND                                                      | -          | -    | 10     | μA   |

| Ishort <sub>HSD1</sub> | Short circuit current limit                     | -                                                                                     | 0.75       | -    | 1.5    | А    |

| TS <sub>HSD1</sub>     | Thermal shut-down temperature                   | Temperature rising                                                                    | 150        | -    | 190    | °C   |

| HYS <sub>TS-HSD1</sub> | Hysteresis on thermal shut-<br>down temperature | -                                                                                     | 5          | -    | 15     | °C   |

| HSD2                   |                                                 |                                                                                       |            |      |        |      |

| Vdrop <sub>HSD2</sub>  | Output saturation                               | $I_{load} = 0.5 A$                                                                    | -          | -    | 500    | mV   |

| lleak <sub>HSD2</sub>  | Leakage current                                 | HSD off<br>output shorted to GND                                                      | -          | -    | 10     | μA   |

| Ishort <sub>HSD2</sub> | Short circuit current limit                     | -                                                                                     | 0.75       | -    | 1.5    | А    |

| TS <sub>HSD2</sub>     | Thermal shut-down temperature                   | Temperature rising                                                                    | 150        | -    | 190    | °C   |

| HYS <sub>TS-HSD2</sub> | Hysteresis on thermal shut-<br>down temperature | -                                                                                     | 5          | -    | 15     | °C   |

| Switching reg          | julator                                         |                                                                                       |            | •    | •      | •    |

| Vout <sub>SW</sub>     | Output voltage                                  | Selectable through external resistor divider                                          | 1.2        | -    | 8      | V    |

| I <sub>LOADmaxSW</sub> | Load current limitation                         | V <sub>outSW</sub> decreasing of<br>100 mV <sup>(1)</sup><br>CLIM = 0 V<br>CLIM = 5 V | 1.2<br>2.5 | -    | 3<br>6 | A    |

| f <sub>sw</sub>        | Free-run switching frequency                    | -                                                                                     | 150        | 180  | 210    | kHz  |

| $V_{FB}$               | FB voltage                                      | -                                                                                     | 970        | -    | 1030   | mV   |

| Vdrop <sub>SW</sub>    | Dropout voltage                                 | $Vout_{SW} = 8 V$<br>$Iload_{SW} = 2.5 A^{(1)}$                                       | -          | -    | 1.2    | V    |

| f <sub>SYNC</sub>      | Switching frequency selectable through SYNC pin | -                                                                                     | 220        | -    | 400    | kHz  |

| η                      | Efficiency                                      | free run frequency <sup>(1)</sup><br>$V_{outSW} = 8 V$ ; $I_{load} = 2.5 A$           | 85         | -    | -      | %    |

| SR <sub>SS</sub>       | Soft-start pin slew rate                        | $C_{SOST} = 10 \text{ nF}^{(1)}$                                                      | -          | -    | 10     | V/ms |

| TS <sub>SW</sub>       | Thermal shut-down temperature                   | Temperature rising                                                                    | 150        | -    | 190    | °C   |

| HYS <sub>SW</sub>      | Hysteresis on thermal shut-<br>down temperature | -                                                                                     | 5          | -    | 15     | °C   |

| Table 5. | Electrical characteristics | (continued) |

|----------|----------------------------|-------------|

|          |                            | (           |

| Symbol                 | Parameter                              | Test conditions           | Min.  | Тур. | Max.  | Unit |  |

|------------------------|----------------------------------------|---------------------------|-------|------|-------|------|--|

| Reset functio          | n                                      |                           |       |      |       |      |  |

| THR <sub>RST</sub>     | Reset threshold on VSTBY               | VSTBY = 3.3 V             | 93    | -    | 98    | %    |  |

| HYS <sub>RST</sub>     | Hysteresis on RST                      | -                         | 30    | -    | 150   | mV   |  |

| Vsat <sub>RST</sub>    | RST pin saturation voltage             | I <sub>RST</sub> = 0.5 mA | -     | -    | 0.4   | V    |  |

| DLY <sub>RST</sub>     | RST delay time                         | C = 100 pF on RSTDLY pin  | 25    | -    | 75    | μs   |  |

| Tfall <sub>RST</sub>   | RST fall time                          | R = 47 kΩ<br>C = 50 pF    | -     | -    | 1     | μs   |  |

| Tglitch <sub>RST</sub> | Glitch filter time for RST             | -                         | 5     | -    | 20    | μs   |  |

| THR <sub>RSTDLY</sub>  | RSTDLY pin threshold                   | RST falling               | 3     | -    | 3.7   | V    |  |

| IRSTDLY                | RSTDLY output current                  | RSTDLY = Off              | 7     | -    | 13    | μA   |  |

| Controls               |                                        |                           |       |      |       |      |  |

| тир                    | EN minimum level recognized as high    | -                         | 2     | -    | -     | V    |  |

| THR <sub>EN</sub>      | EN maximum level recognized as low     | -                         |       | -    | 0.8   | V    |  |

| HYS <sub>EN</sub>      | Hysteresis on EN                       | -                         | 150   | -    | -     | mV   |  |

| leak <sub>EN</sub>     | EN pin leakage current                 | -                         | -1    | -    | 1     | μA   |  |

| TUD                    | CLIM pin threshold                     | -                         | 0.8   | -    | -     | - V  |  |

| THR <sub>CLIM</sub>    |                                        | -                         |       | -    | 2     |      |  |

| leak <sub>CLIM</sub>   | CLIM pin leakage current               | -                         | -1    | -    | 1     | μA   |  |

| THR <sub>LVWIN</sub>   | LVWIN threshold                        | -                         | 1.225 | -    | 1.275 | V    |  |

| HYST <sub>LVWIN</sub>  | LVWIN hysteresis                       | -                         | 100   | -    | 200   | mV   |  |

| I <sup>2</sup> C bus   |                                        |                           |       |      |       |      |  |

| THR <sub>SCL</sub>     | CLOCK minimum level recognized as High | -                         | 2.2   | -    | -     | V    |  |

|                        | CLOCK maximum level recognized as low  | -                         | -     | -    | 0.8   | v    |  |

| <b>T</b> 115           | DATA minimum level recognized as High  | -                         | 2.2   | -    | -     | V    |  |

| THR <sub>SDA</sub>     | DATA maximum level recognized as low   | -                         | -     | -    | 0.8   | V    |  |

| f <sub>SCL</sub>       | Clock frequency                        | -                         | -     | -    | 400   | kHz  |  |

Table 5. Electrical characteristics (continued)

1. by bench characterization

## 4 Device description

The IC includes one standby regulator, always active to guarantee the standby functions; two switched linear regulators, managed by the I<sup>2</sup>C bus and a step-down switching voltage regulator with selectable current limit.

### 4.1 Regulators

The VSTBY regulator is always active when the IC is supplied.

The other regulators can be enabled or disabled. Their outputs are automatically disabled whenever the VBAT voltage exceeds the over-voltage shutdown threshold. Upon return from over-voltage shutdown, the outputs recover without intervention from the system.

#### 4.1.1 Linear regulators

#### VSTBY (3.3 V / 5.0 V standby)

VSTBY is a linearly regulated 3.3/5 V output. This output is enabled on battery connect. It is supplied from the protected battery input (VBATP).

In order to select the 3.3 V output, the VSTBYSEL pin must be connected to ground.

In order to select the 5.0 V output, the VSTBYSEL pin must be connected to 5 V.

When the dropout voltage of the regulator cannot be maintained, the output shall track the VBATP input voltage less the saturation voltage of the regulator pass element.

This regulator has a short circuit protection consisting of current limit, and thermal shutdown. If the local die temperature exceeds the thermal shutdown detection threshold, the output is disabled. The thermal shutdown circuitry has hysteresis such that the output is enabled only after the die temperature falls below the thermal shutdown disable threshold. Thermal shutdown on this output doesn't directly disable any other circuitry.

RST provides an indication that VSTBY is in regulation. It is an open drain output used to indicate that VSTBY is in regulation (below the low-voltage threshold). RST remains low until VSTBY achieves regulation and the RSTDLY input has charged to its threshold. For instance, RST remains low during battery connect and disconnect and under low-voltage battery lockout. The transition from standby mode to active mode (and vice versa) does not cause the RST output to be triggered.

RSTDLY provides a means to delay the releasing of RST once VSTBY has achieved regulation. It is used to delay the release of RST when VSTBY achieves regulation. This input has a current source to charge an external capacitor and an internal pull-down to discharge the external capacitor. The voltage on this capacitor is used to control the operation of the RST output.

The RSTDLY pull-down is activated when a loss of regulation is detected. The input remains low until VSTBY once again achieves regulation.

When the RSTDLY is released the current source charges the external capacitor. When the voltage exceeds the pin's threshold, RST pin is also released, disabling its pull-down.

#### VLR1 (5.0 V /8.5 V) and VLR2 (3.3 V, 5.0 V, 5.5 V, 6.0 V, 7.0 V, 7.5 V, 8.0 V, 10.0 V)

The output of these two regulators can be selected through the I<sup>2</sup>C bus.

When the dropout voltage of the regulator cannot be maintained, the output tracks the VBAT input voltage less the saturation voltage of the regulator pass element.

This regulator has a short circuit protection consisting of current limit and thermal shutdown. If the local die temperature exceeds the thermal shutdown detection threshold, the output is disabled. The thermal shutdown circuitry has hysteresis such that the output is enabled only after the die temperature falls below the thermal shutdown disable threshold. Thermal shutdown on this output doesn't directly disable any other circuitry.

VLR2 has its own power supply (VINLR2) because of its high current capability.

#### 4.1.2 Switching regulator

The IC contains an independent, step-down, synchronous switching regulator, which is used to produce an output voltage that is adjustable in the system by means of an external resistor divider.

The switching regulator functionality is guaranteed in the 1.2-8.0 V output voltage range. The switching frequency is externally synchronizable. The switcher has its own supply input pin (VINSW) and is enabled by the EN input.

The regulator contains soft-start control to protect external devices from excessive in-rush currents. This control is independent of the presence of a synchronizing signal on the SYNCH input.

The switching cycle is synchronized to the internal oscillator unless a signal is present on the SYNC input. The signal present on the SYNCH input overrides the internal oscillator to control the switching of the regulator if its frequency gets inside the allowed range (220-400 kHz). The IC detects a small number of edges (e.g. 2-5) prior to recognize a valid input signal and synchronizing internal operation to the external signal.

It is designed to operate in continuous conduction mode (CCM), where the inductor current remains continuous throughout the entire load range of the output. It can also work in DCM mode.

This regulator has short circuit protection consisting of cycle-by-cycle duty-cycle limitation.

Upon return from over-voltage shutdown this regulator employs the soft-start.

An external bootstrap capacitor must be connected between the output (PH, phase output pin) and the CBS pin.

The switching regulator output slew rate can be controlled with an external capacitor on the SOST (soft start) pin. This protects the device against excessive dV/dt transients, lowering the stress of the internal components. A maximum slews rate of 10 V/ms is suggested.

Two separate current limits for the switching regulator can be chosen in order to guarantee a proper protection for the device at the desired load current rating. The CLIM pin should be tied to ground for the low limit (max 3 A) or to 5.0 V for the high limit (max 6 A).

The VFB pin is the voltage feedback from the regulated output for the switching regulator; the VCMP one is the compensation feedback for the switching regulator.

### 4.2 High side drivers

The device embeds fully-protected high-side drivers for use outside of the car-radio module.

#### HSD1, HSD2

These high side driver outputs have short circuit protections consisting of current limit and independent thermal shutdown. If the local die temperature exceeds the thermal shutdown detection threshold, the output is disabled. The thermal shutdown circuitry has hysteresis such that the output is enabled only after the die temperature falls below the thermal shutdown disable threshold. Thermal shutdown on any one output doesn't directly disable any other circuitry.

HSD1 and HSD2 are protected from shorts to ground and shorts to battery (0-18 V) during a loss of car-radio module battery.

## 5 Operating mode

When a power source is connected to the IC, the internal circuitry begins to establish internal bias, the bandgap reference voltage, and other related functions. The standby (VSTBY) regulator and battery detection are functional.

The standby mode is activated when the enable (EN) input is asserted low.

When the enable (EN) input is set high (EN =1: active mode.), the IC exits the standby mode and enters the active mode.

During active mode, I2C interface is activated and all functions are operational. The IC remains in active mode until either the standby regulator falls out of regulation (where the IC enters the low-voltage reset state) or until the enable (EN) input is brought back to 0 V (where the IC enters the standby state).

### 5.1 Battery detection

The operating voltage for VLR1, high side drivers and battery warnings is provided by VBAT pin. This input is also used as reference to detect an over-voltage or an under-voltage condition. When such condition is detected, the VBATVW output is pulled down. The overvoltage detection circuit has hysteresis for noise rejection.

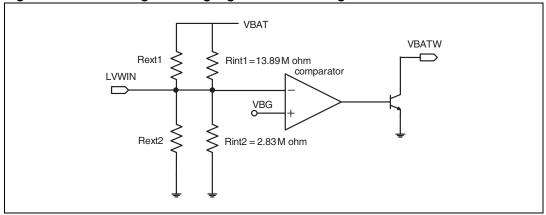

Two external resistors (Rext1, Rext2), whose values are lower than 100 kohm, are connected to the LWIN (low warning input) pin to give the possibility to trim the threshold at which the low voltage warning comparator triggers. When LVWIN voltage is below the input voltage threshold (1.25 V typ), the VBATW (battery voltage warning) output is pulled down and a low-voltage warning is indicated. When no external resistor network is connected to LVWIN, the detector sets the threshold to a nominal 7.5 V.

No external interaction is required to reset the output state, because it is automatically reset when the fault condition is removed.

*Figure 4* shows an high level block diagram of the low-voltage warning circuit. VBAT is divided by two internal resistors (Rint1, Rint2) and two external programming resistors (Rext1, Rext2). When VBAT decreases so that LVWIN voltage gets lower than the internal reference (VBG), VBATW is pulled down to ground.

Figure 4. Low voltage warning high level block diagram

18/24

## 6 I<sup>2</sup>C bus interface

Data transmission from microprocessor to the L5962 and viceversa takes place through the 2 wires  $I^2C$  bus interface, consisting of the two lines SDA and SCL (pull-up resistors to positive supply voltage must be connected).

### 6.1 Data validity

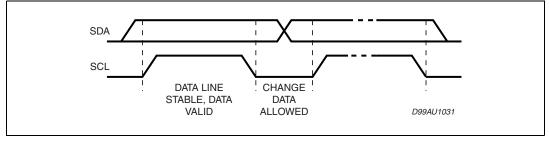

As shown by *Figure 5*, the data on the SDA line must be stable during the high period of the clock. The HIGH and LOW state of the data line can only change when the clock signal on the SCL line is LOW.

### 6.2 Start and stop conditions

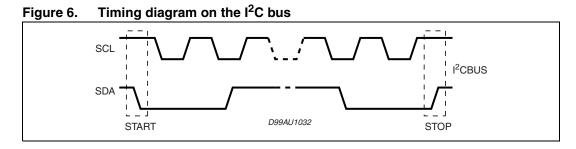

As shown by *Figure 6* a start condition is a HIGH to LOW transition of the SDA line while SCL is HIGH. The stop condition is a LOW to HIGH transition of the SDA line while SCL is HIGH.

### 6.3 Byte format

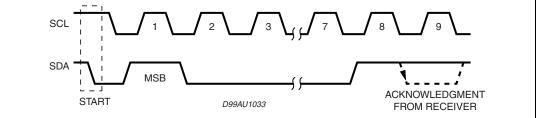

Every byte transferred to the SDA line must contain 8 bits. Each byte must be followed by an acknowledge bit. The MSB is transferred first.

### 6.4 Acknowledge

The transmitter\* puts a resistive HIGH level on the SDA line during the acknowledge clock pulse (see *Figure 6*). The receiver\*\* the acknowledges has to pull-down (LOW) the SDA line during the acknowledge clock pulse, so that the SDAline is stable LOW during this clock pulse.

\* Transmitter

- master (µP) when it writes an address to the L5962

- slave (L5962) when the  $\mu$ P reads a data byte from L5962

\*\* Receiver

- slave (L5962) when the  $\mu$ P writes an address to the L5962

- master ( $\mu$ P) when it reads a data byte from L5962

#### Figure 5. Data validity on the I<sup>2</sup>C bus

# 7 Software specifications

#### Table 6. Chip address

| D7 (MSB) |   |   |   |   |   |   | D0 (LSB) |        |

|----------|---|---|---|---|---|---|----------|--------|

| 0        | 0 | 0 | 1 | 0 | 0 | 0 | R/W      | 10 Hex |

IC functions can be driven sending one data byte IB1

#### Table 7. IB1 data byte

| Bit position | Bit name | Function description |

|--------------|----------|----------------------|

| D7           | VLR2EN   | VLR2 enable          |

| D6           | VLR2SEL2 | VLR2 selection       |

| D5           | VLR2SEL1 |                      |

| D4           | VLR2SEL0 |                      |

| D3           | VLR1EN   | VLR1 enable          |

| D2           | VLR1SEL  | VLR1 selection       |

| D1           | HSD2EN   | HSD2 enable          |

| D0           | HSD1EN   | HSD1 enable          |

Bits D6-D4 are used to select VLR2 output voltage according to the following table

#### Table 8. VLR2 output level selection

| VLR2SEL2 | VLR2SEL1 | VLR2SEL0 | VLR2 output voltage |

|----------|----------|----------|---------------------|

| 0        | 0        | 0        | 3.3V                |

| 0        | 0        | 1        | 5.0V                |

| 0        | 1        | 0        | 5.5V                |

| 0        | 1        | 1        | 6.0V                |

| 1        | 0        | 0        | 7.0V                |

| 1        | 0        | 1        | 7.5V                |

| 1        | 1        | 0        | 8.0V                |

| 1        | 1        | 1        | 10.0V               |

## 8 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: <u>www.st.com</u>.

$ECOPACK^{\mathbb{R}}$  is an ST trademark.

Figure 8. PowerSO36 (slug-up) mechanical data and package dimensions

# 9 Revision history

#### Table 9.Document revision history

| Date                                                                                  | Revision | Changes                                                                                  |

|---------------------------------------------------------------------------------------|----------|------------------------------------------------------------------------------------------|

| 24-Nov-2009                                                                           | 1        | Initial release.                                                                         |

| 10-Dec-20092Updated Figure 8: PowerSO36 (slug-up) n<br>package dimensions on page 22. |          | Updated Figure 8: PowerSO36 (slug-up) mechanical data and package dimensions on page 22. |

| 18-Sep-2013                                                                           | 3        | Updated Disclaimer.                                                                      |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

ST PRODUCTS ARE NOT DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER'S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR "AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL" INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries. Information in this document supersedes and replaces all information previously supplied. The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2013 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

24/24