#### 150 mA low quiescent current low noise voltage regulator

#### Datasheet - production data

#### **Features**

- Input voltage from 1.5 to 5.5 V

- Ultra low dropout voltage (80 mV typ. at 100 mA load)

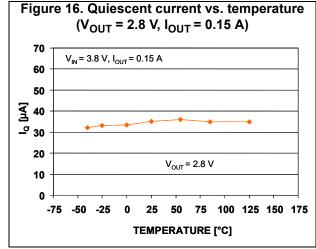

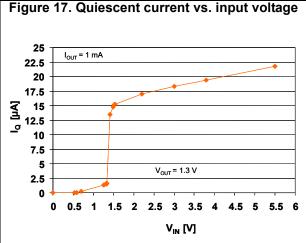

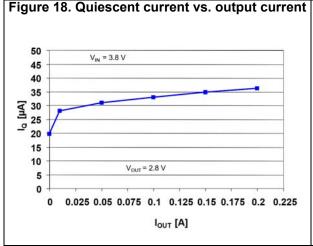

- Very low quiescent current (20 μA typ. at no load, 35 μA typ. at 150 mA load, 1 μA max in off mode)

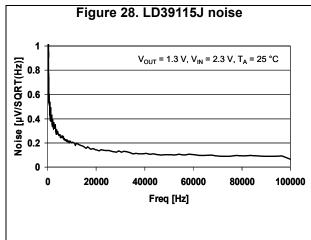

- Very low noise (33 μV<sub>RMS</sub> from 1 kHz to 100 kHz at V<sub>OUT</sub> = 1.8 V)

- Output voltage tolerance: ± 2.0 % @ 25 °C

- 150 mA guaranteed output current

- Wide range of output voltages available on request: 0.8 V to 4.5 V with 100 mV step

- Logic-controlled electronic shutdown

- Compatible with ceramic capacitor C<sub>OUT</sub> = 1 μF

- Internal current and thermal limit

- Flip-chip 4 bumps 0.8 x 0.8 mm. pitch 0.4 mm

- Temperature range: -40 °C to 125 °C

#### **Applications**

- Mobile phones

- Personal digital assistants (PDAs)

- Cordless phones and similar battery-powered systems

#### **Description**

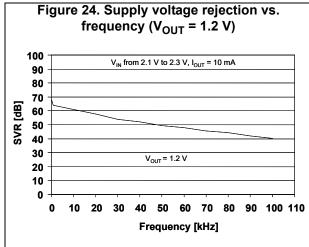

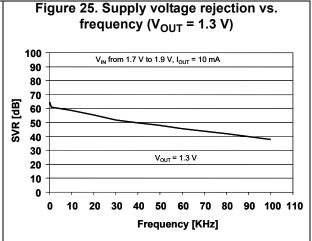

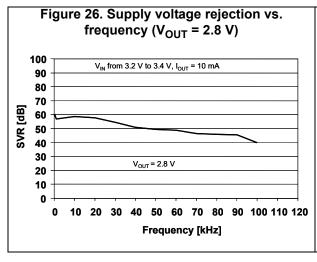

The LD39115J provides 150 mA maximum current from an input voltage ranging from 1.5 V to 5.5 V with a typical dropout voltage of 80 mV. It is stabilized with a ceramic capacitor. The ultra low drop voltage, low quiescent current and low noise features make it suitable for low power battery-powered applications. Power supply rejection is 65 dB at low frequencies and starts to roll off at 10 kHz. An enable logic control function puts the LD39115J in shutdown mode allowing a total current consumption lower than 1  $\mu A$ . The device also includes a short-circuit constant current limiting and thermal protection.

Table 1. Device summary

| Order codes | Output voltages |

|-------------|-----------------|

| LD39115J12R | 1.2 V           |

| LD39115J14R | 1.4 V           |

| LD39115J15R | 1.5 V           |

| LD39115J18R | 1.8 V           |

| LD39115J25R | 2.5 V           |

| LD39115J28R | 2.8 V           |

| LD39115J30R | 3.0 V           |

| LD39115J33R | 3.3 V           |

February 2021 DocID15527 Rev 8 1/21

Contents LD39115J

## **Contents**

| 1  | Diagram 3                                                              |

|----|------------------------------------------------------------------------|

| 2  | Pin configuration                                                      |

| 3  | Typical application 5                                                  |

| 4  | Maximum ratings                                                        |

| 5  | Electrical characteristics                                             |

| 6  | Typical performance characteristics                                    |

| 7  | Package mechanical data                                                |

| 8  | Packaging mechanical data                                              |

| 9  | Different output voltage versions of the LD39115J available on request |

| 10 | Revision history                                                       |

Downloaded from Arrow.com.

LD39115J Diagram

# 1 Diagram

IN

BandGap

1.22 V

Trimming

R1

Protection

R2

Figure 1. Block diagram

Pin configuration LD39115J

# 2 Pin configuration

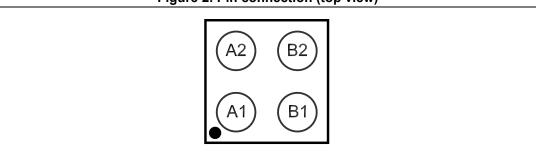

Figure 2. Pin connection (top view)

Table 2. Pin description

| Pin n° | Symbol | Function                                              |

|--------|--------|-------------------------------------------------------|

| A2     | EN     | Enable pin logic input: Low = shutdown, High = active |

| A1     | GND    | Common ground                                         |

| B2     | IN     | Input voltage of the LDO                              |

| B1     | OUT    | Output voltage                                        |

5/

LD39115J Typical application

# 3 Typical application

V<sub>IN</sub> IN OUT V<sub>OUT</sub> 1 μF Load

V<sub>EN</sub> EN GND

Figure 3. Typical application circuit

Maximum ratings LD39115J

#### 4 Maximum ratings

Table 3. Absolute maximum ratings

| Symbol           | Parameter                            | Value                         | Unit |

|------------------|--------------------------------------|-------------------------------|------|

| V <sub>IN</sub>  | DC input voltage                     | - 0.3 to 6                    | V    |

| V <sub>OUT</sub> | DC output voltage                    | - 0.3 to V <sub>I</sub> + 0.3 | V    |

| V <sub>EN</sub>  | Enable input voltage                 | - 0.3 to V <sub>I</sub> + 0.3 | V    |

| I <sub>OUT</sub> | Output current                       | Internally limited            | mA   |

| P <sub>D</sub>   | Power dissipation                    | Internally limited            | mW   |

| T <sub>STG</sub> | Storage temperature range            | - 65 to 150                   | °C   |

| T <sub>OP</sub>  | Operating junction temperature range | - 40 to 125                   | °C   |

Note:

Absolute maximum ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. All values are referred to GND.

Table 4. Thermal data

| Symbol     | Parameter                           | Value | Unit |

|------------|-------------------------------------|-------|------|

| $R_{thJA}$ | Thermal resistance junction-ambient | 180   | °C/W |

**Table 5. ESD performance**

| Symbol | Parameter              | Test conditions | Value | Unit |

|--------|------------------------|-----------------|-------|------|

| ESD    | ESD protection voltage | НВМ             | 4     | kV   |

#### 5 Electrical characteristics

$T_J$  = 25 °C,  $V_{IN}$  =  $V_{OUT(NOM)}$  + 1 V,  $C_{IN}$  =  $C_{OUT}$  = 1  $\mu F,\ I_{OUT}$  = 1 mA,  $V_{EN}$  =  $V_{IN},\ unless otherwise specified.$

Table 6. Electrical characteristics for LD39115J <sup>(1)</sup>

| Symbol            | Parameter                                | Test conditions                                                                                                                             | Min. | Тур.  | Max. | Unit                 |  |

|-------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|----------------------|--|

| V <sub>IN</sub>   | Operating input voltage                  |                                                                                                                                             | 1.5  |       | 5.5  | V                    |  |

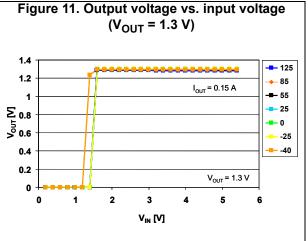

| \/                | Turn-on threshold                        |                                                                                                                                             |      | 1.45  | 1.48 | V                    |  |

| $V_{UVLO}$        | Turn-off threshold                       |                                                                                                                                             | 1.30 | 1.35  |      | mV                   |  |

|                   |                                          | $V_{OUT} > 1.5 \text{ V}, I_{OUT} = 1 \text{ mA},$<br>$T_{J} = 25 ^{\circ}\text{C}$                                                         | -2.0 |       | 2.0  | %                    |  |

| V <sub>OUT</sub>  | V <sub>OUT</sub> accuracy                | V <sub>OUT</sub> > 1.5 V, I <sub>OUT</sub> = 1 mA,<br>-40 °C < T <sub>J</sub> < 125 °C                                                      | -3.0 |       | 3.0  | %                    |  |

|                   |                                          | V <sub>OUT</sub> ≤ 1.5 V, I <sub>OUT</sub> = 1 mA                                                                                           |      | ±10   |      | mV                   |  |

|                   |                                          | V <sub>OUT</sub> ≤ 1.5 V, I <sub>OUT</sub> = 1 mA,<br>-40 °C < T <sub>J</sub> < 125 °C                                                      |      | ±30   |      | mV                   |  |

| ΔV <sub>OUT</sub> | Static line regulation                   | $V_{OUT}$ +1 V $\leq$ V <sub>IN</sub> $\leq$ 5.5 V, $I_{OUT}$ = 1 mA                                                                        |      | 0.01  |      | %/V                  |  |

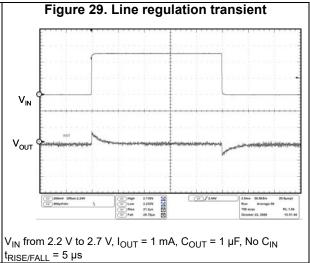

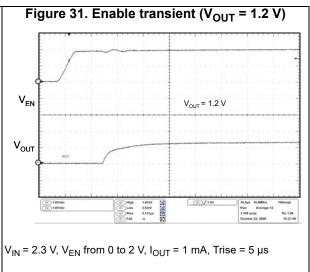

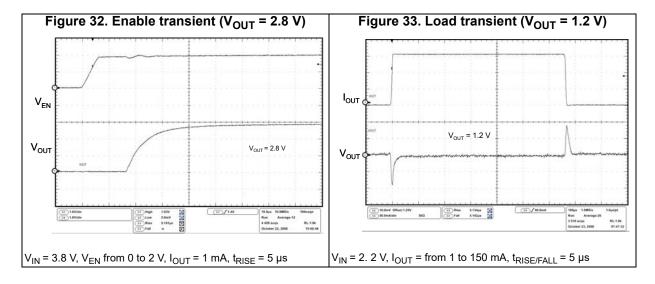

| ΔV <sub>OUT</sub> | Transient line regulation <sup>(2)</sup> | $\Delta V_{IN}$ = +500 mV, $I_{OUT}$ = 1 mA, $T_R$ = $T_F$ = 5 $\mu$ s                                                                      |      | 10    |      | mVpp                 |  |

| $\Delta V_{OUT}$  | Static load regulation                   | I <sub>OUT</sub> = 1 mA to 150 mA                                                                                                           |      | 0.002 |      | %/mA                 |  |

| ΔV <sub>OUT</sub> | Transient load regulation <sup>(2)</sup> | $I_{OUT} = 1 \text{ mA to } 150 \text{ mA},$<br>$t_R = t_F = 5 \mu \text{s}$                                                                |      | 40    |      | mVpp                 |  |

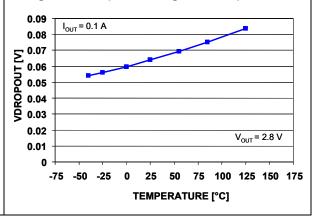

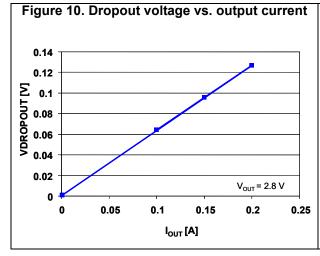

| V <sub>DROP</sub> | Dropout voltage (3)                      | I <sub>OUT</sub> = 100 mA, V <sub>OUT</sub> > 1.5 V<br>-40 °C < T <sub>J</sub> < 125 °C                                                     |      | 80    | 110  | mV                   |  |

| e <sub>N</sub>    | Output noise voltage                     | 10 Hz to 100 kHz, I <sub>OUT</sub> = 10 mA                                                                                                  |      | 30    |      | μV <sub>RMS</sub> /V |  |

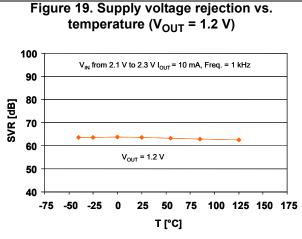

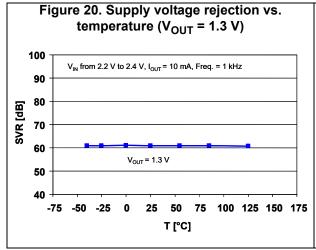

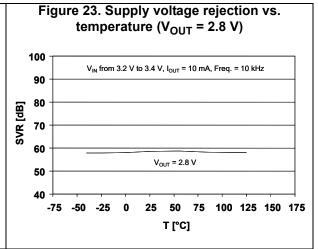

| SVR               | Supply voltage                           | V <sub>IN</sub> = V <sub>OUTNOM</sub> +1 V +/- V <sub>RIPPLE</sub><br>V <sub>RIPPLE</sub> = 0.1 V Freq. = 1 kHz<br>I <sub>OUT</sub> = 10 mA |      | 74    |      |                      |  |

| SVK               | rejection V <sub>OUT</sub> = 1.5 V       | $V_{IN} = V_{OUTNOM} + 0.5 \text{ V +/- } V_{RIPPLE}$<br>$V_{RIPPLE} = 0.1 \text{ V Freq.} = 10 \text{ kHz}$<br>$I_{OUT} = 10 \text{ mA}$   |      | 67    |      | — dB                 |  |

|                   |                                          | I <sub>OUT</sub> = 0 mA                                                                                                                     |      | 20    |      |                      |  |

|                   |                                          | I <sub>OUT</sub> = 0 mA, -40 °C < T <sub>J</sub> < 125 °C                                                                                   |      |       | 50   |                      |  |

|                   |                                          | I <sub>OUT</sub> = 0 to 150 mA                                                                                                              |      | 35    |      |                      |  |

| Ι <sub>Q</sub>    | Quiescent current                        | I <sub>OUT</sub> = 0 to 150 mA,<br>-40 °C < T <sub>J</sub> < 125 °C                                                                         |      |       | 70   | μΑ                   |  |

|                   |                                          | V <sub>IN</sub> input current in OFF MODE:<br>V <sub>EN</sub> = GND                                                                         |      | 0.001 | 1    |                      |  |

Electrical characteristics LD39115J

Table 6. Electrical characteristics for LD39115J (continued)<sup>(1)</sup>

| Symbol            | Parameter                | Test conditions                                                       | Min. | Тур. | Max. | Unit |

|-------------------|--------------------------|-----------------------------------------------------------------------|------|------|------|------|

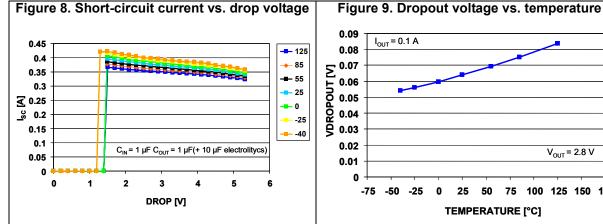

| I <sub>SC</sub>   | Short circuit current    | R <sub>L</sub> = 0                                                    | 200  |      |      | mA   |

| V                 | Enable input logic low   | V <sub>IN</sub> = 1.5 V to 5.5 V,<br>-40 °C < T <sub>J</sub> < 125 °C |      |      | 0.4  | V    |

| $V_{EN}$          | Enable input logic high  | V <sub>IN</sub> = 1.5 V to 5.5 V,<br>-40 °C < T <sub>J</sub> < 125 °C | 0.9  |      |      | V    |

| I <sub>EN</sub>   | Enable pin input current | V <sub>SHDN</sub> = V <sub>IN</sub>                                   |      | 0.1  | 100  | nA   |

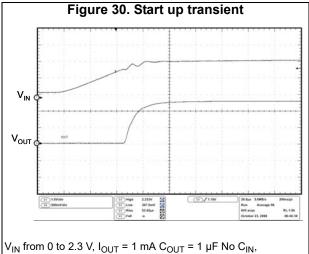

| T <sub>ON</sub>   | Turn on time (4)         |                                                                       |      | 30   |      | μs   |

| т                 | Thermal shutdown         |                                                                       |      | 160  |      | °C   |

| T <sub>SHDN</sub> | Hysteresis               |                                                                       |      | 20   |      |      |

| C <sub>OUT</sub>  | Output capacitor         | Capacitance (see Section 6: Typical performance characteristics)      | 1    |      | 22   | μF   |

<sup>1.</sup> For  $V_{OUT(NOM)}$  < 1.2 V,  $V_{IN}$  = 1.5 V.

<sup>2.</sup> All transient values are guaranteed by design, not production tested.

<sup>3.</sup> Dropout voltage is the input-to-output voltage difference at which the output voltage is 100 mV below its nominal value. This specification does not apply for output voltages below 1.5 V.

<sup>4.</sup> Turn-on time is time measured between the enable input just exceeding V<sub>EN</sub> high value and the output voltage just reaching 95 % of its nominal value.

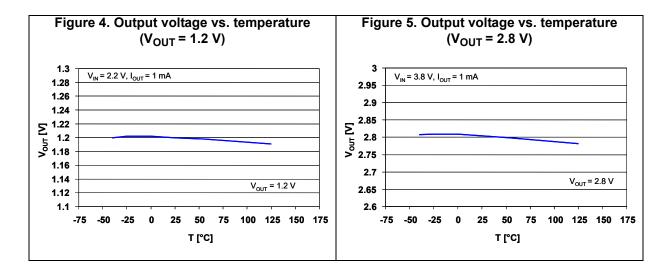

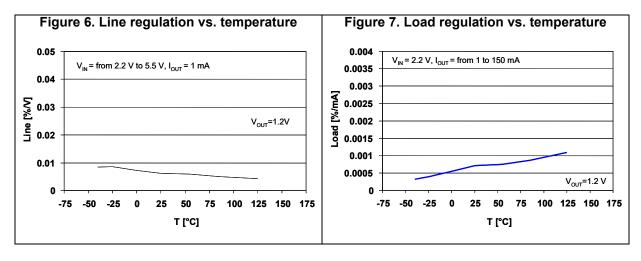

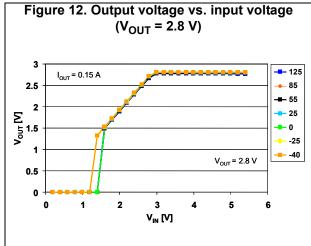

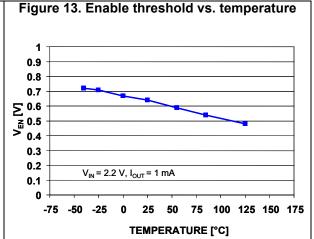

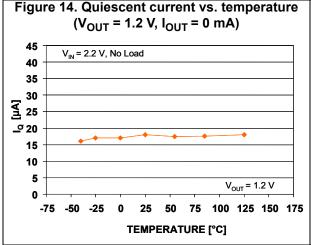

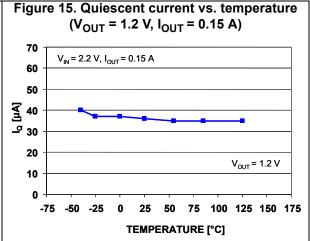

## **6** Typical performance characteristics

$$C_{IN}$$

=  $C_{OUT}$  = 1  $\mu$ F,  $V_{EN}$  to  $V_{IN}$ .

577

Figure 21. Supply voltage rejection vs. temperature (Freq. = 1 kHz) 100  $V_{\text{IN}}$  from 3.7 V to 3.9 V,  $I_{\text{OUT}}$  = 10 mA, Freq. = 1 kHz 90 80 SVR [dB] 70 60 50 V<sub>OUT</sub> = 2.8 V 40 -50 -25 50 75 100 125 150 175 -75 T [°C]

Figure 22. Supply voltage rejection vs. temperature (Freq. = 10 kHz)

100

V<sub>IN</sub> from 1.7 V to 1.9 V, I<sub>OUT</sub> = 10 mA, Freq. = 10 kHz

80

70

60

50

V<sub>OUT</sub> = 1.3 V

T [°C]

57

Figure 27. Supply voltage rejection vs. output current 100  $V_{IN}$  from 1.7 V to 1.9 V, F = 10 kHz 90 80 70 60 50 40 30 V<sub>OUT</sub> = 1.3 V 20 10 0.025 0.05 0.075 0.1 0.125 0.15 0.175 0.2 0.225 0.25 I<sub>OUT</sub> [A]

$t_{RISE} = 60 \mu s$

577

DocID15527 Rev 8

13/21

Downloaded from **Arrow.com**.

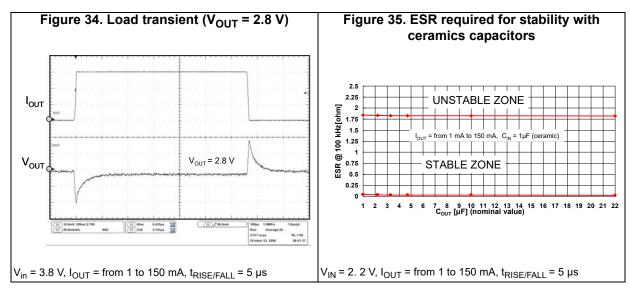

#### 7 Package mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: <a href="https://www.st.com">www.st.com</a>. ECOPACK is an ST trademark.

TOP VIEW

CCCC

Al see note 1

BOTTOM VIEW

Figure 36. Flip-chip 4 drawings

Table 7. Flip-chip 4 mechanical data

| Dim  |       | mm    |       |

|------|-------|-------|-------|

| Dim. | Min.  | Тур.  | Max.  |

| Α    | 0.52  | 0.56  | 0.60  |

| A1   | 0.17  | 0.20  | 0.23  |

| A2   | 0.35  | 0.36  | 0.37  |

| b    | 0.23  | 0.25  | 0.29  |

| D    | 0.758 | 0.788 | 0.818 |

| D1   |       | 0.4   |       |

| E    | 0.758 | 0.788 | 0.818 |

| E1   |       | 0.4   |       |

| SD   | 0.18  | 0.2   | 0.22  |

| SE   | 0.18  | 0.2   | 0.22  |

| f    |       | 0.199 |       |

| ccc  |       | 0.075 |       |

Figure 37. Flip-chip 4 footprint

# 8 Packaging mechanical data

A Population of the scale of th

Table 8. Flip-chip 4 tape and reel mechanical data

| Dim.   | mm   |      |      |  |

|--------|------|------|------|--|

| Dilli. | Min. | Тур. | Max. |  |

| Α      |      |      | 178  |  |

| С      | 12.8 |      | 13.2 |  |

| D      | 20.2 |      |      |  |

| N      | 59   | 60   | 61   |  |

| Т      |      |      | 8.4  |  |

| Ao     | 0.82 | 0.87 | 0.92 |  |

| Во     | 0.82 | 0.87 | 0.92 |  |

| Ko     | 0.64 | 0.69 | 0.74 |  |

| Ро     | 3.9  | 4.0  | 4.1  |  |

| Р      | 3.9  | 4.0  | 4.1  |  |

# 9 Different output voltage versions of the LD39115J available on request

Table 9. Options available on request

| Order codes | Output voltages |

|-------------|-----------------|

| LD39115J08R | 0.8 V           |

| LD39115J10R | 1.0 V           |

Revision history LD39115J

# 10 Revision history

**Table 10. Document revision history**

| Date        | Revision | Changes                                                                                                                                                                                |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 26-Mar-2009 | 1        | Initial release.                                                                                                                                                                       |

| 12-Jun-2009 | 2        | Modified: Table 1 on page 1 and Table 8 on page 19.                                                                                                                                    |

| 05-Aug-2009 | 3        | Modified: tape and reel mechanical data on page 18.                                                                                                                                    |

| 17-May-2011 | 4        | Modified: Table 1 on page 1 and Table 8 on page 19.                                                                                                                                    |

| 20-Dec-2011 | 5        | Added: new order code LD39115J25R Table 1 on page 1.                                                                                                                                   |

| 16-Jan-2014 | 6        | Part number LD39115Jxx changed to LD39115J. Updated the Description in cover page, Section 7: Package mechanical data. Added Section 8: Packaging mechanical data. Minor text changes. |

| 12-Sep-2018 | 7        | Added Table 5: ESD performance.                                                                                                                                                        |

| 23-Feb-2021 | 8        | Updated Figure 18 and Figure 28.                                                                                                                                                       |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2021 STMicroelectronics - All rights reserved