# **VNQ6040S-E**

# Quad channel high-side driver

Datasheet - production data

### **Features**

- General

- 16 bit ST-SPI for full and diagnostic

- Programmable BULB/LED mode

- Integrated PWM and phase shift generation unit

- 160 Hz internal PWM fallback frequency

- Advanced limp home functionalities for robust fail-safe system

- Very low standby current

- Optimized electromagnetic emissions

- Very low electromagnetic susceptibility

- In compliance with the 2002/95/EC

- Diagnostic

- Multiplex proportional load current sense

- Synchronous diagnostic of overload and short to GND, output shorted to V<sub>CC</sub>, ON-state and OFF-state open-load

- Programmable case overtemperature warning

- Protections

- Load current limitation

- Self limiting of fast thermal transients

- Power limitation and overtemperature shutdown (latching off or autorestart)

- Undervoltage shutdown

- Overvoltage clamp

- Reverse battery protected through power outputs self turn-on (no external components)

- Load dump protected

This is information on a product in full production.

- Protection against loss of ground

# **Description**

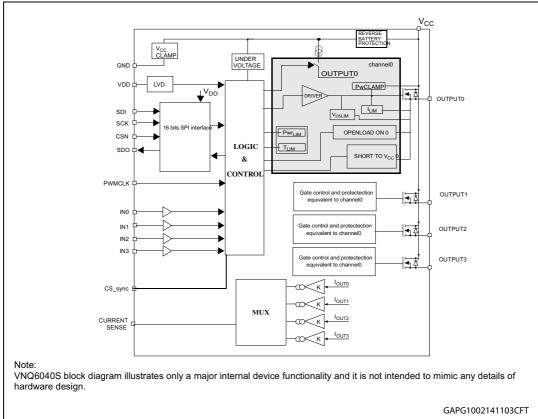

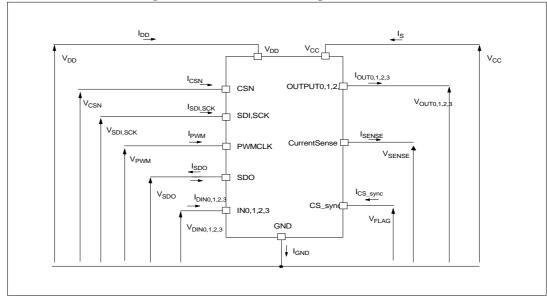

The VNQ6040S-E is a device made using STMicroelectronics VIPower technology. It is intended for driving resistive or inductive loads directly connected to ground. The device is protected against voltage transient on  $V_{CC}$  pin.

Programming, control and diagnostics are implemented via the SPI bus.

An analog current feedback for each channel is connected to the CURRENT-SENSE pin via a multiplexer. A CS\_SYNC pin delivers a synchronous signal for sampling the current sense while the corresponding output is on.

The device detects open-load for both on-state and off-state conditions.

Real time diagnostic is available through the SPI bus (open-load, output short to  $V_{CC}$ , overtemperature, communication error).

Output current limitation protects the device in an overload condition. The device can limit the dissipated power to a safe level up to thermal shutdown intervention. Thermal shutdown can be configured as latched off or with automatic restart.

The device enters a limp home mode in case of loss of digital supply  $(V_{DD})$ , reset of digital memory or CSN monitoring time-out event. In this mode states of channel 0, 1, 2 or 3 are respectively controlled by four dedicated pins IN0, IN1, IN2 and IN3. Each channel can be programmed in BULB/LED mode.

www.st.com

Contents VNQ6040S-E

# **Contents**

| 1 | Bloc  | k diagr | am and pin description                                      | 8  |

|---|-------|---------|-------------------------------------------------------------|----|

| 2 | Fund  | ctional | description                                                 | 12 |

|   | 2.1   | Opera   | ting modes                                                  | 12 |

|   |       | 2.1.1   | Reset mode                                                  | 14 |

|   |       | 2.1.2   | Fail Safe mode                                              | 14 |

|   |       | 2.1.3   | Normal mode                                                 | 15 |

|   |       | 2.1.4   | Standby mode                                                | 16 |

|   |       | 2.1.5   | Sleep mode 1                                                | 16 |

|   |       | 2.1.6   | Sleep mode 2                                                | 16 |

|   |       | 2.1.7   | Battery undervoltage mode                                   | 16 |

|   | 2.2   | Progra  | ammable functions                                           | 19 |

|   |       | 2.2.1   | Outputs configuration                                       | 19 |

|   |       | 2.2.2   | Case over temperature                                       | 20 |

|   |       | 2.2.3   | Protections                                                 | 21 |

|   |       | 2.2.4   | Open-load ON-state detection                                | 22 |

|   |       | 2.2.5   | Open-load OFF-state detection                               | 23 |

|   |       | 2.2.6   | Current sense                                               | 24 |

|   | 2.3   | Test m  | node (reserved)                                             | 25 |

| 3 | SPI f | unction | nal description                                             | 26 |

|   | 3.1   | SPI co  | mmunication                                                 | 26 |

|   |       | 3.1.1   | Signal description                                          | 26 |

|   |       | 3.1.2   | Connecting to the SPI bus                                   | 26 |

|   |       | 3.1.3   | SPI mode                                                    | 26 |

|   | 3.2   | SPI pr  | otocol                                                      | 27 |

|   |       | 3.2.1   | SDI, SDO format                                             | 27 |

|   |       | 3.2.2   | Global status byte description                              | 28 |

|   |       | 3.2.3   | Operating code definition                                   | 29 |

|   | 3.3   | Addres  | ss mapping                                                  | 32 |

|   |       | 3.3.1   | Address 00h - Control Register (CTLR)                       |    |

|   |       | 3.3.2   | Address 01h - SPI Output Control Register (SOCR)            |    |

|   |       | 3.3.3   | Address 02h - Direct Input Enable Control Register (DIENCR) | 35 |

|   |       |         |                                                             |    |

VNQ6040S-E Contents

|   |      | 3.3.4     | Address 03h - Current Sense Multiplexer Control Register (CSMUXCR)                     |

|---|------|-----------|----------------------------------------------------------------------------------------|

|   |      | 3.3.5     | Address 04h - Current Sense Ratio Control Register (CSRATCR) 36                        |

|   |      | 3.3.6     | Address 05h - PWM Mode Control Register (PWMCR)                                        |

|   |      | 3.3.7     | Address 06h - Open-load ON-State Control Register (OLONCR) 37                          |

|   |      | 3.3.8     | Address 07h - Open-load OFF-State Control Register (OLOFFCR) 37                        |

|   |      | 3.3.9     | Address 08h - Automatic Shutdown Control Register (ASDTCR) 37                          |

|   |      | 3.3.10    | Address 09h - Channel Control Register (CCR)                                           |

|   |      | 3.3.11    | Address 10h - 13h - Duty Cycle Control Register (DUTYXCR) 38                           |

|   |      | 3.3.12    | Address 18h - 1Ah - Phase Control Register (PHASEXCR)39                                |

|   |      | 3.3.13    | Address 2Eh - Channel Read Back Status Register (CHDRVR) 39                            |

|   |      | 3.3.14    | Address 2Fh - General Status Register (GENSTR) 40                                      |

|   |      | 3.3.15    | Address 30h - Over Temperature Status Register (OTFLTR)40                              |

|   |      | 3.3.16    | Address 31h - Open-Load ON-State Status Register (OLFLTR) 41                           |

|   |      | 3.3.17    | Address 32h - Open-Load OFF-State / Stuck to V <sub>CC</sub> Status Register (STKFLTR) |

|   |      | 3.3.18    | Address 33h - Power Limitation Status Register (PWLMFLTR) 42                           |

|   |      | 3.3.19    | Address 34h - Over Load Status Register (OVLFLTR)                                      |

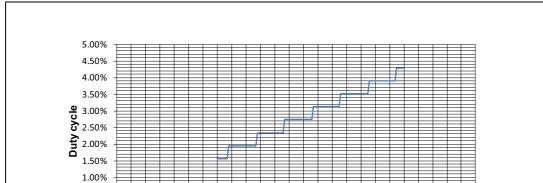

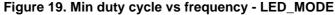

|   |      | 3.3.20    | Minimum duty cycle vs frequency43                                                      |

|   |      | 3.3.21    | Address 3Eh - Test Register (TEST)                                                     |

|   |      | 3.3.22    | Address 3Fh - Configuration Register (GLOBCTR)                                         |

| 4 | Elec | trical sp | pecifications 46                                                                       |

|   | 4.1  | Absolu    | te maximum ratings                                                                     |

|   | 4.2  | Therma    | al data                                                                                |

|   | 4.3  | Electric  | cal characteristics                                                                    |

|   |      | 4.3.1     | SPI                                                                                    |

|   |      | 4.3.2     | BULB mode                                                                              |

|   |      | 4.3.3     | LED mode                                                                               |

|   | 4.4  | Maxim     | um demagnetization energy (V <sub>CC</sub> = 13.5 V)                                   |

| 5 | Pacl | kage and  | d PCB thermal data 63                                                                  |

|   | 5.1  | Power     | SSO-36 thermal data 63                                                                 |

| 6 | Pacl | kage info | ormation                                                                               |

|   | 6.1  | ECOP      | ACK <sup>®</sup> package 66                                                            |

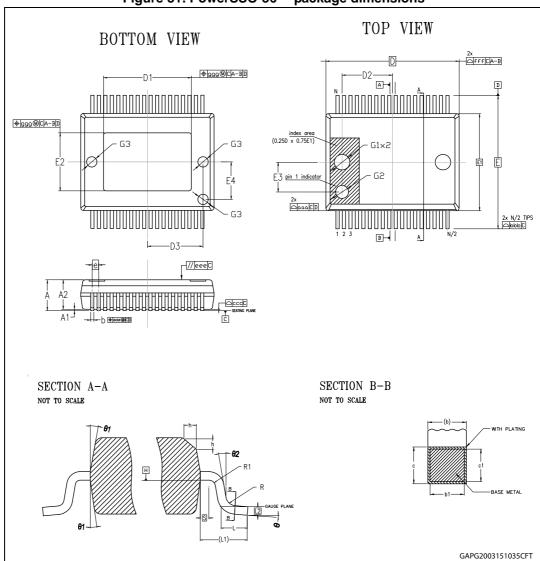

|   | 6.2  | Power     | SSO-36™ mechanical data 66                                                             |

|   |      |           |                                                                                        |

| Contents |      |                     | VNQ6040 | S-E |

|----------|------|---------------------|---------|-----|

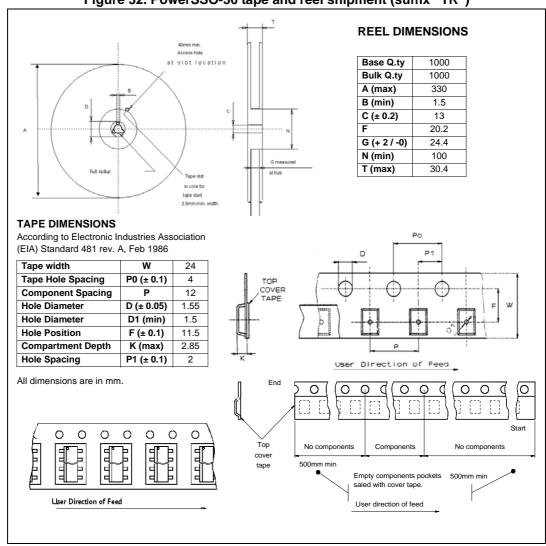

|          | 6.3  | Packing information |         | 68  |

| 7        | Orde | er codes            |         | 69  |

| 8        | Revi | sion history        |         | 70  |

VNQ6040S-E List of tables

# List of tables

| Table 1.  | Pin functionality description                                  | 10 |

|-----------|----------------------------------------------------------------|----|

| Table 2.  | Operating modes                                                |    |

| Table 3.  | Output control truth table                                     | 19 |

| Table 4.  | Example of DUTYCXCR register                                   | 20 |

| Table 5.  | Example of PHASEXCR register                                   |    |

| Table 6.  | Activation of blanking filter in case of power limitation      | 22 |

| Table 7.  | Nominal open-load thresholds                                   |    |

| Table 8.  | STKFLTR state                                                  |    |

| Table 9.  | Current sense ratio                                            | 24 |

| Table 10. | SPI signal description                                         | 26 |

| Table 11. | Command byte                                                   |    |

| Table 12. | Input data byte                                                |    |

| Table 13. | Global status byte                                             | 28 |

| Table 14. | Output data byte                                               | 28 |

| Table 15. | Global status byte                                             | 28 |

| Table 16. | Operating codes                                                | 29 |

| Table 17. | RAM memory map                                                 | 32 |

| Table 18. | ROM memory map                                                 | 33 |

| Table 19. | Control register                                               | 34 |

| Table 20. | SPI output control register                                    | 34 |

| Table 21. | Direct enable control register                                 | 35 |

| Table 22. | Current sense multiplexer control register                     | 35 |

| Table 23. | Current sense ratio control register                           | 36 |

| Table 24. | PWM mode control register                                      | 36 |

| Table 25. | Open-load ON-state control register                            | 37 |

| Table 26. | Open-load OFF-state control register                           | 37 |

| Table 27. | Automatic shutdown control register                            | 37 |

| Table 28. | Channel control register                                       | 38 |

| Table 29. | DUTYCXCR - duty cycle control register                         | 38 |

| Table 30. | PHASECXCR - duty cycle control register                        | 39 |

| Table 31. | Channel read back status register                              | 39 |

| Table 32. | General status register                                        | 40 |

| Table 33. | Over temperature status register                               | 40 |

| Table 34. | Open-load ON-state status register                             | 41 |

| Table 35. | Open-load OFF-state / stuck to V <sub>CC</sub> status register | 42 |

| Table 36. | Power limitation status register                               | 42 |

| Table 37. | Over load status register                                      | 43 |

| Table 38. | Test register                                                  | 45 |

| Table 39. | Configuration register                                         | 45 |

| Table 40. | Absolute maximum ratings                                       | 46 |

| Table 41. | Thermal data                                                   | 47 |

| Table 42. | SPI - DC characteristics                                       |    |

| Table 43. | SPI - AC characteristics (SDI, SCK, CSN, SDO, PWMCLK pins)     |    |

| Table 44. | SPI - dynamic characteristics                                  |    |

| Table 45. | SPI - CS_sync pin                                              |    |

| Table 46. | SPI - power section                                            |    |

| Table 47. | SPI - logic inputs (IN0,1,2,3 pins)                            |    |

| Table 48. | SPI - protections                                              | 51 |

|           |                                                                |    |

DocID18061 Rev 11

5/73

List of tables VNQ6040S-E

| Table 49. | SPI - open-load detection (8V < VCC < 18 V)              | . 51 |

|-----------|----------------------------------------------------------|------|

| Table 50. | BULB - power section                                     |      |

| Table 51. | BULB - switching (VCC = 13 V)                            | . 52 |

| Table 52. | BULB - open-load detection (8 V < VCC < 18 V)            | . 52 |

| Table 53. | BULB - protections and diagnosis                         | . 52 |

| Table 54. | BULB - current sense (8 V < VCC < 18 V, channel 0,1,2,3) | . 53 |

| Table 55. | LED - power section                                      |      |

| Table 56. | LED - switching (VCC=13V channel 0,1,2,3)                | . 54 |

| Table 57. | LED - open-load detection (8 V < VCC < 18 V)             | . 55 |

| Table 58. | LED - protections and diagnosis                          | . 55 |

| Table 59. | LED - current sense (8 V < VCC < 18 V , channel 0,1,2,3) | . 55 |

| Table 60. | Electrical transient requirements (part 1)               | . 57 |

| Table 61. | Electrical transient requirements (part 2)               | . 57 |

| Table 62. | Electrical transient requirements (part 3)               | . 58 |

| Table 63. | Thermal parameter                                        | . 65 |

| Table 64. | PowerSSO-36 mechanical data                              | . 67 |

| Table 65. | Device summary                                           | . 69 |

| Table 66  | Document revision history                                | 70   |

VNQ6040S-E List of figures

# **List of figures**

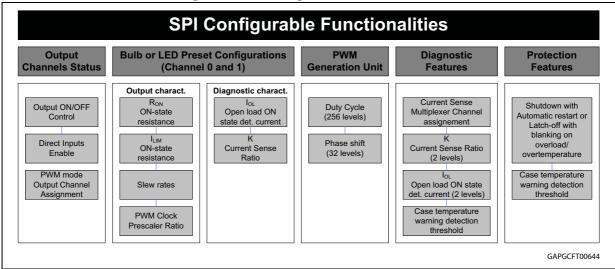

| Figure 1.  | SPI configurable functionalities                                             | . 8 |

|------------|------------------------------------------------------------------------------|-----|

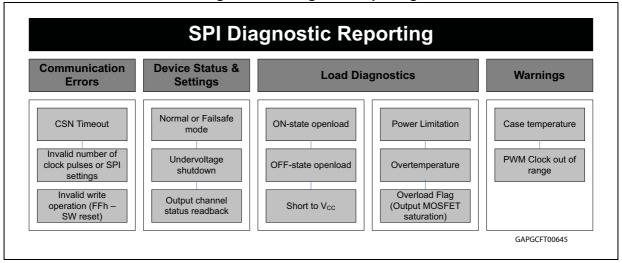

| Figure 2.  | SPI diagnostic reporting                                                     | . 8 |

| Figure 3.  | Block diagram                                                                | . 9 |

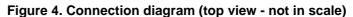

| Figure 4.  | Connection diagram (top view - not in scale)                                 | . 9 |

| Figure 5.  | Battery undervoltage shutdown diagram                                        | 17  |

| Figure 6.  | Device state diagram                                                         |     |

| Figure 7.  | Example of PWM mode                                                          | 20  |

| Figure 8.  | Open-load OFF-state detection                                                | 23  |

| Figure 9.  | Example of CS_SYNC synchronization and the current sense pin                 | 24  |

| Figure 10. | Bus master and two devices in a normal configuration                         | 27  |

| Figure 11. | Supported SPI mode                                                           | 27  |

| Figure 12. | SPI write operation                                                          | 30  |

| Figure 13. | SPI read operation                                                           | 30  |

| Figure 14. | SPI read and clear operation                                                 | 31  |

| Figure 15. | SPI read device information                                                  | 32  |

| Figure 16. | Behaviour of overtemperature status bits                                     | 41  |

| Figure 17. | Behaviour of power limitation status bits                                    | 43  |

| Figure 18. | Min duty cycle vs frequency - BULB_MODE                                      | 44  |

| Figure 19. | Min duty cycle vs frequency - LED_MODE                                       | 44  |

| Figure 20. | Current and voltage conventions                                              | 46  |

| Figure 21. | Current sense delay characteristics                                          | 56  |

| Figure 22. | Switching characteristics                                                    | 57  |

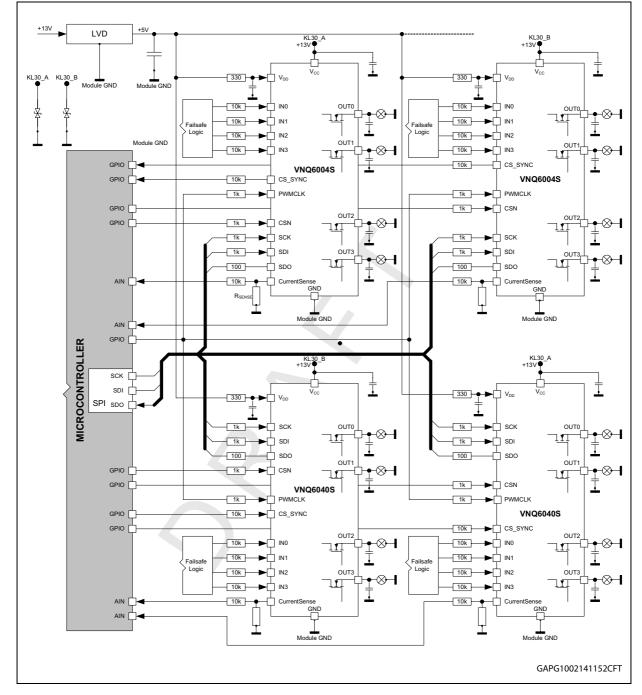

| Figure 23. | Application schematic                                                        | 59  |

| Figure 24. | Typical application                                                          | 60  |

| Figure 25. | SPI timings                                                                  |     |

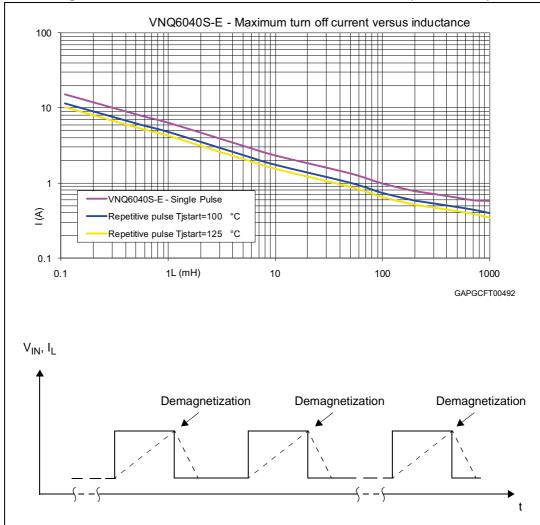

| Figure 26. | Maximum turn off current versus inductance (channel 0-3)                     | 62  |

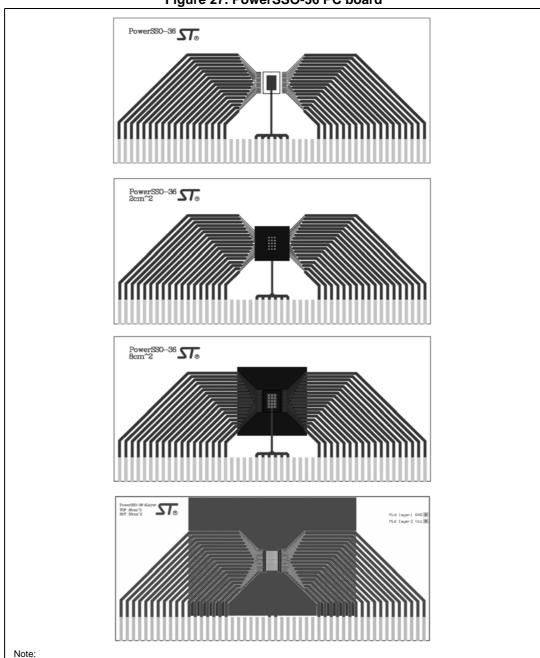

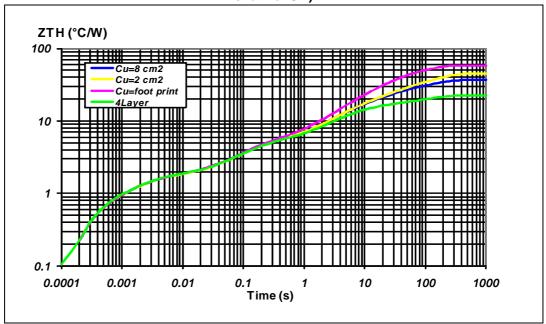

| Figure 27. | PowerSSO-36 PC board                                                         |     |

| Figure 28. | Rthj-amb vs PCB copper area in open box free air condition (one channel ON)  |     |

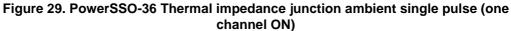

| Figure 29. | PowerSSO-36 Thermal impedance junction ambient single pulse (one channel ON) | 64  |

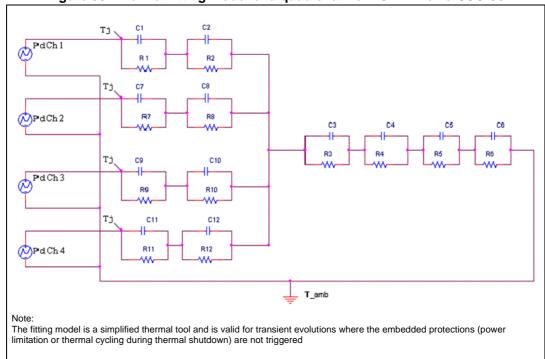

| Figure 30. | Thermal fitting model of a quad channel HSD in PowerSSO-36                   | 65  |

| Figure 31. | PowerSSO-36™ package dimensions                                              | 66  |

| Figure 32. | PowerSSO-36 tape and reel shipment (suffix "TR")                             | 68  |

# 1 Block diagram and pin description

Figure 1. SPI configurable functionalities

Figure 2. SPI diagnostic reporting

577

Figure 3. Block diagram

DocID18061 Rev 11

9/73

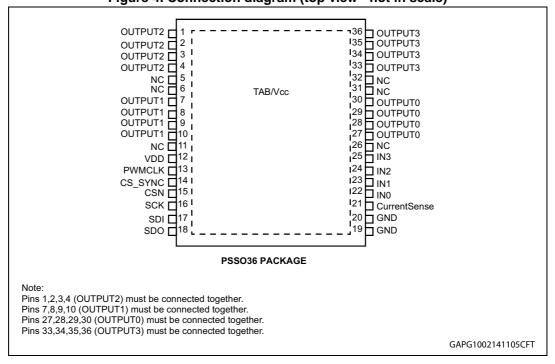

Table 1. Pin functionality description

| Pin number     | Name            | Function                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|----------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| _              | V <sub>CC</sub> | Battery connection. This is the backside TAB and is the direct connection to drain Power MOSFET switches.                                                                                                                                                                                                                   |  |  |  |  |

| 19, 20         | GND             | Ground connection. This pin serves as the ground connection for the logic part of the device.                                                                                                                                                                                                                               |  |  |  |  |

| 27, 28, 29, 30 | OUTPUT0         | Power OUTPUT 0. It is the direct connection to the source Power MOSFET switch No. 0.                                                                                                                                                                                                                                        |  |  |  |  |

| 7, 8, 9, 10    | OUTPUT1         | Power OUTPUT 1. It is the direct connection to the source Power MOSFET switch No. 1.                                                                                                                                                                                                                                        |  |  |  |  |

| 1, 2, 3, 4     | OUTPUT2         | Power OUTPUT 2. It is the direct connection to the source Power MOSFET switch No. 2.                                                                                                                                                                                                                                        |  |  |  |  |

| 33, 34, 35, 36 | OUTPUT3         | Power OUTPUT 3. It is the direct connection to the source Power MOSFET switch No. 3.                                                                                                                                                                                                                                        |  |  |  |  |

| 15             | CSN             | Chip Select Not (Active low). It is the selection pin of the device. It is CMOS compatible input. It is also used as CSN monitoring pin. It must be toggled within a CSN monitoring Time-out period to keep the device alive.                                                                                               |  |  |  |  |

| 16             | SCK             | Serial Clock. It is a CMOS compatible input.                                                                                                                                                                                                                                                                                |  |  |  |  |

| 17             | SDI             | Serial Data Input. Transfers data to be written serially into the device on SCK rising edge.                                                                                                                                                                                                                                |  |  |  |  |

| 18             | SDO             | Serial Data Output. Transfers data serially out of the device on SCK falling edge.                                                                                                                                                                                                                                          |  |  |  |  |

| 13             | PWMCLK          | PWM external clock. The frequency of the internal PWM signal is 1/512xPWM CLK frequency for channels operating in BULB mode and 1/256xPWM CLK frequency for channels operating in LED mode. Device defaults to internally generated fixed PWM frequencies if PWM CLK frequency decreases below the minimum specified value. |  |  |  |  |

| 14             | CS_SYNC         | Current sense synchronization pin. The pin is high when the outputs, whose currents are reflected on current sense pin, are on.                                                                                                                                                                                             |  |  |  |  |

| 22             | IN0             | Direct Input pin for channel 0. Controls the OUTPUT 0 state in Limp Home mode.                                                                                                                                                                                                                                              |  |  |  |  |

| 23             | IN1             | Direct Input pin for channel 1. Controls the OUTPUT 1 state in Limp Home mode.                                                                                                                                                                                                                                              |  |  |  |  |

| 24             | IN2             | Direct Input pin for channel 2. Controls the OUTPUT 2 state in Limp Home mode.                                                                                                                                                                                                                                              |  |  |  |  |

| 25             | IN3             | Direct Input pin for channel 3. Controls the OUTPUT 3 state in Limp Home mode.                                                                                                                                                                                                                                              |  |  |  |  |

| 12             | V <sub>DD</sub> | External 5V Supply. Powers the SPI interface.                                                                                                                                                                                                                                                                               |  |  |  |  |

Table 1. Pin functionality description (continued)

| Pin number              | Name         | Function                                                                                                                                                                                                                                                                                                                            |

|-------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21                      | CurrentSense | Analog current sense generator proportional to output current. Current Sense ratio can be programmed for each channel. The pin can output the current sense of OUTPUT 0, 1, 2 or 3. The value of resistance that is connected between the CURRENT SENSE pin and device ground determines the reading level for the microcontroller. |

| 5, 6, 11, 26,<br>31, 32 | NC           | Not connected.                                                                                                                                                                                                                                                                                                                      |

# 2 Functional description

# 2.1 Operating modes

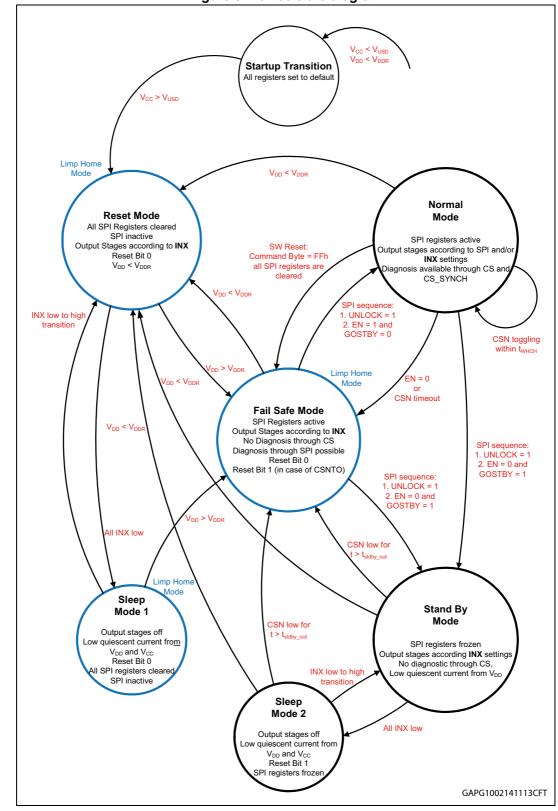

The device can operate in 7 different modes:

Reset mode

Reset mode is entered after startup, and if the digital voltage  $V_{DD}$  falls below  $V_{DDR}$ . In this condition, the outputs are controlled by the direct inputs INX. The SPI is inactive, all SPI registers are cleared.

Fail Safe mode

After reset, after wake-up from Standby or Sleep mode 1 or 2 and in case of several error conditions, the device operates in Fail Safe mode. In this condition, the outputs are controlled by the direct inputs INX regardless of SPI commands. Diagnosis is available through SPI bus.

Normal mode

If the device is in Fail Safe mode, Normal mode can be entered using a special SPI sequence. In Normal mode, outputs can be driven by SPI commands or a combination of SPI command and direct inputs INX. Diagnosis is available through SPI bus and CurrentSense pin.

Standby mode

If the device is in Normal mode or Fail Safe mode, Standby mode can be entered using a special SPI sequence. In Standby mode the consumption of the digital part is nearly 0. The outputs are controlled by the direct inputs INX regardless of SPI commands.

Sleep mode 1

If the device is in Reset mode and the direct inputs INX are all 0, the device enters Sleep mode 1. In Sleep mode 1, the output stages are off, the current consumption of the digital part is nearly 0 and the current consumption on  $V_{CC}$  is below  $I_{Soff}$ .

Sleep mode 2

If the device is in Standby mode and the direct inputs INX are all 0, the device enters Sleep mode 2. In Sleep mode 2, the output stages are off, the current consumption of the digital part is nearly 0 and the current consumption on  $V_{CC}$  is below  $I_{Soff}$ .

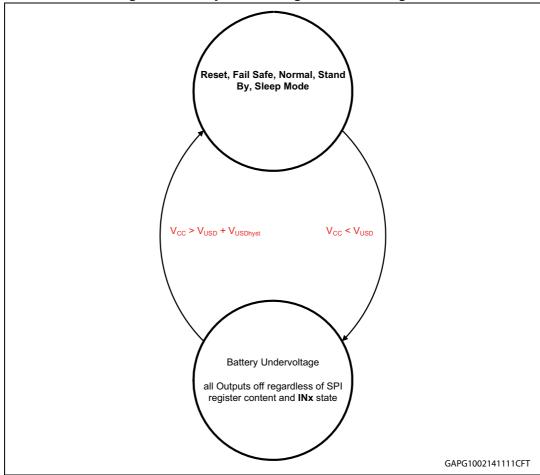

Battery undervoltage mode

If the battery voltage  $V_{CC}$  is below the undervoltage threshold, the device enters Battery undervoltage mode. In this condition, the output stages are off regardless of SPI commands.

The Reset mode, the Fail Safe mode and the Sleep mode 1 are combined into the Limp home mode. In this mode the chip is able to operate without the connection to the SPI. All transitions between the states in limp home mode are driven by  $V_{DD}$  and INX. The outputs are controlled by the direct inputs INX.

For an overview over the operating modes and the triggering conditions please refer to *Table 2*.

**577**

**Table 2. Operating modes**

| Operating mode | Entering conditions                                                                                                                                                                                                                           | Leaving conditions                                                                                                                                                                                                                     | Characteristics                                                                                                                                                                                                                |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reset          | <ul> <li>Startup</li> <li>Any mode:</li> <li>V<sub>DD</sub> &lt; V<sub>DDR</sub></li> <li>Sleep 1:</li> <li>INX low to high</li> </ul>                                                                                                        | <ul><li>All INX low: sleep 1</li><li>V<sub>DD</sub> &gt; V<sub>DDR</sub>: fail safe</li></ul>                                                                                                                                          | <ul> <li>Outputs: according to INX</li> <li>SPI: inactive</li> <li>Registers: cleared</li> <li>Diagnostics: not available</li> </ul>                                                                                           |

| Fail Safe      | <ul> <li>Reset or sleep 1:         V<sub>DD</sub> &gt; V<sub>DDR</sub> </li> <li>Standby or sleep 2:         CSN low for t &gt; t<sub>stdby_out</sub> </li> <li>Normal:         EN = 0         or CSN time out         or SW reset</li> </ul> | - V <sub>DD</sub> < V <sub>DDR</sub> : reset - SPI sequence 1. UNLOCK = 1 2. STBY = 0 and EN = 1: normal - SPI sequence 1. UNLOCK = 1 2. STBY = 1 and EN = 0: fail safe                                                                | <ul> <li>Outputs: according to INX</li> <li>SPI: active</li> <li>Registers: read/writeable, cleared if entered after HW or SW reset</li> <li>Diagnostics: SPI possible CurrentSense not possible</li> </ul>                    |

| Normal         | <ul> <li>Fail Safe:</li> <li>SPI sequence</li> <li>1. UNLOCK = 1</li> <li>2. STBY = 0</li> <li>and EN = 1</li> </ul>                                                                                                                          | <ul> <li>V<sub>DD</sub> &lt; V<sub>DDR</sub>: reset</li> <li>SPI sequence</li> <li>1. UNLOCK = 1</li> <li>2. STBY = 1</li> <li>and EN = 0: standby</li> <li>EN = 0</li> <li>or CSN time out</li> <li>or SW reset: fail safe</li> </ul> | <ul> <li>Outputs: according to SPI register settings and INX</li> <li>SPI: active</li> <li>Registers: read/writeable</li> <li>Diagnostics: SPI and CurrentSense possible</li> <li>Regular toggling of CSN necessary</li> </ul> |

| Standby        | <ul> <li>Normal: SPI sequence</li> <li>1. UNLOCK=1</li> <li>2. STBY = 1 and EN = 0</li> <li>Fail Safe: SPI sequence</li> <li>1. UNLOCK=1</li> <li>2. STBY = 1 and EN = 0</li> <li>Sleep 2:</li> <li>INX low to high</li> </ul>                | <ul> <li>V<sub>DD</sub> &lt; V<sub>DDR</sub>: reset</li> <li>CSN low for t&gt;t<sub>stdby_out</sub>: fail safe</li> <li>All INX low: sleep 2</li> </ul>                                                                                | <ul> <li>Outputs: according to INX</li> <li>SPI: inactive</li> <li>Registers: frozen</li> <li>Diagnostics: not available</li> <li>Low supply current from V<sub>DD</sub></li> </ul>                                            |

| Sleep 1        | - Reset: all INX = 0                                                                                                                                                                                                                          | <ul><li>V<sub>DD</sub> &gt; V<sub>DDR</sub>: fail safe</li><li>INX low to high: reset</li></ul>                                                                                                                                        | <ul> <li>Outputs: OFF</li> <li>SPI: inactive</li> <li>Registers: cleared</li> <li>Diagnostics: not available</li> <li>Low supply current from V<sub>DD</sub> and V<sub>CC</sub></li> </ul>                                     |

Operating **Entering conditions** Leaving conditions Characteristics mode Outputs: OFF  $V_{DD} < V_{DDR}$ : reset SPI: inactive CSN low for  $t > t_{stdby\_out}$ : fail - Registers: frozen Standby: all INX = 0 Sleep 2 Diagnostics: not available INX low to high: standby Low supply current from V<sub>DD</sub> and  $V_{CC}$ - Outputs: OFF SPI: active Battery  $V_{CC} > V_{USD}$ : back to last Any mode: V<sub>CC</sub> < V<sub>USD</sub> Register: read/writeable undervoltage Diagnostics: SPI possible, CurrentSense not possible

Table 2. Operating modes (continued)

#### 2.1.1 Reset mode

The device enters Reset mode under 3 conditions:

- Automatically during startup

- If it is in any other mode and if V<sub>DD</sub> falls below V<sub>DDR</sub>

- If it is in Sleep mode 1 and if one input INX is set to 1

In Reset mode, the output stages are controlled by INX inputs. The SPI is inactive and all SPI registers are cleared. The reset bit inside the Global Status Byte is set to 0. The diagnostics is not available, but the protections are fully functional. In case of over temperature or power limitation, the outputs work in Autorestart.

Reset mode can be left with 2 conditions:

- If V<sub>DD</sub> rises above V<sub>DDR</sub>, the device enters Fail Safe mode

- If all inputs INX are 0, the device enters Sleep mode 1.

#### 2.1.2 Fail Safe mode

The device enters Fail Safe mode under 5 conditions:

- If it is in Reset mode or in Sleep mode 1 and V<sub>DD</sub> rises above V<sub>DDR</sub>

- If it is in Standby mode or in Sleep mode 2 and CSN is low for t > t<sub>stdby out</sub>

- If it is in Normal mode and bit EN is cleared

- If it is in Normal mode and CSN is not toggled within t<sub>WHCH</sub> (CSN timeout)

- If it is in Normal mode and the SPI sends a SW reset (Command byte = FFh).

In Fail Safe mode, the output stages are according to the inputs INX. The SPI is active. The reset bit is 0 if the last state was Reset mode or the last command was a SW reset and it is set to 1 after the first SPI access. The SPI diagnostics is available, the CurrentSense pin is not available. The protections are fully functional. In case of over temperature or power limitation, the outputs work in Autorestart.

Fail Safe mode can be left with 2 conditions:

- If the SPI sends the goto Normal mode sequence, the device enters Normal mode:

- In a first communication set bit UNLOCK = 1

In the consecutive communication set bit STBY = 0 and bit EN = 1

- This mechanism avoids entering the Normal mode unintentionally.

- If the SPI sends the goto standby mode sequence, the device enters Standby mode:

- In a first communication set bit UNLOCK = 1

In the consecutive communication set bit STBY = 1 and bit EN = 0

- This mechanism avoids entering the Standby mode unintentionally.

- If V<sub>DD</sub> falls below V<sub>DDR</sub>, the device enters Reset mode.

### 2.1.3 Normal mode

The device enters Normal mode, if it is in Fail Safe mode and if the SPI sends the goto Normal mode sequence:

- In a first communication set bit UNLOCK = 1

In the consecutive communication set bit STBY = 0 and bit EN = 1

- This mechanism avoids entering the Normal mode unintentionally.

In Normal mode, the output stages are controlled by the SPI and the INX settings. The SPI is active. CSN must be toggled regularly within  $t_{WHCH}$  to keep the device in Normal mode. The SPI diagnostics and the CurrentSense pin are both available. The protection are fully functional. The outputs can be set to Autorestart or Latch. In Autorestart the outputs are switched on again automatically after an over temperature or power limitation event, while in Latch the relevant status register has to be cleared to switch them on again.

Normal mode can be left with 5 conditions:

- If V<sub>DD</sub> falls below V<sub>DDR</sub>, the device enters Reset mode.

- If the SPI sends the goto standby sequence, the devices enters Standby mode:

- In a first communication set UNLOCK = 1

In the consecutive communication set STBY = 1 and EN = 0

- This mechanism avoids entering the Standby mode unintentionally.

- If the SPI clears the EN bit (EN = 0), the devices enters Fail Safe mode

- CSN time out: If CSN is not toggled within the minimum CSN monitoring timeout period t<sub>WHCH</sub>, the device enters Fail Safe mode.

- If the SPI sends a SW reset command (Command byte = FFh), all registers are cleared and the device enters Fail Safe mode.

### 2.1.4 Standby mode

The device enters Standby mode under three conditions:

- If it is in Fail Safe mode and the SPI sends the goto standby sequence:

- In a first communication set UNLOCK = 1

In the consecutive communication set STBY = 1 and EN = 0

- This mechanism avoids entering the Standby mode unintentionally.

- If it is in Normal mode and the SPI sends the goto standby sequence:

- In a first communication set UNLOCK = 1

In the consecutive communication set STBY = 1 and EN = 0

- This mechanism avoids entering the Standby mode unintentionally.

- If it is in Sleep mode 2 and one input INX is set to one.

The output stages are according to INX settings, the current from  $V_{DD}$  is nearly 0.The SPI is inactive and all registers are frozen to the last state. The diagnostics is not available.

Standby mode can be left with 3 conditions:

- If V<sub>DD</sub> falls below V<sub>DDR</sub>, the device enters Reset mode.

- If CSN is low for t > t<sub>stdby\_out</sub>, the device wakes up. As EN has been set to 0, the device

enters Fail Safe mode and recovers full functionality with command of the outputs and

diagnostics.

- If all direct inputs INX are 0, the device enters Sleep Mode 2 resulting in minimal supply current from V<sub>CC</sub> and V<sub>DD</sub>.

### 2.1.5 Sleep mode 1

The device enters Sleep mode 1, if it is in Reset mode and if all inputs INX are 0.

All outputs are off, the current from  $V_{DD}$  is nearly 0, and the current from  $V_{CC}$  is reduced to  $I_{Soff}$ . The SPI is inactive and all registers are cleared. The diagnostics is not available.

Sleep mode 1 can be left with 2 conditions:

- If V<sub>DD</sub> rises above V<sub>DDR</sub>, the device enters Fail Safe mode.

- If one of the inputs INX is set to 1, the device enters Reset mode.

### 2.1.6 Sleep mode 2

The device enters Sleep mode 2, if it is in Standby mode and if all inputs INX are 0.

All outputs are off, the current from  $V_{DD}$  is nearly 0, and the current from  $V_{CC}$  is reduced to  $I_{Soff}$ . The SPI is inactive and all registers are frozen to the last state. The diagnostics is not available.

Sleep mode 2 can be left with 3 conditions:

- If V<sub>DD</sub> falls below V<sub>DDR</sub>, the device enters Reset mode.

- If CSN is low for t > t<sub>stdby\_out</sub>, the device enters Fail Safe mode.

- If one of the inputs INX is set to 1, the device enters Standby mode.

# 2.1.7 Battery undervoltage mode

If the battery supply voltage  $V_{CC}$  falls below the undervoltage shutdown threshold  $V_{USD}$  while VDD remains above the reset threshold  $V_{DDR}$ , the device enters Battery undervoltage

mode independent from the operation mode. In Battery undervoltage mode, the outputs are turned off. The SPI is active and the SPI register contents are retained. The SPI diagnostics is available, the CurrentSense pin is not available. The bit VCCUV in the general status register GENSTR is set. If  $V_{CC}$  rises above the threshold  $V_{USD} + V_{USDhyst}$ , the device returns to the last mode and VCCUV is cleared.

Figure 5. Battery undervoltage shutdown diagram

Figure 6. Device state diagram

# 2.2 Programmable functions

### 2.2.1 Outputs configuration

The status of the output drivers is configured via the SPI Output Control Register (SOCR), the Direct Input Enable Control Register (DIENCR), the PWM Mode Control Register (PWMCR) and the Channel Control Register (CCR). The DIENCR selects if the outputs OUTPUTX are controlled also by the direct inputs INX or only by the SOCR. The PWMCR selects if the outputs operates in PWM mode. Please refer to *Table 3* for details.

| DIENCRX | INX | SOCRX | PWMCRX | ОИТРИТХ |

|---------|-----|-------|--------|---------|

| 0       | Х   | 0     | 0      | OFF     |

| 0       | Х   | 0     | 1      | OFF     |

| 0       | Х   | 1     | 0      | ON      |

| 0       | Х   | 1     | 1      | PWM     |

| 1       | L   | 0     | 0      | OFF     |

| 1       | L   | 0     | 1      | OFF     |

| 1       | L   | 1     | 0      | ON      |

| 1       | L   | 1     | 1      | PWM     |

| 1       | Н   | Х     | 0      | ON      |

| 1       | Н   | Х     | 1      | PWM     |

Table 3. Output control truth table

The output channels 0 and 1 can be configured to operate in BULB or LED mode using the Channel Control Register (CCR). If the relevant bit in CCR is 0, the output is configured in BULB mode, if it is set to 1, the output is configured in LED mode. This configuration has an influence on the base frequency for PWM operation (see below in this chapter), on the open-load thresholds (see *Chapter 2.2.4*) and on the current sense ratio (see *Chapter 2.2.6*).

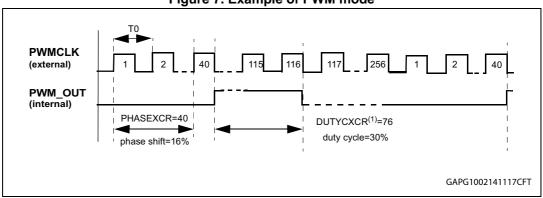

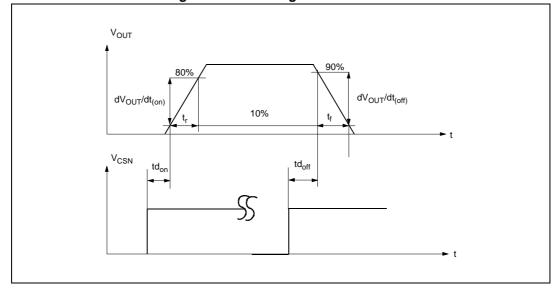

#### **PWM** operation

If the PWMCRX bit is set, the relevant output OUTPUTX operates in PWM mode. The duty cycle and the phase of the PWM signal are configured via the DUTYCXCR and the PHASEXCR registers, respectively.

The signal on the PWMCLK is divided internally by 512 or by 256 depending on the operating mode of the output (BULB mode or LED mode) to generate the base frequency for the output.

The duty cycle of the output signal is configured for each OUTPUTX with the DUTYCXCR register using 8 bits (MSB first). DUTYCXCR = 00h means a duty cycle of 0, consequently in this setting the output is OFF, while DUTYCXCR = FFh results in a maximum duty cycle of 255/256 = 99.6 %. To switch the output permanently ON, it is necessary to select PWMCRX = 0 (see *Table 3*).

The phase shift of the output signal is configured for each OUTPUTX with the PHASEXCR register using 5 bits (MSB first, bit2 ... bit0 are ignored). PHASEXCR = 00h means a phase shift of 0, while PHASEXCR = F8h results in a maximum phase shift of 31/32 = 96.9 %. The

DocID18061 Rev 11 19/73

phase shift is relative to the base frequency of the selected channel. Thus, the exact point in time when the channel switches on depends also on the operating mode (BULB or LED mode) of the selected channel.

Below, an example with a 30% duty cycle and a 16% phase is given:

- 30% duty cycle results in a DUTYCXCR register content equal to 76 = 4Ch (30 % x 256 = 76).

- 2. 16% phase results in a PHASECXR register content equal to 5 (16 %  $\times$  32 = 5), equivalent to a content of 40 = 28 h for a 8 bit register.

Table 4. Example of DUTYCXCR register

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 0     | 1     | 0     | 0     | 1     | 1     | 0     | 0     |

Table 5. Example of PHASEXCR register

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 0     | 0     | 1     | 0     | 1     | Х     | Х     | Х     |

Resulting waveforms can be seen in *Figure 7*.

Figure 7. Example of PWM mode

- Note: 1 If the frequency on PWMCLK is too low ( $f < f_{pwm}$ ), the device falls back to an internally generated PWM frequency of about 160 Hz in BULB mode and 240 Hz in LED mode. In this case the PWMLOW bit in the General Status Register (GENSTR) and the global error flag are set.

- 2 The application should ensure that the duty cycle is not chosen too low. For very low duty cycle there are two restrictions: Due to the slew-rate control of the outputs, the outputs do not switch on and off immediately. Therefore, for low duty cycles, the output pulses are no longer rectangular but change to triangular form, resulting in a non-linear duty cycle power relationship. Moreover, if the output is switched off while the voltage drop on the PowerMOS V<sub>DS</sub> is still above V<sub>DSmax</sub>, this causes a false over load detection (see also Chapter 2.2.3).

### 2.2.2 Case over temperature

If the case temperature rises above the case thermal detection pre-warning threshold  $T_{CSD}$ , the bit  $T_{FRAME}$  in the Global Status Byte is set.  $T_{FRAME}$  is cleared automatically when the

case temperature drops below the case temperature reset threshold  $T_{CR}$ . The typical value of  $T_{CSD}$  can be set using the bits CTDTH1 and CTDTH0 inside the CTLR register (see *Chapter 3.3.1*).

#### 2.2.3 Protections

#### Junction over temperature

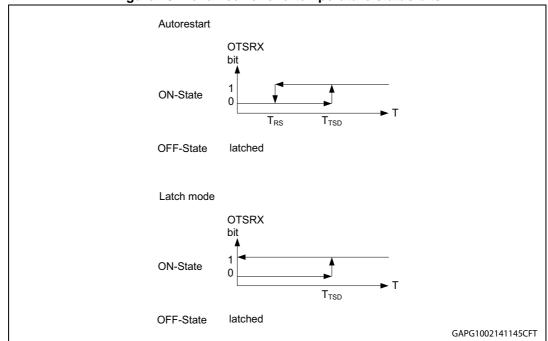

If the junction temperature of one channel rises above the shutdown temperature  $T_{TSD}$ , an over temperature event (OT) is detected. The channel is switched OFF and the corresponding bit in the over temperature status register OTFLTR (address 30h) is set. Consequently, the thermal shutdown bit (bit 4) in the Global Status Byte and the Global Error Flag are set.

Each output channel can be either set in Autorestart or Latched OFF operation in case of junction over temperature event by setting the corresponding ASDTCR register bit (address 08h).

In Autorestart operation, the output is switched off as described and switches on again automatically when the junction temperature falls below the reset temperature  $T_R$ . The status bit is latched during OFF-state of the channel in order to allow asynchronous diagnostic and it is automatically cleared when the junction temperature falls below the thermal reset temperature of OT detection  $T_{RS}$ .

In Latched OFF operation, the output remains switched OFF until the junction temperature falls below  $T_{RS}$  and a read and clear command is sent.

#### **Power limitation**

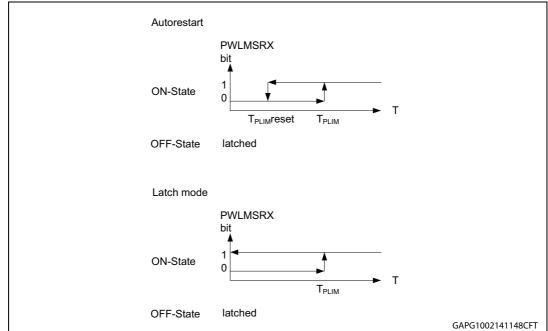

If the difference between junction temperature and case temperature ( $\Delta T = T_j - T_c$ ) rises above the power limitation threshold  $\Delta T_{PLIM}$ , a power limitation event is detected. The corresponding bit in the power limitation status register PWLMFLTR (address 33h) is set and the channel is switched OFF. Consequently, the power limitation bit (bit 4) in the Global Status Byte and the Global Error Flag are set.

Each output channel can be either set in Autorestart or Latched OFF operation in case of power limitation event by setting the corresponding ASDTCR register bit (address 08h).

In Autorestart operation, the output is switched off as described and switches on again automatically when  $\Delta T$  falls below the reset threshold  $\Delta T_{PLIMreset}.$  The status bit is latched during OFF-state of the channel in order to allow asynchronous diagnostic and it is automatically cleared in ON-state when the power limitation event is removed.

In Latched OFF operation, the output remains switched OFF until  $\Delta T$  falls below the reset threshold  $\Delta T_{PLIMreset}$  and a read and clear command is sent.

Each time a channel is switched on via the corresponding bit in SOCR, power limitation events and the relevant diagnostic indication in the PWLMFLTR register are masked for a blanking time  $t_{blanking}$ . The blanking time does not account for an overtemperature event, i.e. the outputs are switched OFF and the relevant bits in OTFLTR are set even during the blanking time, or for an over load event.

The blanking filter is only active, if the channel is turned on through SOCR. There are, however, additional conditions which cause the output to switch from OFF to steady ON-state or to PWM output which do not activate the blanking filter. Refer to *Table 6* for more details.

DocID18061 Rev 11

Blanking filter Action **Output state** Switches from off to steady state or PWM SOCR = 0 to 1 Active according to PWMCR SOCR = 0Switches from off to steady state or PWM DIEN = 1Not active according to PWMCR INX = 0 to 1 SOCR = 1, DIEN = 0 PWMCR = 1 Switches from off to PWM Not active DUTYCRX = 00h to nonzero value SOCR = 1, DIEN = 0 PWMCR = 1 to 0 Switches from off to steady state Not active DUTYCRX = 00h

Table 6. Activation of blanking filter in case of power limitation

#### Over load

During low duty cycle PWM operation on a shorted load, ON-time may be too short to allow power limitation or over temperature detection. Current sense output is 0. This would make detection of this over load condition impossible. To overcome this, always when an output channel is turned OFF, the voltage drop on the PowerMOS ( $V_{DS}$ ) is measured. If  $V_{DS}$  exceeds the threshold  $V_{OVL}$ , an over load condition is detected. The corresponding bit in the over load status register OVLFLTR (address 34H) is set. Consequently, the over load bit (bit 4) in the Global Status Byte and the Global Error Flag are set.

The OVLFLTR is a warning and the channel can be switched on again even if the OVLFLTRX bit is set. The OVLFLTRX bit remains unchanged until a read and clear command on OVLFLTR is sent by the SPI or until the output is turned off the next time, when  $V_{DS}$  is evaluated again.

If the output channel is switched ON for a very short time,  $V_{DS}$  might be greater than  $V_{OVL}$  even if the output is not in over load state so that a false warning is issued. Please refer to *Table 37* for more details.

### 2.2.4 Open-load ON-state detection

If the current through the output during the ON-state falls below the open-load ON-state detection thresholds, an open-load condition is detected for the relevant channel. The corresponding bit in the open-load ON-state status register (OLFLTR) is set. At the same time, the open-load at ON-state bit (bit 2) in the Global Status Byte and the Global Error Flag are set.

Two different open-load ON-state detection thresholds (see *Table 7*) can be set for each channel by writing into OLONCR register (address 06H). For channel related information, bit0 corresponds to channel0, bit1 to channel1, bit2 to channel2, bit3 to channel3.

577

| Table 11 Hermia open lead in conclus |         |                                 |                                |  |  |  |  |

|--------------------------------------|---------|---------------------------------|--------------------------------|--|--|--|--|

| Channel                              | OLONCRX | I <sub>OLnom</sub><br>BULB mode | I <sub>OLnom</sub><br>LED mode |  |  |  |  |

| 0, 1, 2, 3                           | 0       | 40 mA                           | 10 mA                          |  |  |  |  |

|                                      | 1       | 300 mA                          | 100 mA                         |  |  |  |  |

Table 7. Nominal open-load thresholds

### 2.2.5 Open-load OFF-state detection

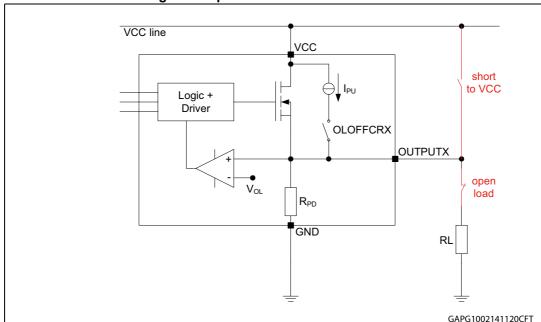

If the output voltage  $V_{OUT}$  in OFF-state of the output is greater than the open-load detection threshold voltage  $V_{OL}$ , an open-load OFF-state / Stuck to  $V_{CC}$  event is detected (see *Figure 8*). The corresponding bit in the Open-load OFF-state / Stuck to VCC status register STKFLTR (Address 32h) is set. Consequently, the OLOFF bit (bit 1) in the Global Status Register and the Global Error Flag are set. To avoid false detection, the diagnosis starts after turn-off of a channel with an additional delay  $t_{DOLOFF}$ .

To distinguish between an open-load OFF-state event and a short to  $V_{CC}$  condition, an internal pull-up current generator can be enabled for each channel by setting the corresponding bit in the open-load OFF-state control register (OLOFFCR, address 07h), see *Table 8*.

The activated pull-up current generators are active in Normal Mode, in Fail Safe Mode and in Standby Mode. In Sleep Mode 2, the current generators are switched off. The register contents, however, are saved also in Sleep Mode 2, consequently the current generators are reactivated after a return to Standby or a wakeup to Fail Safe Mode. A hardware reset  $(V_{DD} < V_{DDR})$  or a software reset (Command byte = FFh) clears all register contents and hence the current generators are switched off.

Figure 8. Open-load OFF-state detection

5

DocID18061 Rev 11

Table 8. STKFLTR state

|                                           | With internal pull-up<br>generator | Without internal pull-up generator |  |

|-------------------------------------------|------------------------------------|------------------------------------|--|

| Case 1: load connected                    | "0" / no fault                     | "0" / no fault                     |  |

| Case 2: no load                           | "1" / fault                        | "0" / no fault                     |  |

| Case 3: output shorted to V <sub>CC</sub> | "1" / fault                        | "1" / fault                        |  |

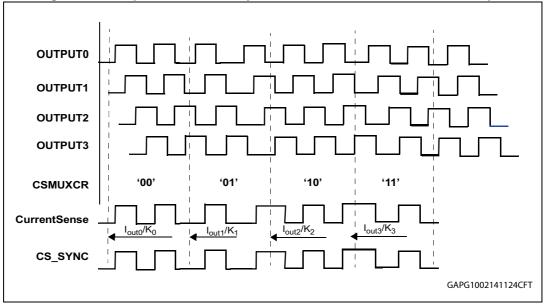

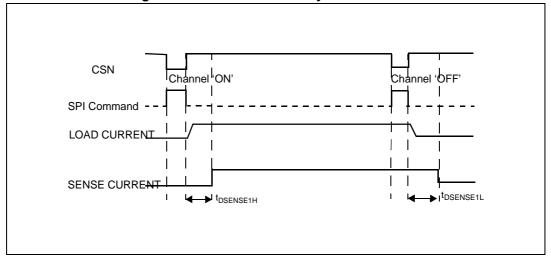

#### 2.2.6 Current sense

Each channel integrates an analog current sense function which can be connected to the current sense pin by setting the CURSEN bit (bit 3) in the CTLR register (address 00H) and by setting the corresponding channel in the CSMUXCR register (address 03H).

The ratio between output current and sense current can be also selected by writing into the CSRATCR register (address 04H).

The current sense ratio is as shown in Table 9.

Table 9. Current sense ratio

| Channel    | CSRATCRX | Current sense ratio K<br>(typical)<br>BULB mode | Current sense ratio K<br>(typical)<br>LED mode |

|------------|----------|-------------------------------------------------|------------------------------------------------|

| 0, 1, 2, 3 | 0        | 1300                                            | 430                                            |

| 0, 1, 2, 3 | 1        | 3800                                            | 1290                                           |

The output CS\_SYNC provides a synchronization signal for the current sense pin. It is "1" if the corresponding output is ON, and "0" if the output is OFF. If no output is selected (CURSEN = 0), CS\_SYNC is in high impedance state. Please refer also to *Figure 9*.

Figure 9. Example of CS\_SYNC synchronization and the current sense pin

# 2.3 Test mode (reserved)

The Digital core and most of the advanced functionalities integrated in the VNQ6040S-E are tested by setting the device in a special Test Mode. In this state, the CSN monitoring timeout control is disabled and the functionality of the other SPI pins (SDI and SDO) might be different from the standardized communication protocol, whilst other pins might be configured as diagnostic I/O's.

Test Mode is intended only for the ST serial production testing flow.

Accessing Test Mode in the application might lead the device to operate in uncontrolled conditions.

Entering Test Mode is prevented by operating the device within its Absolute Maximum Ratings.

DocID18061 Rev 11 25/73

# 3 SPI functional description

### 3.1 SPI communication

The SPI communication is based on a standard ST-SPI 16-bit interface, using CSN, SDI, SDO and SCK signal lines.

Input data are shifted into SDI, MSB first while Output data are shifted out on SDO, MSB first.

## 3.1.1 Signal description

During all operations,  $V_{DD}$  must be held stable and within the specified valid range:  $V_{DD}$  min. to  $V_{DD}$  max.

| Table 10. Of 1 signal description |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Name                              | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Serial clock<br>SCK               | This input signal provides the timing of the serial interface. Data present at Serial Data Input (SDI) are latched on the rising edge of Serial Clock (SCK). Data on Serial Data Output (SDO) change after the falling edge of Serial Clock (SCK).                                                                                                                                                                                                                                                            |  |  |  |  |

| Serial data input<br>SDI          | This input signal is used to transfer data serially into the device. It receives data to be written. Values are sampled on the rising edge of Serial Clock (SCK).                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| Serial data output<br>SDO         | This output signal is used to transfer data serially out of the device. Data are shifted out on the falling edge of Serial Clock (SCK).                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| Chip select<br>CSN                | When this input signal is High, the device is deselected and Serial Data Output (SDO) is high impedance. Driving this input Low enables the communication. The communication must start on a Low level of Serial Clock (SCK). Data are accepted only if exactly 16 bits have been shifted in.  This signal is used as CSN monitoring input and must be toggled within CSN monitoring timeout period to stay in Normal mode. Otherwise the device enters Fail Safe mode. SPI registers contents are unchanged. |  |  |  |  |

Table 10. SPI signal description

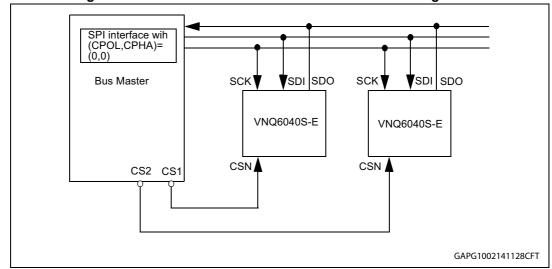

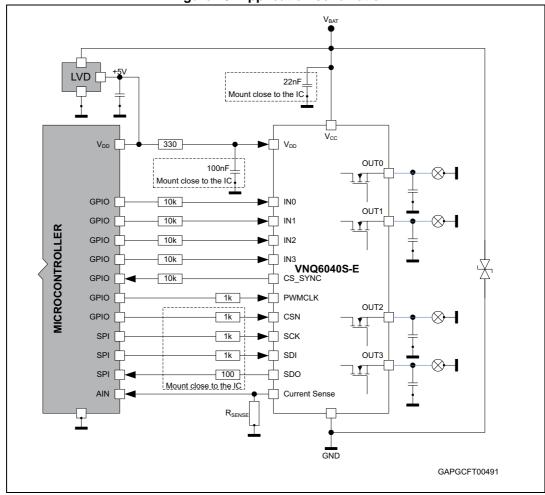

# 3.1.2 Connecting to the SPI bus

A schematic view of the architecture between the bus and devices can be seen in Figure 10.

All input data bytes are shifted into the device, MSB first. The Serial Data Input (SDI) is sampled on the first rising edge of the Serial Clock (SCK) after Chip Select (CSN) goes low.

All output data bytes are shifted out of the device on the falling edge of SCK, MSB first on the first falling edge of the Chip Select (CSN).

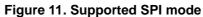

### 3.1.3 **SPI** mode

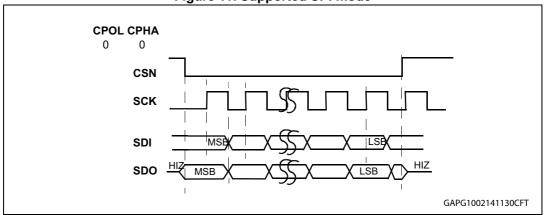

Supported SPI mode during a communication phase can be seen in *Figure 11*.

This device can be driven by a micro controller with its SPI peripheral running in the following mode:

• CPOL=0, CPHA=0

Figure 10. Bus master and two devices in a normal configuration

# 3.2 SPI protocol

## 3.2.1 SDI, SDO format

SDI format during each communication frame starts with a command byte. It begins with two bits of operating code (OC0, OC1) which specify the type of operation (read, write, read and clear status, read device information) and is followed by a 6 bit address (A0:A5). The command byte is followed by an input data byte (D0:D7).

Table 11. Command byte

| MSB |     |    |    |    |    |    | LSB |

|-----|-----|----|----|----|----|----|-----|

| OC1 | OC0 | A5 | A4 | A3 | A2 | A1 | A0  |

DocID18061 Rev 11

Table 12. Input data byte

| MSB |    |    |    |    |    |    | LSB |

|-----|----|----|----|----|----|----|-----|

| D7  | D6 | D5 | D4 | D3 | D2 | D1 | D0  |

SDO format during each communication frame starts with a specific byte called Global Status Byte (see *Section 3.2.2: Global status byte description* for more details of bit0-bit7). This byte is followed by an output data byte (D0:D7).

Table 13. Global status byte

| MSB  |      |      |      |      |      |      | LSB  |

|------|------|------|------|------|------|------|------|

| bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

### Table 14. Output data byte

| MSB |    |    |    |    |    |    | LSB |

|-----|----|----|----|----|----|----|-----|

| D7  | D6 | D5 | D4 | D3 | D2 | D1 | D0  |

# 3.2.2 Global status byte description

The data shifted out on SDO during each communication starts with a specific byte called Global Status Byte. This one is used to inform the microcontroller about global faults which can be happened on the channel part (like thermal shutdown, OLON,...) or on the SPI interface (like CSN monitoring timeout event, communication error,...). This specific register has the following format.

Table 15. Global status byte

| Bit        | Name                | Reset | Content                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------|---------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>(MSB) | Global error flag   | 1     | Active high: this bit is set in case of any fault on any channel or CSNTO, a communication error, a chip reset, a V <sub>CC</sub> undervoltage or a too low PWM clock frequency.  This bit is also accessible while CSN is held low and SCK is stable (high or low). This operation does not set the communication error bit.                                                                                                                                                                                                                                                                                                                                            |

| 6          | Communication error | 0     | Active high: this bit is set at the end of the communication in case of wrong number of clock cycles during a communication frame or invalid bus condition (SPI mode not equal to CPOL = 0, CPHA = 0).  A clock monitor counts the number of clock pulses during a communication frame (while CSN is low). If the number of pulses does not correspond with the frame width indicated in the 'SPI-frame_ID' (address 3Eh), the frame is ignored and the communication error bit is set. The communication error bit can be read in the frame which follows the erroneous one and is automatically cleared once a frame with valid number of clock pulses is transferred. |

Bit Reset Content Name Active low: this bit is low in case of chip reset (hardware reset due to a loss of  $V_{DD}$  supply or Not (ChipReset or software reset) or a communication error (wrong 5 0 ComError) number of clock pulses during a communication frame). The bit is reset when the next valid communication frame is transferred. Thermal shutdown (OT) Active high: this bit is set in case of thermal shutdown or power limitation or in case of high V<sub>DS</sub> (OVL) at Power limitation (PWLM) 0 4 turn-off detected on any channel. The bit reflects the corresponding faulty channel bits in OTFLTR, or PWLMFLTR and OVLFLTR registers. Over load (OVL) Active high: this bit is set if the case temperature is greater than T<sub>CSD</sub> and can be used as a temperature 0 3 T<sub>Frame</sub> prewarning. The bit is cleared automatically when the case temperature drops below the case temperature reset threshold (T<sub>CR</sub>). Active high: this bit is set in case of open-load ON-Open-load at ON-state state detected on any channel. This bit reflects the 2 0 (OLON) corresponding faulty channel bit in the OLFLTR register Active high: this bit is set in case of open-load OFF-Open-load at OFF-state state or output shorted to  $V_{\mbox{\footnotesize CC}}$  condition detected on 1 or output shorted to V<sub>CC</sub> 0 any channel. This bit reflects the corresponding faulty (OLOFF) channel bit in the STKFLTR register. 0 FailSafe 1 Active high: This bit is set in case of failsafe mode. (LSB)

Table 15. Global status byte (continued)

Note:

The FFh or 00h combinations for the Global Status Byte are not possible due to the active low of chip reset bit (bit 5) and the exclusive combination between bit 5 and 6. Consequently a FFh or 00h combination for the Global Status Byte must be detected by the microcontroller as a failure (SDO stuck to GND or to  $V_{DD}$  or loss of SCK).

# 3.2.3 Operating code definition

The SPI interface features four different addressing modes which are listed in Table 16.

Table 16. Operating codes

|     | 1   |                                 |

|-----|-----|---------------------------------|

| OC1 | OC0 | Meaning                         |

| 0   | 0   | Write operation                 |

| 0   | 1   | Read operation                  |

| 1   | 0   | Read and clear status operation |

| 1   | 1   | Read device information         |

DocID18061 Rev 11

#### Write mode

The write mode of the device allows to write the content of the input data byte into the addressed register (see list of registers in *Table 17*). Incoming data are sampled on the rising edge of the serial clock (SCK), MSB first.

During the same sequence outgoing data are shifted out MSB first on the falling edge of the CSN pin and subsequent bits on the falling edge of the serial clock (SCK). The first byte corresponds to the Global Status Byte and the second to the previous content of the addressed register.

CSN Data Command Byte SDI (8 bit) 0 0 MSB Address LSB MSB LSB Global Status Byte Data SDO (8 bit) (previous content of register) LSB MSB LSB MSB GAPG1002141134CFT

Figure 12. SPI write operation

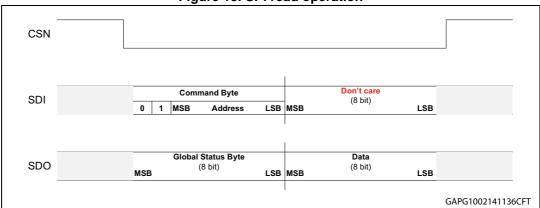

#### Read mode

The read mode of the device allows to read and to check the state of any register.

Incoming data are sampled on the rising edge of the serial clock (SCK), MSB first.

Outgoing data are shifted out MSB first on the falling edge of the CSN pin and others on the falling edge of the serial clock (SCK). The first byte corresponds to the Global Status Byte and the second to the content of the addressed register.

In case of a read mode on an unused address, the 'global status/error' byte on the SDO pin is following by 00H byte.

In order to avoid inconsistency between the Global status byte and the status register, the status register contents are frozen during SPI communication.

Figure 13. SPI read operation

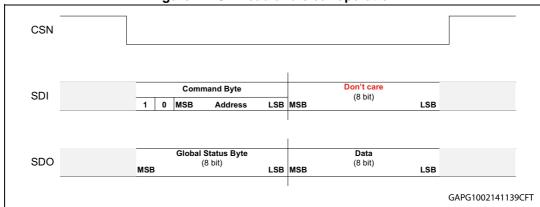

#### Read and clear status command

The read and clear status operation is used to clear the content of the addressed status register (see *Table 17*). A read and clear status operation with address 3Fh clears all status registers simultaneously and reads back the Configuration register (GLOBCTR).

Incoming data are sampled on the rising edge of the serial clock (SCK), MSB first. The command byte allows to determine which register content is read then erased while the data byte is 'don't care'.

Outgoing data are shifted out MSB first on the falling edge of the CSN pin and others on the falling edge of the serial clock (SCK). The first byte corresponds to the Global Status byte and the second to the content of the addressed register.

In order to avoid inconsistency between the Global status byte and the status register, the status register contents are frozen during SPI communication.

Figure 14. SPI read and clear operation

#### **Read device information**

Specific informations can be read but not modified during this mode. Accessible data can be seen in *Table 18*.

Incoming data are sampled on the rising edge of the serial clock (SCK), MSB first. The command byte allows to determine which information is read while the data byte is 'don't care'.

Outgoing data are shifted out MSB first on the falling edge of the CSN pin and others on the falling edge of the serial clock (SCK). The first byte corresponds to the Global Status byte and the second to the content of the addressed register.

57/

CSN Don't care (8 bit) Command Byte SDI 1 MSB LSB Address LSB MSB Global Status Byte (8 bit) Data (8 bit) SDO MSB LSB MSB LSB GAPG1002141141CFT

Figure 15. SPI read device information

#### **Address mapping** 3.3

Table 17. RAM memory map

| Address      | Name     | Access     | Content                                    |

|--------------|----------|------------|--------------------------------------------|

| Control regi | sters    |            |                                            |

| 00h          | CTRL     | Read/write | Device enable, standby, current sense      |

| 01h          | SOCR     | Read/write | SPI Output Control Register                |

| 02h          | DIENCR   | Read/write | Direct Input Enable Control Register       |

| 03h          | CSMUXCR  | Read/write | Current Sense Multiplexer Control Register |

| 04h          | CSRATCR  | Read/write | Current Sense Ratio Control Register       |

| 05h          | PWMCR    | Read/write | PWM Mode Control Register                  |

| 06h          | OLONCR   | Read/write | Open-load ON-state Control Register        |

| 07h          | OLOFFCR  | Read/write | Open-load OFF-state Control Register       |

| 08h          | ASDTCR   | Read/write | Automatic Shutdown Control Register        |

| 09h          | CCR      | Read/write | Channel Control Register                   |

| 0Ah-0Fh      |          |            | not used                                   |

| 10h          | DUTYC0CR | Read/write | Duty Cycle Control Register 0              |

| 11h          | DUTYC1CR | Read/write | Duty Cycle Control Register 2              |

| 12h          | DUTYC2CR | Read/write | Duty Cycle Control Register 2              |

| 13h          | DUTYC3CR | Read/write | Duty Cycle Control Register 3              |

| 14h-17h      |          |            | not used                                   |

| 18h          | PHASE0CR | Read/write | Phase Control Register 0                   |

| 19h          | PHASE1CR | Read/write | Phase Control Register 1                   |

| 1Ah          | PHASE2CR | Read/write | Phase Control Register 2                   |

| 1Bh          | PHASE3CR | Read/write | Phase Control Register 3                   |

| 1Ch-2Dh      |          |            | not used                                   |

DocID18061 Rev 11 32/73

Table 17. RAM memory map (continued)

| A alabasa s     | Mana             | Comtont    |                                                  |  |  |  |  |  |

|-----------------|------------------|------------|--------------------------------------------------|--|--|--|--|--|

| Address         | Name             | Access     | Content                                          |  |  |  |  |  |

| Status regist   | Status registers |            |                                                  |  |  |  |  |  |

| 2Eh             | CHDRVR           | Read only  | Channel Read Back Status Register                |  |  |  |  |  |

| 2Fh             | GENSTR           | Read only  | General Status Register                          |  |  |  |  |  |

| 30h             | OTFLTR           | Read/clear | Over Temperature Status Register                 |  |  |  |  |  |

| 31h             | OLFLTR           | Read/clear | Open-load ON-state Status Register               |  |  |  |  |  |

| 32h             | STKFLTR          | Read/clear | Open-load OFF-state/Stuck to Vcc Status Register |  |  |  |  |  |

| 33h             | PWLMFLTR         | Read/clear | Power Limitation Status Register                 |  |  |  |  |  |

| 34h             | OVLFLTR          | Read/clear | Over load Status Register                        |  |  |  |  |  |

| 35h-3Dh         |                  |            | not used                                         |  |  |  |  |  |

| Other registers |                  |            |                                                  |  |  |  |  |  |

| 3Eh             | TEST             | Read/write | Test Register (reserved)                         |  |  |  |  |  |

| 3Fh             | GLOBCTR          | Read/write | Configuration Register                           |  |  |  |  |  |