## High performance 3-phase motor controller with embedded STM32G4 MCU

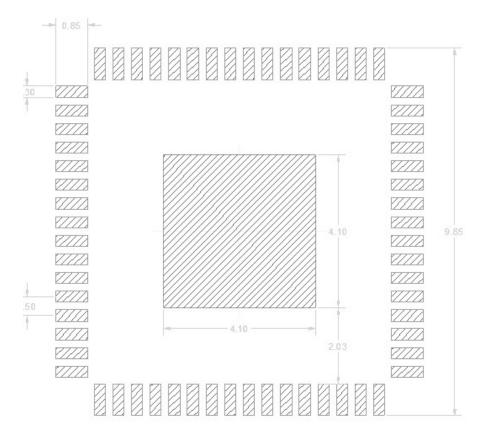

VFQFPN 9x9x1.0 64L

#### **Features**

- Motor supply voltage from 5.5 V to 75 V

- Three-phase gate drivers:

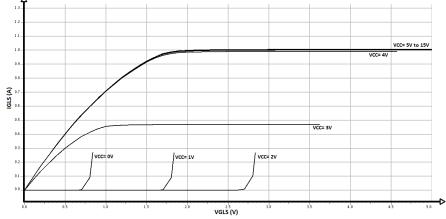

- 1 A sink/source current capability

- VDS monitoring of the power stage MOSFETs

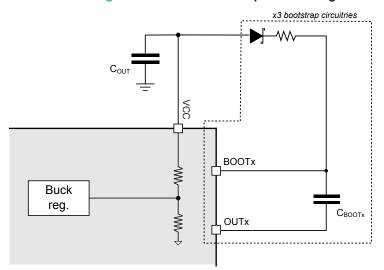

- Integrated bootstrap diodes

- I2C accessible configuration and status registers for best application fit

- Cross-conduction prevention

- STM32G431 microcontroller with 32-bit ARM® Cortex®-M4 MCU+FPU core:

- Up to 170 MHz clock frequency

- CORDIC mathematical hardware accelerator for trigonometric functions

- 128 kB Flash memory with proprietary code readout protection (PCROP), securable memory area, 1 kB OTP

- 32 kB SRAM memory with HW parity check

- 2 x advanced times for motor control, 16-bit with up to 6 x PWM channels

- 8 x general purpose timers

- 2 x ADCs 12-bit resolution (up to 19 channels) with 4 Msps conversion rate

- 4 x 12-bit DAC channels

- 4 x ultra-fast rail-to-rail comparators

- 3 x rail-to-rail operational amplifiers usable also in PGA mode

- Internal high precision voltage reference

- Up to 40 GPIOs

- Full set of interfaces: I2C, SPI, UART and CAN

- Self-supplied thanks to embedded flexible power management

- VCC buck converter up to 200 mA, with programmable output and embedded MOSFET

- 3.3 V LDO linear regulator up to 150 mA

- Low guiescent linear regulator for MCU supply during standby

- Full set of protection features: thermal shutdown, short-circuit, overload and UVLO

- Possibility to control 2 motors simultaneously from the same MCU

- Standby mode for reduced power consumption

- · On-chip debug support via SWD or JTAG

- Extended temperature range: -40 to +125°C

#### **Application**

- Industrial and home automation

- Home appliances such as vacuum cleaners, dryers and cleaning robots

- · Servo drives and e-bikes

- Service and automation robots

- · Power and garden tools

- · Pumps and fans

- Drones and aero modeling

#### **Description**

The STSPIN32G4 is an extremely integrated and flexible motor controller for driving 3-phase brushless motors, helping designers to choose the most suitable driving mode and reduce PCB area and overall Bill Of Materials.

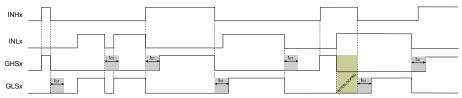

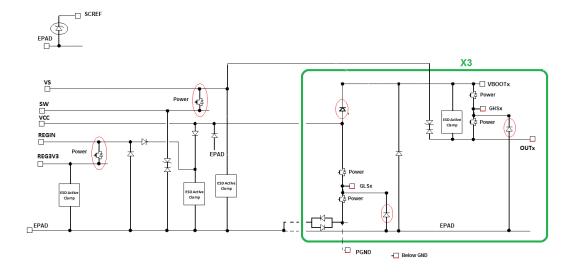

It embeds a triple half-bridge gate driver able to drive power MOSFETs with a current capability of 1 A (sink and source). Three bootstrap diodes are embedded as well. The high- and low-side switches of the same half-bridge cannot be simultaneously driven high thanks to an integrated interlocking function. An additional protection feature is represented by hardware VDS monitoring circuitry that constantly monitors each of the six external MOSFETs and in case an overvoltage is detected across one of them, switches off all gate driver outputs. The overvoltage threshold is set through a dedicated SCREF pin.

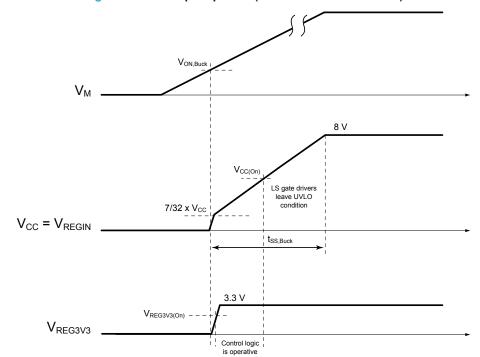

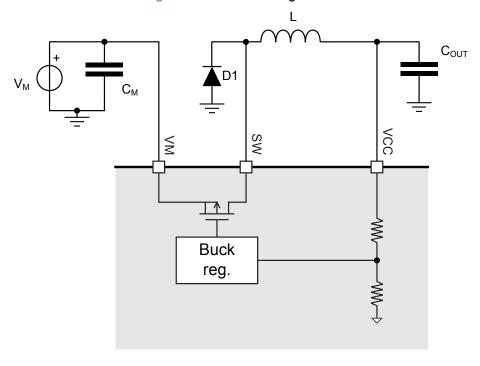

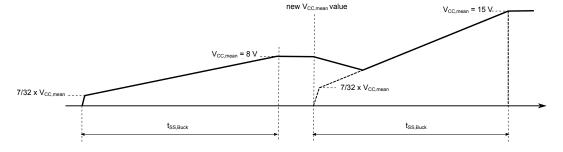

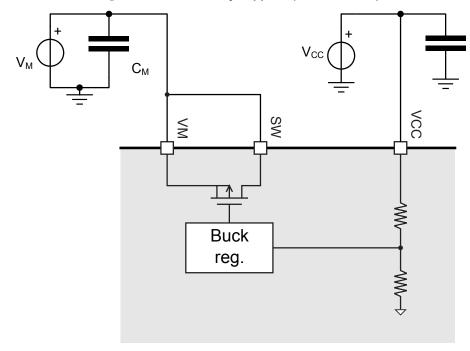

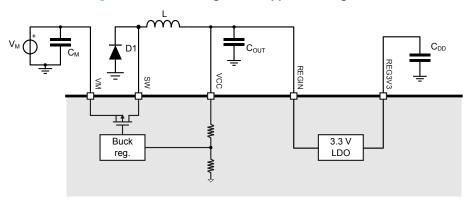

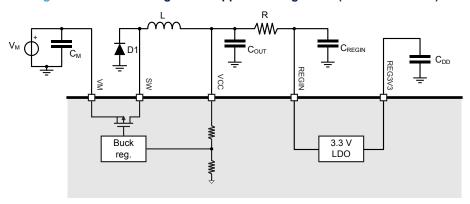

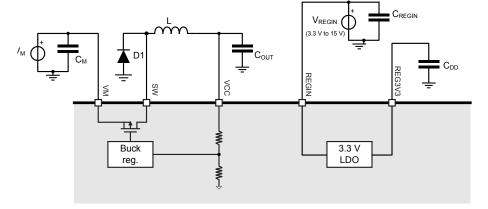

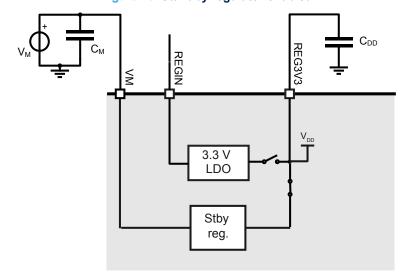

The device is fully self-supplied thanks to an integrated flexible power management structure able to generate all required supplies starting from the motor supply voltage,  $V_M$ ; the only one to be provided from outside. An embedded programmable buck regulator, with embedded power MOSFET, generates the supply voltage for the gate drivers starting from the motor supply voltage  $V_M$ . Four different  $V_{CC}$  output values can be selected through a dedicated configuration register, 8 V (default value), 10 V, 12 V and 15 V.

An internal high precision low-drop linear regulator (LDO) is used to generate the 3.3 V supply ( $V_{REG3V3}$ ) starting from the REGIN input voltage. The 3.3 V output voltage supplies both the gate driver logic and the microcontroller. It is protected against short-circuit, overload and undervoltage conditions.

Both the buck and LDO regulators can be bypassed providing externally  $V_{CC}$  and  $V_{REG3V3}$  supplies.

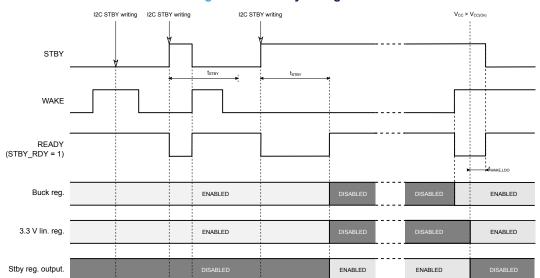

An additional very low-quiescent regulator is used when the STSPIN32G4 is in standby mode, allowing to reduce the overall current consumption down to 15  $\mu$ A typical.

The integrated MCU (STM32G431VBx3) is based on the high-performance 32-bit ARM® Cortex®-M4 core, operating at a frequency up to 170 MHz and featuring a single-precision floating-point unit (FPU), full set of DSP (Digital Signal Processing) instructions and a memory protection unit (MPU), which enhances the application's security.

This microcontroller represents the mainstream choice for advanced motor control applications thanks to the very rich and specific set of features such as: two fast 12-bit ADCs (4 Msps), four comparators, three operational amplifiers, four DAC channels (2 external and 2 internal), an internal voltage reference buffer, one general-purpose 32-bit timer, two 16-bit PWM timers dedicated to motor control, seven general-purpose 16-bit timers, one 16-bit low-power timer.

It also embeds high-speed memories (128 kB of Flash memory, and 32 kB of SRAM) with several protection mechanisms, up to 40 available GPIOs, mathematical/arithmetic function acceleration peripherals (CORDIC for trigonometric functions and FMAC unit for filter functions), main interfaces (I2C, SPI, UART and CAN), a comprehensive set of power-saving modes and an analog independent supply input for ADC, DAC, operational amplifiers and comparators.

Such a feature rich microcontroller allows running very high-performance motor control algorithms offering unprecedented flexibility in choosing the best fitting control choice even for the most challenging motion control applications. Users can program the STSPIN32G4 to run sensorless or sensored Field Oriented Control (FOC) with one, two or three shunts, more advanced position or torque control algorithms or more traditional six-steps control mode.

The STSPIN32G4 also features the full set of protections and an extended temperature range (-40°C to +125°C), guaranteeing stable operation even in the most demanding industrial applications. Both SWD and JTAG interfaces are provided for microcontroller firmware programming and debugging.

Finally, with an additional external three-phase driver (such as the STDRIVE101) two independent 3-phase BLDC motors can be efficiently driven from the STSPIN32G4, offering an unprecedented BOM saving and application optimization.

DS13630 - Rev 1 page 2/48

Downloaded from Arrow.com.

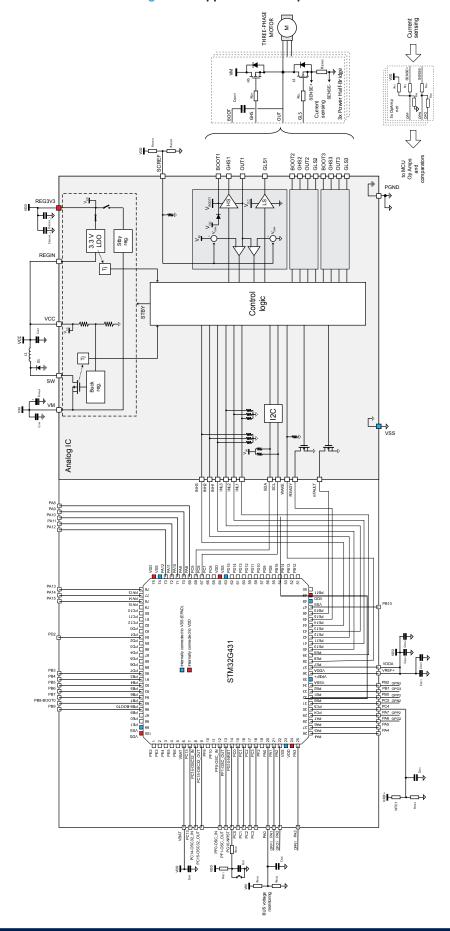

# 1 Block diagram

6 6 183 6 183 6 183 6 183 6 183 6 183 6 183 ڻا< REGIN CONTROL 12C vss PA8 PA9 PA10 PA11 PA12 PA13 PA14 PA15 PB3 PB4 PB5 PB6 PB7 PB8-BOOT0 PB9

Figure 1. STSPIN32G4 system-in-package block diagram

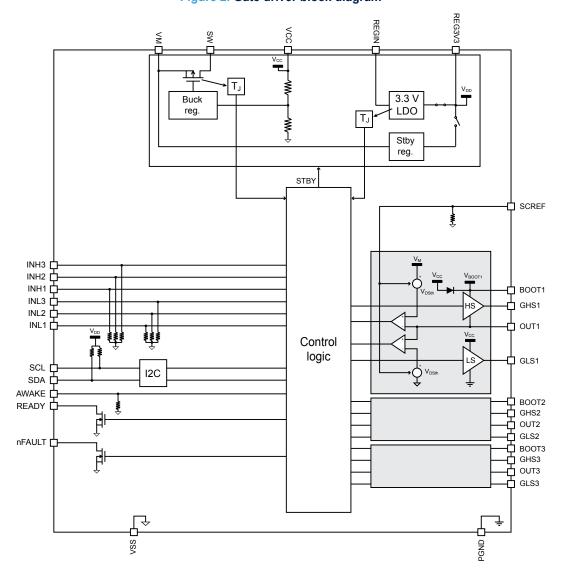

Figure 2. Gate driver block diagram

Downloaded from Arrow.com.

#### 2 Electrical data

#### 2.1 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in Table 1 may cause permanent damage to the device. Exposure to maximum rating conditions for extended periods may affect device reliability.

All voltages referred to ground pins unless otherwise specified.

Table 1. Absolute maximum ratings

| Symbol                                                   | Parameter                                    | Test Condition                           | Value                                                             | Unit |

|----------------------------------------------------------|----------------------------------------------|------------------------------------------|-------------------------------------------------------------------|------|

| $V_{M}$                                                  | Motor supply voltage                         |                                          | -0.3 to 78                                                        | V    |

| V <sub>CC</sub>                                          | Gate driving supply voltage                  |                                          | -0.3 to 20                                                        | V    |

| V <sub>SW</sub>                                          | SW pin voltage                               |                                          | -2 to V <sub>M</sub>                                              | V    |

| V <sub>REGIN</sub>                                       | 3.3 V LDO linear regulator input             |                                          | -0.3 to 20                                                        | V    |

| V <sub>REG3V3</sub>                                      | Logic supply voltage                         |                                          | -0.3 to 3.6                                                       | V    |

| V <sub>REG3V3,drop</sub>                                 | 3.3 V linear regulator voltage drop          | V <sub>REGIN</sub> - V <sub>REG3V3</sub> | -0.3 to 20                                                        | V    |

| P <sub>d,REG3V3</sub>                                    | 3.3 V LDO linear regulator power dissipation |                                          | Up to 1                                                           | W    |

| V <sub>OUTx</sub>                                        | OUTx pins voltage                            |                                          | -2 to V <sub>M</sub> + 2                                          | V    |

| V <sub>BOOTx</sub>                                       | Bootstrap pins voltage                       |                                          | -0.3 to 98                                                        | V    |

| V <sub>BOx</sub>                                         | High-side driver supply voltage              | V <sub>BOOTx</sub> – V <sub>OUTx</sub>   | -0.3 to 20                                                        | V    |

| $V_{GHSx}$                                               | High-side gates voltage                      |                                          | V <sub>OUT</sub> -0.3 to<br>V <sub>BOOT</sub> +0.3                | V    |

| $V_{GLSx}$                                               | Low-side gates voltage                       |                                          | -0.3 to V <sub>CC</sub> +0.3                                      | V    |

| dV <sub>OUT</sub> /dt                                    | Output slew rate                             |                                          | ± 20                                                              | V/ns |

| V <sub>SCREF</sub>                                       | SCREF input                                  |                                          | -0.3 to 3.6                                                       | V    |

| V <sub>DD</sub> , V <sub>DDA</sub> ,<br>V <sub>BAT</sub> | MCU main supply voltages <sup>(1)</sup>      |                                          | -0.3 to 4.0                                                       | V    |

| V <sub>IO</sub>                                          | MCU logic input voltage (1) (2)              | FT_xxx pins except FT_c pins             | $V_{SS}$ -0.3 to min( $V_{DD}$ , $V_{DDA}$ ) + 4.0 <sup>(3)</sup> | V    |

| •10                                                      | Woo logic input voltage                      | FT_c pins                                | V <sub>SS</sub> -0.3 to 5.5                                       | V    |

|                                                          |                                              | TT_xx pins and other pins                | V <sub>SS</sub> -0.3 to 4.0                                       | V    |

| I <sub>IO</sub>                                          | MCU I/O output current <sup>(1)</sup>        |                                          | -20 to 20                                                         | mA   |

| Σιιο                                                     | MCU I/O total output current(1) (4)          |                                          | -100 to 100                                                       | mA   |

| T <sub>STG</sub>                                         | Storage temperature                          |                                          | -55 to 150                                                        | °C   |

| T <sub>J</sub>                                           | Junction temperature                         |                                          | -40 to 150                                                        | °C   |

<sup>1.</sup> Refer to the Absolute maximum ratings section in the STM32G431VBx3 datasheet.

DS13630 - Rev 1 page 5/48

<sup>2.</sup> All main power (VDD, VDDA, VBAT) and ground (VSS, VSSA) pins must always be connected to the external power supply, in the permitted range.

<sup>3.</sup> To sustain a voltage higher than 4 V the internal pull-up/pull-down resistors must be disabled.

<sup>4.</sup> This current consumption must be correctly distributed over all I/Os and control pins.

#### 2.2 **Recommended operating conditions**

All voltages referred to ground pins unless otherwise specified.

Table 2. Recommended operating conditions

| Symbol                   | Parameter                                                 | Test Condition                                 | Min.               | Тур.             | Max.               | Unit  |

|--------------------------|-----------------------------------------------------------|------------------------------------------------|--------------------|------------------|--------------------|-------|

| $V_{M}$                  | Supply voltage                                            |                                                | 5.5 <sup>(1)</sup> |                  | 75                 | V     |

| dV <sub>M</sub> /dt      | Supply voltage slope                                      |                                                |                    |                  | 10                 | V/ µs |

|                          |                                                           | Internally generated, set to 8 V               |                    | 8                |                    | V     |

|                          | VCC Buck conventor                                        | Internally generated, set to 10 V              |                    | 10               |                    | V     |

| $V_{CC}$                 | VCC Buck converter output and gate driving supply voltage | Internally generated, set to 12 V              |                    | 12               |                    | V     |

|                          |                                                           | Internally generated, set to 15 V              |                    | 15               |                    | V     |

|                          |                                                           | Externally provided                            | 5.5 <sup>(1)</sup> |                  | 15                 | V     |

| I <sub>CC</sub>          | VCC Buck converter output current                         |                                                |                    |                  | 200 <sup>(2)</sup> | mA    |

| V <sub>REGIN</sub>       | 3.3 V LDO linear regulator input                          |                                                | 3.3                |                  | 15                 | V     |

| V <sub>REG3V3</sub>      | Logic supply voltage                                      |                                                |                    | 3.3              |                    | V     |

| I <sub>REG3V3</sub>      | 3.3 V linear regulator output current                     |                                                |                    |                  | 150(2)             | mA    |

| I <sub>REG3V3,Stby</sub> | Standby regulator output current                          | V <sub>M</sub> ≥ 8V                            |                    |                  | 6                  | mA    |

| V                        | SCREF input                                               | Protection enabled                             | 0.2                |                  | 2.5                | V     |

| V <sub>SCREF</sub>       | SCREF IIIput                                              | Protection disabled                            | 2.9                |                  | 3.3                | V     |

|                          |                                                           | ADC or COMP used                               | 1.62               |                  | 3.6                | V     |

|                          |                                                           | DAC 1 MSPS or DAC<br>15 MSPS                   | 1.71               |                  | 3.6                | V     |

| $V_{DDA}$                | MCU analog supply                                         | Op-amp used                                    | 2.0                |                  | 3.6                | V     |

| 227.                     | voltage                                                   | VREFBUS used                                   | 2.4                |                  | 3.6                | V     |

|                          |                                                           | ADC, DAC, Op-amp,<br>COMP, VREFBUF not<br>used | 0                  |                  | 3.6                | V     |

| V <sub>BAT</sub>         | MCU backup operating voltage                              |                                                | 1.55               |                  | 3.6                | V     |

| V                        | ADC positive                                              | V <sub>DDA</sub> < 2 V                         | 2                  |                  | $V_{DDA}$          | V     |

| $V_{REF+}$               | reference voltage                                         | V <sub>DDA</sub> < 2 V                         |                    | V <sub>DDA</sub> |                    | V     |

| T <sub>amb</sub>         | Operative ambient temperature                             |                                                | -40                |                  | 125(2)             | °C    |

<sup>1.</sup> Actual operative range can be limited by UVLO protections.

#### 2.3 Thermal data

Thermal values are calculated by simulation with the following boundary conditions: 2s2p board as per the std. JEDEC (JESD51-7) in natural convection, board dimensions: 114.3 x 76.2 x 1.6 mm, ambient temperature: 25°C.

page 6/48

<sup>2.</sup> Actual operative range can be limited by thermal shutdown.

Table 3. Thermal data

| Symbol            | Parameter                                    | Conditions                                 | Value | Unit |

|-------------------|----------------------------------------------|--------------------------------------------|-------|------|

| R <sub>thJA</sub> | Junction-to-ambient thermal resistance       | Natural convection, according to JESD51-2a | 48.3  | °C/W |

| $\Psi_{JT}$       | Junction-to-top characterization parameter   | According to JESD51-2a                     | 1.6   | °C/W |

| ΨЈВ               | Junction-to-board characterization parameter | According to JESD51-2a                     | 32.0  | °C/W |

# 2.4 Electrical sensitivity characteristics

Table 4. ESD protection ratings

| Symbol | Parameter              | Test Condition                                             |  | Value | Unit |

|--------|------------------------|------------------------------------------------------------|--|-------|------|

| HBM    | Human Body Model       | Conforming to ANSI/ESDA/JEDEC JS-001-2014                  |  | 2     | kV   |

| CDM    | Charge Device<br>Model | All pins Conforming to ANSI/ESDA/JEDEC JS-002-2014         |  | 500   | V    |

| CDM    | Charge Device<br>Model | Corner pins only Conforming to ANSI/ESDA/JEDEC JS-002-2014 |  | 750   | V    |

### 3 Electrical characteristics

Testing conditions:  $V_M$  = 60 V,  $V_{CC}$  = 12 V,  $V_{REGIN}$  =  $V_{REG3V3}$  = 3.3 V unless otherwise specified. Typical values are tested at  $T_{amb}$  = 25°C, minimum and maximum values are guaranteed by thermal characterization in the temperature range of -40 to 125°C, unless otherwise specified.

Table 5. Electrical characteristics - Gate driver IC

| Symbol                       | Parameter                                                   | Test condition                                          | Min. | Тур.  | Max. | Unit |

|------------------------------|-------------------------------------------------------------|---------------------------------------------------------|------|-------|------|------|

| Supply                       |                                                             |                                                         |      |       |      |      |

| V <sub>REG3V3(On)</sub>      | Control logic turn-on threshold                             | V <sub>REG3V3</sub> rising                              |      |       | 2.5  | V    |

| V <sub>REG3V3(Off)</sub>     | Control logic turn-off threshold                            | V <sub>REG3V3</sub> falling                             | 1.9  |       |      | V    |

| V <sub>REG3V3Stby(Off)</sub> | Control logic turn-off threshold during standby             | V <sub>REG3V3</sub> falling                             |      | 2.4   |      | V    |

| I <sub>REG3V3,qu</sub>       | Control logic quiescent consumption                         | MCU consumption excluded<br>T <sub>amb</sub> = 25°C     |      | 1.9   | 3    | μА   |

| V <sub>CC(On)</sub>          | V <sub>CC</sub> UVLO turn-on threshold                      | V <sub>CC</sub> rising                                  |      |       | 5.5  | V    |

| V <sub>CC(Hyst)</sub>        | V <sub>CC</sub> UVLO hysteresis                             | V <sub>CC</sub> falling                                 | 70   |       |      | mV   |

| I <sub>CC,qu</sub>           | V <sub>CC</sub> quiescent consumption                       |                                                         |      | 850   | 1700 | μA   |

| V <sub>BO(On)</sub>          | V <sub>BOOT</sub> - V <sub>OUT</sub> UVLO turn-on threshold | V <sub>BOOT</sub> rising                                |      |       | 5    | V    |

| V <sub>BO(Hyst)</sub>        | V <sub>BOOT</sub> - V <sub>OUT</sub> UVLO hysteresis        | V <sub>BOOT</sub> falling                               | 100  |       |      | mV   |

| I <sub>BO,qu</sub>           | VBOOT - VOUT quiescent current                              |                                                         |      | 170   | 250  | μA   |

| I <sub>M,qu</sub>            | VM quiescent consumption                                    | V <sub>CC</sub> = 15 V ext All gate driver outputs low. |      | 1500  | 3000 | μA   |

| VCC buck regul               | ator                                                        |                                                         |      |       |      |      |

| V <sub>ON,Buck</sub>         | Regulator turn-on threshold                                 | V <sub>M</sub> rising                                   | 3    |       | 4.5  | V    |

| V <sub>Hyst,Buck</sub>       | Regulator turn-off hysteresis                               | V <sub>M</sub> falling                                  | 50   | 150   | 250  | mV   |

|                              |                                                             | Set to 8 V, mean value                                  | 7.2  | 8     | 8.8  |      |

| V <sub>CC.mean</sub>         | Regulated output voltage                                    | Set to 10 V, mean value                                 | 9    | 10    | 11   | V    |

| • CC,mean                    | regulated output voltage                                    | Set to 12 V, mean value                                 | 10.8 | 12    | 13.2 |      |

|                              |                                                             | Set to 15 V, mean value                                 | 13.5 | 15    | 16.5 |      |

| V <sub>CC,PkPk</sub>         | Peak-to-peak output ripple                                  | Percentage referred to target V <sub>CC</sub>           |      | 1.875 |      | %    |

| I <sub>peak,Buck</sub>       | Peak current threshold                                      |                                                         |      | 750   |      | mA   |

| f <sub>SW,Buck</sub>         | Switching frequency                                         |                                                         |      | 500   |      | kHz  |

| t <sub>ON,Buck, min</sub>    | Minimum buck ON-time                                        |                                                         |      |       | 220  | ns   |

| t <sub>OFF,Buck min</sub>    | Minimum buck OFF-time                                       |                                                         |      | 220   |      | ns   |

| R <sub>DS(ON),SW</sub>       | PMOS switch on-resistance                                   |                                                         |      | 3     |      | Ω    |

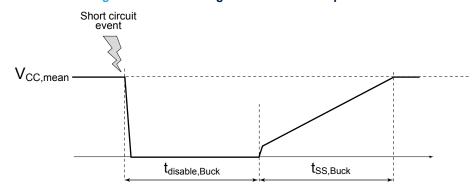

| t <sub>SS,Buck</sub>         | Soft-start time                                             |                                                         |      | 3.3   |      | ms   |

| f <sub>SW,SS</sub>           | Soft-start switching frequency                              |                                                         |      | 60    |      | kHz  |

| t <sub>disable,Buck</sub>    | Disable time                                                |                                                         |      | 4     |      | ms   |

DS13630 - Rev 1 page 8/48

| Symbol                | Parameter                             | Test condition                                        | Min. | Тур. | Max. | Unit |

|-----------------------|---------------------------------------|-------------------------------------------------------|------|------|------|------|

| I <sub>OC,Buck</sub>  | Buck converter overcurrent threshold  |                                                       |      | 1.2  |      | А    |

| T <sub>SD</sub>       | Shutdown temperature                  |                                                       | 140  |      | 160  | °C   |

| T <sub>SD(Hyst)</sub> | Thermal shutdown hysteresis           |                                                       |      | 30   |      | °C   |

| 3.3 V Linear re       | gulator                               |                                                       |      |      |      |      |

|                       | 3.3 V linear regulator output         | V <sub>REGIN</sub> = 5 V                              | 0.4  | 0.0  | 0.5  | l ., |

| V <sub>REG3V3</sub>   | and logic supply voltage              | I <sub>REG3V3</sub> = 150 mA                          | 3.1  | 3.3  | 3.5  | V    |

| REG3V3lim             | 3.3 V linear regulator current limit  | REG3V3 shorted to ground                              | 151  |      |      | mA   |

| T <sub>SD</sub>       | Shutdown temperature                  |                                                       | 140  |      | 160  | °C   |

| T <sub>SD(Hyst)</sub> | Thermal shutdown hysteresis           |                                                       |      | 30   |      | °C   |

| Gate drivers          |                                       |                                                       |      |      |      |      |

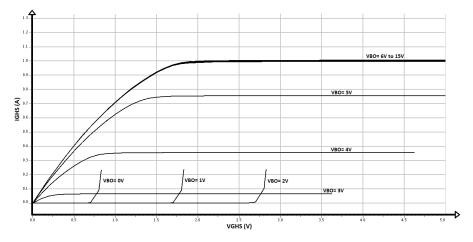

|                       |                                       | V <sub>CC</sub> = 5.5 V to 15 V                       |      |      |      |      |

|                       |                                       | V <sub>BOx</sub> = 5.5 V to 15 V                      | 700  | 1000 | 1300 | mA   |

|                       | Ointe (annual annual annual airte     | T <sub>amb</sub> = 25°C                               |      |      |      |      |

| gate                  | Sink/source current capabilities      | V <sub>CC</sub> = 5.5 V to 15 V                       |      |      |      |      |

|                       |                                       | V <sub>BOx</sub> = 5.5 V to 15 V                      | 500  |      | 1500 | mA   |

|                       |                                       | Full temperature range                                |      |      |      |      |

|                       |                                       | V <sub>CC</sub> = 12 V, V <sub>BOx</sub> = 12 V       |      |      |      |      |

|                       |                                       | I <sub>source</sub> = 100 mA                          |      | 3.7  |      | Ω    |

| D                     | DMOC on resistance                    | T <sub>amb</sub> = 25°C                               |      |      |      |      |

| R <sub>PMOS</sub>     | PMOS on-resistance                    | V <sub>CC</sub> = 12 V, V <sub>BOx</sub> = 12 V       |      |      |      |      |

|                       |                                       | I <sub>source</sub> = 100 mA                          |      |      | 5.8  | Ω    |

|                       |                                       | Full temperature range                                |      |      |      |      |

|                       |                                       | V <sub>CC</sub> = 12 V, V <sub>BOx</sub> = 12 V       |      |      |      |      |

|                       |                                       | I <sub>sink</sub> = 100 mA                            |      | 1.6  |      | Ω    |

| 2                     | NIMOS on registance                   | T <sub>amb</sub> = 25°C                               |      |      |      |      |

| R <sub>NMOS</sub>     | NMOS on-resistance                    | V <sub>CC</sub> = 12 V, V <sub>BOx</sub> = 12 V       |      |      |      |      |

|                       |                                       | I <sub>sink</sub> = 100 mA                            |      |      | 2.6  | Ω    |

|                       |                                       | Full temperature range                                |      |      |      |      |

| DT                    | Deadtime                              | Minimum deadtime enabled                              |      | 150  |      | ns   |

|                       | OUT: him assument                     | $V_{OUTx} = V_M = 60 \text{ V}$                       |      | 180  | 260  | μA   |

| OUTx,bias             | OUTx bias current                     | V <sub>OUTx</sub> = 0 V                               |      | 180  | 260  | μA   |

|                       |                                       | V <sub>CC</sub> = 5.5 V to 15 V                       |      |      |      |      |

|                       |                                       | V <sub>BOOTx</sub> -V <sub>OUTx</sub> = 5.5 V to 15 V |      | 30   | 60   | ns   |

| on, t <sub>off</sub>  | Input to output propagation delay     | V <sub>CC</sub> = 5.5 V to 15 V                       |      |      |      |      |

|                       | dolay                                 | V <sub>BOOTx</sub> -V <sub>OUTx</sub> = 5.5 V to 15 V |      |      | 120  | ns   |

|                       |                                       | Full temperature range                                |      |      |      |      |

| MT                    | Delay matching, HS and LS turn-on/off | (1)                                                   |      | 0    | 50   | ns   |

DS13630 - Rev 1 page 9/48

| Symbol                         | Parameter                                              | Test condition                                      | Min. | Тур. | Max. | Unit |

|--------------------------------|--------------------------------------------------------|-----------------------------------------------------|------|------|------|------|

| MT <sub>CH</sub>               | Delay matching between channels                        | (2)                                                 |      | 0    | 50   | ns   |

| R <sub>DS_diode</sub>          | Bootstrap diode on-resistance                          |                                                     |      | 100  | 200  | Ω    |

| R <sub>PDin</sub>              | Input lines pull-down resistor                         |                                                     |      | 500  |      | kΩ   |

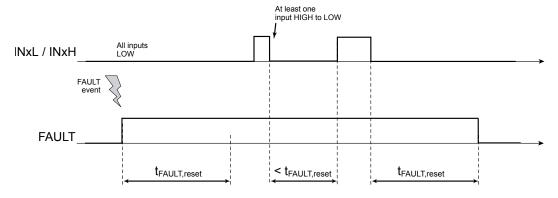

| t <sub>FAULT,reset</sub>       | Fault reset time                                       |                                                     |      |      | 160  | μs   |

| R <sub>PU,I<sup>2</sup>C</sub> | I2C lines pull-up resistors                            |                                                     |      | 4    |      | kΩ   |

| I <sup>2</sup> C speed         | I2C speed                                              |                                                     | 0.1  |      | 1    | Mbps |

| Standby                        |                                                        |                                                     |      |      |      |      |

|                                | O complication discovered from                         | V <sub>M</sub> = 75 V                               |      |      |      |      |

| I <sub>STBY</sub>              | Overall standby consumption from VM                    | Standby regulator enabled, MCU consumption excluded |      | 15   | 30   | μA   |

| t <sub>STBY</sub>              | Standby time                                           |                                                     |      | 100  |      | μs   |

| V <sub>REGStby</sub>           | Standby regulator output voltage                       | V <sub>M</sub> = 5 V<br>I <sub>REG3V3</sub> = 1 mA  | 3    | 3.3  | 3.6  | V    |

| I <sub>REGStby,lim</sub>       | Standby regulator current limit                        | V <sub>M</sub> = 5.5 V, T <sub>amb</sub> = 25°C     | 5    |      |      | mA   |

| t <sub>WAKE,LDO</sub>          | 3.3V LDO wake-up time                                  |                                                     |      | 10   |      | μs   |

| VDS monitorii                  | ng protection                                          |                                                     | ı    | 1    |      |      |

|                                |                                                        | V <sub>SCREF</sub> = 0.2 V, T <sub>amb</sub> = 25°C | 0.1  | 0.2  | 0.3  |      |

| $V_{DSth}$                     | VDS monitoring protection threshold                    | V <sub>SCREF</sub> = 1 V, T <sub>amb</sub> = 25°C   | 0.8  | 1    | 1.2  | V    |

|                                | u                                                      | V <sub>SCREF</sub> = 2.5 V, T <sub>amb</sub> = 25°C | 2.2  | 2.5  | 2.8  |      |

| V <sub>SCREF,en</sub>          | VDS monitoring protection enable voltage               |                                                     |      |      | 2.55 | V    |

| V <sub>SCREF,dis</sub>         | VDS monitoring protection disable voltage              |                                                     | 2.9  |      |      | V    |

| R <sub>SCREF</sub>             | VDS monitoring protection reference pull-down resistor |                                                     |      | 400  |      | kΩ   |

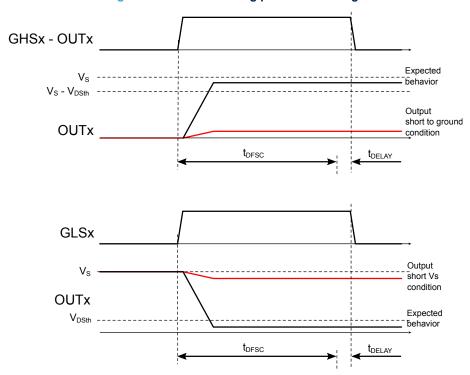

|                                |                                                        | VDS_P_DEG = 00                                      |      | 6    |      |      |

| toree                          | VDS monitoring protection                              | VDS_P_DEG = 01                                      |      | 4    |      | 116  |

| <sup>t</sup> DFSC              | deglitch filter time                                   | VDS_P_DEG = 10                                      |      | 3    |      | μs   |

|                                |                                                        | VDS_P_DEG = 11                                      |      | 2    |      |      |

$<sup>1. \</sup>quad MT = max. \ (|t_{on(GLS)} - t_{off(GLS)}|, \ |t_{on(GHS)} - t_{off(GHS)}|, \ |t_{off(GLS)} - t_{on(GHS)}|, \ |t_{off(GHS)} - t_{on(GHS)}|).$

DS13630 - Rev 1 page 10/48

<sup>2.</sup>  $MT_{CH}$  is the difference between the  $t_{on}$  and  $t_{off}$  of a channel and the same timings of any other channel.

# 4 Pin description

PA15 PA14 PA13 REG3V3/VDD 48 PA12 VBAT 47 PA11 PC13 46 PA10 vss PC14 45 PA9 44 PC15 PA8 PF0 43 GHS1 OUT1 PF1 42 BOOT1 PG10 40 GHS2 PC0 PC1 OUT2 воот2 PC2 GHS3 PC3 OUT3 PA0 воот3 PA1 14 15 34 PA2 NC PA3 16 33 NC PB10 VDDA

Figure 3. STSPIN32G4 pin connection

Table 6. STSPIN32G4 pin list

| N. | Name       | Туре       | Function <sup>(1)</sup>                                           |

|----|------------|------------|-------------------------------------------------------------------|

| 1  | REG3V3/VDD | Power      | 3.3V LDO regulator output and control logic supply voltage        |

| 2  | VBAT       | Power      | MCU backup supply                                                 |

| 3  | PC13       | I/O – FT   | TIM8_CH4N, EVENTOUT, WKUP2,                                       |

| 3  | PC13       | 1/0 - F1   | RTC_TAMP1, RTC_TS, RTC_OUT1                                       |

| 4  | PC14       | I/O – FT   | EVENTOUT, OSC32_IN                                                |

| 5  | PC15       | I/O – FT   | EVENTOUT, OSC32_OUT                                               |

| 6  | PF0        | I – FT fa  | I2C2_SDA, SPI2_NSS/I2S2_WS,                                       |

| 0  | FIO        | -          | EVENTOUT, ADC1_IN10, OSC_IN                                       |

| 7  | PF1        | O-FT a     | SPI2_SCK/I2S2_CK, EVENTOUT                                        |

|    |            | 0 - 1 1_a  | ADC2_IN10, COMP3_INM, OSC_OUT                                     |

| 8  | PG10       | I/O - FT   | MCO, EVENTOUT, NRST                                               |

| 9  | PC0        | I/O – FT_a | LPTIM1_IN1, LPUART1_RX, EVENTOUT, ADC12_IN6, COMP3_INM            |

| 10 | PC1        | I/O – TT_a | LPTIM1_OUT, LPUART1_TX, SAI1_SD_A, EVENTOUT, ADC12_IN7, COMP3_INP |

| 11 | PC2        | I/O – FT_a | LPTIM1_IN2, COMP3_OUT, EVENTOUT, ADC12_IN8                        |

| 12 | PC3        | I/O – FT_a | LPTIM1_ETR, SAI1_D1, SAI1_SD_A, EVENTOUT, ADC12_IN9               |

DS13630 - Rev 1 page 11/48

| N. | Name  | Туре        | Function <sup>(1)</sup>                                                                                                    |

|----|-------|-------------|----------------------------------------------------------------------------------------------------------------------------|

| N. | Name  | туре        |                                                                                                                            |

| 40 | DAG   | 1/O TT      | TIM2_CH1, USART2_CTS, COMP1_OUT, TIM8_BKIN, TIM8_ETR, TIM2_ETR,                                                            |

| 13 | PA0   | I/O – TT_a  | EVENTOUT, ADC12_IN1, COMP1_INM, COMP3_INP, RTC_TAMP2, WKUP1                                                                |

| 14 | PA1   | I/O – TT_a  | RTC_REFIN, TIM2_CH2, USART2_RTS_DE, TIM15_CH1N, EVENTOUT, ADC12_IN2, COMP1_INP, OPAMP1_VINP, OPAMP3_VINP                   |

| 15 | PA2   | I/O – TT_a  | TIM2_CH3, USART2_TX, COMP2_OUT, TIM15_CH1, LPUART1_TX, UCPD1_FRSTX, EVENTOUT, ADC1_IN3, COMP2_INM, OPAMP1_VOUT,            |

|    |       |             | WKUP4/LSCO                                                                                                                 |

| 16 | PA3   | I/O – TT_a  | TIM2_CH4, SAI1_CK1, USART2_RX, TIM15_CH2, LPUART1_RX, SAI1_MCLK_A, EVENTOUT, ADC1_IN4, COMP2_INP, OPAMP1_VINM/ OPAMP1_VINP |

| 17 | PA4   | I/O – TT_a  | TIM3_CH2, SPI1_NSS, SPI3_NSS/I2S3_WS, USART2_CK, SAI1_FS_B, EVENTOUT, ADC2_IN17, DAC1_OUT1, COMP1_INM                      |

| 18 | PA5   | I/O – TT_a  | TIM2_CH1, TIM2_ETR, SPI1_SCK, UCPD1_FRSTX, EVENTOUT, ADC2_IN13, DAC1_OUT2, COMP2_INM, OPAMP2_VINM                          |

| 19 | PA6   | I/O – TT_a  | TIM16_CH1, TIM3_CH1, TIM8_BKIN, SPI1_MISO, TIM1_BKIN, COMP1_OUT, LPUART1_CTS, EVENTOUT, ADC2_IN3, OPAMP2_VOUT              |

| 20 | PA7   | I/O – TT_a  | TIM17_CH1, TIM3_CH2, TIM8_CH1N, SPI1_MOSI, COMP2_OUT, UCPD1_FRSTX, EVENTOUT, ADC2_IN4, COMP2_INP, OPAMP1_VINP, OPAMP2_VINP |

| 21 | PC4   | I/O - FT_fa | I2C2_SCL, USART1_TX, EVENTOUT, ADC2_IN5                                                                                    |

| 22 | PC5   | I/O – TT_a  | TIM15_BKIN, SAI1_D3, USART1_RX, EVENTOUT, ADC2_IN11, OPAMP1_VINM, OPAMP2_VINM, WKUP5                                       |

| 23 | PB0   | I/O – TT_a  | TIM3_CH3, TIM8_CH2N, UCPD1_FRSTX, EVENTOUT, ADC1_IN15, COMP4_INP, OPAMP2_VINP, OPAMP3_VINP                                 |

| 24 | PB1   | I/O – TT_a  | TIM3_CH4, TIM8_CH3N, COMP4_OUT, LPUART1_RTS_DE, EVENTOUT, ADC1_IN12, COMP1_INP, OPAMP3_VOUT                                |

| 25 | PB2   | I/O – TT_a  | RTC_OUT2, LPTIM1_OUT, EVENTOUT, ADC2_IN12, COMP4_INM, OPAMP3_VINM                                                          |

| 26 | VREF+ | Power       | MCU VREF+, VREFBUF_OUT                                                                                                     |

| 27 | VDDA  | Power       | MCU analog supply voltage                                                                                                  |

| 28 | PB10  | I/O – TT_a  | USART3_TX, LPUART1_RX, SAI1_SCK_A, EVENTOUT, OPAMP3_VINM                                                                   |

| 29 | GLS1  | Analog Out  | Phase 1 low-side driver output                                                                                             |

| 30 | GLS2  | Analog Out  | Phase 2 low-side driver output                                                                                             |

| 31 | GLS3  | Analog Out  | Phase 3 low-side driver output                                                                                             |

| 32 | PGND  | Power       | Gate drivers power ground                                                                                                  |

| 33 | NC    |             | Internally not connected                                                                                                   |

| 34 | NC    |             | Internally not connected                                                                                                   |

| 35 | воотз | Power       | Phase 3 bootstrap supply voltage                                                                                           |

| 36 | OUT3  | Power       | Phase 3 high-side (floating) common voltage                                                                                |

| 37 | GHS3  | Analog Out  | Phase 3 high-side driver output                                                                                            |

| 38 | BOOT2 | Power       | Phase 2 bootstrap supply voltage                                                                                           |

| 39 | OUT2  | Power       | Phase 2 high-side (floating) common voltage                                                                                |

| 40 | GHS2  | Analog Out  | Phase 2 high-side driver output                                                                                            |

| 41 | BOOT1 | Power       | Phase 1 bootstrap supply voltage                                                                                           |

| 42         OUT1         Power         Phase 1 high-side (floating) common voltage           43         GHS1         Analog Out         Phase 1 high-side driver output           44         PA8         I/O – FT_f         MCO, I2C2_SDA, I2S2_MCK, USART1_CK, TIM<br>SAI1_SCK_A, EVENTOUT           45         PA9         I/O – FT_fd         I2C2_SCL, I2S3_MCK, USART1_TX, TIM15_BK<br>SAI1_FS_A, EVENTOUT, UCPD1_DBCC1           46         PA10         I/O – FT_da         TIM17_BKIN, USB_CRS_SYNC, I2C2_SMBA, S<br>TIM2_CH4, TIM8_BKIN, SAI1_D1, SAI1_SD_A, I<br>UCPD1_DBCC2           47         PA11         I/O – FT_u         SPI2_MOSI/I2S2_SD, USART1_CTS, COMP1_C<br>TIM4_CH1, EVENTOUT, USB_DM           48         PA12         I/O – FT_u         TIM16_CH1, I2SCKIN, USART1_RTS_DE, COM<br>TIM4_CH2, EVENTOUT, USB_DD           49         PA13 (2)         I/O – FT_f         SWDIO-JTMS, TIM16_CH1N, I2C1_SCL, IR_OU<br>TIM4_CH3, SAI1_SD_B, EVENTOUT           50         PA14(2)         I/O – FT_f         SWCLK-JTCK, LPTIM1_OUT, I2C1_SCL, SPI1_N<br>SAI1_FS_B, EVENTOUT           51         PA15(2)         I/O – FT_f         JTDI, TIM2_CH1, TIM8_CH1, I2C1_SCL, SPI1_N<br>I2S3_WS, USART2_RX, UART4_RTS_DE, TIM2           52         SCREF         Analog In         If the voltage pin is higher than VSCREF, dis three<br>protection is disabled.           53         PD2         I/O – FT         TIM3_ETR, TIM8_BKIN, EVENTOUT                                                       |                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| MCO, I2C2_SDA, I2S2_MCK, USART1_CK, TIM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          |

| 444         FAO         I/O - FT_I         SAI1_SCK_A, EVENTOUT           45         PA9         I/O - FT_fd         I2C2_SCL, I2S3_MCK, USART1_TX, TIM15_BK SAI1_FS_A, EVENTOUT, UCPD1_DBCC1           46         PA10         I/O - FT_da         TIM17_BKIN, USB_CRS_SYNC, I2C2_SMBA, S TIM2_CH4, TIM8_BKIN, SAI1_D1, SAI1_SD_A, IUCPD1_DBCC2           47         PA11         I/O - FT_u         SPI2_MOSI/I2S2_SD, USART1_CTS, COMP1_CTMM4_CH1, EVENTOUT, USB_DM           48         PA12         I/O - FT_u         TIM16_CH1, I2SCKIN, USART1_RTS_DE, COM TIM4_CH2, EVENTOUT, USB_DP           49         PA13 (2)         I/O - FT_f         SWDIO-JTMS, TIM16_CH1N, I2C1_SCL, IR_OUTMM4_CH3, SAI1_SD_B, EVENTOUT           50         PA14(2)         I/O - FT_f         SWCLK-JTCK, LPTIM1_OUT, I2C1_SDA, TIM8_SAI1_FS_B, EVENTOUT           51         PA15(2)         I/O - FT_f         JTDI, TIM2_CH1, TIM8_CH1, I2C1_SCL, SPI1_N I2S3_WS, USART2_RX, UART4_RTS_DE, TIM2_SWS, USART2_RX, UART4_RTS_DE, TIM2_SWS, USART2_RX, UART4_RTS_DE, TIM2_SWS, USART2_RX, UART4_RTS_DE, TIM2_SWS, USART2_RX, UART4_RTS_DE, TIM3_ETR, TIM8_BKIN, EVENTOUT           52         SCREF         Analog In         If the voltage pin is higher than VSCREF, dis thres protection is disabled.           53         PD2         I/O - FT         TIM3_ETR, TIM8_BKIN, EVENTOUT           54         PB3(2)         I/O - FT         JTDO-TRACESWO, TIM2_CH2, TIM4_ETR, USI TIM8_CH1N, SPI1_SCK, SPI3_SCK/I2S3_CK, USAI1_SC |                          |

| PA9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | I4_ETR, SAI1_CK2,        |

| 46         PA10         I/O - FT_da         TIM2_CH4, TIM8_BKIN, SAI1_D1, SAI1_SD_A, IUCPD1_DBCC2           47         PA11         I/O - FT_u         SPI2_MOSI/I2S2_SD, USART1_CTS, COMP1_CTM_NUSB_DM           48         PA12         I/O - FT_u         TIM16_CH1, I2SCKIN, USART1_RTS_DE, COMM_TIM4_CH2, EVENTOUT, USB_DP           49         PA13 (2)         I/O - FT_f         SWDIO-JTMS, TIM16_CH1N, I2C1_SCL, IR_OUMDIM4_CH3, SAI1_SD_B, EVENTOUT           50         PA14(2)         I/O - FT_f         SWCLK-JTCK, LPTIM1_OUT, I2C1_SDA, TIM8_SAI1_FS_B, EVENTOUT           51         PA15(2)         I/O - FT_f         JTDI, TIM2_CH1, TIM8_CH1, I2C1_SCL, SPI1_NI2S3_WS, USART2_RX, UART4_RTS_DE, TIM2           52         SCREF         Analog In         If the voltage pin is higher than VSCREF, dis threst protection is disabled.           53         PD2         I/O - FT         TIM3_ETR, TIM8_BKIN, EVENTOUT           54         PB3(2)         I/O - FT         JTDO-TRACESWO, TIM2_CH2, TIM4_ETR, USI TIM8_CH1, SPI1_SCK, SPI3_SCK/I2S3_CK, USAI1_SCK_B, EVENTOUT           55         DB4(2)         I/O - ET_C         JTRST, TIM16_CH1, TIM3_CH1, TIM8_CH2N, S                                                                                                                                                                                                                                                                                                                       | IN, TIM2_CH3,            |

| 47         PATT         I/O - FT_u         TIMA_CH1, EVENTOUT, USB_DM           48         PA12         I/O - FT_u         TIM16_CH1, I2SCKIN, USART1_RTS_DE, COM TIM4_CH2, EVENTOUT, USB_DP           49         PA13 (2)         I/O - FT_f         SWDIO-JTMS, TIM16_CH1N, I2C1_SCL, IR_OU TIM4_CH3, SAI1_SD_B, EVENTOUT           50         PA14(2)         I/O - FT_f         SWCLK-JTCK, LPTIM1_OUT, I2C1_SDA, TIM8_SAI1_FS_B, EVENTOUT           51         PA15(2)         I/O - FT_f         JTDI, TIM2_CH1, TIM8_CH1, I2C1_SCL, SPI1_N I2S3_WS, USART2_RX, UART4_RTS_DE, TIM2           52         SCREF         Analog In         If the voltage pin is higher than VSCREF,dis three protection is disabled.           53         PD2         I/O - FT         TIM3_ETR, TIM8_BKIN, EVENTOUT           54         PB3(2)         I/O - FT         JTDO-TRACESWO, TIM2_CH2, TIM4_ETR, USI TIM8_CH1N, SPI1_SCK, SPI3_SCK/I2S3_CK, USAI1_SCK_B, EVENTOUT           55         DB4(2)         I/O - FT         JTRST, TIM16_CH1, TIM3_CH1, TIM8_CH2N, S                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _                        |

| TIM4_CH2, EVENTOUT, USB_DP    PA13 (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | OUT, FDCAN1_RX,          |

| TIM4_CH3, SAI1_SD_B, EVENTOUT  TIM4_CH3, SAI1_SD_B, EVENTOUT  SWCLK-JTCK, LPTIM1_OUT, I2C1_SDA, TIM8_SAI1_FS_B, EVENTOUT  I/O - FT_f SAI1_FS_B, EVENTOUT  PA15(2)  I/O - FT_f JTDI, TIM2_CH1, TIM8_CH1, I2C1_SCL, SPI1_N I2S3_WS, USART2_RX, UART4_RTS_DE, TIM2  Set the threshold voltage of the short-circuit protection is disabled.  SCREF Analog In If the voltage pin is higher than VSCREF, dis three protection is disabled.  PD2 I/O - FT TIM3_ETR, TIM8_BKIN, EVENTOUT  JTDO-TRACESWO, TIM2_CH2, TIM4_ETR, USI TIM8_CH1N, SPI1_SCK, SPI3_SCK/I2S3_CK, USAI1_SCK_B, EVENTOUT  JTRST, TIM16_CH1, TIM3_CH1, TIM8_CH2N, S  JTRST, TIM16_CH1, TIM3_CH1, TIM8_CH2N, S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | IP2_OUT, FDCAN1_TX,      |

| SAI1_FS_B, EVENTOUT  PA15(2)  I/O - FT_f  JTDI, TIM2_CH1, TIM8_CH1, I2C1_SCL, SPI1_N I2S3_WS, USART2_RX, UART4_RTS_DE, TIM2  Set the threshold voltage of the short-circuit prote If the voltage pin is higher than VSCREF, dis threshold voltage pin is disabled.  PD2  I/O - FT  TIM3_ETR, TIM8_BKIN, EVENTOUT  JTDO-TRACESWO, TIM2_CH2, TIM4_ETR, USA TIM8_CH1N, SPI1_SCK, SPI3_SCK/I2S3_CK, USAI1_SCK_B, EVENTOUT  TIM5_CH1N, SPI1_SCK_SPI3_SCK/I2S3_CK, USAI1_SCK_B, EVENTOUT  JTRST, TIM16_CH1, TIM3_CH1, TIM8_CH2N, S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | JT, USART3_CTS,          |

| SCREF  Analog In  Set the threshold voltage of the short-circuit protection is disabled.  SOURCE TIME  Analog In  Set the threshold voltage of the short-circuit protection is disabled.  TIME TIME TIME TIME TIME TIME TIME TIME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CH2, USART2_TX,          |

| SCREF Analog In If the voltage pin is higher than VSCREF, dis thres protection is disabled.  53 PD2 I/O – FT TIM3_ETR, TIM8_BKIN, EVENTOUT  54 PB3 <sup>(2)</sup> I/O – FT JTDO-TRACESWO, TIM2_CH2, TIM4_ETR, USI TIM8_CH1N, SPI1_SCK, SPI3_SCK/I2S3_CK, USAI1_SCK_B, EVENTOUT  55 PB4 <sup>(2)</sup> I/O – ET C JTRST, TIM16_CH1, TIM3_CH1, TIM8_CH2N, S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                          |

| protection is disabled.  53 PD2 I/O – FT TIM3_ETR, TIM8_BKIN, EVENTOUT  54 PB3 <sup>(2)</sup> I/O – FT JIM8_CH1N, SPI1_SCK, SPI3_SCK/I2S3_CK, USAI1_SCK_B, EVENTOUT  55 PB4 <sup>(2)</sup> JTRST, TIM16_CH1, TIM3_CH1, TIM8_CH2N, S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ection.                  |

| 54 PB3 <sup>(2)</sup> I/O – FT JTRST, TIM16_CH1, TIM3_CH1, TIM8_CH2N, S  55 PB4 <sup>(2)</sup> JTRST, TIM16_CH1, TIM3_CH1, TIM8_CH2N, S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | shold, the short-circuit |

| 54 PB3 <sup>(2)</sup> I/O – FT TIM8_CH1N, SPI1_SCK, SPI3_SCK/I2S3_CK, U SAI1_SCK_B, EVENTOUT  55 PB4 <sup>(2)</sup> JTRST, TIM16_CH1, TIM3_CH1, TIM8_CH2N, S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                          |

| TIM16_BKIN, TIM3_CH2, TIM8_CH3N, I2C1_SN SPI3_MOSI/I2S3_SD, USART2_CK, TIM17_CH1 SAI1_SD_B, EVENTOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                          |

| TIM16_CH1N, TIM4_CH1, TIM8_CH1, TIM8_ET1<br>COMP4_OUT, TIM8_BKIN2, LPTIM1_ETR, SAI1<br>UCPD1_CC1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                          |

| 58 PB7 I/O – FT_f TIM17_CH1N, TIM4_CH2, I2C1_SDA, TIM8_BKI COMP3_OUT, TIM3_CH4, LPTIM1_IN2, UART4_PVD_IN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <u> </u>                 |

| MCU PB8-BOOT0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                          |

| 59 PB8 <sup>(3)</sup> I/O – FT_f TIM16_CH1, TIM4_CH3, SAI1_CK1, I2C1_SCL, COMP1_OUT, FDCAN1_RX, TIM8_CH2, SAI1_N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                          |

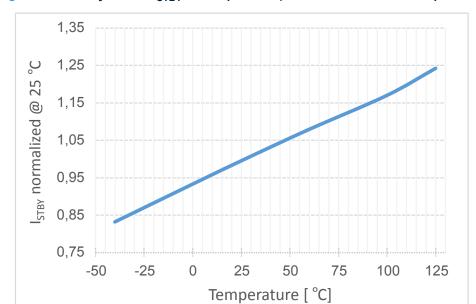

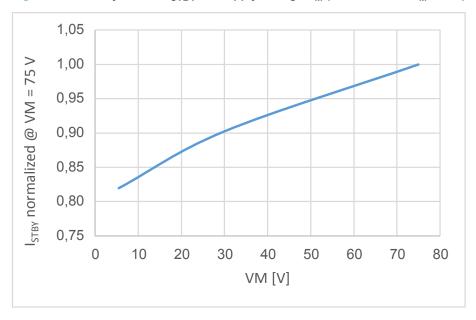

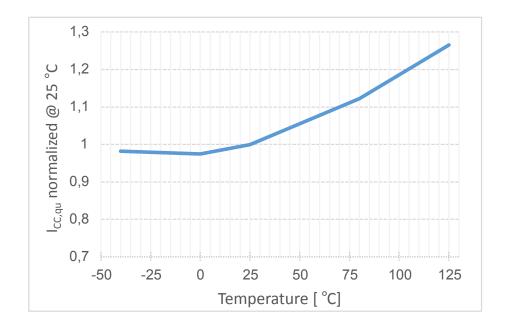

| 60 PB9 I/O – FT_f TIM17_CH1, TIM4_CH4, SAI1_D2, I2C1_SDA, If COMP2_OUT, FDCAN1_TX, TIM8_CH3, SAI1_F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                          |