### **VN7016AJ**

# High-side driver with MultiSense analog feedback for automotive applications

Datasheet - production data

#### **Features**

| Max transient supply voltage      | Vcc               | 40 V      |

|-----------------------------------|-------------------|-----------|

| Operating voltage range           | Vcc               | 4 to 28 V |

| Typ. on-state resistance (per Ch) | Ron               | 16 mΩ     |

| Current limitation (typ)          | ILIMH             | 77 A      |

| Standby current (max)             | I <sub>STBY</sub> | 0.5 μΑ    |

- Automotive qualified

- General

- Single channel smart high-side driver with MultiSense analog feedback

- Very low standby current

- Compatible with 3 V and 5 V CMOS outputs

- MultiSense diagnostic functions

- Multiplexed analog feedback of: load current with high precision proportional current mirror, V<sub>CC</sub> supply voltage and T<sub>CHIP</sub> device temperature

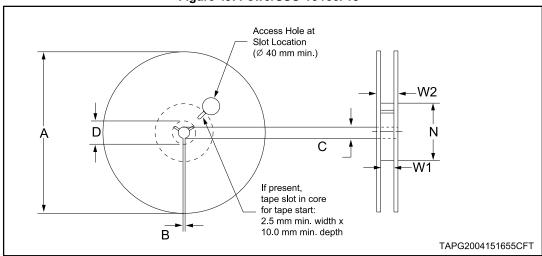

- Overload and short to ground (power limitation) indication

- Thermal shutdown indication

- OFF-state open-load detection

- Output short to V<sub>CC</sub> detection

- Sense enable/disable

- Protections

- Undervoltage shutdown

- Overvoltage clamp

- Load current limitation

- Self limiting of fast thermal transients

- Configurable latch-off on overtemperature or power limitation with dedicated fault reset pin

- Loss of ground and loss of V<sub>CC</sub>

- Reverse battery with external components

- Electrostatic discharge protection

### **Applications**

- All types of Automotive resistive, inductive and capacitive loads

- Specially intended for Automotive Headlamps

### Description

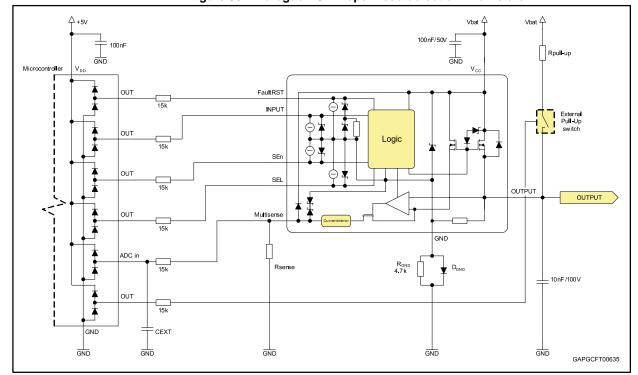

The device is a single channel high-side driver manufactured using ST proprietary VIPower® M0-7 technology and housed in PowerSSO-16 package. The device is designed to drive 12 V automotive grounded loads through a 3 V and 5 V CMOS-compatible interface, providing protection and diagnostics.

The device integrates advanced protective functions such as load current limitation, overload active management by power limitation and overtemperature shutdown with configurable latch-off.

A FaultRST pin unlatches the output in case of fault or disables the latch-off functionality.

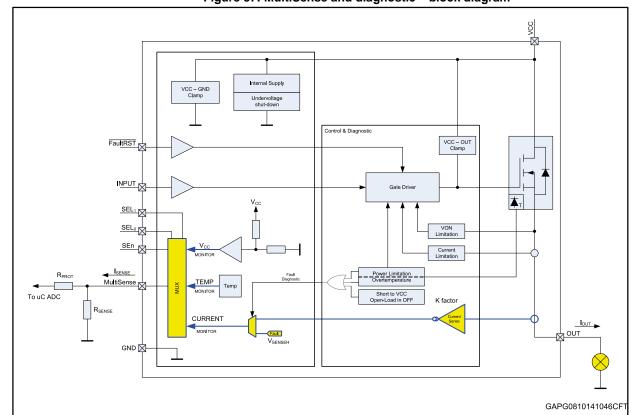

A dedicated multifunction multiplexed analog output pin delivers sophisticated diagnostic functions including high precision proportional load current sense, supply voltage feedback and chip temperature sense, in addition to the detection of overload and short circuit to ground, short to V<sub>CC</sub> and OFF-state open-load.

A sense enable pin allows OFF-state diagnosis to be disabled during the module low-power mode as well as external sense resistor sharing among similar devices.

May 2015 DocID027399 Rev 1 1/45

VN7016AJ

### **Contents**

Contents

| 1 | Block d | iagram ar  | nd pin description                             | 5  |

|---|---------|------------|------------------------------------------------|----|

| 2 |         | _          | cation                                         |    |

|   | 2.1     | Absolute   | maximum ratings                                | 7  |

|   | 2.2     |            | datad                                          |    |

|   | 2.3     | Main elec  | ctrical characteristics                        | 8  |

|   | 2.4     | Waveforr   | ns                                             | 19 |

|   | 2.5     | Electrical | characteristics curves                         | 21 |

| 3 | Protect | ions       |                                                | 25 |

|   | 3.1     | Power lin  | nitation                                       | 25 |

|   | 3.2     | Thermal    | shutdown                                       | 25 |

|   | 3.3     | Current li | mitation                                       | 25 |

|   | 3.4     | Negative   | voltage clamp                                  | 25 |

| 4 | Applica | tion infor | mation                                         | 26 |

|   | 4.1     | GND pro    | tection network against reverse battery        | 26 |

|   |         | 4.1.1      | Diode (DGND) in the ground line                | 27 |

|   | 4.2     | Immunity   | against transient electrical disturbances      | 27 |

|   | 4.3     | MCU I/O    | s protection                                   | 27 |

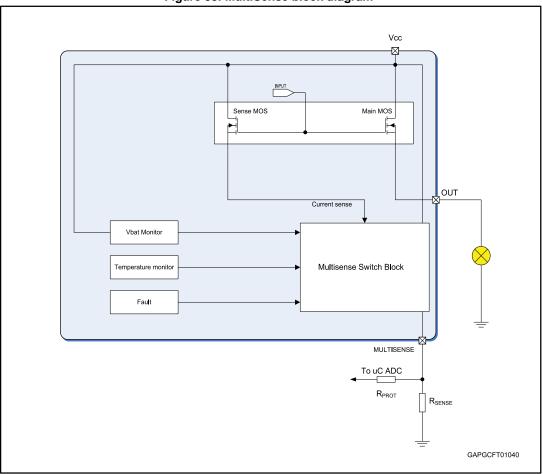

|   | 4.4     | Multisens  | se - analog current sense                      | 28 |

|   |         | 4.4.1      | Principle of Multisense signal generation      | 29 |

|   |         | 4.4.2      | TCASE and VCC monitor                          |    |

| _ |         | 4.4.3      | Short to VCC and OFF-state open-load detection |    |

| 5 |         |            | netization energy (VCC = 16 V)                 |    |

| 6 | Packag  | e and PC   | 3 thermal data                                 | 35 |

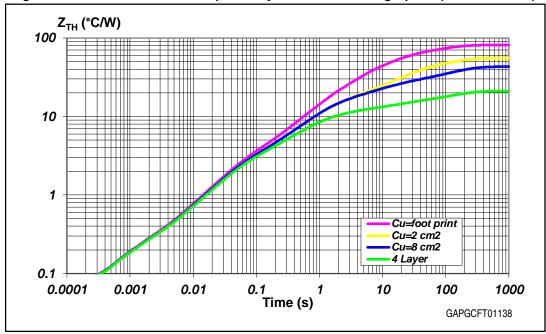

|   | 6.1     | PowerSS    | SO-16 thermal data                             | 35 |

| 7 | Packag  | e informa  | tion                                           | 38 |

|   | 7.1     | PowerSS    | SO-16 package information                      | 38 |

|   | 7.2     | PowerSS    | SO-16 packing information                      | 40 |

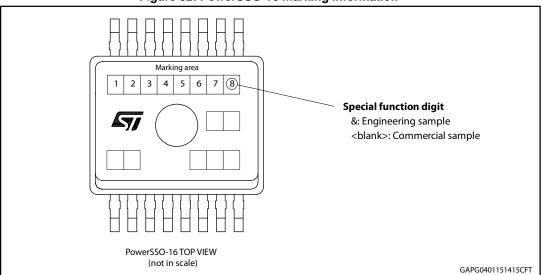

|   | 7.3     | PowerSS    | SO-16 marking information                      | 42 |

| 8 | Order c | odes       |                                                | 43 |

| 9 | Revisio | n history  |                                                | 44 |

|   |         | •          |                                                |    |

VN7016AJ List of tables

# List of tables

| Table 1: Pin functions                                                   | 5  |

|--------------------------------------------------------------------------|----|

| Table 2: Suggested connections for unused and not connected pins         | 6  |

| Table 3: Absolute maximum ratings                                        | 7  |

| Table 4: Thermal data                                                    | 8  |

| Table 5: Power section                                                   |    |

| Table 6: Switching                                                       | 9  |

| Table 7: Logic inputs                                                    | 10 |

| Table 8: Protections                                                     | 11 |

| Table 9: MultiSense                                                      | 11 |

| Table 10: Truth table                                                    | 18 |

| Table 11: MultiSense multiplexer addressing                              | 18 |

| Table 12: ISO 7637-2 - electrical transient conduction along supply line | 27 |

| Table 13: MultiSense pin levels in off-state                             | 31 |

| Table 14: PCB properties                                                 | 35 |

| Table 15: Thermal parameters                                             | 37 |

| Table 16: PowerSSO-16 mechanical data                                    | 38 |

| Table 17: Reel dimensions                                                | 40 |

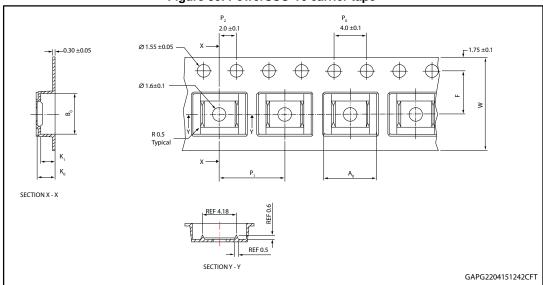

| Table 18: PowerSSO-16 carrier tape dimensions                            | 41 |

| Table 19: Device summary                                                 |    |

| Table 20: Document revision history                                      | 44 |

List of figures VN7016AJ

# List of figures

|                                                                                                          | _  |

|----------------------------------------------------------------------------------------------------------|----|

| Figure 1: Block diagram                                                                                  |    |

| Figure 2: Configuration diagram (top view)                                                               |    |

| Figure 3: Current and voltage conventions                                                                |    |

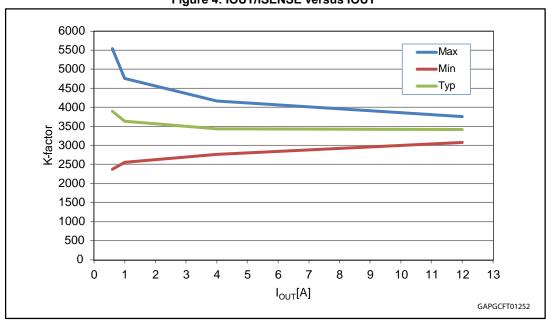

| Figure 4: IOUT/ISENSE versus IOUT                                                                        | 15 |

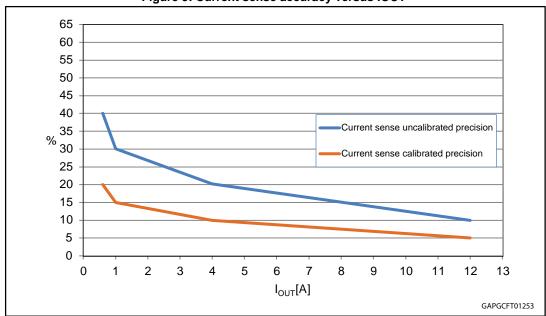

| Figure 5: Current sense accuracy versus IOUT                                                             | 15 |

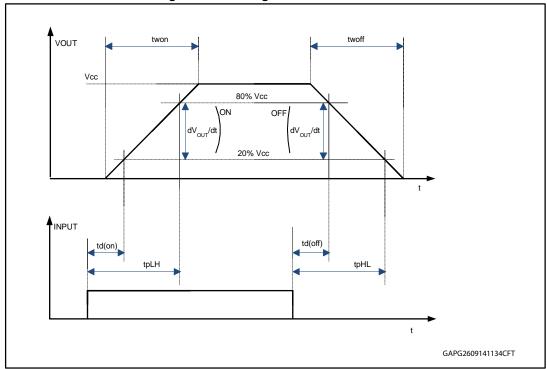

| Figure 6: Switching time and Pulse skew                                                                  | 16 |

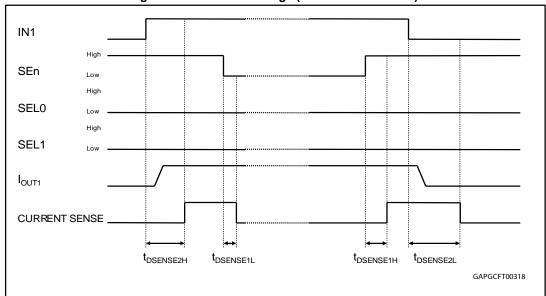

| Figure 7: MultiSense timings (current sense mode)                                                        | 16 |

| Figure 8: Multisense timings (chip temperature and VCC sense mode)                                       |    |

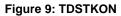

| Figure 9: TDSTKON                                                                                        |    |

| Figure 10: Latch functionality - behavior in hard short circuit condition (TAMB << TTSD)                 |    |

| Figure 11: Latch functionality - behavior in hard short circuit condition                                | 19 |

| Figure 12: Latch functionality - behavior in hard short circuit condition (autorestart mode + latch off) |    |

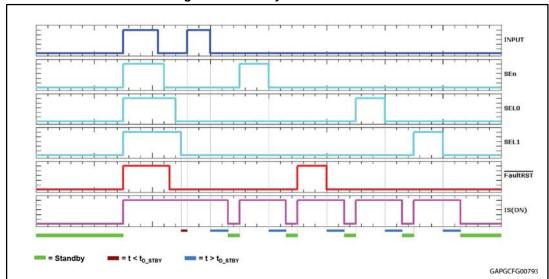

| Figure 13: Standby mode activation                                                                       |    |

| Figure 14: Standby state diagram                                                                         |    |

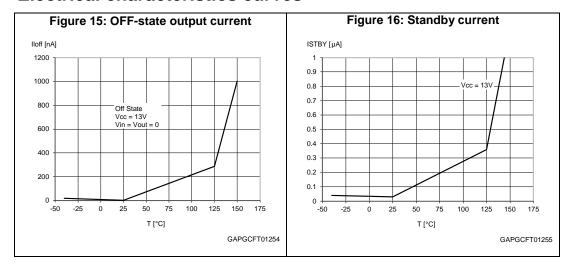

| Figure 15: OFF-state output current                                                                      |    |

| Figure 16: Standby current                                                                               |    |

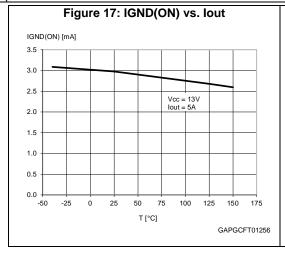

| Figure 17: IGND(ON) vs. lout                                                                             |    |

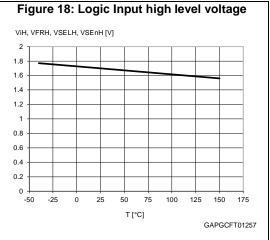

| Figure 18: Logic Input high level voltage                                                                |    |

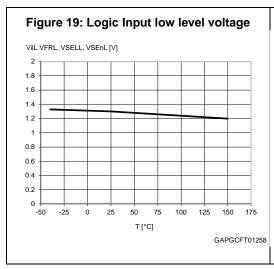

| Figure 19: Logic Input low level voltage                                                                 |    |

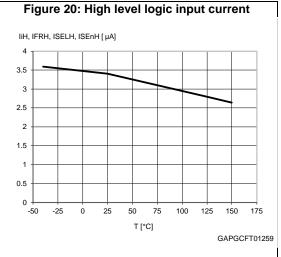

| Figure 20: High level logic input current                                                                |    |

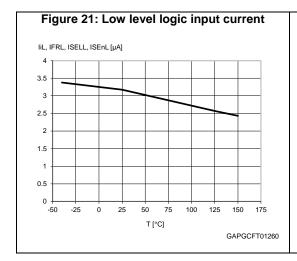

| Figure 21: Low level logic input current                                                                 |    |

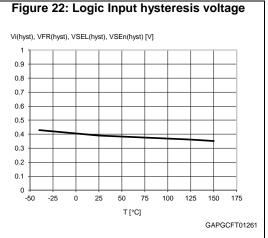

| Figure 22: Logic Input hysteresis voltage                                                                |    |

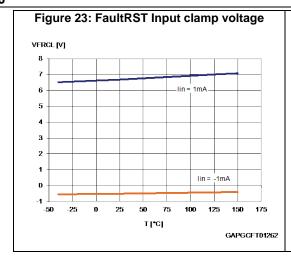

| Figure 23: FaultRST Input clamp voltage                                                                  |    |

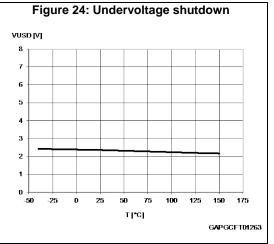

| Figure 24: Undervoltage shutdown                                                                         |    |

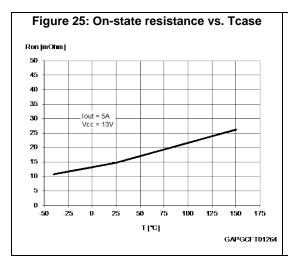

| Figure 25: On-state resistance vs. Tcase                                                                 |    |

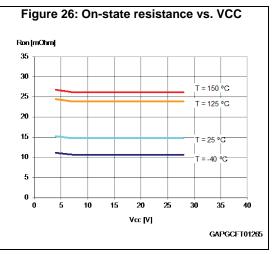

| Figure 26: On-state resistance vs. VCC                                                                   |    |

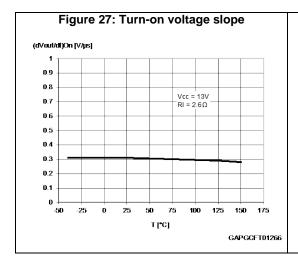

| Figure 27: Turn-on voltage slope                                                                         |    |

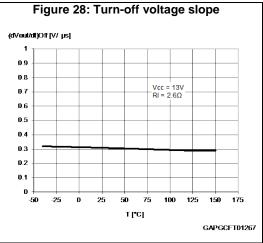

| Figure 28: Turn-off voltage slope                                                                        |    |

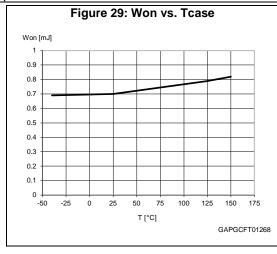

| Figure 29: Won vs. Tcase                                                                                 |    |

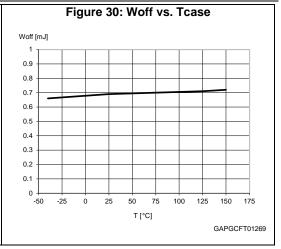

| Figure 30: Woff vs. Tcase                                                                                |    |

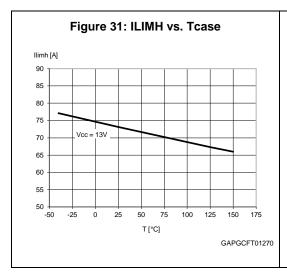

| Figure 31: ILIMH vs. Tcase                                                                               |    |

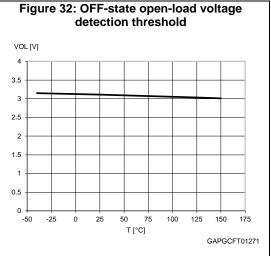

| Figure 32: OFF-state open-load voltage detection threshold                                               | 24 |

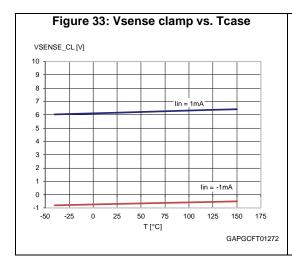

| Figure 33: Vsense clamp vs. Tcase                                                                        |    |

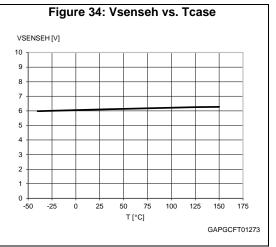

| Figure 34: Vsenseh vs. Tcase                                                                             |    |

| Figure 35: Application diagram                                                                           |    |

| Figure 36: Simplified internal structure                                                                 |    |

| Figure 37: MultiSense and diagnostic – block diagram                                                     |    |

| Figure 38: MultiSense block diagram                                                                      |    |

| Figure 39: Analogue HSD – open-load detection in off-state                                               |    |

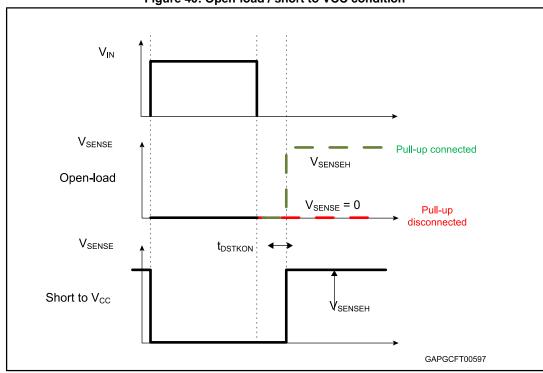

| Figure 40: Open-load / short to VCC condition                                                            |    |

| Figure 41: GND voltage shift                                                                             |    |

| Figure 42: Maximum turn off current versus inductance                                                    |    |

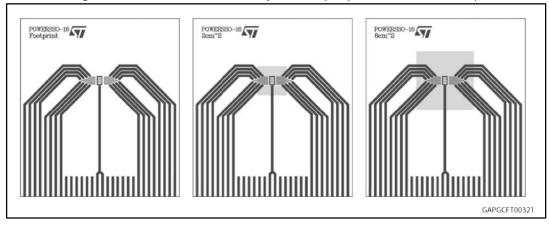

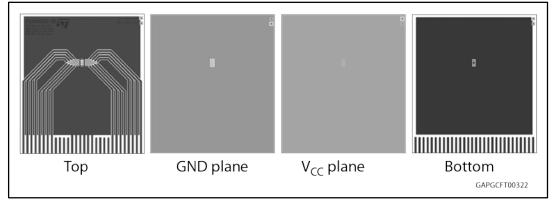

| Figure 43: PowerSSO-16 on two-layers PCB (2s0p to JEDEC JESD 51-5)                                       |    |

| Figure 44: PowerSSO-16 on four-layers PCB (2s2p to JEDEC JESD 51-7)                                      |    |

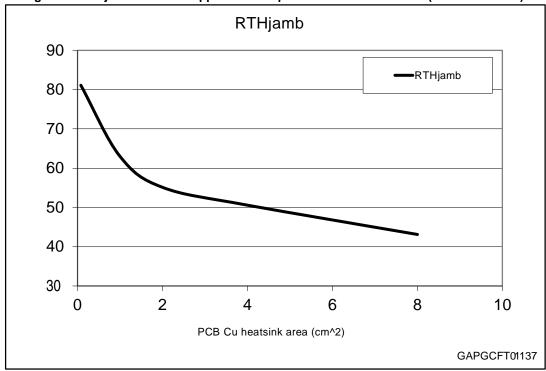

| Figure 45: Rthj-amb vs PCB copper area in open box free air condition (one channel on)                   |    |

| Figure 46: PowerSSO-16 thermal impedance junction ambient single pulse (one channel on)                  |    |

| Figure 47: Thermal fitting model of a double-channel HSD in PowerSSO-16                                  |    |

| Figure 48: PowerSSO-16 package dimensions                                                                |    |

| Figure 49: PowerSSO-16 reel 13"                                                                          |    |

| Figure 50: PowerSSO-16 carrier tape                                                                      |    |

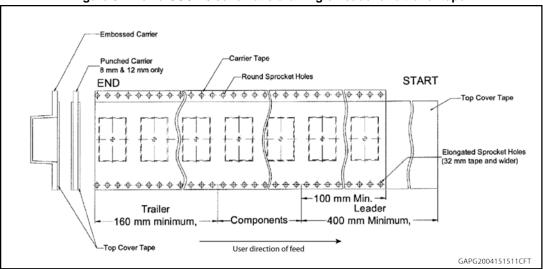

| Figure 51: PowerSSO-16 schematic drawing of leader and trailer tape                                      |    |

| Figure 52: PowerSSO-16 marking information                                                               | 42 |

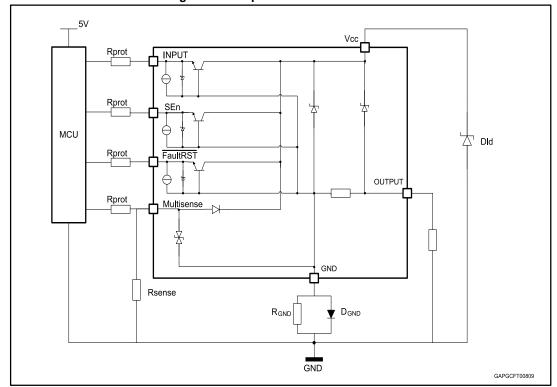

# 1 Block diagram and pin description

FaultrST

Voc

Ganp

Undervoltage

shut-down

INPUT

SEL

SEL

Voc

Gate

FaultrST

Voc

Gate

Gate

Fower Limitation

Overtemperature

Short to Voc

Open-Load in OFF

GAPGCFT00328

Figure 1: Block diagram

**Table 1: Pin functions**

| Name               | Function                                                                                                                                               |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vcc                | Battery connection.                                                                                                                                    |

| OUTPUT             | Power outputs. All the pins must be connected together.                                                                                                |

| GND                | Ground connection. Must be reverse battery protected by an external diode / resistor network.                                                          |

| INPUT              | Voltage controlled input pin with hysteresis, compatible with 3 V and 5 V CMOS outputs. It controls output switch state.                               |

| MultiSense         | Multiplexed analog sense output pin; it delivers a current proportional to the selected diagnostic: load current, supply voltage or chip temperature.  |

| SEn                | Active high compatible with 3 V and 5 V CMOS outputs pin; it enables the MultiSense diagnostic pin.                                                    |

| SEL <sub>0,1</sub> | Active high compatible with 3 V and 5 V CMOS outputs pin; they address the MultiSense multiplexer.                                                     |

| FaultRST           | Active low compatible with 3 V and 5 V CMOS outputs pin; it unlatches the output in case of fault; If kept low, sets the outputs in auto-restart. mode |

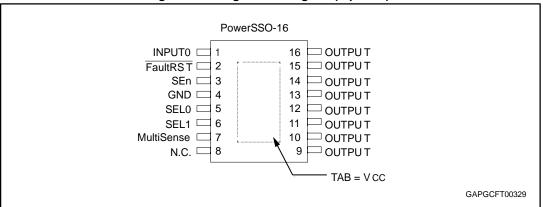

Figure 2: Configuration diagram (top view)

Pins 9, 10, 11 and 12 are internally connected; Pins 13, 14, 15 and 16 are internally connected; All output pins must be connected together on PCB.

Table 2: Suggested connections for unused and not connected pins

| Connection / pin | MultiSense            | N.C.  | Output      | Input                  | SEn, SELx, FaultRST       |

|------------------|-----------------------|-------|-------------|------------------------|---------------------------|

| Floating         | Not allowed           | X (1) | Χ           | X                      | X                         |

| To ground        | Through 1 kΩ resistor | Х     | Not allowed | Through 15 kΩ resistor | Through 15 kΩ<br>resistor |

#### Notes:

(1)X: do not care.

577

### 2 Electrical specification

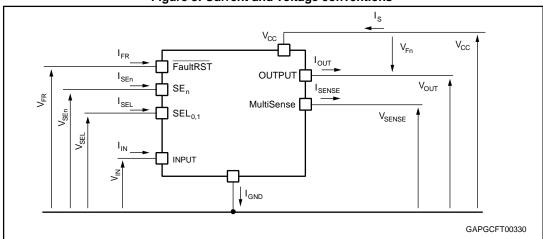

Figure 3: Current and voltage conventions

$V_{Fn} = V_{OUTn} - V_{CC}$  during reverse battery condition.

# 2.1 Absolute maximum ratings

Stressing the device above the rating listed in *Table 3: "Absolute maximum ratings"* may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to the conditions in table below for extended periods may affect device reliability.

**Table 3: Absolute maximum ratings**

| Symbol            | Parameter                                                                                   | Value                 | Unit |

|-------------------|---------------------------------------------------------------------------------------------|-----------------------|------|

| Vcc               | DC supply voltage                                                                           | 38                    | V    |

| -V <sub>CC</sub>  | Reverse DC supply voltage                                                                   | 0.3                   | V    |

| V <sub>CCPK</sub> | Maximum transient supply voltage (ISO 16750-2:2010 Test B clamped to 40 V; RL = 4 $\Omega)$ | 40                    | V    |

| V <sub>CCJS</sub> | Maximum jump start voltage for single pulse short circuit protection                        | 28                    | V    |

| -I <sub>GND</sub> | DC reverse ground pin current                                                               | 200                   | mA   |

| Іоит              | OUTPUT DC output current                                                                    | Internally<br>limited | Α    |

| -Іоит             | Reverse DC output current                                                                   | 22                    |      |

| I <sub>IN</sub>   | INPUT DC input current                                                                      |                       |      |

| I <sub>SEn</sub>  | SEn DC input current                                                                        | -1 to 10              | Λ    |

| ISEL              | SEL <sub>0,1</sub> DC input current                                                         | -1 10 10              | mA   |

| I <sub>FR</sub>   | FaultRST DC input current                                                                   |                       |      |

DocID027399 Rev 1

| Symbol              | Parameter                                                                                                                                                                         | Value                                | Unit      |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------|

| V <sub>FR</sub>     | FaultRST DC input voltage                                                                                                                                                         | 7.5                                  | V         |

|                     | MultiSense pin DC output current (V <sub>GND</sub> = V <sub>CC</sub> and V <sub>SENSE</sub> < 0 V)                                                                                | 10                                   | A         |

| ISENSE              | MultiSense pin DC output current in reverse (V <sub>CC</sub> < 0 V)                                                                                                               | -20                                  | mA        |

| -V <sub>SENSE</sub> | MultiSense pin DC inverse voltage                                                                                                                                                 | 3                                    | ٧         |

| Емах                | Maximum switching energy (single pulse) ( $T_{DEMAG} = 0.4 \text{ ms}$ ; $T_{jstart} = 150 \text{ °C}$ )                                                                          | 88                                   | mJ        |

| V <sub>ESD</sub>    | <ul> <li>Electrostatic discharge (JEDEC 22A-114F)</li> <li>INPUT</li> <li>MultiSense</li> <li>SEn, SEL<sub>0,1</sub>, FaultRST</li> <li>OUTPUT</li> <li>V<sub>CC</sub></li> </ul> | 4000<br>2000<br>4000<br>4000<br>4000 | < < < < < |

| V <sub>ESD</sub>    | Charge device model (CDM-AEC-Q100-011)                                                                                                                                            | 750                                  | V         |

| Tj                  | Junction operating temperature                                                                                                                                                    | -40 to 150                           | °C        |

| T <sub>stg</sub>    | Storage temperature                                                                                                                                                               | -55 to 150                           |           |

### 2.2 Thermal data

Table 4: Thermal data

| Symbol                 | Parameter                                                            | Typ. value | Unit |

|------------------------|----------------------------------------------------------------------|------------|------|

| R <sub>thj-board</sub> | Thermal resistance junction-board (JEDEC JESD 51-5 / 51-8) (1)       | 4.6        |      |

| R <sub>thj-amb</sub>   | Thermal resistance junction-ambient (JEDEC JESD 51-5)(2)             | 55         | °C/W |

| R <sub>thj-amb</sub>   | Thermal resistance junction-ambient (JEDEC JESD 51-7) <sup>(1)</sup> | 21.5       |      |

#### Notes:

### 2.3 Main electrical characteristics

$7 \text{ V} < V_{CC} < 18 \text{ V}$ ;  $-40^{\circ}\text{C} < T_{j} < 150^{\circ}\text{C}$ , unless otherwise specified.

All typical values refer to  $V_{CC}$  = 13 V;  $T_j$  = 25°C, unless otherwise specified.

**Table 5: Power section**

| Symbol           | Parameter                   | Test conditions | Min. | Тур. | Max. | Unit |

|------------------|-----------------------------|-----------------|------|------|------|------|

| Vcc              | Operating supply voltage    |                 | 4    | 13   | 28   | ٧    |

| V <sub>USD</sub> | Undervoltage<br>shutdown    |                 |      |      | 4    | ٧    |

| VusDReset        | Undervoltage shutdown reset |                 |      |      | 5    | ٧    |

| V                | Undervoltage                |                 |      | 0.3  |      | ٧    |

8/45 \_\_\_\_\_ DocID027399 Rev 1

<sup>&</sup>lt;sup>(1)</sup>Device mounted on four-layers 2s2p PCB

$<sup>^{(2)}</sup>$ Device mounted on two-layers 2s0p PCB with 2 cm<sup>2</sup> heatsink copper trace

| Symbol               | Parameter                                                                                                                                | Test conditions                                                                                                                                   | Min. | Тур. | Max. | Unit |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

|                      |                                                                                                                                          | $I_{OUT} = 5 \text{ A}; T_j = 25^{\circ}\text{C}$                                                                                                 |      | 16   |      |      |

| Ron                  | On-state resistance                                                                                                                      | $I_{OUT} = 5 \text{ A}; T_j = 150^{\circ}\text{C}$                                                                                                |      |      | 32   | mΩ   |

|                      |                                                                                                                                          | $I_{OUT} = 5 \text{ A}; V_{CC} = 4 \text{ V}; T_j = 25^{\circ}\text{C}$                                                                           |      |      | 24   |      |

|                      | Clamp voltage                                                                                                                            | $I_S = 20 \text{ mA}; 25^{\circ}\text{C} < T_j < 150^{\circ}\text{C}$                                                                             | 41   | 46   | 52   | V    |

| V <sub>clamp</sub>   | Clamp voltage                                                                                                                            | $I_S = 20 \text{ mA}; T_j = -40^{\circ}\text{C}$                                                                                                  | 38   |      |      | V    |

|                      | $\begin{split} V_{CC} &= 13 \ V; \ V_{IN} = V_{OUT} = V_{FR} = V_{SEn} = 0 \ V; \\ V_{SEL0,1} &= 0 \ V; \ T_j = 25^{\circ}C \end{split}$ |                                                                                                                                                   |      | 0.5  |      |      |

| Іѕтву                | Supply current in standby at Vcc = 13 V                                                                                                  | $\begin{split} &V_{CC} = 13 \ V; \ V_{IN} = V_{OUT} = V_{FR} = V_{SEn} = 0 \ V; \\ &V_{SEL0,1} = 0 \ V; \ T_j = 85^{\circ}C \ ^{(2)} \end{split}$ |      |      | 0.5  | μΑ   |

|                      |                                                                                                                                          | $\begin{split} &V_{CC} = 13 \ V; \ V_{IN} = V_{OUT} = V_{FR} = V_{SEn} = 0 \ V; \\ &V_{SEL0,1} = 0 \ V; \ T_j = 125 ^{\circ}C \end{split}$        |      |      | 3    |      |

| t <sub>D_STBY</sub>  | Standby mode blanking time                                                                                                               | $V_{CC} = 13 \text{ V}; V_{SEN} = 5 \text{ V}$<br>to 0 V; $V_{IN} = V_{OUT} = V_{FR} = V_{SEL0,1} = 0 \text{ V}$                                  | 60   | 300  | 550  | μs   |

| I <sub>S(ON)</sub>   | Supply current                                                                                                                           | $V_{CC} = 13 \text{ V}; V_{SEn} = V_{FR} = V_{SEL0,1} = 0 \text{ V};$<br>$V_{IN} = 5 \text{ V}; I_{OUT} = 0 \text{ A}$                            |      | 3    | 5    | mA   |

| I <sub>GND(ON)</sub> | Control stage current consumption in ON-state. All channels active.                                                                      | V <sub>CC</sub> = 13 V; V <sub>SEn</sub> = 5 V; V <sub>FR</sub> = V <sub>SEL0,1</sub> = 0 V;<br>V <sub>IN</sub> = 5 V; I <sub>OUT</sub> = 3 A     |      |      | 6    | mA   |

| l. /- m              | Off-state output current                                                                                                                 | $V_{IN} = V_{OUT} = 0 \ V; \ V_{CC} = 13 \ V; \ T_j = 25^{\circ}C$                                                                                | 0    | 0.01 | 0.5  |      |

| I <sub>L(off)</sub>  | at V <sub>CC</sub> = 13 V                                                                                                                | $V_{IN} = V_{OUT} = 0 \text{ V}; V_{CC} = 13 \text{ V}; T_j = 125^{\circ}\text{C}$                                                                | 0    |      | 3    | μA   |

| V <sub>F</sub>       | Output - V <sub>CC</sub> diode voltage                                                                                                   | $I_{OUT} = -5 \text{ A}; T_j = 150^{\circ}\text{C}$                                                                                               |      |      | 0.7  | V    |

#### Notes:

Table 6: Switching

| $V_{CC}$ = 13 V; -40°C < T <sub>j</sub> < 150°C, unless otherwise specified |                                                                |                        |      |      |         |       |  |  |

|-----------------------------------------------------------------------------|----------------------------------------------------------------|------------------------|------|------|---------|-------|--|--|

| Symbol                                                                      | Parameter                                                      | Test conditions        | Min. | Тур. | Max.    | Unit  |  |  |

| t <sub>d(on)</sub> (1)                                                      | Turn-on delay time at T <sub>j</sub> = 25 °C                   | R <sub>L</sub> = 2.6 Ω | 10   | 30   | 120     | μs    |  |  |

| t <sub>d(off)</sub> (1)                                                     | Turn-off delay time at $T_j = 25$ °C                           | KL = 2.0 12            | 10   | 50   | 100     |       |  |  |

| $(dV_{OUT}/dt)_{on}$                                                        | Turn-on voltage slope at $T_j = 25$ °C                         | R <sub>L</sub> = 2.6 Ω | 0.1  | 0.31 | 0.7     | \//uo |  |  |

| (dVout/dt)off <sup>(1)</sup>                                                | Turn-off voltage slope at $T_j = 25$ °C                        | KL = 2.0 12            | 0.1  | 0.31 | 0.7     | V/µs  |  |  |

| Won                                                                         | Switching energy losses at turn-on (twon)                      | $R_L = 2.6 \Omega$     | _    | 0.7  | 0.94(2) | mJ    |  |  |

| Woff                                                                        | Switching energy losses at turn-off (twoff)                    | $R_L = 2.6 \Omega$     |      | 0.7  | 0.91(2) | mJ    |  |  |

| tskew <sup>(1)</sup>                                                        | Differential Pulse skew (t <sub>PHL</sub> - t <sub>PLH</sub> ) | $R_L = 2.6 \Omega$     | -40  | 10   | 60      | μs    |  |  |

#### Notes:

<sup>&</sup>lt;sup>(1)</sup>PowerMOS leakage included.

$<sup>\</sup>ensuremath{^{(2)}}\mbox{Parameter specified by design; not subject to production test.}$

<sup>(1)</sup>See Figure 6: "Switching time and Pulse skew".

$<sup>^{(2)}</sup>$ Parameter guaranteed by design and characterization; not subject to production test.

Table 7: Logic inputs

| Symbol                 | Parameter                                 | Test conditions          | Min. | Тур. | Max. | Unit |  |

|------------------------|-------------------------------------------|--------------------------|------|------|------|------|--|

| NPUT cha               | racteristics                              |                          |      |      |      |      |  |

| VIL                    | Input low level voltage                   |                          |      |      | 0.9  | V    |  |

| I <sub>IL</sub>        | Low level input current                   | V <sub>IN</sub> = 0.9 V  | 1    |      |      | μΑ   |  |

| VIH                    | Input high level voltage                  |                          | 2.1  |      |      | V    |  |

| Iн                     | High level input current                  | V <sub>IN</sub> = 2.1 V  |      |      | 10   | μΑ   |  |

| V <sub>I(hyst)</sub>   | Input hysteresis voltage                  |                          | 0.2  |      |      | V    |  |

| \/                     | Innut alama valtaga                       | I <sub>IN</sub> = 1 mA   | 5.3  |      | 7.2  | V    |  |

| V <sub>ICL</sub>       | Input clamp voltage                       | I <sub>IN</sub> = -1 mA  |      | -0.7 |      | V    |  |

| FaultRST               | characteristics                           |                          |      |      |      |      |  |

| V <sub>FRL</sub>       | Input low level voltage                   |                          |      |      | 0.9  | V    |  |

| I <sub>FRL</sub>       | Low level input current                   | V <sub>IN</sub> = 0.9 V  | 1    |      |      | μΑ   |  |

| V <sub>FRH</sub>       | Input high level voltage                  |                          | 2.1  |      |      | V    |  |

| I <sub>FRH</sub>       | High level input current                  | V <sub>IN</sub> = 2.1 V  |      |      | 10   | μA   |  |

| V <sub>FR(hyst)</sub>  | Input hysteresis voltage                  |                          | 0.2  |      |      | V    |  |

| Vercl                  | Innut alama valtaga                       | I <sub>IN</sub> = 1 mA   | 5.3  |      | 7.5  | V    |  |

| VFRCL                  | Input clamp voltage                       | I <sub>IN</sub> = -1 mA  |      | -0.7 |      | V    |  |

| SEL <sub>0,1</sub> cha | racteristics (7 V < Vcc < 18 V)           | )                        |      |      |      |      |  |

| Vsell                  | Input low level voltage                   |                          |      |      | 0.9  | V    |  |

| Isell                  | Low level input current                   | V <sub>IN</sub> = 0.9 V  | 1    |      |      | μΑ   |  |

| $V_{SELH}$             | Input high level voltage                  |                          | 2.1  |      |      | V    |  |

| I <sub>SELH</sub>      | High level input current                  | V <sub>IN</sub> = 2.1 V  |      |      | 10   | μΑ   |  |

| V <sub>SEL(hyst)</sub> | Input hysteresis voltage                  |                          | 0.2  |      |      | V    |  |

| Vselcl                 | Input clamp voltage                       | I <sub>IN</sub> = 1 mA   | 5.3  |      | 7.2  | V    |  |

| V SELCL                | Imput clamp voltage                       | I <sub>IN</sub> = -1 mA  |      | -0.7 |      | V    |  |

| SEn chara              | cteristics (7 V < V <sub>CC</sub> < 18 V) |                          |      |      |      |      |  |

| $V_{SEnL}$             | Input low level voltage                   |                          |      |      | 0.9  | V    |  |

| I <sub>SEnL</sub>      | Low level input current                   | $V_{IN} = 0.9 \ V$       | 1    |      |      | μΑ   |  |

| $V_{SEnH}$             | Input high level voltage                  |                          | 2.1  |      |      | V    |  |

| I <sub>SEnH</sub>      | High level input current                  | V <sub>IN</sub> = 2.1 V  |      |      | 10   | μΑ   |  |

| V <sub>SEn(hyst)</sub> | Input hysteresis voltage                  |                          | 0.2  |      |      | V    |  |

| Vos. 5:                | Input clamp voltage                       | I <sub>IN</sub> = 1 mA   | 5.3  |      | 7.2  | V    |  |

| VSEnCL                 | Imput clamp voltage                       | $I_{IN} = -1 \text{ mA}$ |      | -0.7 |      | 7 V  |  |

10/45 DocID027399 Rev 1

**Table 8: Protections**

| 7 V < Vcc                                                      | $7 \text{ V} < \text{V}_{CC} < 18 \text{ V}; -40^{\circ}\text{C} < \text{T}_{j} < 150^{\circ}\text{C}$ |                                                                                                                         |                     |                     |          |      |  |  |  |  |

|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------|----------|------|--|--|--|--|

| Symbol                                                         | Parameter                                                                                              | Test conditions                                                                                                         | Min.                | Тур.                | Max.     | Unit |  |  |  |  |

| I                                                              | DC short circuit current                                                                               | Vcc = 13 V                                                                                                              | 55                  | 77                  | 110      |      |  |  |  |  |

| I <sub>LIMH</sub>                                              | DC short circuit current                                                                               | 4 V < Vcc < 18 V <sup>(1)</sup>                                                                                         |                     |                     | 110      | Α    |  |  |  |  |

| I <sub>LIML</sub> Short circuit current during thermal cycling |                                                                                                        | $V_{CC} = 13 \text{ V};$<br>$T_R < T_j < T_{TSD}$                                                                       |                     | 32                  |          |      |  |  |  |  |

| T <sub>TSD</sub>                                               | Shutdown temperature                                                                                   |                                                                                                                         | 150                 | 175                 | 200      |      |  |  |  |  |

| T <sub>R</sub>                                                 | Reset temperature <sup>(1)</sup>                                                                       |                                                                                                                         | T <sub>RS</sub> + 1 | T <sub>RS</sub> + 7 |          |      |  |  |  |  |

| T <sub>RS</sub>                                                | Thermal reset of fault diagnostic indication                                                           | V <sub>FR</sub> = 0 V; V <sub>SEn</sub> = 5 V                                                                           | 135                 |                     |          | °C   |  |  |  |  |

| T <sub>HYST</sub>                                              | Thermal hysteresis (T <sub>TSD</sub> - T <sub>R</sub> ) <sup>(1)</sup>                                 |                                                                                                                         |                     | 7                   |          |      |  |  |  |  |

| $\Delta T_{J\_SD}$                                             | Dynamic temperature                                                                                    | $T_j = -40$ °C; $V_{CC} = 13 \text{ V}$                                                                                 |                     | 60                  |          | K    |  |  |  |  |

| tlatch_rst                                                     | Fault reset time for output unlatch <sup>(1)</sup>                                                     | VFR = 5 V to 0 V; V <sub>SEn</sub> = 5 V;<br>V <sub>IN</sub> = 5 V; V <sub>SEL0</sub> = 0 V;<br>V <sub>SEL1</sub> = 0 V | 3                   | 10                  | 20       | μs   |  |  |  |  |

| V <sub>DEMAG</sub>                                             | Turn-off output voltage                                                                                | $I_{OUT} = 2 \text{ A}; L = 6 \text{ mH};$<br>$T_j = -40^{\circ}\text{C}$                                               | Vcc - 38            |                     |          | ٧    |  |  |  |  |

| V DEMAG                                                        | clamp                                                                                                  | louт = 2 A; L = 6 mH;<br>T <sub>j</sub> = 25°С to 150°С                                                                 | Vcc - 41            | Vcc - 46            | Vcc - 52 | V    |  |  |  |  |

| Von                                                            | Output voltage droplimitation                                                                          | Іоит = 0.6 А                                                                                                            |                     | 20                  |          | mV   |  |  |  |  |

#### Notes:

Table 9: MultiSense

| 7 V < Vcc < 18                                    | 7 V < V <sub>CC</sub> < 18 V; -40°C < T <sub>j</sub> < 150°C |                                                                                 |      |      |      |      |  |  |  |  |

|---------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------|------|------|------|------|--|--|--|--|

| Symbol                                            | Parameter                                                    | Test conditions                                                                 | Min. | Тур. | Max. | Unit |  |  |  |  |

| V <sub>SENSE_CL</sub>                             | MultiSense clamp voltage                                     | Vsen = 0 V; Isense = 1 mA                                                       | -17  |      | -12  | V    |  |  |  |  |

|                                                   |                                                              | V <sub>SEn</sub> = 0 V; I <sub>SENSE</sub> = -1 mA                              |      | 7    |      | V    |  |  |  |  |

| CurrentSense                                      | e characteristics                                            |                                                                                 |      |      |      |      |  |  |  |  |

| K <sub>0</sub>                                    | lout/Isense                                                  | I <sub>OUT</sub> = 0.6 A; V <sub>SENSE</sub> = 0.5 V;<br>V <sub>SEn</sub> = 5 V | 2370 | 3900 | 5540 |      |  |  |  |  |

| dK <sub>0</sub> /K <sub>0</sub> <sup>(1)(2)</sup> | Current sense ratio drift                                    | I <sub>OUT</sub> = 0.6 A; V <sub>SENSE</sub> = 0.5 V;<br>V <sub>SEn</sub> = 5 V | -20  |      | 20   | %    |  |  |  |  |

| K <sub>1</sub>                                    | lout/Isense                                                  | I <sub>OUT</sub> = 1 A; V <sub>SENSE</sub> = 4 V;<br>V <sub>SEn</sub> = 5 V     | 2560 | 3640 | 4760 |      |  |  |  |  |

| dK <sub>1</sub> /K <sub>1</sub> <sup>(1)(2)</sup> | Current sense ratio drift                                    | I <sub>OUT</sub> = 1 A; V <sub>SENSE</sub> = 4 V;<br>V <sub>SEn</sub> = 5 V     | -15  |      | 15   | %    |  |  |  |  |

| K <sub>2</sub>                                    | lout/Isense                                                  | IOUT = 4 A; VSENSE = 4 V;<br>VSEn = 5 V                                         | 2770 | 3440 | 4170 |      |  |  |  |  |

DocID027399 Rev 1

<sup>&</sup>lt;sup>(1)</sup>Parameter guaranteed by design and characterization; not subject to production test.

| 7 V < Vcc < 18                                    | 8 V; -40°C < T <sub>j</sub> < 150°C                                                                   |                                                                                                                                                                                                                   |      |      |      |          |

|---------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|----------|

| Symbol                                            | Parameter                                                                                             | Test conditions                                                                                                                                                                                                   | Min. | Тур. | Max. | Unit     |

| dK <sub>2</sub> /K <sub>2</sub> <sup>(1)(2)</sup> | Current sense ratio drift                                                                             | IOUT = 4 A; VSENSE = 4 V;<br>VSEn = 5 V                                                                                                                                                                           | -10  |      | 10   | %        |

| <b>K</b> <sub>3</sub>                             | Iout/Isense                                                                                           | I <sub>OUT</sub> = 12 A; V <sub>SENSE</sub> = 4 V;<br>V <sub>SEn</sub> = 5 V                                                                                                                                      | 3080 | 3420 | 3760 |          |

| dK <sub>3</sub> /K <sub>3</sub> <sup>(1)(2)</sup> | Current sense ratio drift                                                                             | IOUT = 12 A; VSENSE = 4 V;<br>VSEn = 5 V                                                                                                                                                                          | -5   |      | 5    | %        |

|                                                   |                                                                                                       | MultiSense disabled: V <sub>SEn</sub> = 0 V                                                                                                                                                                       | 0    |      | 0.5  |          |

|                                                   |                                                                                                       | MultiSense disabled:<br>-1 V < V <sub>SENSE</sub> < 5 V <sup>(1)</sup>                                                                                                                                            | -0.5 |      | 0.5  |          |

| Isenseo                                           | MultiSense leakage current                                                                            | MultiSense enabled: $V_{SEn} = 5 \text{ V}$ ; Channel ON; $I_{OUT} = 0 \text{ A}$ ; Diagnostic selected; $V_{IN} = 5 \text{ V}$ ; $V_{SEL0} = 0 \text{ V}$ ; $V_{SEL1} = 0 \text{ V}$ ; $I_{OUT} = 0 \text{ A}$   | 0    |      | 2    | μΑ       |

|                                                   |                                                                                                       | MultiSense enabled: $V_{SEn} = 5 \text{ V}$ ;<br>Channel OFF; Diagnostic<br>selected: $V_{IN} = 0 \text{ V}$ ; $V_{SEL0} = 0 \text{ V}$ ;<br>$V_{SEL1} = 0 \text{ V}$                                             | 0    |      | 2    |          |

| Vout_msd <sup>(1)</sup>                           | Output Voltage for<br>MultiSense shutdown                                                             | $\begin{aligned} &V_{IN} = 5 \; V; \; V_{SEn} = 5 \; V; \\ &V_{SEL0} = 0 \; V; \; V_{SEL1} = 0 \; V; \\ &R_{SENSE} = 2.7 \; k\Omega; \; I_{OUT} = 5 \; A \end{aligned}$                                           |      | 5    |      | ٧        |

| Vsense_sat                                        | Multisense saturation voltage                                                                         | $\begin{split} &V_{CC} = 7 \; V; \; R_{SENSE} = 2.7 \; k\Omega; \\ &V_{SEn} = 5 \; V; \; V_{IN} = 5 \; V; \\ &V_{SEL0} = 0 \; V; \; V_{SEL1} = 0 \; V; \\ &I_{OUT} = 12 \; A; \; T_j = 150 ^{\circ}C \end{split}$ | 5    |      |      | <b>V</b> |

| ISENSE_SAT <sup>(1)</sup>                         | CS saturation current                                                                                 | $\label{eq:VCC} \begin{aligned} &V_{CC} = 7 \; V; \; V_{SENSE} = 4 \; V; \\ &V_{IN} = 5 \; V; \; V_{SEn} = 5 \; V; \\ &V_{SEL0} = 0 \; V; \; V_{SEL1} = 0 \; V; \\ &T_{j} = 150 ^{\circ} C \end{aligned}$         | 4    |      |      | mA       |

| lout_sat <sup>(1)</sup>                           | Output saturation current                                                                             | V <sub>CC</sub> = 7 V; V <sub>SENSE</sub> = 4 V;<br>V <sub>IN</sub> = 5 V; V <sub>SEn</sub> = 5 V;<br>V <sub>SEL0</sub> = 0 V; V <sub>SEL1</sub> = 0 V;<br>T <sub>j</sub> = 150°C                                 | 15   |      |      | Α        |

| OFF-state dia                                     | agnostic                                                                                              |                                                                                                                                                                                                                   |      |      |      |          |

| V <sub>OL</sub>                                   | OFF-state open-load voltage detection threshold                                                       | V <sub>IN</sub> = 0 V; V <sub>SEn</sub> = 5 V;<br>V <sub>SEL0</sub> = 0 V; V <sub>SEL1</sub> = 0 V                                                                                                                | 2    | 3    | 4    | V        |

| I <sub>L(off2)</sub>                              | OFF-state output sink current                                                                         | $V_{IN} = 0 \text{ V}; V_{OUT} = V_{OL}; T_j = -40^{\circ}\text{C}$ to 125°C                                                                                                                                      | -100 |      | -15  | μA       |

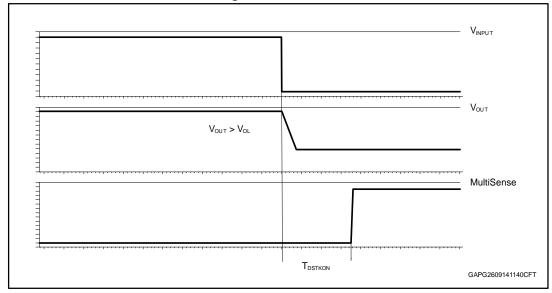

| tostkon                                           | OFF-state diagnostic delay time from falling edge of INPUT (see Figure 9: "TDSTKON")                  | $V_{IN} = 5 \text{ V to } 0 \text{ V; } V_{SEn} = 5 \text{ V;}$<br>$V_{SEL0} = 0 \text{ V; } V_{SEL1} = 0 \text{ V;}$<br>$I_{OUT} = 0 \text{ A; } V_{OUT} = 4 \text{ V}$                                          | 100  | 350  | 700  | μs       |

| t <sub>D_</sub> OL_V                              | Settling time for valid<br>OFF-state open-load<br>diagnostic indication<br>from rising edge of<br>SEn | V <sub>IN</sub> = 0 V; V <sub>FR</sub> = 0 V; V <sub>SEL0</sub> = 0 V;<br>V <sub>SEL1</sub> = 0 V; V <sub>OUT</sub> = 4 V;<br>V <sub>SEn</sub> = 0 V to 5 V                                                       |      |      | 60   | μs       |

12/45 DocID027399 Rev 1

| 7 V < Vcc < 18                          | 8 V; $-40^{\circ}$ C < T <sub>j</sub> < $150^{\circ}$ C                                          |                                                                                                                                                                                                                                   |                      |          |                     |          |

|-----------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------|---------------------|----------|

| Symbol                                  | Parameter                                                                                        | Test conditions                                                                                                                                                                                                                   | Min.                 | Тур.     | Max.                | Unit     |

| t <sub>D_VOL</sub>                      | OFF-state diagnostic delay time from rising edge of V <sub>OUT</sub>                             | $V_{IN} = 0 \text{ V; } V_{SEn} = 5 \text{ V; } V_{SEL0} = 0 \text{ V; } V_{SEL1} = 0 \text{ V; } V_{OUT} = 0 \text{ V to 4 V}$                                                                                                   |                      | 5        | 30                  | μs       |

| Chip tempera                            | ature analog feedback                                                                            |                                                                                                                                                                                                                                   |                      |          |                     |          |

|                                         |                                                                                                  | $\begin{split} &V_{\text{SEn}} = 5 \text{ V; } V_{\text{SEL0}} = 0 \text{ V;} \\ &V_{\text{SEL1}} = 5 \text{ V; } V_{\text{IN}} = 0 \text{ V;} \\ &R_{\text{SENSE}} = 1 \text{ k}\Omega; T_{j} = -40^{\circ}\text{C} \end{split}$ | 2.325                | 2.41     | 2.495               | ٧        |

|                                         | MultiSense output<br>voltage proportional to<br>chip temperature                                 | $\begin{split} &V_{\text{SEn}} = 5 \text{ V; } V_{\text{SEL0}} = 0 \text{ V;} \\ &V_{\text{SEL1}} = 5 \text{ V; } V_{\text{IN}} = 0 \text{ V;} \\ &R_{\text{SENSE}} = 1 \text{ k}\Omega; T_{j} = 25^{\circ}\text{C} \end{split}$  | 1.985                | 2.07     | 2.155               | >        |

|                                         |                                                                                                  | $\begin{split} &V_{\text{SEn}} = 5 \text{ V; } V_{\text{SEL0}} = 0 \text{ V;} \\ &V_{\text{SEL1}} = 5 \text{ V; } V_{\text{IN}} = 0 \text{ V;} \\ &R_{\text{SENSE}} = 1 \text{ k}\Omega; T_j = 125^{\circ}\text{C} \end{split}$   | 1.435                | 1.52     | 1.605               | >        |

| dV <sub>SENSE_TC</sub> /dT              | Temperature coefficient                                                                          | $T_j = -40^{\circ}C \text{ to } 150^{\circ}C$                                                                                                                                                                                     |                      | -5.5     |                     | mV/<br>K |

| Transfer funct                          | ion                                                                                              | $V_{SENSE\_TC}(T) = V_{SENSE\_TC}(T_0) + d$                                                                                                                                                                                       | V <sub>SENSE_T</sub> | c / dT * | (T - T <sub>0</sub> | )        |

| Vcc supply vo                           | oltage analog feedback                                                                           |                                                                                                                                                                                                                                   |                      |          |                     |          |

| Vsense_vcc                              | MultiSense output voltage proportional to Vcc supply voltage                                     | $V_{CC} = 13 \text{ V; } V_{SEn} = 5 \text{ V; } V_{SEL0} = 5 \text{ V; } V_{SEL1} = 5 \text{ V; } V_{IN} = 0 \text{ V; } R_{SENSE} = 1 \text{ k}\Omega$                                                                          | 3.16                 | 3.23     | 3.3                 | V        |

| Transfer funct                          | ion <sup>(3)</sup>                                                                               | Vsense_vcc = Vcc / 4                                                                                                                                                                                                              |                      |          |                     |          |

| Fault diagnos                           | stic feedback (see <i>Table</i>                                                                  | e 10: "Truth table")                                                                                                                                                                                                              |                      |          |                     |          |

| Vsenseh                                 | MultiSense output voltage in fault condition                                                     | $\begin{aligned} &V_{CC} = 13 \ V; \ V_{IN} = 0 \ V; \\ &V_{SEn} = 5 \ V; \ V_{SEL0} = 0 \ V; \\ &V_{SEL1} = 0 \ V; \ I_{OUT} = 0 \ A; \\ &V_{OUT} = 4 \ V; \ R_{SENSE} = 1 \ k\Omega; \end{aligned}$                             | 5                    |          | 6.6                 | V        |

| İsenseh                                 | MultiSense output current in fault condition                                                     | Vcc = 13 V; Vsense = 5 V                                                                                                                                                                                                          | 7                    | 20       | 30                  | mA       |

| MultiSense ti<br>mode)") <sup>(4)</sup> | mings (current sense n                                                                           | node - see Figure 7: "MultiSense                                                                                                                                                                                                  | timings              | s (curre | ent sen             | se       |

| t <sub>DSENSE1H</sub>                   | Current sense settling time from rising edge of SEn                                              | $V_{IN} = 5 \text{ V}; V_{SEn} = 0 \text{ V to 5 V};$<br>$R_{SENSE} = 1 \text{ k}\Omega; R_L = 2.6 \Omega$                                                                                                                        |                      |          | 60                  | μs       |

| t <sub>DSENSE1L</sub>                   | Current sense disable delay time from falling edge of SEn                                        | $V_{IN} = 5 \text{ V}; V_{SEn} = 5 \text{ V to 0 V};$<br>$R_{SENSE} = 1 \text{ k}\Omega; R_L = 2.6 \Omega$                                                                                                                        |                      | 5        | 20                  | μs       |

| t <sub>DSENSE2H</sub>                   | Current sense settling time from rising edge of INPUT                                            | $V_{\text{IN}} = 0 \text{ V to 5 V; } V_{\text{SEn}} = 5 \text{ V;}$ $R_{\text{SENSE}} = 1 \text{ k}\Omega; \ R_{\text{L}} = 2.6 \ \Omega$                                                                                        |                      | 100      | 250                 | μs       |

| ∆t <sub>DSENSE2</sub> H                 | Current sense settling time from rising edge of lout (dynamic response to a step change of lout) | $V_{\text{IN}} = 5 \text{ V; } V_{\text{SEn}} = 5 \text{ V;}$ $R_{\text{SENSE}} = 1 \text{ k}\Omega; \text{ Isense} = 90 \% \text{ of}$ $I_{\text{SENSEMAX; }} R_{\text{L}} = 2.6 \Omega$                                         |                      |          | 100                 | μs       |

| 7 V < V <sub>CC</sub> < 18 V; -40°C < T <sub>j</sub> < 150°C                                                                   |                                                                                |                                                                                                                                                                                                                                                                                                 |          |          |      |      |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|------|------|--|--|--|

| Symbol                                                                                                                         | Parameter                                                                      | Test conditions                                                                                                                                                                                                                                                                                 | Min.     | Тур.     | Max. | Unit |  |  |  |

| t <sub>DSENSE2L</sub>                                                                                                          | Current sense turn-off delay time from falling edge of INPUT                   | $V_{IN} = 5$ V to 0 V; $V_{SEn} = 5$ V; $R_{SENSE} = 1$ k $\Omega$ ; $R_L = 2.6$ $\Omega$                                                                                                                                                                                                       |          | 50       | 250  | μs   |  |  |  |

| MultiSense timings (chip temperature sense mode - see Figure 8: "Multisense timings (chip temperature and VCC sense mode)")(4) |                                                                                |                                                                                                                                                                                                                                                                                                 |          |          |      |      |  |  |  |

| t <sub>DSENSE3H</sub>                                                                                                          | V <sub>SENSE_TC</sub> settling time from rising edge of SEn                    | $V_{SEn} = 0 \text{ V to 5 V; } V_{SEL0} = 0 \text{ V;}$<br>$V_{SEL1} = 5 \text{ V; } R_{SENSE} = 1 \text{ k}\Omega$                                                                                                                                                                            |          |          | 60   | μs   |  |  |  |

| t <sub>DSENSE3L</sub>                                                                                                          | V <sub>SENSE_TC</sub> disable delay time from falling edge of SEn              | $V_{SEn} = 5 \text{ V to } 0 \text{ V; } V_{SEL0} = 0 \text{ V;}$<br>$V_{SEL1} = 5 \text{ V; } R_{SENSE} = 1 \text{ k}\Omega$                                                                                                                                                                   |          |          | 20   | μs   |  |  |  |

|                                                                                                                                | imings (V <sub>CC</sub> voltage sense mode)"                                   | se mode - see <i>Figure 8: "Multise</i><br>) <sup>(4)</sup>                                                                                                                                                                                                                                     | ense tim | nings (d | hip  |      |  |  |  |

| t <sub>DSENSE4H</sub>                                                                                                          | Vsense_vcc settling time from rising edge of SEn                               | $V_{SEn} = 0 \text{ V to 5 V; } V_{SEL0} = 5 \text{ V;}$<br>$V_{SEL1} = 5 \text{ V; } R_{SENSE} = 1 \text{ k}\Omega$                                                                                                                                                                            |          |          | 60   | μs   |  |  |  |

| t <sub>DSENSE4L</sub>                                                                                                          | V <sub>SENSE_VCC</sub> disable delay time from falling edge of SEn             | $V_{SEn} = 5 \text{ V to } 0 \text{ V; } V_{SEL0} = 5 \text{ V;}$<br>$V_{SEL1} = 5 \text{ V; } R_{SENSE} = 1 \text{ k}\Omega$                                                                                                                                                                   |          |          | 20   | μs   |  |  |  |

| MultiSense t                                                                                                                   | imings (Multiplexer tran                                                       | sition times) <sup>(4)</sup>                                                                                                                                                                                                                                                                    |          |          |      |      |  |  |  |

| t <sub>D_CStoTC</sub>                                                                                                          | MultiSense transition delay from current sense to T <sub>C</sub> sense         | $\begin{split} &V_{IN} = 5 \; V; \; V_{SEn} = 5 \; V; \\ &V_{SEL0} = 0 \; V; \; V_{SEL1} = 0 \; V \; to \; 5 \; V; \\ &I_{OUT} = 2.5 \; A; \; R_{SENSE} = 1 \; k \Omega \end{split}$                                                                                                            |          |          | 60   | μs   |  |  |  |

| t <sub>D_TCto</sub> cs                                                                                                         | MultiSense transition delay from T <sub>C</sub> sense to current sense         | $\begin{split} &\text{V}_{\text{IN}} = 5 \text{ V}; \text{ V}_{\text{SEn}} = 5 \text{ V}; \\ &\text{V}_{\text{SEL0}} = 0 \text{ V}; \text{ V}_{\text{SEL1}} = 5 \text{ V to } 0 \text{ V}; \\ &\text{I}_{\text{OUT}} = 2.5 \text{ A}; \text{ R}_{\text{SENSE}} = 1 \text{ k}\Omega \end{split}$ |          |          | 20   | μs   |  |  |  |

| tp_cstovcc                                                                                                                     | MultiSense transition delay from current sense to V <sub>CC</sub> sense        | $\begin{split} &V_{\text{IN}} = 5 \text{ V}; \text{ V}_{\text{SEn}} = 5 \text{ V}; \\ &V_{\text{SEL0}} = 5 \text{ V}; \text{ V}_{\text{SEL1}} = 0 \text{ V to 5 V}; \\ &I_{\text{OUT}} = 2.5 \text{ A}; \text{ R}_{\text{SENSE}} = 1 \text{ k}\Omega \end{split}$                               |          |          | 60   | μs   |  |  |  |

| t <sub>D_</sub> vcctocs                                                                                                        | MultiSense transition delay from V <sub>CC</sub> sense to current sense        | $\begin{split} &V_{\text{IN}} = 5 \text{ V}; \text{ V}_{\text{SEn}} = 5 \text{ V}; \\ &V_{\text{SEL0}} = 5 \text{ V}; \text{ V}_{\text{SEL1}} = 5 \text{ V} \text{ to 0 V}; \\ &I_{\text{OUT}} = 2.5 \text{ A}; \text{ R}_{\text{SENSE}} = 1 \text{ k}\Omega \end{split}$                       |          |          | 20   | μs   |  |  |  |

| t <sub>D_TCto</sub> vcc                                                                                                        | MultiSense transition delay from T <sub>C</sub> sense to V <sub>CC</sub> sense | $\begin{split} &V_{CC} = 13 \ V; \ T_j = 125^{\circ}C; \\ &V_{SEn} = 5 \ V; \ V_{SEL0} = 0 \ V \ to \ 5 \ V; \\ &V_{SEl1} = 5 \ V; \ R_{SENSE} = 1 \ k\Omega \end{split}$                                                                                                                       |          |          | 20   | μs   |  |  |  |

| t <sub>D_</sub> vcctotc                                                                                                        | MultiSense transition delay from V <sub>CC</sub> sense to T <sub>C</sub> sense | $V_{CC} = 13 \text{ V; } T_j = 125^{\circ}\text{C;}$<br>$V_{SEn} = 5 \text{ V; } V_{SEL0} = 5 \text{ V to 0 V;}$<br>$V_{SEL1} = 5 \text{ V; } R_{SENSE} = 1 \text{ k}\Omega$                                                                                                                    |          |          | 20   | μs   |  |  |  |

#### Notes:

$<sup>\</sup>ensuremath{^{(1)}}\mbox{Parameter specified by design; not subject to production test.}$

$<sup>^{(2)}\</sup>text{All}$  values refer to Vcc = 13 V;  $T_j$  = 25°C, unless otherwise specified.

$<sup>^{(3)}\</sup>mbox{Vcc}$  sensing and Tc are referred to GND potential.

$<sup>^{\</sup>rm (4)} Transition$  delay are measured up to +/- 10% of final conditions.

Figure 4: IOUT/ISENSE versus IOUT

Figure 5: Current sense accuracy versus IOUT

Figure 6: Switching time and Pulse skew

Figure 7: MultiSense timings (current sense mode)

High SEn Low High SEL0 Low High SEL1 Low  $V_{CC}$ V<sub>SENSE</sub> = V<sub>SENSE\_VCC</sub>  $V_{SENSE} = V_{SENSE\_TC}$ SENSE t<sub>DSENSE4H</sub> t<sub>DSENSE4L</sub> t<sub>DSENSE3H</sub> t<sub>DSENSE3L</sub> VCC VOLTAGE SENSE MODE CHIP TEMPERATURE SENSE MODE GAPGCFT00319

Figure 8: Multisense timings (chip temperature and VCC sense mode)

Table 10: Truth table

| Mode                    | Conditions                                                                           | INx | FR | SEn | SELx             | OUTx  | MultiSense         | Comments                                     |

|-------------------------|--------------------------------------------------------------------------------------|-----|----|-----|------------------|-------|--------------------|----------------------------------------------|

| Standby                 | All logic inputs low                                                                 | П   | L  | L   | L                | L     | Hi-Z               | Low quiescent current consumption            |

|                         |                                                                                      | L   | X  |     |                  | L     | See (1)            |                                              |

| Normal                  | Nominal load connected;                                                              | Н   | L  | Se  | e <sup>(1)</sup> | Н     | See <sup>(1)</sup> | Outputs configured for auto-restart          |

|                         | T <sub>j</sub> < 150 °C                                                              | Ι   | Ι  |     |                  | Ι     | See <sup>(1)</sup> | Outputs configured for<br>Latch-off          |

|                         |                                                                                      |     | Χ  |     |                  | L     | See (1)            |                                              |

| Overload                | Overload or short to GND causing: $T_j > T_{TSD}$ or $\Delta T_j > \Delta T_{j\_SD}$ | Η   | L  | Se  | e <sup>(1)</sup> | Н     | See <sup>(1)</sup> | Output cycles with temperature hysteresis    |

|                         |                                                                                      | Н   | Н  |     |                  | L     | See (1)            | Output latches-off                           |

| Undervoltage            | Vcc < V <sub>USD</sub> (falling)                                                     | X   | X  | X   | X                |       | Hi-Z<br>Hi-Z       | Re-start when Vcc > Vusb + Vusbhyst (rising) |

| OFF-state               | Short to Vcc                                                                         | L   | Х  | C 0 | a (1)            | Н     | See (1)            |                                              |

| diagnostics             | Open-load                                                                            | L   | Χ  | Se  | e <sup>(1)</sup> | Н     | See (1)            | External pull-up                             |

| Negative output voltage | Inductive loads turn-off                                                             | L   | X  | Se  | e <sup>(1)</sup> | < 0 V | See (1)            |                                              |

#### Notes:

Table 11: MultiSense multiplexer addressing

|     |                  |                  | EL <sub>0</sub> MUX channel | MultiSense output |                                            |                 |                 |  |  |  |

|-----|------------------|------------------|-----------------------------|-------------------|--------------------------------------------|-----------------|-----------------|--|--|--|

| SEn | SEL <sub>1</sub> | SEL <sub>0</sub> |                             | Normal mode       | Overload                                   | OFF-state diag. | Negative output |  |  |  |

| L   | Χ                | Χ                |                             | Hi-Z              |                                            |                 |                 |  |  |  |

| Н   | L                | L                | Output                      | Isense =          | Vsense =                                   | Vsense =        | LI: 7           |  |  |  |

| Н   | L                | Н                | diagnostic                  | 1/K * Iоит        | Vsenseh                                    | Vsenseh         | Hi-Z            |  |  |  |

| Н   | Н                | L                | T <sub>CHIP</sub> Sense     |                   | V <sub>SENSE</sub> = V <sub>SENSE_TC</sub> |                 |                 |  |  |  |

| Н   | Н                | Η                | Vcc Sense                   |                   | Vsense = Vsense_vcc                        |                 |                 |  |  |  |

#### Notes:

(1)In case the output channel corresponding to the selected MUX channel is latched off while the relevant input is low, Multisense pin delivers feedback according to OFF-State diagnostic. Example 1: FR = 1; IN = 0; OUT = L (latched); MUX channel = channel 0 diagnostic; Mutisense = 0. Example 2: FR = 1; IN = 0; OUT = latched, Vout > Vol.; MUX channel = channel 0 diagnostic; Mutisense = Vsenseh

<sup>(1)</sup>Refer to Table 11: "MultiSense multiplexer addressing"

### 2.4 Waveforms

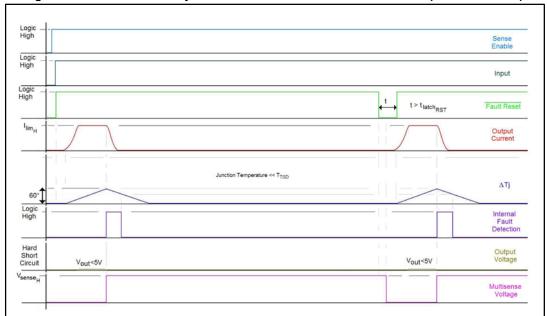

Figure 10: Latch functionality - behavior in hard short circuit condition (TAMB << TTSD)

Figure 11: Latch functionality - behavior in hard short circuit condition

Electrical specification VN7016AJ

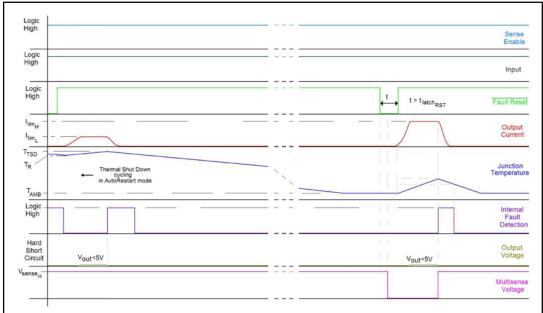

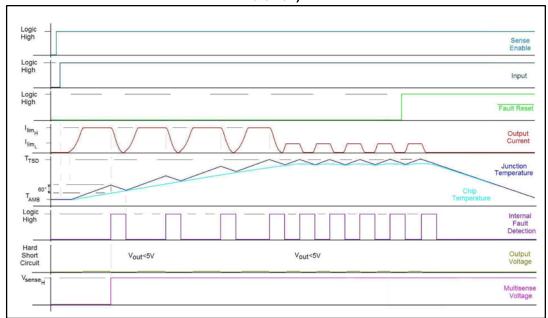

Figure 12: Latch functionality - behavior in hard short circuit condition (autorestart mode + latch off)

Figure 13: Standby mode activation

577

Figure 14: Standby state diagram **Normal Operation** INx = LowINx = HighAND OR FaultRST = Low FaultRST = High AND OR t > t <sub>D\_STBY</sub> SEn = Low SEn = High AND OR SELx = Low SELx = High Stand-by Mode GAPGCFT00598

#### 2.5 **Electrical characteristics curves**

VN7016AJ Protections

#### 3 Protections

#### 3.1 Power limitation

The basic working principle of this protection consists of an indirect measurement of the junction temperature swing  $\Delta T_j$  through the direct measurement of the spatial temperature gradient on the device surface in order to automatically shut off the output MOSFET as soon as  $\Delta T_j$  exceeds the safety level of  $\Delta T_{j\_SD}$ . According to the voltage level on the FaultRST pin, the output MOSFET switches on and cycles with a thermal hysteresis according to the maximum instantaneous power which can be handled (FaultRST = Low) or remains off (FaultRST = High). The protection prevents fast thermal transient effects and, consequently, reduces thermo-mechanical fatigue.

#### 3.2 Thermal shutdown