# VN5E010AFH-E

# 10 m $\Omega$ high-side driver with analog current sense for automotive applications

### Features

| Max supply voltage       | V <sub>CC</sub>   | 41 V                |

|--------------------------|-------------------|---------------------|

| Operating voltage range  | V <sub>CC</sub>   | 4.5 V to 28 V       |

| Typ. ON-state resistance | R <sub>ON</sub>   | 10 mΩ               |

| Current limitation (typ) | I <sub>LIMH</sub> | 85 A                |

| OFF-state supply current | ۱ <sub>S</sub>    | 2 µA <sup>(1)</sup> |

1. Typical value with all loads connected

#### General

- Very low standby current

- 3 V CMOS compatible inputs

- Optimized electromagnetic emissions

- Very low electromagnetic susceptibility

- Compliance with European directive 2002/95/EC

- Very low current sense leakage

- Diagnostic functions

- Proportional load current sense

- High current sense precision for wide current range

- Current sense disable

- OFF-state open-load detection

- Output short to V<sub>CC</sub> detection

- Overload and short to ground (power limitation) indication

- Thermal shutdown indication

- Protection

- Undervoltage shutdown

- Overvoltage clamp

- Load current limitation

- Self limiting of fast thermal transients

- Protection against loss of ground and loss of  $V_{CC}$

- Overtemperature shutdown with autorestart (thermal shutdown)

- Inrush current active management by power limitation

- Reverse battery protection with self switch on of the Power MOSFET

- Electrostatic discharge protection

### Applications

- All types of resistive, inductive and capacitive loads

- Suitable as LED driver

# Description

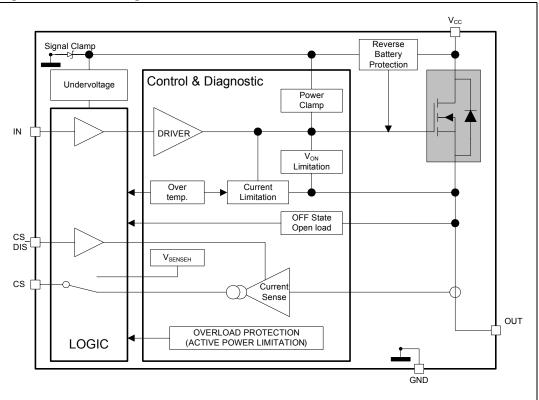

The VN5E010AFH-E is a single-channel high-side driver manufactured using ST proprietary VIPower<sup>™</sup> M0-5 technology and housed in HPAK package. The device is designed to drive 12 V automotive grounded loads, and to provide protection and diagnostics. It also implements a 3 V and 5 V CMOS compatible interface for use with any microcontroller.

The device integrates advanced protective functions such as load current limitation, inrush and overload active management by power limitation, overtemperature shut-off with autorestart and overvoltage active clamp. A dedicated analog current sense pin is associated with every output channel providing ehnanced diagnostic functions including fast detection of overload and short-circuit to ground through power limitation indication, overtemperature indication, short-circuit to V<sub>CC</sub> diagnosis and ON-state and OFF-state open-load detection.

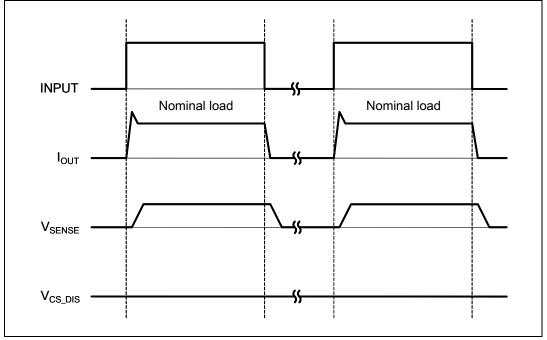

The current sensing and diagnostic feedback of the whole device can be disabled by pulling the CS\_DIS pin high to share the external sense resistor with similar devices.

December 2010

# Contents

| 1 | Bloc | k diagram and pin configuration5                     |

|---|------|------------------------------------------------------|

| 2 | Elec | trical specifications                                |

|   | 2.1  | Absolute maximum ratings 7                           |

|   | 2.2  | Thermal data                                         |

|   | 2.3  | Electrical characteristics                           |

|   | 2.4  | Waveforms                                            |

|   | 2.5  | Electrical characteristics curves 21                 |

| 3 | Арр  | lication information                                 |

|   | 3.1  | Load dump protection 24                              |

|   | 3.2  | MCU I/Os protection 24                               |

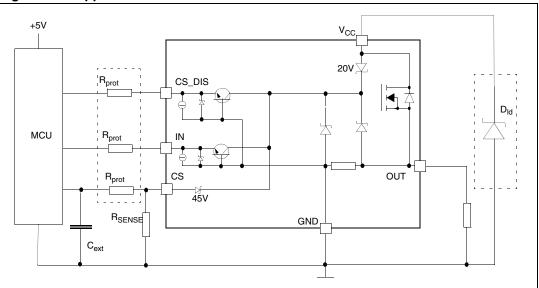

|   | 3.3  | Current sense and diagnostic                         |

|   |      | 3.3.1 Short to VCC and OFF-state open-load detection |

|   | 3.4  | Maximum demagnetization energy (VCC = 13.5 V) 27     |

| 4 | Pacl | cage and PC board thermal data 28                    |

|   | 4.1  | HPAK thermal data 28                                 |

| 5 | Pacl | age and packing information                          |

|   | 5.1  | ECOPACK <sup>®</sup>                                 |

|   | 5.2  | HPAK mechanical data                                 |

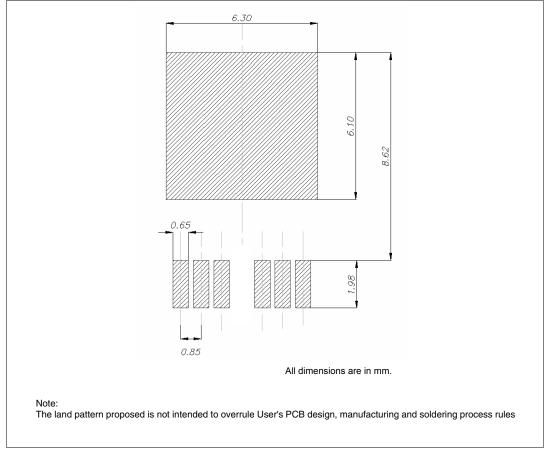

|   | 5.3  | HPAK suggested land pattern                          |

|   | 5.4  | Packing information                                  |

| 6 | Orde | er codes                                             |

| 7 | Revi | sion history                                         |

# List of tables

| Table 1.  | Pin functions                                           | 5 |

|-----------|---------------------------------------------------------|---|

| Table 2.  | Suggested connections for unused and not connected pins | 6 |

| Table 3.  | Absolute maximum ratings                                | 7 |

| Table 4.  | Thermal data                                            | 8 |

| Table 5.  | Power section                                           | 9 |

| Table 6.  | Switching (VCC = 13 V, Tj = 25 °C)                      | 9 |

| Table 7.  | Logic inputs                                            | 0 |

| Table 8.  | Protection and diagnostics                              | 0 |

| Table 9.  | Current sense (8 V < V <sub>CC</sub> < 18 V)            | 1 |

| Table 10. | Open-load detection (8 V < VCC < 18 V)                  |   |

| Table 11. | Truth table                                             |   |

| Table 12. | Electrical transient requirements (part 1) 1            | 7 |

| Table 13. | Electrical transient requirements (part 2) 1            | 7 |

| Table 14. | Electrical transient requirements (part 3) 1            | 7 |

| Table 15. | Thermal parameter                                       | 0 |

| Table 16. | HPAK mechanical data                                    | 2 |

| Table 17. | Device summary                                          | 5 |

| Table 18. | Document revision history                               | 6 |

# List of figures

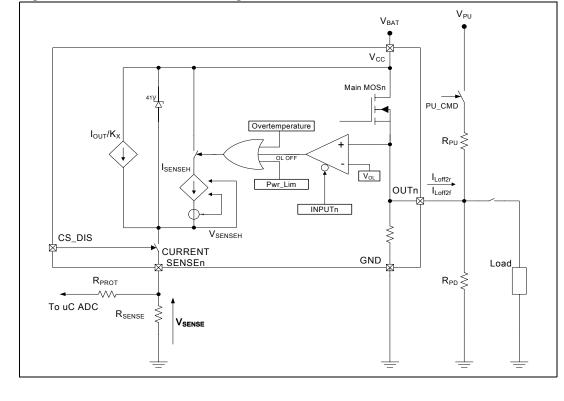

| Figure 1.  | Block diagram                                                                       |

|------------|-------------------------------------------------------------------------------------|

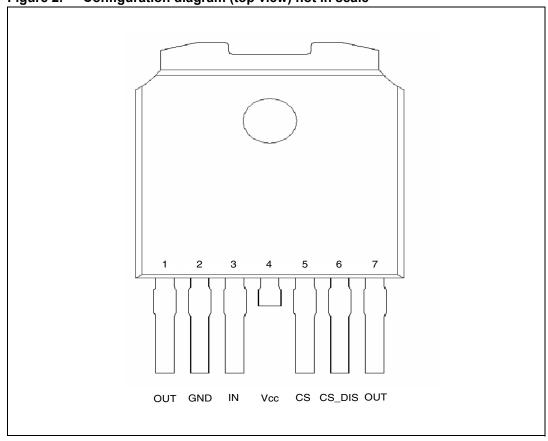

| Figure 2.  | Configuration diagram (top view) not in scale                                       |

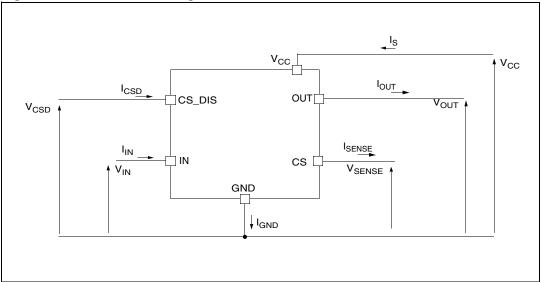

| Figure 3.  | Current and voltage conventions7                                                    |

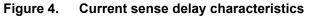

| Figure 4.  | Current sense delay characteristics                                                 |

| Figure 5.  | Open-load OFF-state delay timing                                                    |

| Figure 6.  | Switching characteristics                                                           |

| Figure 7.  | Delay response time between rising edge of ouput current and rising edge of current |

|            | sense (CS enabled)                                                                  |

| Figure 8.  | Output voltage drop limitation                                                      |

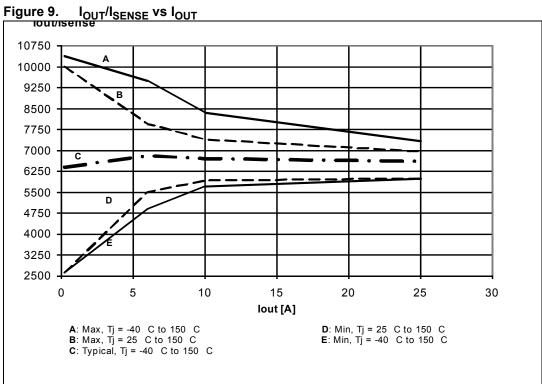

| Figure 9.  | I <sub>OUT</sub> /I <sub>SENSE</sub> vs I <sub>OUT</sub>                            |

| Figure 10. | Maximum current sense ratio drift vs load current                                   |

| Figure 11. | Normal operation                                                                    |

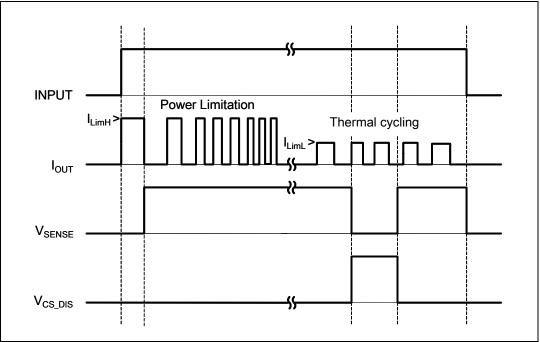

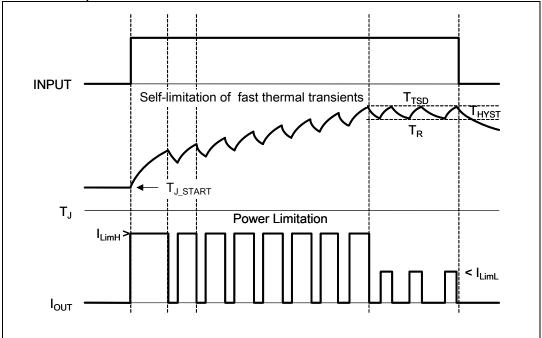

| Figure 12. | Overload or short to GND                                                            |

| Figure 13. | Intermittent overload                                                               |

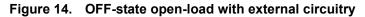

| Figure 14. | OFF-state open-load with external circuitry 19                                      |

| Figure 15. | Short to V <sub>CC</sub>                                                            |

| Figure 16. | T <sub>i</sub> evolution in overload or short to GND                                |

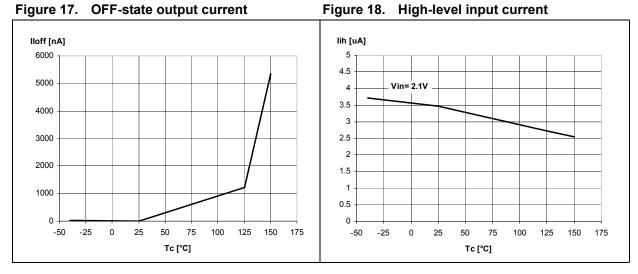

| Figure 17. | ÓFF-state output current                                                            |

| Figure 18. | High-level input current                                                            |

| Figure 19. | Input clamp voltage                                                                 |

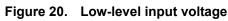

| Figure 20. | Low-level input voltage                                                             |

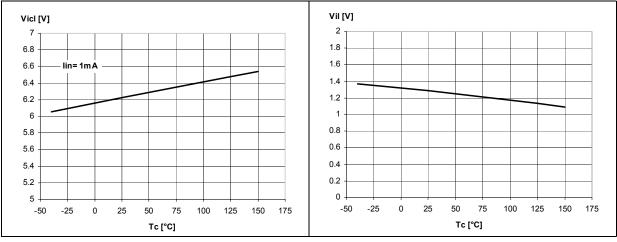

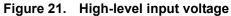

| Figure 21. | High-level input voltage                                                            |

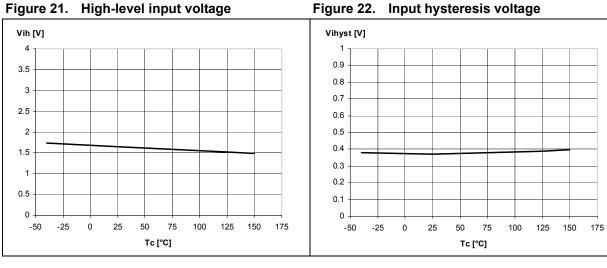

| Figure 22. | Input hysteresis voltage                                                            |

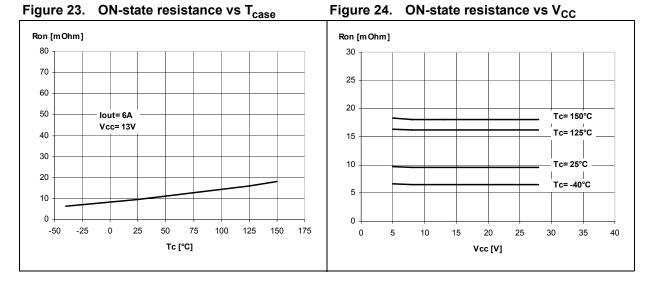

| Figure 23. | ON-state resistance vs Tcase                                                        |

| Figure 24. | ON-state resistance vs VCC                                                          |

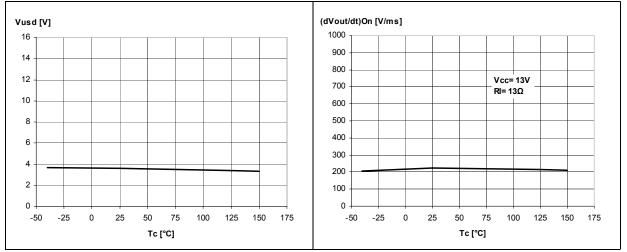

| Figure 25. | Undervoltage shutdown                                                               |

| Figure 26. | Turn-on voltage slope                                                               |

| Figure 27. | ILIMH vs Tcase                                                                      |

| Figure 28. | Turn-off voltage slope                                                              |

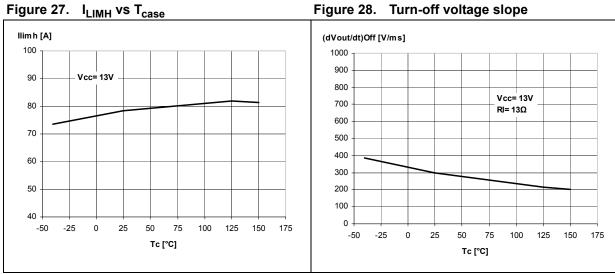

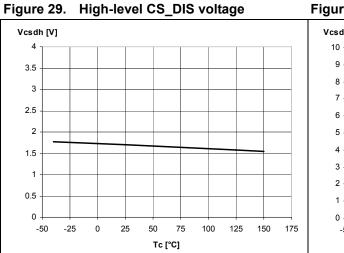

| Figure 29. | High-level CS_DIS voltage                                                           |

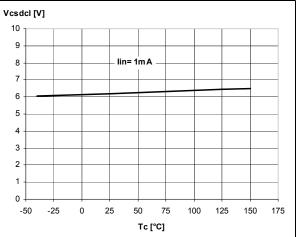

| Figure 30. | CS_DIS clamp voltage                                                                |

| Figure 31. | Low-level CS_DIS voltage                                                            |

| Figure 32. | Application schematic                                                               |

| Figure 33. | Current sense and diagnostic                                                        |

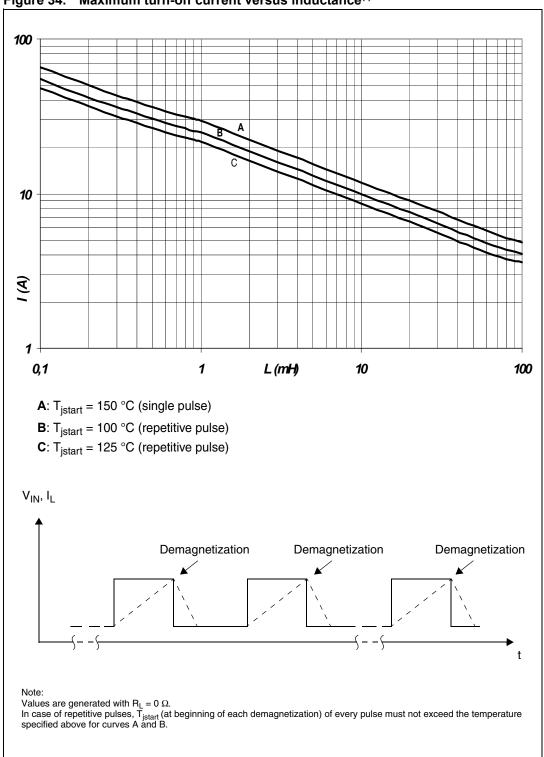

| Figure 34. | Maximum turn-off current versus inductance <sup>()</sup> 27                         |

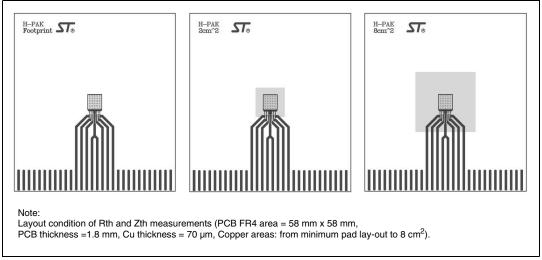

| Figure 35. | PC board                                                                            |

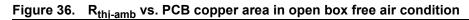

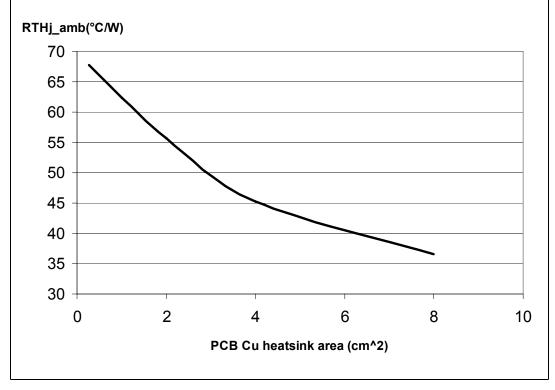

| Figure 36. | Rthj-amb vs. PCB copper area in open box free air condition                         |

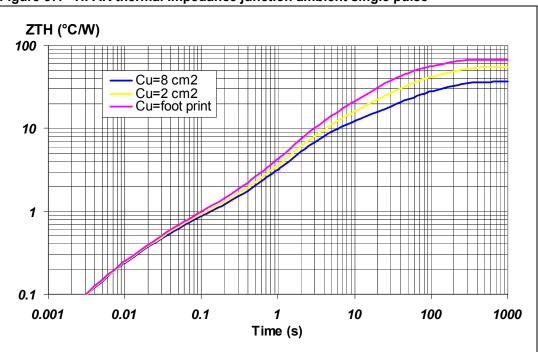

| Figure 37. | HPAK thermal impedance junction ambient single pulse                                |

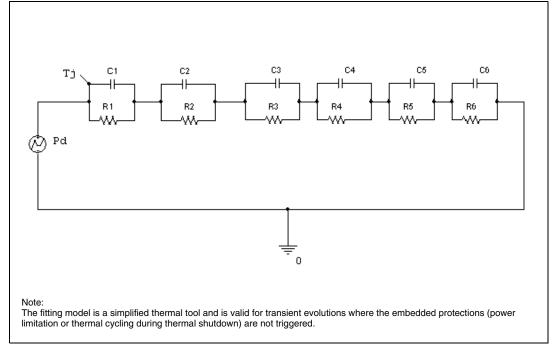

| Figure 38. | Thermal fitting model of a single-channel HSD in HPAK                               |

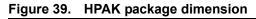

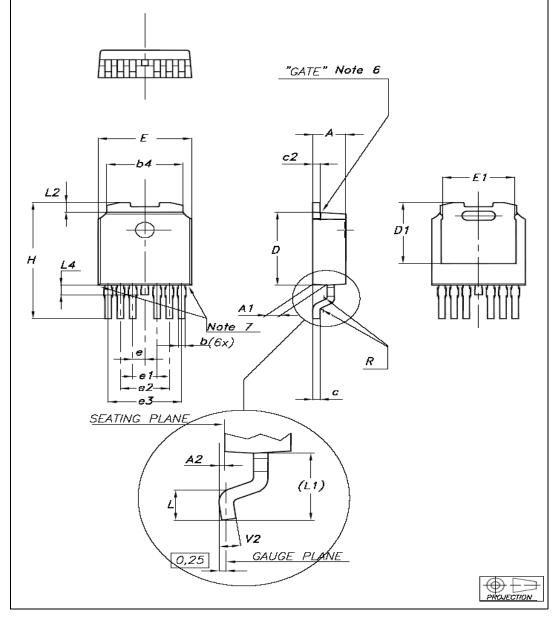

| Figure 39. | HPAK package dimension                                                              |

| Figure 40. | HPAK suggested pad layout                                                           |

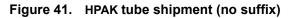

| Figure 41. | HPAK tube shipment (no suffix)                                                      |

| Figure 42. | HPAK tape and reel (suffix "TR")                                                    |

|            |                                                                                     |

# **1** Block diagram and pin configuration

#### Table 1.Pin functions

| Name            | Function                                                                                    |

|-----------------|---------------------------------------------------------------------------------------------|

| V <sub>CC</sub> | Battery connection                                                                          |

| OUT             | Power output <sup>(1)</sup>                                                                 |

| GND             | Ground connection                                                                           |

| IN              | Voltage controlled input pin with hysteresis, CMOS compatible. Controls output switch state |

| CS              | Analog CS pin, delivers a current proportional to the load current                          |

| CS_DIS          | Active high CMOS compatible pin, to disable the CS pin                                      |

1. Pins 1 and 7 must be externally tied together.

Figure 2. Configuration diagram (top view) not in scale

| Table 2. | Suggested connections for unused and not connected pins |

|----------|---------------------------------------------------------|

|----------|---------------------------------------------------------|

| Connection / pin | CS                       | Ουτ                       | IN                        | CS_DIS                    |

|------------------|--------------------------|---------------------------|---------------------------|---------------------------|

| Floating         | Not allowed              | Х                         | Х                         | х                         |

| To ground        | Through 1 kΩ<br>resistor | Through 22 kΩ<br>resistor | Through 10 kΩ<br>resistor | Through 10 kΩ<br>resistor |

# 2 Electrical specifications

#### Figure 3. Current and voltage conventions

### 2.1 Absolute maximum ratings

Stressing the device above the rating listed in the *Table 3: Absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE program and other relevant quality document.

| Symbol              | Parameter                                                                                                                                                                                               | Value              | Unit   |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------|

| V <sub>CC</sub>     | DC supply voltage                                                                                                                                                                                       | 41                 | V      |

| -V <sub>CC</sub>    | Reverse DC supply voltage                                                                                                                                                                               | 16                 | V      |

| I <sub>OUT</sub>    | DC output current                                                                                                                                                                                       | Internally limited | Α      |

| -I <sub>OUT</sub>   | Reverse DC output current                                                                                                                                                                               | 20                 | А      |

| I <sub>IN</sub>     | DC input current                                                                                                                                                                                        | -1 to 10           | mA     |

| I <sub>CSD</sub>    | DC current sense disable input current                                                                                                                                                                  | -1 to 10           | mA     |

| V <sub>CSENSE</sub> | SENSE Current sense maximum voltage (V <sub>CC</sub> > 0)                                                                                                                                               |                    | V<br>V |

| E <sub>MAX</sub>    | Maximum switching energy (single pulse)<br>(L = 2.2 mH; R <sub>L</sub> = 0 $\Omega$ ; V <sub>BAT</sub> = 13.5 V; T <sub>jstart</sub> = 150 °C;<br>I <sub>OUT</sub> = I <sub>limL</sub> ( <i>Typ.</i> )) | 645                | mJ     |

Table 3.

Absolute maximum ratings

| Symbol           | Parameter                                                             | Value      | Unit |

|------------------|-----------------------------------------------------------------------|------------|------|

|                  | Electrostatic discharge                                               |            |      |

|                  | (human body model: $R = 1.5 \text{ k}\Omega$ ; $C = 100 \text{ pF}$ ) |            |      |

|                  | – IN                                                                  | 4000       | V    |

| $V_{ESD}$        | – CS                                                                  | 2000       | V    |

|                  | – CS_DIS                                                              | 4000       | V    |

|                  | – OUT                                                                 | 5000       | V    |

|                  | – V <sub>CC</sub>                                                     | 5000       | V    |

| $V_{\text{ESD}}$ | Charge device model (CDM-AEC-Q100-011)                                | 750        | V    |

| Тj               | Junction operating temperature                                        | -40 to 150 | °C   |

| T <sub>stg</sub> | Storage temperature                                                   | -55 to 150 | °C   |

Table 3.

Absolute maximum ratings (continued)

# 2.2 Thermal data

| <b>-</b> | <b>—</b> , , , , , |

|----------|--------------------|

| Table 4. | Thermal data       |

| Symbol                                                   | Parameter                        | Max. value | Unit |  |

|----------------------------------------------------------|----------------------------------|------------|------|--|

| R <sub>thj-case</sub>                                    | Thermal resistance junction-case | 0.55       | °C/W |  |

| R <sub>thj-amb</sub> Thermal resistance junction-ambient |                                  | 67.7       | °C/W |  |

# 2.3 Electrical characteristics

Values specified in this section are for 8 V < V\_{CC} < 28 V, -40  $^\circ C$  < T\_j < 150  $^\circ C$ , unless otherwise specified.

| Symbol               | Parameter                                      | Test conditions                                                                                              | Min. | Тур. | Max. | Unit |

|----------------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------|------|------|------|

| $V_{CC}$             | Operating supply voltage                       |                                                                                                              | 4.5  | 13   | 28   | V    |

| V <sub>USD</sub>     | Undervoltage shutdown                          |                                                                                                              |      | 3.5  | 4.5  | V    |

| V <sub>USDhyst</sub> | Undervoltage shutdown<br>hysteresis            |                                                                                                              |      | 0.5  |      | V    |

|                      |                                                | I <sub>OUT</sub> = 6 A; T <sub>j</sub> = 25 °C                                                               |      | 10   |      |      |

| R <sub>ON</sub>      | ON-state resistance                            | I <sub>OUT</sub> = 6 A; T <sub>j</sub> = 150 °C                                                              |      |      | 20   | mΩ   |

|                      |                                                | $I_{OUT} = 6 \text{ A}; V_{CC} = 5 \text{ V}; T_j = 25 \text{ °C}$                                           |      |      | 13   |      |

| R <sub>ON-Rev</sub>  | R <sub>DSON</sub> in reverse battery condition | $V_{CC}$ = -13 V; $I_{OUT}$ = -6 A;<br>T <sub>j</sub> = 25 °C                                                |      | 10   |      | mΩ   |

| V <sub>clamp</sub>   | Clamp voltage                                  | I <sub>CC</sub> = 20 mA; I <sub>OUT</sub> = 0 A                                                              | 41   | 46   | 52   | V    |

| I                    | Supply autrent                                 | OFF-state: $V_{CC} = 13 \text{ V}$ ; $T_j = 25 \text{ °C}$ ;<br>$V_{IN} = V_{OUT} = V_{SENSE} = 0 \text{ V}$ |      | 2    | 5    | μA   |

| I <sub>S</sub>       | Supply current                                 | ON-state: $V_{CC} = 13 \text{ V}$ ; $V_{IN} = 5 \text{ V}$ ;<br>$I_{OUT} = 0 \text{ A}$                      |      | 1.5  | 3    | mA   |

| I <sub>L(off)</sub>  | OFF-state output current                       | $V_{IN} = V_{OUT} = 0 V; V_{CC} = 13 V;$<br>$T_j = 25 \text{ °C}$                                            | 0    | 0.01 | 3    | - μΑ |

|                      |                                                | $V_{IN} = V_{OUT} = 0 V; V_{CC} = 13 V;$<br>$T_j = 125 \text{ °C}$                                           | 0    |      | 5    |      |

Table 5.Power section

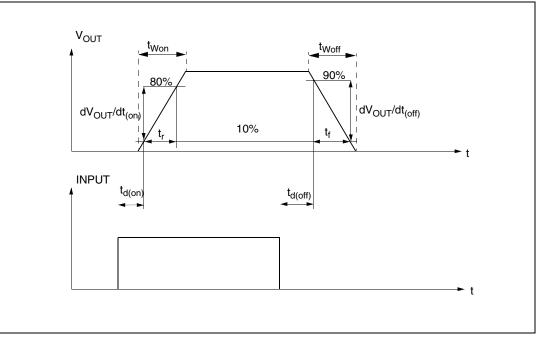

Table 6. Switching ( $V_{CC}$  = 13 V,  $T_j$  = 25 °C)

| Symbol                                 | Parameter                                                      | Test conditions                                  | Min. | Тур.            | Max. | Unit |

|----------------------------------------|----------------------------------------------------------------|--------------------------------------------------|------|-----------------|------|------|

| t <sub>d(on)</sub>                     | Turn-on delay time                                             | R <sub>L</sub> = 2.2 Ω<br>(see <i>Figure 6</i> ) | _    | 40              | _    | μs   |

| t <sub>d(off)</sub>                    | Turn-off delay time                                            | R <sub>L</sub> = 2.2 Ω<br>(see <i>Figure 6</i> ) |      | 28              |      | μs   |

| (dV <sub>OUT</sub> /dt) <sub>on</sub>  | Turn-on voltage slope                                          | $R_L = 2.2 \Omega$                               | _    | (see Figure 26) | _    | V/µs |

| (dV <sub>OUT</sub> /dt) <sub>off</sub> | Turn-off voltage slope                                         | $R_L = 2.2 \Omega$                               | _    | (see Figure 28) | _    | V/µs |

| W <sub>ON</sub>                        | Switching energy<br>losses at turn-on<br>(t <sub>won</sub> )   | R <sub>L</sub> = 2.2 Ω<br>(see <i>Figure 6</i> ) |      | 2               |      | mJ   |

| W <sub>OFF</sub>                       | Switching energy<br>losses at turn-off<br>(t <sub>woff</sub> ) | R <sub>L</sub> = 2.2 Ω<br>(see <i>Figure 6</i> ) | _    | 0.6             | _    | mJ   |

|                        | Logic inputs              |                          |      |      |      |      |  |

|------------------------|---------------------------|--------------------------|------|------|------|------|--|

| Symbol                 | Parameter                 | Test conditions          | Min. | Тур. | Max. | Unit |  |

| V <sub>IL</sub>        | Low-level input voltage   |                          |      |      | 0.9  | V    |  |

| IIL                    | Low-level input current   | V <sub>IN</sub> = 0.9 V  | 1    |      |      | μA   |  |

| V <sub>IH</sub>        | High-level input voltage  |                          | 2.1  |      |      | V    |  |

| I <sub>IH</sub>        | High-level input current  | V <sub>IN</sub> = 2.1 V  |      |      | 10   | μA   |  |

| V <sub>I(hyst)</sub>   | Input hysteresis voltage  |                          | 0.25 |      |      | V    |  |

| V                      |                           | I <sub>IN</sub> = 1 mA   | 5.5  |      | 7    | v    |  |

| V <sub>ICL</sub>       | Input clamp voltage       | I <sub>IN</sub> = -1 mA  |      | -0.7 |      | V    |  |

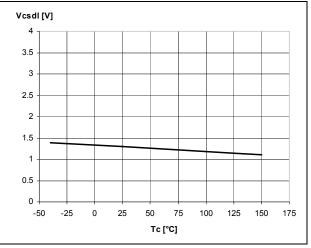

| V <sub>CSDL</sub>      | Low-level CS_DIS voltage  |                          |      |      | 0.9  | V    |  |

| I <sub>CSDL</sub>      | Low-level CS_DIS current  | V <sub>CSD</sub> = 0.9 V | 1    |      |      | μA   |  |

| V <sub>CSDH</sub>      | High-level CS_DIS voltage |                          | 2.1  |      |      | V    |  |

| I <sub>CSDH</sub>      | High-level CS_DIS current | V <sub>CSD</sub> = 2.1 V |      |      | 10   | μA   |  |

| V <sub>CSD(hyst)</sub> | CS_DIS hysteresis voltage |                          | 0.25 |      |      | V    |  |

| Veee                   |                           | I <sub>CSD</sub> = 1 mA  | 5.5  |      | 7    | v    |  |

| V <sub>CSCL</sub>      | CS_DIS clamp voltage      | I <sub>CSD</sub> = -1 mA |      | -0.7 |      |      |  |

|                        |                           |                          |      |      |      |      |  |

Table 7. Logic inputs

Table 8.

Protection and diagnostics<sup>(1)</sup>

| Symbol             | Parameter                                                  | Test conditions                                                              | Min.                 | Тур.                 | Max.                 | Unit |

|--------------------|------------------------------------------------------------|------------------------------------------------------------------------------|----------------------|----------------------|----------------------|------|

| 1                  | Short-circuit current                                      | V <sub>CC</sub> = 13 V                                                       | 60                   | 85                   | 120                  | А    |

| I <sub>limH</sub>  | Shon-circuit current                                       | 5 V < V <sub>CC</sub> < 28 V                                                 |                      |                      | 120                  | A    |

| I <sub>limL</sub>  | Short-circuit current during thermal cycling               | V <sub>CC</sub> =13 V;<br>T <sub>R</sub> < T <sub>j</sub> < T <sub>TSD</sub> |                      | 21                   |                      | A    |

| T <sub>TSD</sub>   | Shutdown temperature                                       |                                                                              | 150                  | 175                  | 200                  | °C   |

| Τ <sub>R</sub>     | Reset temperature                                          |                                                                              | T <sub>RS</sub> + 1  | T <sub>RS</sub> + 5  |                      | °C   |

| T <sub>RS</sub>    | Thermal reset of status                                    |                                                                              | 135                  |                      |                      | °C   |

| T <sub>HYST</sub>  | Thermal hysteresis<br>(T <sub>TSD</sub> - T <sub>R</sub> ) |                                                                              |                      | 7                    |                      | °C   |

| V <sub>DEMAG</sub> | Turn-off output voltage clamp                              | $I_{OUT} = 2 \text{ A}; \text{ V}_{IN} = 0;$<br>L = 6 mH                     | V <sub>CC</sub> - 41 | V <sub>CC</sub> - 46 | V <sub>CC</sub> - 52 | V    |

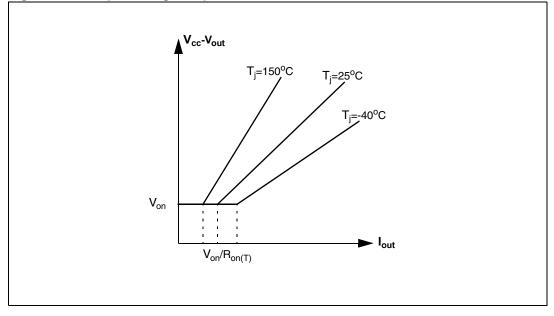

| V <sub>ON</sub>    | Output voltage drop<br>limitation                          | I <sub>OUT</sub> = 0.5 A;<br>T <sub>j</sub> = -40 °C to 150 °C               |                      | 25                   |                      | mV   |

1. To ensure long term reliability under heavy overload or short-circuit conditions, protection and related diagnostic signals must be used together with a proper software strategy. If the device is subjected to abnormal conditions, this software must limit the duration and number of activation cycles

| Table 9.Current sense (8 V < V <sub>CC</sub> < 18 V) |                                                           |                                                                                                                                                                                    |              |              |                |      |

|------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|----------------|------|

| Symbol                                               | Parameter                                                 | Test conditions                                                                                                                                                                    | Min.         | Тур.         | Max.           | Unit |

| K <sub>0</sub>                                       | I <sub>OUT</sub> /I <sub>SENSE</sub>                      | $I_{OUT} = 0.25 \text{ A}; V_{SENSE} = 0.5 \text{ V}$<br>$T_j = -40 \text{ °C to } 150 \text{ °C}$<br>$T_j = 25 \text{ °C to } 150 \text{ °C}$                                     | 2600<br>2600 | 6400<br>6400 | 10400<br>10000 |      |

| K <sub>1</sub>                                       | I <sub>OUT</sub> /I <sub>SENSE</sub>                      | $I_{OUT} = 6 \text{ A}; V_{SENSE} = 0.5 \text{ V}$<br>$T_j = -40 \text{ °C to } 150 \text{ °C}$<br>$T_j = 25 \text{ °C to } 150 \text{ °C}$                                        | 4900<br>5500 | 6800<br>6800 | 9500<br>7950   |      |

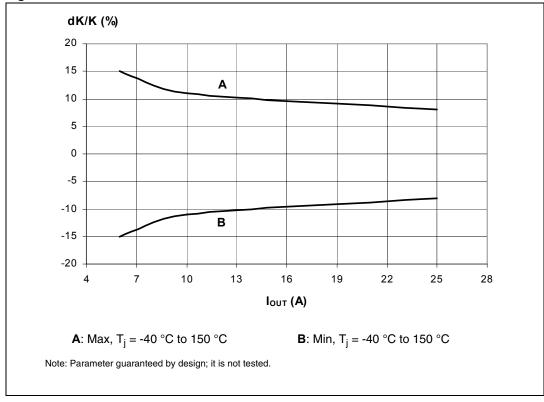

| dK <sub>1</sub> /K <sub>1</sub> <sup>(1)</sup>       | Current sense ratio drift                                 | $I_{OUT} = 6 \text{ A}; V_{SENSE} = 0.5 \text{ V};$<br>$V_{CSD} = 0 \text{ V};$<br>$T_j = -40 \text{ °C to } 150 \text{ °C}$                                                       | -15          |              | 15             | %    |

| K <sub>2</sub>                                       | I <sub>OUT</sub> /I <sub>SENSE</sub>                      | $I_{OUT} = 10 \text{ A}; V_{SENSE} = 4 \text{ V}$<br>$T_j = -40 ^{\circ}\text{C} \text{ to } 150 ^{\circ}\text{C}$<br>$T_j = 25 ^{\circ}\text{C} \text{ to } 150 ^{\circ}\text{C}$ | 5700<br>5900 | 6700<br>6700 | 8350<br>7400   |      |

| dK <sub>2</sub> /K <sub>2</sub> <sup>(1)</sup>       | Current sense ratio drift                                 | $I_{OUT} = 10 \text{ A}; \text{ V}_{SENSE} = 4 \text{ V};$<br>$V_{CSD} = 0 \text{ V};$<br>$T_j = -40 \text{ °C to 150 °C}$                                                         | -11          |              | 11             | %    |

| K <sub>3</sub>                                       | I <sub>OUT</sub> /I <sub>SENSE</sub>                      | $I_{OUT} = 25 \text{ A}; V_{SENSE} = 4 \text{ V}$<br>$T_j = -40 ^{\circ}\text{C} \text{ to } 150 ^{\circ}\text{C}$<br>$T_j = 25 ^{\circ}\text{C} \text{ to } 150 ^{\circ}\text{C}$ | 6000<br>6000 | 6600<br>6600 | 7350<br>6950   |      |

| dK <sub>3</sub> /K <sub>3</sub> <sup>(1)</sup>       | Current sense ratio drift                                 | $I_{OUT} = 25 \text{ A}; V_{SENSE} = 4 \text{ V};$<br>$V_{CSD} = 0 \text{ V};$<br>$T_j = -40 \text{ °C to } 150 \text{ °C}$                                                        | -8           |              | 8              | %    |

|                                                      |                                                           | $\begin{split} I_{OUT} &= 0 \text{ A};  V_{SENSE} = 0  V; \\ V_{CSD} &= 5  V;  V_{IN} = 0  V; \\ T_j &= -40 ^\circ\text{C} \text{ to } 150 ^\circ\text{C} \end{split}$             | 0            |              | 1              |      |

| I <sub>SENSE0</sub>                                  | Analog sense leakage<br>current                           | $\begin{split} I_{OUT} &= 0 \text{ A};  V_{SENSE} = 0  V; \\ V_{CSD} &= 0  V;  V_{IN} = 5  V; \\ T_j &= -40 ^\circ\text{C} \text{ to } 150 ^\circ\text{C} \end{split}$             | 0            |              | 2              | μA   |

|                                                      |                                                           | $I_{OUT} = 2 \text{ A}; V_{SENSE} = 0 \text{ V};$<br>$V_{CSD} = 5 \text{ V}; V_{IN} = 5 \text{ V};$<br>$T_j = -40 \text{ °C to } 150 \text{ °C}$                                   |              |              | 1              |      |

| I <sub>OL</sub>                                      | Open load ON-state<br>current detection<br>threshold      | V <sub>IN</sub> = 5 V; 8 V < V <sub>CC</sub> < 18 V;<br>I <sub>SENSE</sub> = 5 μA                                                                                                  | 5            |              | 80             | mA   |

| V <sub>SENSE</sub>                                   | Max analog sense<br>output voltage                        | l <sub>OUT</sub> = 18 A; R <sub>SENSE</sub> = 3.9 kΩ                                                                                                                               | 5            |              |                | V    |

| V <sub>SENSEH</sub> <sup>(2)</sup>                   | Analog sense output voltage in fault condition            | $V_{CC}$ = 13 V; $R_{SENSE}$ = 3.9 k $\Omega$                                                                                                                                      |              | 8            |                | V    |

| I <sub>SENSEH</sub> <sup>(2)</sup>                   | Analog sense output current in fault condition            | V <sub>CC</sub> = 13 V; V <sub>SENSE</sub> = 5 V                                                                                                                                   |              | 9            |                | mA   |

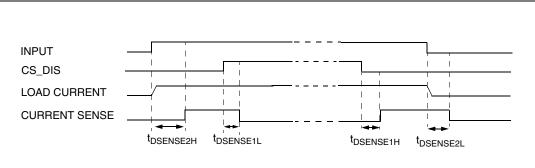

| t <sub>DSENSE1H</sub>                                | Delay response time<br>from falling edge of<br>CS_DIS pin | V <sub>SENSE</sub> < 4 V;<br>1.5 A < I <sub>OUT</sub> < 25 A<br>I <sub>SENSE</sub> = 90% of I <sub>SENSE max</sub><br>(see <i>Figure 4</i> )                                       |              | 50           | 100            | μs   |

Table 9. Current sense (8 V <  $V_{CC}$  < 18 V)

|                       |                                                                                                     |                                                                                                                                                                                     | -    | -    |      | -    |

|-----------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Symbol                | Parameter                                                                                           | Test conditions                                                                                                                                                                     | Min. | Тур. | Max. | Unit |

| t <sub>DSENSE1L</sub> | Delay response time<br>from rising edge of<br>CS_DIS pin                                            | V <sub>SENSE</sub> < 4 V;<br>1.5 A < I <sub>OUT</sub> < 25 A<br>I <sub>SENSE</sub> =10% of I <sub>SENSE max</sub><br>(see <i>Figure 4</i> )                                         |      | 5    | 20   | μs   |

| t <sub>DSENSE2H</sub> | Delay response time<br>from rising edge of<br>IN pin                                                | V <sub>SENSE</sub> < 4 V;<br>1.5 A < I <sub>OUT</sub> < 25 A<br>I <sub>SENSE</sub> =90% of I <sub>SENSE max</sub><br>(see <i>Figure 4</i> )                                         |      | 270  | 600  | μs   |

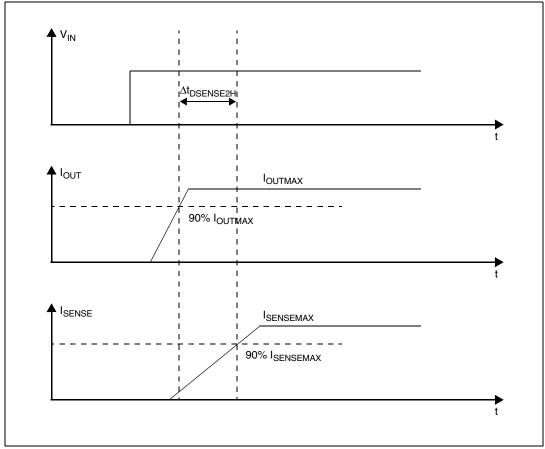

| $\Delta t_{DSENSE2H}$ | Delay response time<br>between rising edge of<br>output current and rising<br>edge of current sense | V <sub>SENSE</sub> < 4V;<br>I <sub>SENSE</sub> = 90% of I <sub>SENSEMAX</sub> ,<br>I <sub>OUT</sub> = 90% of I <sub>OUTMAX</sub><br>I <sub>OUTMAX</sub> = 3A (see <i>Figure 7</i> ) |      |      | 310  | μs   |

| t <sub>DSENSE2L</sub> | Delay response time<br>from falling edge of<br>IN pin                                               | V <sub>SENSE</sub> < 4 V;<br>1.5 A < I <sub>OUT</sub> < 25 A<br>I <sub>SENSE</sub> =10% of I <sub>SENSE max</sub><br>(see <i>Figure 4</i> )                                         |      | 100  | 250  | μs   |

Table 9. Current sense (8 V <  $V_{CC}$  < 18 V) (continued)

1. Parameter guaranteed by design, it is not tested.

2. Fault condition includes: power limitation, over-temperature and open load OFF-state detection.

| Symbol                 | Parameter                                                                                      | Test conditions                                                              | Min. | Тур.                   | Max. | Unit |

|------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------|------------------------|------|------|

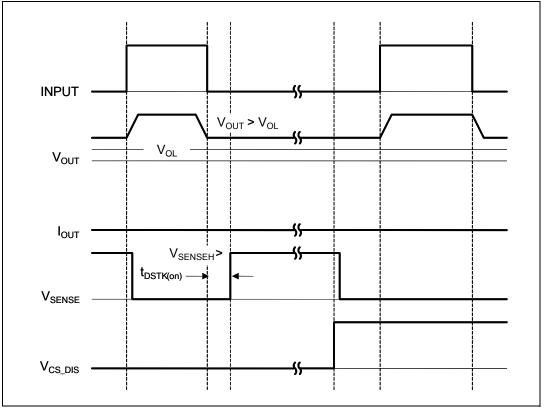

| V <sub>OL</sub>        | Open-load OFF-state<br>voltage detection<br>threshold                                          | V <sub>IN</sub> = 0 V                                                        | 2    | See<br><i>Figure 5</i> | 4    | v    |

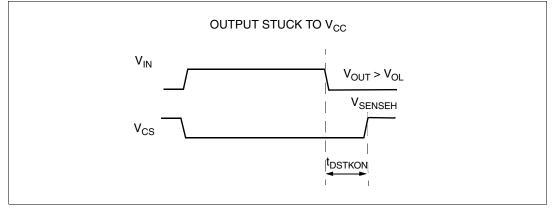

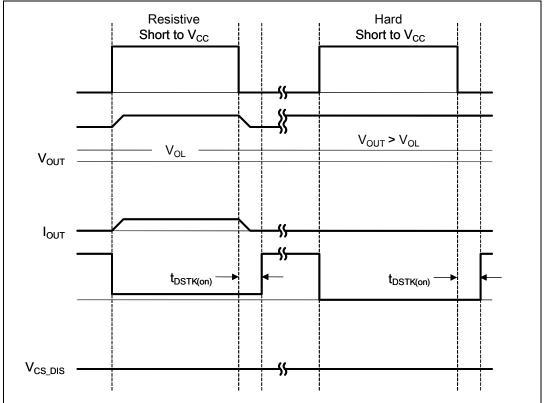

| t <sub>DSTKON</sub>    | Output short-circuit to $V_{CC}$ detection delay at turn-off                                   | See Figure 5                                                                 | 180  |                        | 1200 | μs   |

| I <sub>L(off2)</sub> r | OFF-state output<br>current at V <sub>OUT</sub> = 4 V                                          | $V_{IN} = 0 V; V_{SENSE} = 0 V$<br>$V_{OUT}$ rising from 0 V to 4 V          | -120 |                        | 90   | μΑ   |

| I <sub>L(off2)f</sub>  | OFF-state output<br>current at V <sub>OUT</sub> = 2 V                                          | $V_{IN} = 0 V; V_{SENSE} = V_{SENSEH}; V_{OUT}$ falling from $V_{CC}$ to 2 V | -50  |                        | 90   | μΑ   |

| t <sub>d_vol</sub>     | Delay response from<br>output rising edge to<br>V <sub>SENSE</sub> rising edge in<br>open-load | $V_{OUT} = 4 V; V_{IN} = 0 V$<br>$V_{SENSE} = 90\%$ of $V_{SENSEH}$          |      |                        | 20   | μs   |

Table 10. Open-load detection (8 V <  $V_{CC}$  < 18 V)

#### Figure 5. Open-load OFF-state delay timing

#### Figure 6. Switching characteristics

Figure 7. Delay response time between rising edge of ouput current and rising edge of current sense (CS enabled)

Figure 8. Output voltage drop limitation

Figure 10. Maximum current sense ratio drift vs load current

#### Table 11. Truth table

| Conditions                                                             | Input  | Output                                                      | SENSE $(V_{CSD} = 0 V)^{(1)}$    |

|------------------------------------------------------------------------|--------|-------------------------------------------------------------|----------------------------------|

| Normal operation                                                       | L<br>H | L<br>H                                                      | 0<br>Nominal                     |

| Overtemperature                                                        | L<br>H | L                                                           | 0<br>V <sub>SENSEH</sub>         |

| Undervoltage                                                           | L<br>H | L                                                           | 0<br>0                           |

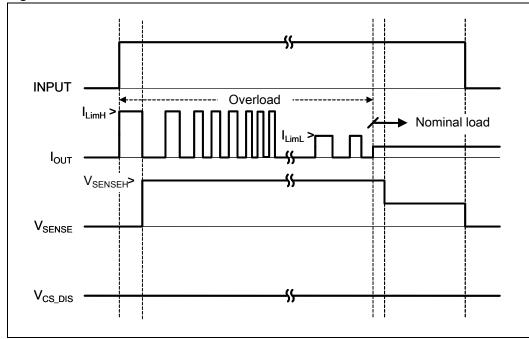

| Overload                                                               | н      | X<br>(no power limitation)<br>Cycling<br>(power limitation) | Nominal<br>V <sub>SENSEH</sub>   |

| Short-circuit to GND (power limitation)                                | L<br>H | L                                                           | 0<br>V <sub>SENSEH</sub>         |

| Open load OFF-state<br>(with external pull-up)                         | L      | н                                                           | V <sub>SENSEH</sub>              |

| Short-circuit to V <sub>CC</sub><br>(external pull-up<br>disconnected) | L<br>H | н                                                           | V <sub>SENSEH</sub><br>< Nominal |

| Negative output voltage clamp                                          | L      | L                                                           | 0                                |

If the V<sub>CSD</sub> is high, the SENSE output is at a high-impedance, its potential depends on leakage currents and external circuit.

| ISO 7637-2:<br>2004(E) | Test le | Test levels <sup>(1)</sup> Number of pulses or repetition time |             | Delays and |        |                       |

|------------------------|---------|----------------------------------------------------------------|-------------|------------|--------|-----------------------|

| Test pulse             | II      | IV                                                             | test times  | Min.       | Max.   | Impedance             |

| 1                      | -75 V   | -100 V                                                         | 5000 pulses | 0.5 s      | 5 s    | 2 ms, 10 Ω            |

| 2a                     | +37 V   | +50 V                                                          | 5000 pulses | 0.2 s      | 5 s    | 50 μs, 2 Ω            |

| 3a                     | -100 V  | -150 V                                                         | 1h          | 90 ms      | 100 ms | 0.1 μs, 50 Ω          |

| 3b                     | +75 V   | +100 V                                                         | 1h          | 90 ms      | 100 ms | 0.1 μs, 50 Ω          |

| 4                      | -6 V    | -7 V                                                           | 1 pulse     |            |        | 100 ms, 0.01 $\Omega$ |

| 5b <sup>(2)</sup>      | +65 V   | +87 V                                                          | 1 pulse     |            |        | 400 ms, 2 Ω           |

Table 12. Electrical transient requirements (part 1)

1. The above test levels must be considered referred to  $V_{CC}$  = 13.5 V except for pulse 5b.

2. Valid in case of external load dump clamp: 40 V maximum referred to ground.

Table 13.

Electrical transient requirements (part 2)

| ISO 7637-2:<br>2004(E) | Test level results |    |  |  |  |

|------------------------|--------------------|----|--|--|--|

| Test pulse             | Ш                  | IV |  |  |  |

| 1                      | С                  | С  |  |  |  |

| 2a                     | C                  | С  |  |  |  |

| 3a                     | C                  | С  |  |  |  |

| 3b                     | C                  | С  |  |  |  |

| 4                      | C                  | С  |  |  |  |

| 5b <sup>(1)</sup>      | С                  | С  |  |  |  |

1. Valid in case of external load dump clamp: 40V maximum referred to ground.

| Table 14. Electrical transferit requirements (part 5 | Table 14. | <b>Electrical transient</b> | requirements | (part 3) |

|------------------------------------------------------|-----------|-----------------------------|--------------|----------|

|------------------------------------------------------|-----------|-----------------------------|--------------|----------|

| Class | Contents                                                                                                                                                                 |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| С     | All functions of the device are performed as designed after exposure to disturbance.                                                                                     |

| E     | One or more functions of the device are not performed as designed after exposure to disturbance and cannot be returned to proper operation without replacing the device. |

### 2.4 Waveforms

#### Figure 12. Overload or short to GND

Figure 13. Intermittent overload

Figure 15. Short to V<sub>CC</sub>

Figure 16. T<sub>i</sub> evolution in overload or short to GND

#### 2.5 **Electrical characteristics curves**

Figure 26. Turn-on voltage slope

22/37

#### Figure 30. CS\_DIS clamp voltage

Figure 31. Low-level CS\_DIS voltage

# 3 Application information

#### Figure 32. Application schematic

### 3.1 Load dump protection

$D_{ld}$  is necessary (voltage transient suppressor) if the load dump peak voltage exceeds the  $V_{CC}$  max DC rating. The same applies if the device is subject to transients on the  $V_{CC}$  line that are greater than the ones shown in the ISO 7637-2 2004 (E) table.

### 3.2 MCU I/Os protection

When negative transients are present on the  $V_{CC}$  line, the control pins is pulled negative to approximatly -1.5 V. ST suggests to insert a resistor ( $R_{prot}$ ) in line to prevent the microcontroller I/Os pins to latch-up.

The value of these resistors is a compromise between the leakage current of microcontroller and the current required by the HSD I/Os (input levels compatibility) with the latch-up limit of microcontroller I/Os.

#### **Equation 1**

$$-V_{CCpeak} / I_{latchup} \le R_{prot} \le (V_{OH\mu C} - V_{IH}) / I_{IHmax}$$

Calculation example:

For  $V_{CCpeak}$  = - 1.5 V;  $I_{latchup} \ge 20$  mA;  $V_{OH\mu C} \ge 4.5$  V

$75 \ \Omega \le R_{prot} \le 240 \ k\Omega$ .

Recommended values:  $R_{prot} = 10 \text{ k}\Omega$ ,  $C_{EXT} = 10 \text{ nF}$ .

Doc ID 18044 Rev 2

24/37

### 3.3 Current sense and diagnostic

The current sense pin performs a double function (see *Figure 33: Current sense and diagnostic*):

- Current mirror of the load current in normal operation, delivering a current proportional to the load one according to a known ratio K<sub>X</sub>. The current I<sub>SENSE</sub> can be easily converted to a voltage V<sub>SENSE</sub> by means of an external resistor R<sub>SENSE</sub>. Linearity between I<sub>OUT</sub> and V<sub>SENSE</sub> is ensured up to 5 V minimum (see parameter V<sub>SENSE</sub> in *Table 9: Current sense (8 V < V<sub>CC</sub> < 18 V)*). The current sense accuracy depends on the output current (refer to current sense electrical characteristics *Table 9: Current sense (8 V < V<sub>CC</sub> < 18 V)*).

- Diagnostic flag in fault conditions, delivering a fixed voltage V<sub>SENSEH</sub> up to a maximum current I<sub>SENSEH</sub> in case of the following fault conditions (refer to *Table 11: Truth table*):

- Power limitation activation

- Overtemperature

- Short to V<sub>CC</sub> in OFF-state

- Open load in OFF-state with additional external components.

A logic level high on CS\_DIS pin sets at the same time all the current sense pins of the device in a high-impedance state, thus disabling the current monitoring and diagnostic detection. This feature allows multiplexing of the microcontroller analog inputs by sharing of sense resistance and ADC line among different devices.

#### 3.3.1 Short to V<sub>CC</sub> and OFF-state open-load detection

#### Short to V<sub>CC</sub>

A short-circuit between  $V_{CC}$  and output is indicated by the relevant current sense pin set to  $V_{SENSEH}$  during the device OFF-state. Small or no current is delivered by the current sense during the ON-state depending on the nature of the short-circuit.

#### OFF-state open-load with external circuitry

Detection of an open load in off mode requires an external pull-up resistor  $R_{PU}$  connecting the output to a positive supply voltage  $V_{PU}$ .

It is preferable  $V_{PU}$  to be switched off during the module standby mode in order to avoid the overall standby current consumption to increase in normal conditions, i.e. when load is connected.

An external pull-down resistor R<sub>PD</sub> connected between output and GND is mandatory to avoid misdetection in case of floating outputs in OFF-state (see *Figure 33: Current sense and diagnostic*).

$R_{PD}$  must be selected in order to ensure  $V_{OUT} < V_{OLmin}$  unless pulled-up by the external circuitry:

#### **Equation 2**

$$\left. \mathsf{V}_{\mathsf{OUT}} \right|_{\mathsf{Pul}\vdash\mathsf{up}_{\mathsf{OFF}}} \!=\! \mathsf{R}_{\mathsf{PD}} \cdot \mathsf{I}_{\mathsf{L}(\mathsf{off2})\mathsf{f}} \! < \! \mathsf{V}_{\mathsf{OLmin}} \! = \! 2 \; \mathsf{V}$$

$R_{PD} \le 22 \ k\Omega$  is recommended.

For proper open load detection in OFF-state, the external pull-up resistor must be selected according to the following formula:

#### **Equation 3**

$$\left. \mathsf{V}_{\mathsf{OUT}} \right|_{\mathsf{Pul}\mathsf{Hup}_{\mathsf{OUT}}} = \frac{\left(\mathsf{R}_{\mathsf{PD}} \cdot \mathsf{V}_{\mathsf{PU}}\right) - \left(\mathsf{R}_{\mathsf{PU}} \cdot \mathsf{R}_{\mathsf{PD}} \cdot \mathsf{I}_{\mathsf{L(off2)r}}\right)}{\left(\mathsf{R}_{\mathsf{PU}} + \mathsf{R}_{\mathsf{PD}}\right)} > \mathsf{V}_{\mathsf{OLmax}} = 4 \mathsf{V}$$

For the values of  $V_{OLmin}$ ,  $V_{OLmax}$ ,  $I_{L(off2)r}$  and  $I_{L(off2)f}$  (see *Table 10: Open-load detection (8 V < VCC < 18 V*)).

# 3.4 Maximum demagnetization energy (V<sub>CC</sub> = 13.5 V)

Figure 34. Maximum turn-off current versus inductance<sup>()</sup>

# 4 Package and PC board thermal data

### 4.1 HPAK thermal data

#### Figure 35. PC board

Figure 37. HPAK thermal impedance junction ambient single pulse

Figure 38. Thermal fitting model of a single-channel HSD in HPAK

57

### Equation 4: pulse calculation formula

$$Z_{TH\delta} \; = \; R_{TH} \cdot \delta + Z_{THtp}(1-\delta)$$

where  $\delta = t_P/T$

| Area/island (cm <sup>2</sup> ) | Footprint | 4   | 8  |

|--------------------------------|-----------|-----|----|

| R1 (°C/W)                      | 0.01      |     |    |

| R2 (°C/W)                      | 0.15      |     |    |

| R3 (°C/W)                      | 0.5       |     |    |

| R4 (°C/W)                      | 8         |     |    |

| R5 (°C/W)                      | 28        | 22  | 12 |

| R6 (°C/W)                      | 31        | 25  | 16 |

| C1 (W.s/°C)                    | 0.005     |     |    |

| C2 (W.s/°C)                    | 0.05      |     |    |

| C3 (W.s/°C)                    | 0.1       |     |    |

| C4 (W.s/°C)                    | 0.4       |     |    |

| C5 (W.s/°C)                    | 0.8       | 1.4 | 3  |

| C6 (W.s/°C)                    | 3         | 6   | 9  |

# 5 Package and packing information

### 5.1 ECOPACK<sup>®</sup>

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: <u>www.st.com</u>. ECOPACK<sup>®</sup> is an ST trademark.

# 5.2 HPAK mechanical data

| Table 16. HPAK mechanical data |              |      |       |  |

|--------------------------------|--------------|------|-------|--|

| Ref. dim                       | Data book mm |      |       |  |

| Rei. uitti                     | Nom.         | Min. | Max.  |  |

| A                              |              | 2.20 | 2.40  |  |

| A1                             |              | 0.90 | 1.10  |  |

| A2                             |              | 0.03 | 0.23  |  |

| b                              |              | 0.40 | 0.55  |  |

| b4                             |              | 5.20 | 5.40  |  |

| С                              |              | 0.45 | 0.60  |  |

| c2                             |              | 0.48 | 0.60  |  |

| D                              |              | 6.00 | 6.20  |  |

| D1                             | 5.10         |      |       |  |

| E                              |              | 6.40 | 6.60  |  |

| E1                             | 5.20         |      |       |  |

| е                              | 0.85         |      |       |  |

| e1                             |              | 1.60 | 1.80  |  |

| e2                             |              | 3.30 | 3.50  |  |

| e3                             |              | 5.00 | 5.20  |  |

| Н                              |              | 9.35 | 10.10 |  |

| L                              |              | 1    |       |  |

| (L1)                           | 2.80         |      |       |  |

| L2                             | 0.80         |      |       |  |

| L4                             |              | 0.60 | 1.00  |  |

| R                              | 0.20         |      |       |  |

| V2                             |              | 0°   | 8°    |  |

Table 16. HPAK mechanical data

32/37

# 5.3 HPAK suggested land pattern

#### Figure 40. HPAK suggested pad layout

### 5.4 Packing information

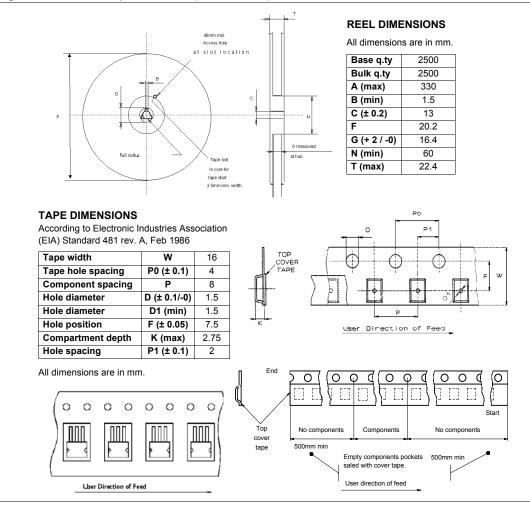

The devices can be packed in tube or tape and reel shipments (see *Table 17: Device summary*).

Figure 42. HPAK tape and reel (suffix "TR")

# 6 Order codes

#### Table 17. Device summary

| Package     | Order codes  |                |

|-------------|--------------|----------------|

|             | Tube         | Tape and reel  |

| 6 pins HPAK | VN5E010AFH-E | VN5E010AFHTR-E |

# 7 Revision history

#### Table 18. Document revision history

| Date        | Revision | Changes                                                    |  |

|-------------|----------|------------------------------------------------------------|--|

| 02-Nov-2010 | 1        | Initial release.                                           |  |

| 15-Dec-2010 | 2        | Changed document state from preliminary data to datasheet. |  |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2010 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com