# 200 mA, PFM Step-Up Micropower Switching Regulator

The NCP1402 series are monolithic micropower step-up DC to DC converter that are specially designed for powering portable equipment from one or two cell battery packs. These devices are designed to startup with a cell voltage of 0.8 V and operate down to less than 0.3 V. With only three external components, this series allow a simple means to implement highly efficient converters that are capable of up to 200 mA of output current at  $V_{in} = 2.0$  V,  $V_{OUT} = 3.0$  V.

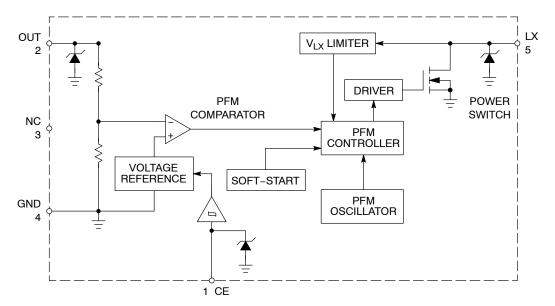

Each device consists of an on-chip PFM (Pulse Frequency Modulation) oscillator, PFM controller, PFM comparator, soft-start, voltage reference, feedback resistors, driver, and power MOSFET switch with current limit protection. Additionally, a chip enable feature is provided to power down the converter for extended battery life.

The NCP1402 device series are available in the Thin SOT-23-5 package with five standard regulated output voltages. Additional voltages that range from 1.8 V to 5.0 V in 100 mV steps can be manufactured.

#### Features

- Extremely Low Startup Voltage of 0.8 V

- Operation Down to Less than 0.3 V

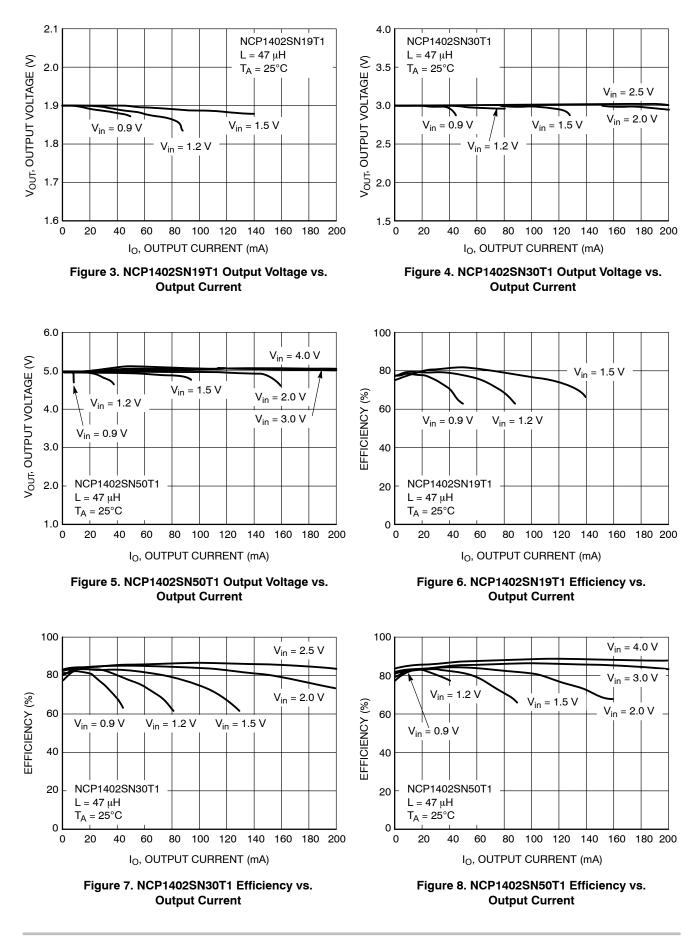

- High Efficiency 85% ( $V_{in} = 2.0 \text{ V}, V_{OUT} = 3.0 \text{ V}, 70 \text{ mA}$ )

- Low Operating Current of 30  $\mu$ A (V<sub>OUT</sub> = 1.9 V)

- Output Voltage Accuracy ±2.5%

- Low Converter Ripple with Typical 30 mV

- Only Three External Components Are Required

- Chip Enable Power Down Capability for Extended Battery Life

- Micro Miniature Thin SOT-23-5 Packages

- Pb–Free Packages are Available

#### **Typical Applications**

- Cellular Telephones

- Pagers

- Personal Digital Assistants (PDA)

- Electronic Games

- Portable Audio (MP3)

- Camcorders

- Digital Cameras

- Handheld Instruments

## **ON Semiconductor®**

http://onsemi.com

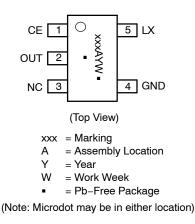

SOT23-5 (TSOP-5, SC59-5) SN SUFFIX CASE 483

#### PIN CONNECTIONS AND MARKING DIAGRAM

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the ordering information section on page 18 of this data sheet.

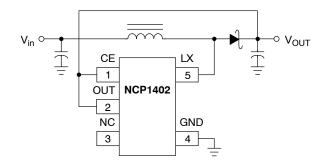

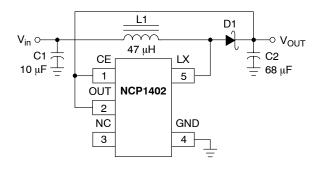

Figure 1. Typical Step-Up Converter Application

Figure 2. Representative Block Diagram

#### **PIN FUNCTION DESCRIPTIONS**

| Pin # | Symbol | Pin Description                                                                                                                                                                                                                                |

|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | CE     | Chip Enable pin<br>(1) The chip is enabled if a voltage which is equal to or greater than 0.9 V is applied<br>(2) The chip is disabled if a voltage which is less than 0.3 V is applied<br>(3) The chip will be enabled if it is left floating |

| 2     | OUT    | Output voltage monitor pin, also the power supply pin of the device                                                                                                                                                                            |

| 3     | NC     | No internal connection to this pin                                                                                                                                                                                                             |

| 4     | GND    | Ground pin                                                                                                                                                                                                                                     |

| 5     | LX     | External inductor connection pin to power switch drain                                                                                                                                                                                         |

#### **ABSOLUTE MAXIMUM RATINGS**

| Rating                                                   | Symbol                             | Value                      | Unit    |

|----------------------------------------------------------|------------------------------------|----------------------------|---------|

| Power Supply Voltage (Pin 2)                             | V <sub>OUT</sub>                   | 6.0                        | V       |

| Input/Output Pins<br>LX (Pin 5)<br>LX Peak Sink Current  | V <sub>LX</sub><br>I <sub>LX</sub> | -0.3 to 6.0<br>400         | V<br>mA |

| CE (Pin 1)<br>Input Voltage Range<br>Input Current Range | V <sub>CE</sub><br>I <sub>CE</sub> | –0.3 to 6.0<br>–150 to 150 | V<br>mA |

| Thermal Resistance, Junction-to-Air                      | $R_{	heta JA}$                     | 250                        | °C/W    |

| Operating Ambient Temperature Range (Note 2)             | T <sub>A</sub>                     | -40 to +85                 | °C      |

| Operating Junction Temperature Range                     | TJ                                 | -40 to +125                | °C      |

| Storage Temperature Range                                | T <sub>stg</sub>                   | -55 to +150                | °C      |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

NOTES:

- 1. This device series contains ESD protection and exceeds the following tests: Human Body Model (HBM) ±2.0 kV per JEDEC standard: JESD22–A114. Machine Model (MM) ±150 V per JEDEC standard: JESD22-A115.

- 2. The maximum package power dissipation limit must not be exceeded.

$$P_{D} = \frac{T_{J(max)} - T_{A}}{R_{\theta}JA}$$

- Latchup Current Maximum Rating: ±150 mA per JEDEC standard: JESD78.

Moisture Sensitivity Level: MSL 1 per IPC/JEDEC standard: J-STD-020A.

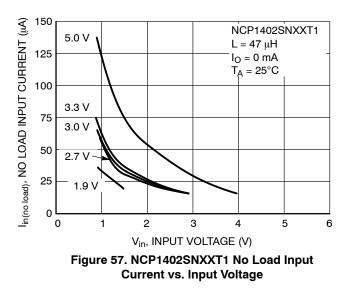

| ELECTRICAL CHARACTERISTICS | (For all values $T_A = 25^{\circ}C$ , unless otherwise noted.) |

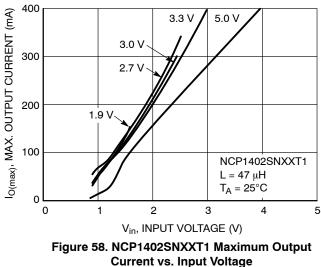

|----------------------------|----------------------------------------------------------------|

|----------------------------|----------------------------------------------------------------|

| Characteristic                                                                                                                   | Symbol                | Min            | Тур        | Max            | Unit    |

|----------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------|------------|----------------|---------|

| OSCILLATOR                                                                                                                       | -                     |                |            | 1              |         |

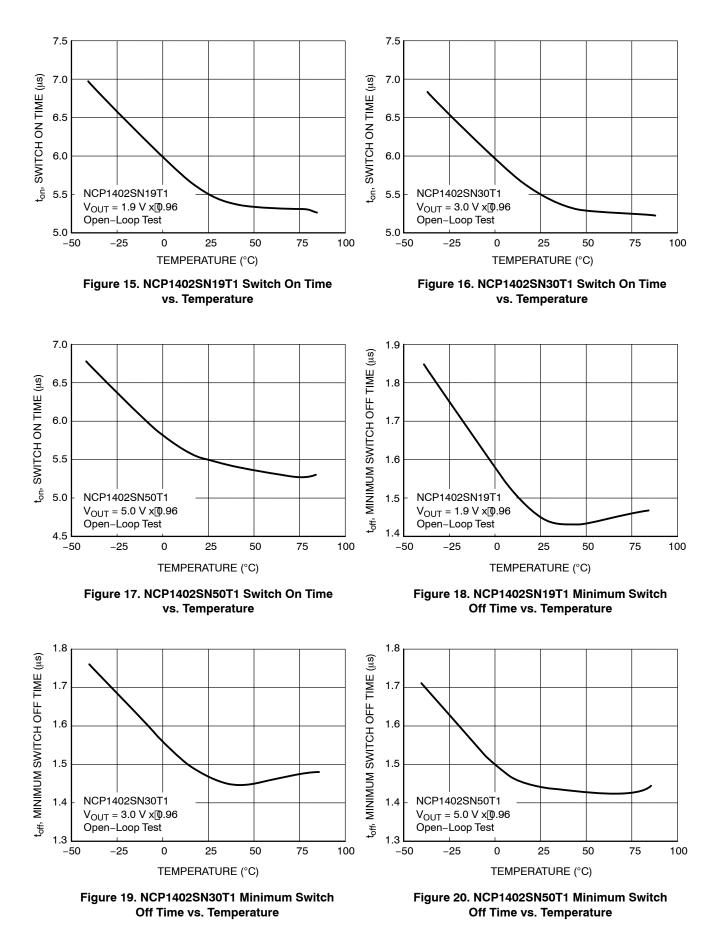

| Switch On Time (current limit not asserted)                                                                                      | t <sub>on</sub>       | 3.6            | 5.5        | 7.6            | μs      |

| Switch Minimum Off Time                                                                                                          | t <sub>off</sub>      | 1.0            | 1.45       | 1.9            | μs      |

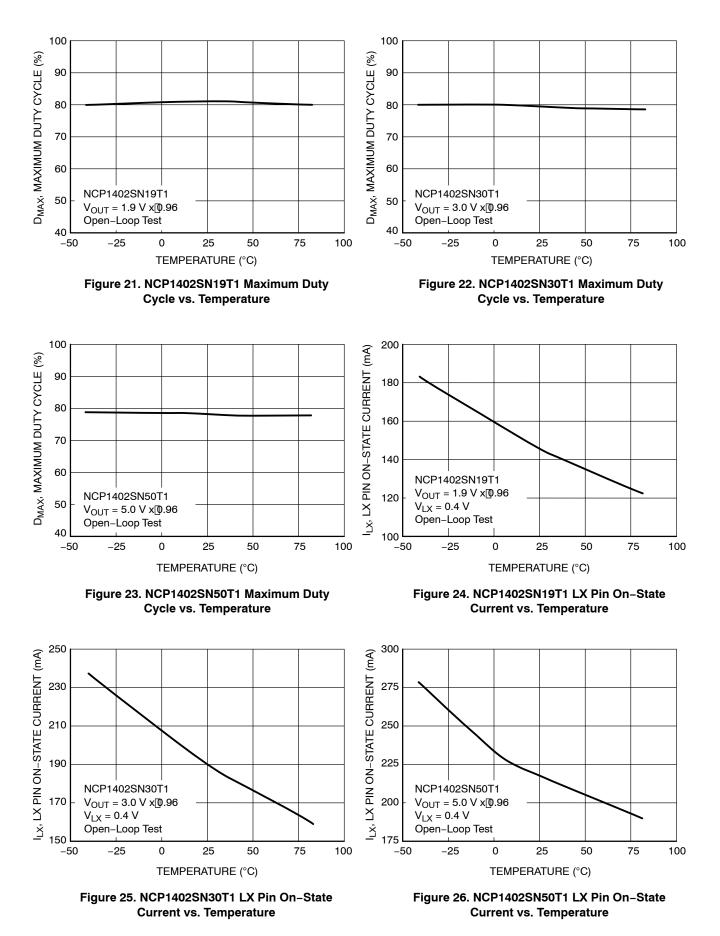

| Maximum Duty Cycle                                                                                                               | D <sub>MAX</sub>      | 70             | 78         | 85             | μe<br>% |

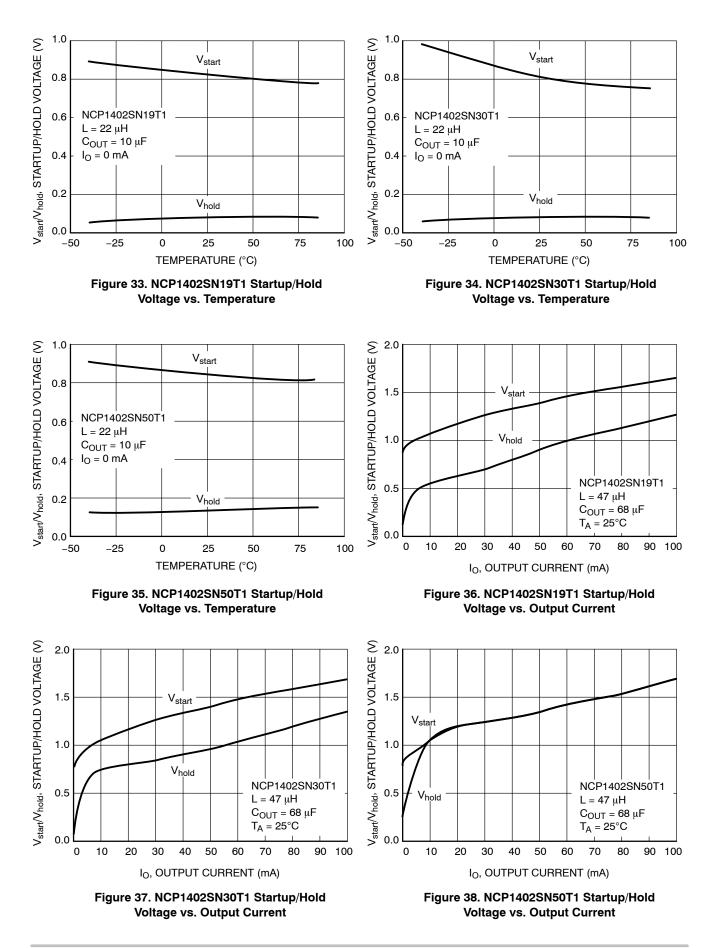

| Minimum Startup Voltage (I <sub>O</sub> = 0 mA)                                                                                  | V <sub>start</sub>    | -              | 0.8        | 0.95           | V       |

|                                                                                                                                  |                       |                |            |                |         |

| Minimum Startup Voltage Temperature Coefficient ( $T_A = -40^{\circ}C$ to 85°C)                                                  | ΔV <sub>start</sub>   | -              | -1.6       | -              | mV/°C   |

| Minimum Operation Hold Voltage (I <sub>O</sub> = 0 mA)                                                                           | V <sub>hold</sub>     | 0.3            | -          | -              | V       |

| Soft-Start Time (V <sub>OUT</sub> > 0.8 V)                                                                                       | t <sub>SS</sub>       | 0.3            | 2.0        | -              | ms      |

| LX (PIN 5)                                                                                                                       | 1                     |                |            |                |         |

| Internal Switching N-Channel FET Drain Voltage                                                                                   | $V_{LX}$              | -              | -          | 6.0            | V       |

| LX Pin On-State Sink Current (V <sub>LX</sub> = 0.4 V)                                                                           | I <sub>LX</sub>       |                |            |                | mA      |

| Device Suffix:<br>19T1                                                                                                           |                       | 110            | 145        |                |         |

| 27T1                                                                                                                             |                       | 130            | 143        | _              |         |

| 30T1                                                                                                                             |                       | 130            | 190        | -              |         |

| 33T1                                                                                                                             |                       | 130            | 200        | -              |         |

| 40T1                                                                                                                             |                       | 130            | 210        | -              |         |

| 50T1                                                                                                                             |                       | 130            | 215        | -              |         |

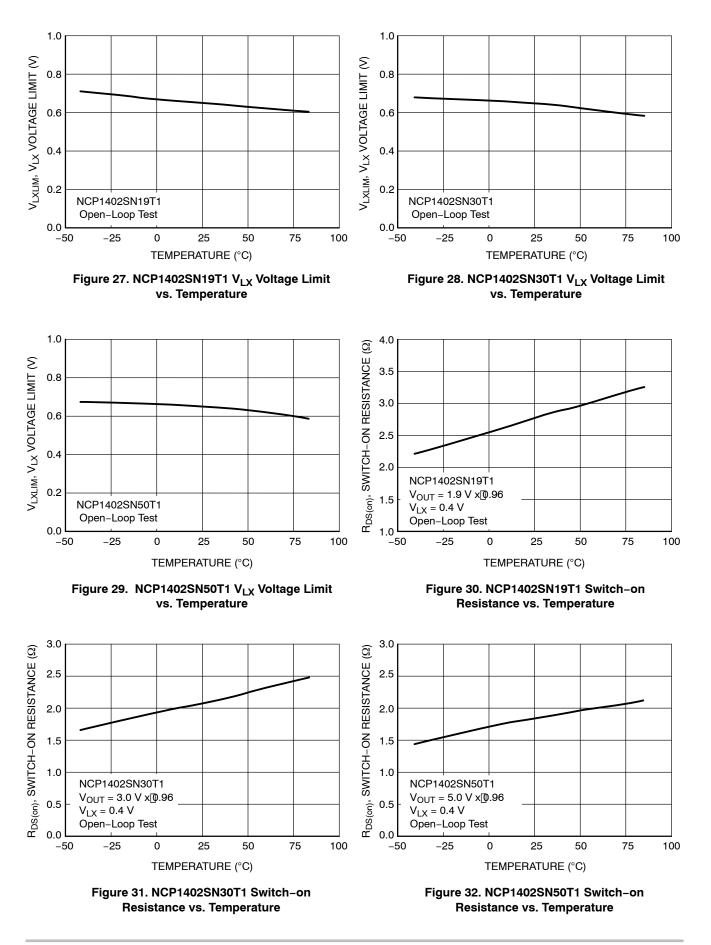

| Voltage Limit                                                                                                                    | V <sub>LXLIM</sub>    | 0.45           | 0.65       | 0.9            | V       |

| Off–State Leakage Current (V <sub>LX</sub> = 6.0 V, $T_A = -40^{\circ}C$ to 85°C)                                                | I <sub>LKG</sub>      | -              | 0.5        | 1.0            | μA      |

| CE (PIN 1)                                                                                                                       |                       |                |            |                |         |

| CE Input Voltage (V <sub>OUT</sub> = V <sub>SET</sub> x 0.96)                                                                    |                       |                |            |                | V       |

| High State, Device Enabled                                                                                                       | V <sub>CE(high)</sub> | 0.9            | -          | -              |         |

| Low State, Device Disabled                                                                                                       | V <sub>CE(low)</sub>  | -              | -          | 0.3            |         |

| CE Input Current (Note 6)                                                                                                        |                       |                |            |                | μΑ      |

| High State, Device Enabled (V <sub>OUT</sub> = V <sub>CE</sub> = 6.0 V)                                                          | I <sub>CE(high)</sub> | -0.5           | 0          | 0.5            |         |

| Low State, Device Disabled ( $V_{OUT}$ = 6.0 V, $V_{CE}$ = 0 V)                                                                  | I <sub>CE(low)</sub>  | -0.5           | 0.15       | 0.5            |         |

| TOTAL DEVICE                                                                                                                     |                       |                |            |                |         |

| Output Voltage                                                                                                                   | V <sub>OUT</sub>      |                |            |                | V       |

| Device Suffix:                                                                                                                   |                       |                |            |                |         |

| 19T1                                                                                                                             |                       | 1.853          | 1.9        | 1.948          |         |

| 27T1                                                                                                                             |                       | 2.632          | 2.7        | 2.768          |         |

| 30T1                                                                                                                             |                       | 2.925          | 3.0        | 3.075          |         |

| 33T1<br>40T1                                                                                                                     |                       | 3.218<br>3.900 | 3.3<br>4.0 | 3.383<br>4.100 |         |

| 50T1                                                                                                                             |                       | 3.900<br>4.875 | 4.0<br>5.0 | 5.125          |         |

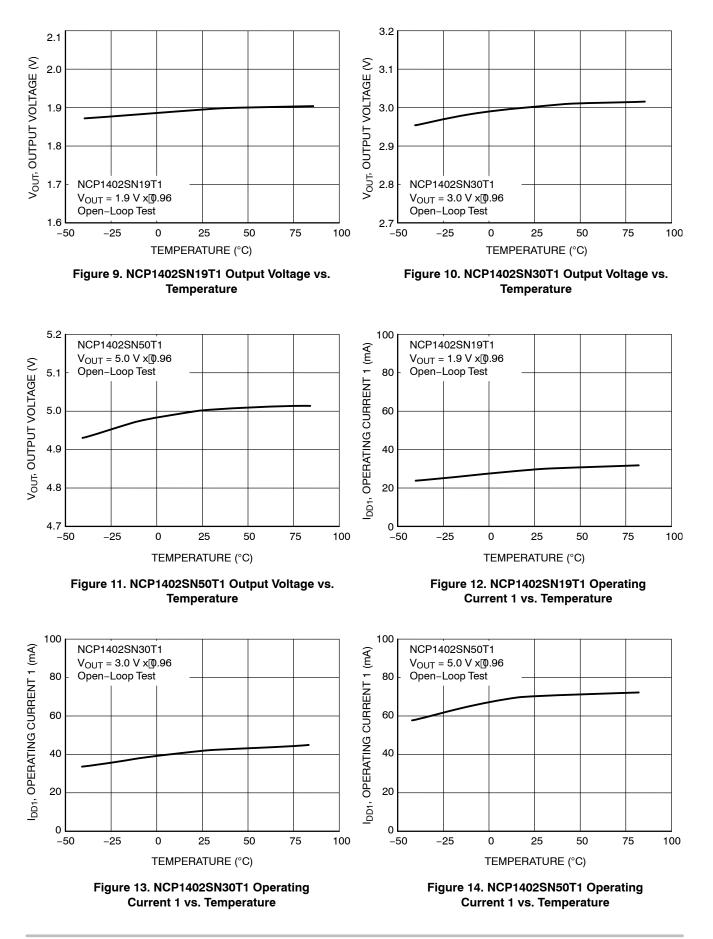

| Output Voltage Temperature Coefficient ( $T_A = -40^{\circ}C$ to +85°C)                                                          | ΔV <sub>OUT</sub>     | 4.070          | 0.0        | 0.120          | ppm/°C  |

| Device Suffix:                                                                                                                   | 2001                  |                |            |                | ppin, O |

| 19T1                                                                                                                             |                       | -              | 150        | -              |         |

| 27T1                                                                                                                             |                       | -              | 150        | -              |         |

| 30T1                                                                                                                             |                       | -              | 150        | -              |         |

| 33T1                                                                                                                             |                       | -              | 150        | -              |         |

| 40T1                                                                                                                             |                       | -              | 150        | -              |         |

| 50T1                                                                                                                             |                       | -              | 150        | -              |         |

| Operating Current 2 ( $V_{OUT}$ = $V_{CE}$ = $V_{SET}$ +0.5 V, Note 5)                                                           | I <sub>DD2</sub>      | -              | 13         | 15             | μΑ      |

| Off–State Current (V <sub>OUT</sub> = 5.0 V, V <sub>CE</sub> = 0 V, T <sub>A</sub> = $-40^{\circ}$ C to $+85^{\circ}$ C, Note 6) | I <sub>OFF</sub>      | -              | 0.6        | 1.0            | μΑ      |

| Operating Current 1 (V <sub>OUT</sub> = V <sub>CE</sub> = V <sub>SET</sub> x 0.96)<br>Device Suffix:                             | I <sub>DD1</sub>      |                |            |                | μΑ      |

| 19T1                                                                                                                             |                       | _              | 30         | 50             |         |

| 27T1                                                                                                                             |                       | _              | 39         | 60             |         |

| 30T1                                                                                                                             |                       | -              | 42         | 60             |         |

| 33T1                                                                                                                             |                       | -              | 45         | 60             |         |

| 40T1                                                                                                                             |                       | -              | 55         | 100            |         |

| 50T1                                                                                                                             | 1                     | 1              | 70         | 100            | 1       |

V<sub>SET</sub> means setting of output voltage.

CE pin is integrated with an internal 10 MΩ pullup resistor.

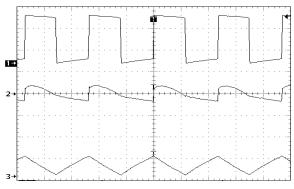

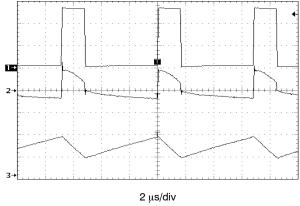

5 μs/div

$V_{OUT}$  = 1.9 V,  $V_{in}$  = 1.2 V,  $I_O$  = 30 mA, L = 47  $\mu H,~C_{OUT}$  = 68  $\mu F$  1.  $V_{LX},~1.0$  V/div

- 2. V<sub>OUT</sub>, 20 mV/div, AC coupled

- 3. I<sub>L</sub>, 100 mA/div

Figure 39. NCP1402SN19T1 Operating Waveforms (Medium Load)

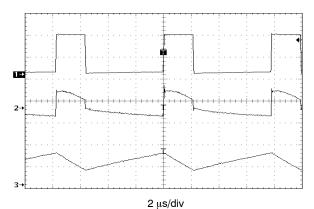

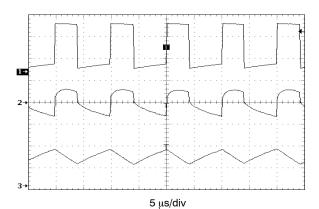

$V_{OUT}$  = 3.0 V,  $V_{in}$  = 1.2 V,  $I_O$  = 30 mA, L = 47  $\mu H,~C_{OUT}$  = 68  $\mu F$  1.  $V_{LX},~$  2.0 V/div

- 2. V<sub>OUT</sub>, 20 mV/div, AC coupled

- 3. I<sub>L</sub>, 100 mA/div

$V_{OUT}$  = 5.0 V,  $V_{in}$  = 1.5 V,  $I_O$  = 30 mA, L = 47  $\mu H,\,C_{OUT}$  = 68  $\mu F$

- 1. V<sub>LX</sub>, 2.0 V/div

- 2. V<sub>OUT</sub>, 20 mV/div, AC coupled

- 3. I<sub>L</sub>, 100 mA/div

#### Figure 43. NCP1402SN50T1 Operating Waveforms (Medium Load)

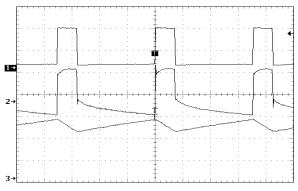

$V_{OUT}$  = 1.9 V,  $V_{in}$  = 1.2 V,  $I_O$  = 70 mA, L = 47  $\mu H,~C_{OUT}$  = 68  $\mu F$

- 1.  $V_{LX}$ , 1.0 V/div

- 2. V<sub>OUT</sub>, 20 mV/div, AC coupled

- 3. I<sub>L</sub>, 100 mA/div

#### Figure 40. NCP1402SN19T1 Operating Waveforms (Heavy Load)

2 μs/div

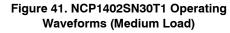

$V_{OUT}$  = 3.0 V,  $V_{in}$  = 1.2 V,  $I_O$  = 70 mA, L = 47  $\mu H,$   $C_{OUT}$  = 68  $\mu F$  1.  $V_{LX},$  2.0 V/div

2. V<sub>OUT</sub>, 20 mV/div, AC coupled

3. I<sub>L</sub>, 100 mA/div

## Figure 42. NCP1402SN30T1 Operating Waveforms (Heavy Load)

#### 2 μs/div

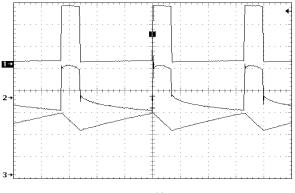

$V_{OUT}$  = 5.0 V,  $V_{in}$  = 1.5 V,  $I_O$  = 60 mA, L = 47  $\mu H,~C_{OUT}$  = 68  $\mu F$

- 1. V<sub>LX</sub>, 2.0 V/div

- 2.  $V_{OUT}$ , 20 mV/div, AC coupled

- 3. IL, 100 mA/div

## Figure 44. NCP1402SN50T1 Operating Waveforms (Heavy Load)

# DETAILED OPERATING DESCRIPTION

#### Operation

The NCP1402 series are monolithic power switching regulators optimized for applications where power drain must be minimized. These devices operate as variable frequency, voltage mode boost regulators and designed to operate in continuous conduction mode. Potential applications include low powered consumer products and battery powered portable products.

The NCP1402 series are low noise variable frequency voltage–mode DC–DC converters, and consist of Soft–Start circuit, feedback resistor, reference voltage, oscillator, PFM comparator, PFM control circuit, current limit circuit and power switch. Due to the on–chip feedback resistor network, the system designer can get the regulated output voltage from 1.8 V to 5 V with a small number of external components. The operating current is typically 30  $\mu$ A (V<sub>OUT</sub> = 1.9 V), and can be further reduced to about 0.6  $\mu$ A when the chip is disabled (V<sub>CE</sub> < 0.3 V).

The NCP1402 operation can be best understood by examining the block diagram in Figure 2. PFM comparator monitors the output voltage via the feedback resistor. When the feedback voltage is higher than the reference voltage, the power switch is turned off. As the feedback voltage is lower than reference voltage and the power switch has been off for at least a period of minimum off-time decided by PFM oscillator, the power switch is then cycled on for a period of on-time also decided by PFM oscillator, or until current limit signal is asserted. When the power switch is on, current ramps up in the inductor, storing energy in the magnetic field. When the power switch is off, the energy in the magnetic field is transferred to output filter capacitor and the load. The output filter capacitor stores the charge while the inductor current is high, then holds up the output voltage until next switching cycle.

#### Soft-Start

There is a Soft–Start circuit in NCP1402. When power is applied to the device, the Soft–Start circuit pumps up the output voltage to approximately 1.5 V at a fixed duty cycle, the level at which the converter can operate normally. What is more, the startup capability with heavy loads is also improved.

## Regulated Converter Voltage (VOUT)

The V<sub>OUT</sub> is set by an internal feedback resistor network. This is trimmed to a selected voltage from 1.8 to 5.0 V range in 100 mV steps with an accuracy of  $\pm 2.5\%$ .

#### **Current Limit**

The NCP1402 series utilizes cycle–by–cycle current limiting as a means of protecting the output switch MOSFET from overstress and preventing the small value inductor from saturation. Current limiting is implemented by monitoring the output MOSFET current build–up during conduction, and upon sensing an overcurrent conduction immediately turning off the switch for the duration of the oscillator cycle.

The voltage across the output MOSFET is monitored and compared against a reference by the VLX limiter. When the threshold is reached, a signal is sent to the PFM controller block to terminate the power switch conduction. The current limit threshold is typically set at 350 mA.

#### Enable / Disable Operation

The NCP1402 series offer IC shut-down mode by chip enable pin (CE pin) to reduce current consumption. An internal pullup resistor tied the CE pin to OUT pin by default i.e. user can float the pin CE for permanent "On". When voltage at pin CE is equal or greater than 0.9 V, the chip will be enabled, which means the regulator is in normal operation. When voltage at pin CE is less than 0.3 V, the chip is disabled, which means IC is shutdown.

Important: DO NOT apply a voltage between 0.3 V and 0.9 V to pin CE as this is the CE pin's hyteresis voltage range. Clearly defined output states can only be obtained by applying voltage out of this range.

## **APPLICATIONS CIRCUIT INFORMATION**

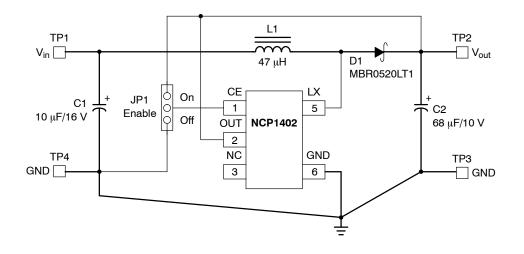

Figure 59. Typical Application Circuit

#### Step-up Converter Design Equations

NCP1402 step-up DC-DC converter designed to operate in continuous conduction mode can be defined by:

| Calculation         | Equation                                                                  |

|---------------------|---------------------------------------------------------------------------|

| L                   | $\leq M\left(\frac{V_{in}^2}{V_{OUT} I_{Omax}}\right)$                    |

| I <sub>PK</sub>     | $\frac{(V_{in} - V_s)t_{on}}{L} + I_{min}$                                |

| I <sub>min</sub>    | $\frac{(t_{on} + t_{off})I_O}{t_{off}} - \frac{(V_{in} - V_S)t_{on}}{2L}$ |

| t <sub>off</sub>    | $\frac{(V_{in} - V_s)t_{on}}{(V_{OUT} + V_F - V_{in})}$                   |

| ΔQ                  | (IL - IO)t <sub>off</sub>                                                 |

| V <sub>ripple</sub> | $\approx \frac{\Delta Q}{C_{OUT}} + (I_{L} - I_{O})ESR$                   |

\*NOTES:

| NOTES               | э. |                                                                               |

|---------------------|----|-------------------------------------------------------------------------------|

| IPK                 | -  | Peak inductor current                                                         |

| I <sub>min</sub>    | -  | Minimum inductor current                                                      |

| l <sub>o</sub>      | -  | Desired dc output current                                                     |

|                     |    | Desired maximum dc output current                                             |

|                     |    | Average inductor current                                                      |

| V <sub>in</sub>     | -  | Nominal operating dc input voltage                                            |

| VOUT                | -  | Desired dc output voltage                                                     |

|                     |    | Diode forward voltage                                                         |

| Vs                  | -  | Saturation voltage of the internal FET switch                                 |

| ΔQ                  | _  | Charge stores in the COUT during charging up                                  |

| V <sub>ripple</sub> | _  | Output ripple voltage                                                         |

| ESR                 | _  | Output ripple voltage<br>Equivalent series resistance of the output capacitor |

|                     |    | An empirical factor, when $V_{OUT} \ge 3.0 \text{ V}$ ,                       |

|                     |    | $M = 8 \times 10^{-6}$ , otherwise $M = 5.3 \times 10^{-6}$ .                 |

|                     |    |                                                                               |

#### **EXTERNAL COMPONENT SELECTION**

#### Inductor

The NCP1402 is designed to work well with a 47  $\mu$ H inductor in most applications. 47  $\mu$ H is a sufficiently low value to allow the use of a small surface mount coil, but large

enough to maintain low ripple. Low inductance values supply higher output current, but also increase the ripple and reduce efficiency. Note that values below 27  $\mu$ H is not recommended due to NCP1402 switch limitations. Higher inductor values reduce ripple and improve efficiency, but also limit output current.

The inductor should have small DCR, usually less than 1  $\Omega$  to minimize loss. It is necessary to choose an inductor with saturation current greater than the peak current which the inductor will encounter in the application.

#### Diode

The diode is the main source of loss in DC–DC converters. The most importance parameters which affect their efficiency are the forward voltage drop,  $V_F$ , and the reverse recovery time,  $t_{rr}$ . The forward voltage drop creates a loss just by having a voltage across the device while a current flowing through it. The reverse recovery time generates a loss when the diode is reverse biased, and the current appears to actually flow backwards through the diode due to the minority carriers being swept from the P–N junction. A Schottky diode with the following characteristics is recommended:

Small forward voltage,  $V_F < 0.3 V$

Small reverse leakage current

Fast reverse recovery time/ switching speed

Rated current larger than peak inductor current,

$I_{rated} > I_{PK}$

Reverse voltage larger than output voltage,

V<sub>reverse</sub> > V<sub>OUT</sub>

#### Input Capacitor

The input capacitor can stabilize the input voltage and minimize peak current ripple from the source. The value of the capacitor depends on the impedance of the input source used. Small Equivalent Series Resistance (ESR) Tantalum or ceramic capacitor with value of 10  $\mu$ F should be suitable.

## **Output Capacitor**

The output capacitor is used for sustaining the output voltage when the internal MOSFET is switched on and smoothing the ripple voltage. Low ESR capacitor should be used to reduce output ripple voltage. In general, a 47 uF to 68 uF low ESR (0.15  $\Omega$  to 0.30  $\Omega$ ) Tantalum capacitor should be appropriate. For applications where space is a critical factor, two parallel 22 uF low profile SMD ceramic capacitors can be used.

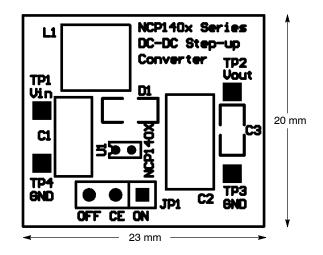

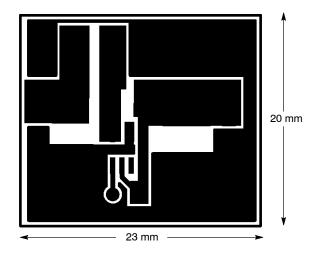

An evaluation board of NCP1402 has been made in the size of 23 mm x 20 mm only, as shown in Figures 60 and 61. Please contact your ON Semiconductor representative for availability. The evaluation board schematic diagram, the artwork and the silkscreen of the surface mount PCB are shown below:

Figure 60. NCP1402 PFM Step-Up DC-DC Converter Evaluation Board Silkscreen

Figure 61. NCP1402 PFM Step–Up DC–DC Converter Evaluation Board Artwork (Component Side)

## **Components Supplier**

| Parts                | Supplier                 | Part Number    | Description                                      | Phone           |

|----------------------|--------------------------|----------------|--------------------------------------------------|-----------------|

| Inductor, L1         | Sumida Electric Co. Ltd. | CD54-470L      | Inductor 47 µH / 0.72 A                          | (852)-2880-6688 |

| Schottky Diode, D1   | ON Semiconductor Corp.   | MBR0520LT1     | Schottky Power Rectifier                         | (852)-2689-0088 |

| Output Capacitor, C2 | KEMET Electronics Corp.  | T494D686K010AS | Low ESR Tantalum Capacitor 68 $\mu F$ / 10 V     | (852)-2305-1168 |

| Input Capacitor, C1  | KEMET Electronics Corp.  | T491C106K016AS | Low Profile Tantalum Capacitor 10 $\mu F$ / 16 V | (852)-2305-1168 |

## **PCB Layout Hints**

#### Grounding

One point grounding should be used for the output power return ground, the input power return ground, and the device switch ground to reduce noise as shown in Figure 62, e.g.: C2 GND, C1 GND, and U1 GND are connected at one point in the evaluation board. The input ground and output ground traces must be thick enough for current to flow through and for reducing ground bounce.

#### **Power Signal Traces**

Low resistance conducting paths should be used for the power carrying traces to reduce power loss so as to improve

efficiency (short and thick traces for connecting the inductor L can also reduce stray inductance), e.g.: short and thick traces listed below are used in the evaluation board:

- 1. Trace from TP1 to L1

- 2. Trace from L1 to Lx pin of U1

- 3. Trace from L1 to anode pin of D1

- 4. Trace from cathode pin of D1 to TP2

#### **Output Capacitor**

The output capacitor should be placed close to the output terminals to obtain better smoothing effect on the output ripple.

Figure 62. NCP1402 Evaluation Board Schematic Diagram

## **ORDERING INFORMATION**

| Device         | Output Voltage | Device Marking | Package              | Shipping <sup>†</sup> |

|----------------|----------------|----------------|----------------------|-----------------------|

| NCP1402SN19T1  | 1.9 V          | DAU            | SOT23-5              |                       |

| NCP1402SN19T1G | 1.9 V          | DAU            | SOT23–5<br>(Pb–Free) |                       |

| NCP1402SN27T1  | 2.7 V          | DAE            | SOT23-5              |                       |

| NCP1402SN27T1G | 2.7 V          | DAE            | SOT23–5<br>(Pb–Free) |                       |

| NCP1402SN30T1  | 3.0 V          | DAF            | SOT23-5              |                       |

| NCP1402SN30T1G | 3.0 V          | DAF            | SOT23–5<br>(Pb–Free) |                       |

| NCP1402SN33T1  | 3.3 V          | DAG            | SOT23-5              | 3,000 Units/Reel      |

| NCP1402SN33T1G | 3.3 V          | DAG            | SOT23–5<br>(Pb–Free) |                       |

| NCP1402SN40T1  | 4.0 V          | DCR            | SOT23-5              |                       |

| NCP1402SN40T1G | 4.0 V          | DCR            | SOT23–5<br>(Pb–Free) |                       |

| NCP1402SN50T1  | 5.0 V          | DAH            | SOT23-5              | 1                     |

| NCP1402SN50T1G | 5.0 V          | DAH            | SOT23–5<br>(Pb–Free) |                       |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

NOTE: The ordering information lists five standard output voltage device options. Additional device with output voltage ranging from 1.8 V to 5.0 V in 100 mV increments can be manufactured. Contact your ON Semiconductor representative for availability.

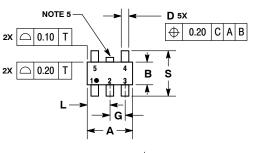

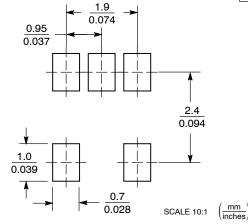

#### PACKAGE DIMENSIONS

**SOT23-5** (TSOP-5, SC59-5) **SN SUFFIX** CASE 483-02 ISSUE J

I

NOTES:

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- CONTROLLING DIMENSION: MILLIMETERS.

MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH THICKNESS. MINIMUM LEAD THICKNESS IS THE MINIMUM THICKNESS OF BASE MATERIAL

- HICKNESS, MINIMUM LEAD THICKNESS IS THE MINIMUM THICKNESS OF BASE MATERIAL.

DIMENSIONS A AND B DO NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE BURRS. MOLD FLASH, PROTRUSIONS, OR GATE BURRS SHALL NOT EXCEED 0.15 PER SIDE. DIMENSION A.

OPTIONAL CONSTRUCTION: AN ADDITIONAL.

- 5. OPTIONAL CONSTRUCTION: AN ADDITIONAL TRIMMED LEAD IS ALLOWED IN THIS LOCATION. TRIMMED LEAD NOT TO EXTEND MORE THAN 0.2 FROM BODY.

|     | MILLIMETERS |      |  |

|-----|-------------|------|--|

| DIM | MIN MAX     |      |  |

| Α   | 3.00        | BSC  |  |

| В   | 1.50        | BSC  |  |

| С   | 0.90        | 1.10 |  |

| D   | 0.25        | 0.50 |  |

| G   | 0.95 BSC    |      |  |

| Н   | 0.01        | 0.10 |  |

| J   | 0.10        | 0.26 |  |

| Κ   | 0.20        | 0.60 |  |

| L   | 1.25 1.55   |      |  |

| М   | 0 °         | 10 ° |  |

| S   | 2.50        | 3.00 |  |

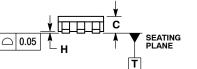

## SOLDERING FOOTPRINT\*

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

The product described herein (NCP1402), may be covered by the following U.S. patents: 6,518,834. There may be other patents pending.

ON Semiconductor and IIIII are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemic.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its product/patent coverage may be accessed at www.onsemic.com/site/pdf/Patent-Marking.pdf. SCILLC particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typical" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights or there. SCILLC products are not designed, intended, or authorized for use as components insystems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding th

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81–3–5817–1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative