## Is Now Part of

# ON Semiconductor®

# To learn more about ON Semiconductor, please visit our website at www.onsemi.com

Please note: As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <a href="www.onsemi.com">www.onsemi.com</a>. Please email any questions regarding the system integration to <a href="mailto:Fairchild\_questions@onsemi.com">Fairchild\_questions@onsemi.com</a>.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees

## FAN6292BMX/FAN6292MX

## Compact Secondary-Side Synchronous Rectifier Control with USB Type-C Control

FAN6292BMX/FAN6292MX are highly integrated, secondary-side power adaptor controllers compatible with Type-C control. Internally adopted synchronous rectifier control helps for less BOM counts as well as easy design.

FAN6292BMX/FAN6292MX are also a source only USB Type-C controllers which are optimized for mobile chargers and power adapters. It supports standard 3 A VBUS current level. N-Channel MOSFET is compatible as a load switch, and helps to reduce BOM cost.

FAN6292BMX/FAN6292MX incorporate adaptive output under-voltage protection to improve system reliability.

#### **Features**

- Type-C Control for Standard 3 A VBUS Current

- N-Channel MOSFET Control as a Type-C Load Switch

- Internal Synchronous Rectifier Control Circuit

- Protections for Safe Operation; Output Under-Voltage-Protection

#### **Typical Applications**

- Battery Chargers for Smart Phones, Feature Phones, and Tablet PCs

- AC-DC Adapters for Portable Devices that Require CV/CC Control

## ON Semiconductor®

www.onsemi.com

TSSOP-8

## **MARKING DIAGRAM**

1st Line:

3<sup>rd</sup> Line:

F: Corporate Logo

Z: Assembly Plant Code

X: Year Code

Y: Week Code

TT: Die Run Code

2<sup>nd</sup> Line: 6292 : IC Part Name for

FAN6292MX

6292B: IC Part Name for

FAN6292BMX

T: Package Type (M=SOIC)

M: Manufacture Flow Code

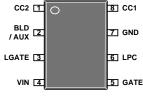

## **PIN CONNECTIONS**

(TOP View)

## **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 13 of this data sheet.

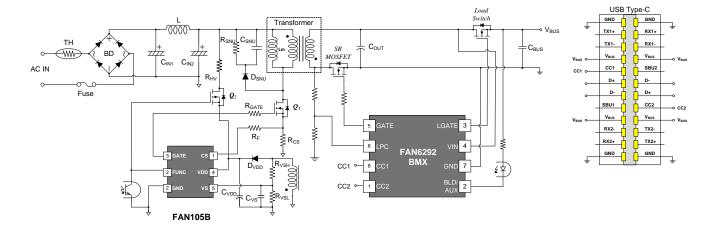

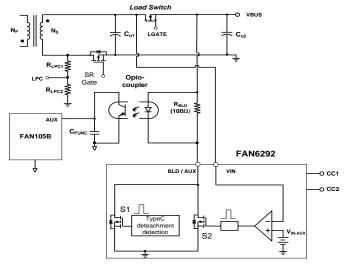

Figure 1 FAN6292BMX Typical Application Schematic

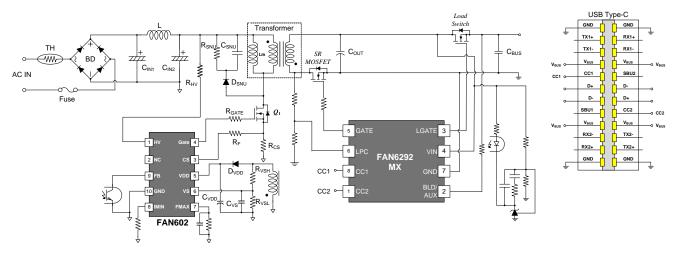

Figure 2 FAN6292MX Typical Application Schematic

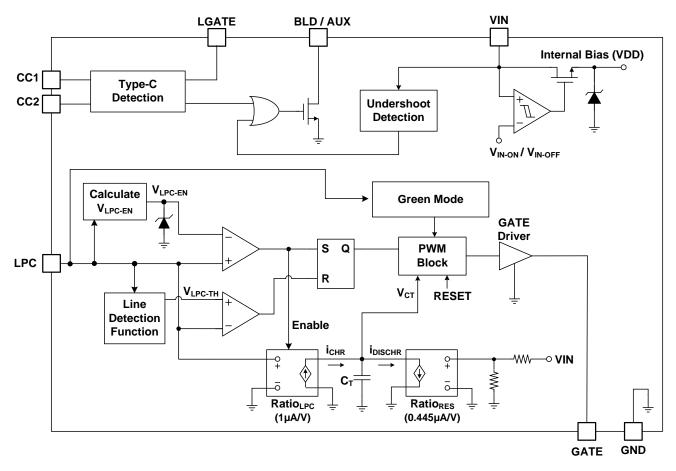

Figure 3 FAN6292BMX/FAN6292MX Function Block Diagram

## PIN FUNCTION DESCRIPTION

| Pin No. | Pin Name     | Description                                                                                                                                                                                                    |

|---------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | CC2          | <b>Configuration Channel 2.</b> This pin is used to detect connections of Type-C cables and connectors. It is tied to the USB Type-C CC2.                                                                      |

| 2       | BLD<br>/ AUX | <b>Bleeder and AUX function.</b> Discharging path of output capacitor when UFP detachment is acknowledged. In addition, information is delivered to primary to enhance output performance.                     |

| 3       | LGATE        | Load Switch Gate. This pin is tied to the gate of the load switch                                                                                                                                              |

| 4       | VIN          | <b>Input Voltage.</b> This pin is tied to the output of the adaptor to monitor its output voltage and supply internal bias. IC operating current, and MOSFET gate drive current are supplied through this pin. |

| 5       | GATE         | Gate Drive Output. Totem-pole output to drive the external SR MOSFET.                                                                                                                                          |

| 6       | LPC          | <b>SR MOSFET Drain Voltage Detection.</b> This pin is used to detect the voltage on the secondary winding during the on time period of the primary MOSFET.                                                     |

| 7       | GND          | Ground.                                                                                                                                                                                                        |

| 8       | CC1          | <b>Configuration Channel 1.</b> This pin is used to detect connections of Type-C cables and connectors. It is tied to the USB Type-C CC1.                                                                      |

## **MAXIMUM RATINGS** (Note 1,2,3)

| Rating                                                 | Symbol               | Value       | Unit |

|--------------------------------------------------------|----------------------|-------------|------|

| VIN Pin Input Voltage                                  | VIN                  | 20          | V    |

| BLD/AUX Pin Input Voltage                              | V <sub>BLD/AUX</sub> | 20          | V    |

| LGATE Pin Input Voltage                                | V <sub>LGATE</sub>   | 20          | V    |

| CC1 Pin Input Voltage                                  | V <sub>CC1</sub>     | -0.3 to 6.0 | V    |

| CC2 Pin Input Voltage                                  | V <sub>CC2</sub>     | -0.3 to 6.0 | V    |

| LPC pin input voltage                                  | VLPC                 | -0.3 to 6.5 | V    |

| GATE pin input voltage                                 | VGATE                | -0.3 to 6.0 | V    |

| Power Dissipation (T <sub>A</sub> =25°C)               | P <sub>D</sub>       | 850         | mW   |

| Operating Junction Temperature                         | TJ                   | -40 to 150  | °C   |

| Storage Temperature Range                              | T <sub>STG</sub>     | -40 to 150  | °C   |

| Lead Temperature, (Soldering,10 Seconds)               | TL                   | 260         | °C   |

| Human Body Model, ANSI/ESDA/JEDEC JS-001-2012 (Note 4) | ESD <sub>HBM</sub>   | 4           | kV   |

| Charged Device Model, JESD22-C101 (Note 4)             | ESD <sub>CDM</sub>   | 1.75        | kV   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

## THERMAL CHARACTERISTICS (Note 5)

| Rating                              | Symbol          | Value | Unit |

|-------------------------------------|-----------------|-------|------|

| Thermal Characteristics,            | _               |       |      |

| Thermal Resistance, Junction-to-Air | $R_{\theta JA}$ | 153   | °C/W |

| Thermal Reference, Junction-to-Top  | $R_{\omega JT}$ | 22    |      |

<sup>5.</sup> T<sub>A</sub>=25°C unless otherwise specified.

#### **RECOMMENDED OPERATING RANGES** (Note 6)

| Rating                    | Symbol               | Min | Max | Unit |

|---------------------------|----------------------|-----|-----|------|

| VIN Pin Input Voltage     | Vin                  | 0   | 6   | V    |

| BLD/AUX Pin Input Voltage | V <sub>BLD/AUX</sub> | 0   | 6   | V    |

| LGATE Pin Input Voltage   | VLGATE               | 0   | 10  | V    |

| CC1 Pin Input Voltage     | V <sub>CC1</sub>     | 0   | 5.8 | V    |

| CC2 Pin Input Voltage     | V <sub>CC2</sub>     | 0   | 5.8 | V    |

| LPC pin input voltage     | VLPC                 | 0   | 5   | V    |

| GATE pin input voltage    | VGATE                | 0   | 5.5 | V    |

<sup>6.</sup> Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

<sup>2.</sup> All voltage values, except differential voltages, are given with respect to the GND pin.

<sup>3.</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device.

<sup>4.</sup> Meets JEDEC standards JS-001-2012 and JESD 22-C101.

| $V_{N}=5 \text{ V I PC}=1.5 \text{ V}$ | I PC width=2 us at T <sub>i</sub> = | :-40~125 °C Func= | :100 kHz_unless ( | otherwise specified |

|----------------------------------------|-------------------------------------|-------------------|-------------------|---------------------|

| Parameter                                                        | Test Conditions                                                              | Symbol                             | Min  | Тур  | Max  | Unit   |

|------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------|------|------|------|--------|

| VIN Section                                                      |                                                                              |                                    |      |      | •    |        |

| Continuous Operating Voltage <sup>(7)</sup>                      |                                                                              | V <sub>IN-OP</sub>                 |      |      | 6    | V      |

| Operating Supply Current                                         | V <sub>IN</sub> =5 V                                                         | I <sub>IN-OP-5</sub> V             |      | 8    |      | mA     |

| Green Mode Operating Supply Current                              | V <sub>IN</sub> =5 V, with SR gate<br>F = 400Hz<br>CC1/CC2 open circuit      | IIN-OP-Green                       | 0.5  | 0.9  | 1.3  | mA     |

| Internal Bias Section                                            |                                                                              |                                    |      |      | •    |        |

| Turn-On Threshold Voltage                                        | V <sub>IN</sub> increases                                                    | V <sub>IN-ON</sub>                 | 3.0  | 3.2  | 3.4  | V      |

| Turn-Off Threshold Voltage                                       | V <sub>IN</sub> decreases                                                    | V <sub>IN-OFF</sub>                | 2.75 | 2.85 | 2.95 | V      |

| Green Mode Section (FAN6292BMX)                                  |                                                                              | <u> </u>                           |      | ı    | ı    |        |

| Green Mode Enable Debounce Time                                  | Non-switching time, when LPC falling                                         | t <sub>Green-EN-</sub><br>Debounce | 54   | 64   | 74   | μs     |

| Number of switching to enter green mode                          | When switching period > T <sub>Green-EN-Debounce</sub>                       | NGreen-EN-<br>Debounce             |      | 1    |      | Cycle  |

| Green Mode Disable Debounce Time                                 | Enable after enter green mode,<br>Non-switching time, when LPC<br>falling    | tGreen-DIS-<br>Debounce            | 54   | 64   | 74   | μs     |

| Green Mode Section (FAN6292MX)                                   |                                                                              |                                    |      |      |      |        |

| Green Mode Enable Debounce Time                                  | Non-switching time, when when LPC falling                                    | tGreen-EN-<br>Debounce             | 0.4  | 0.5  | 0.6  | ms     |

| Green Mode Disable Debounce Time                                 | Enable after enter green mode,<br>Non-switching time, when LPC<br>falling    | tGreen-DIS-<br>Debounce            | 0.2  | 0.3  | 0.4  | ms     |

| Number of consecutive switching to leave green mode              | Independently enable with T <sub>Green-DIS-Debounce</sub> , when LPC falling | NGreen-DIS-<br>Debounce            |      | 256  |      | Cycles |

| Bleeder Section                                                  |                                                                              |                                    |      |      |      |        |

| BLD Pin Sink Current through when bleeding <sup>(7)</sup>        | V <sub>BLD</sub> =5 V                                                        | BLD -Sink                          | 90   |      |      | mA     |

| Maximum Discharging Time when bleeding                           |                                                                              | t <sub>BLD-MAX</sub>               | 275  | 320  | 365  | ms     |

| AUX Section ( FAN6292BMX )                                       |                                                                              |                                    |      |      |      |        |

| Output undershoot detection threshold voltage                    |                                                                              | V <sub>IN-AUX</sub>                | 4.7  | 4.8  | 4.9  | V      |

| Internal debounce time to enable I <sub>AUX</sub> <sup>(7)</sup> | RC filter type                                                               | T <sub>AUX</sub> -                 |      |      | 5    | μS     |

| BLD/AUX pin pull-down time                                       |                                                                              | T <sub>AUX-ON</sub>                | 44   | 64   | 84   | μS     |

| BLD/AUX pin pull down current with V <sub>AUX</sub> =5V          | V <sub>BLD</sub> =5 V, R <sub>BLD</sub> =0 Ω                                 | I <sub>AUX</sub>                   | 3.3  |      | 15   | mA     |

V<sub>IN</sub>=5 V, LPC=1.5 V, LPC width=2 µs at T<sub>J</sub>= -40~125 °C, F<sub>LPC</sub>=100 kHz, unless otherwise specified.

| Parameter                                                            | Test Conditions                                                          | Symbol                  | Min  | Тур  | Max  | Unit |

|----------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------|------|------|------|------|

| Type-C Section                                                       |                                                                          |                         |      |      |      |      |

| Source current on CC1 pin                                            | V <sub>IN</sub> =5 V, V <sub>CC2</sub> =0 V                              | I <sub>P-CC1</sub>      | 304  | 330  | 356  | μA   |

| Source current on CC2 pin                                            | V <sub>IN</sub> =5 V, V <sub>CC1</sub> =0 V                              | I <sub>P-CC2</sub>      | 304  | 330  | 356  | μΑ   |

| Input impedance on CC1 pin                                           |                                                                          | Z <sub>OPEN-CC1</sub>   | 126  |      |      | kΩ   |

| Input impedance on CC2 pin                                           |                                                                          | Zopen-cc2               | 126  |      |      | kΩ   |

| Ra impedance detection threshold on CC1 pin                          | V <sub>IN</sub> =5 V, V <sub>CC2</sub> =0 V, Decreasing V <sub>CC</sub>  | C1 VRA-CC1              | 0.75 | 0.80 | 0.85 | V    |

| Ra impedance detection threshold on CC2 pin                          | V <sub>IN</sub> =5 V, V <sub>CC1</sub> =0 V, Decreasing V <sub>CC</sub>  | C2 VRA-CC2              | 0.75 | 0.80 | 0.85 | V    |

| Rd impedance detection threshold on CC1 pin                          | V <sub>IN</sub> =5 V, V <sub>CC2</sub> =0 V, Increasing V <sub>CC</sub>  | VRD-CC1                 | 2.45 | 2.60 | 2.75 | V    |

| Rd impedance detection threshold on CC2 pin                          | V <sub>IN</sub> =5 V, V <sub>CC1</sub> =0 V, Increasing V <sub>CC2</sub> | VRD-CC2                 | 2.45 | 2.60 | 2.75 | V    |

| UFP attachment debounce time                                         | V <sub>IN</sub> =5 V, V <sub>CC2</sub> =0 V, Increasing V <sub>CC</sub>  | t <sub>CC-Attach-</sub> | 100  | 150  | 200  | ms   |

| UFP detachment debounce time                                         | V <sub>IN</sub> =5 V, V <sub>CC2</sub> =0 V, Decreasing V <sub>CC</sub>  | tCC-Detach-debounce     | 10   | 15   | 20   | ms   |

| After tcc-attach-debounce until V <sub>BUS</sub> =5 V <sup>(7)</sup> | V <sub>IN</sub> =5 V, V <sub>CC2</sub> =0 V, Increasing V <sub>CC</sub>  | tvbus-on                |      |      | 275  | ms   |

| After detaching UFP until V <sub>BUS</sub> =0 V <sup>(7)</sup>       | V <sub>IN</sub> =5 V, V <sub>CC2</sub> =0 V, Decreasing V <sub>CC</sub>  | t <sub>VBUS-OFF</sub>   |      |      | 650  | ms   |

| Gate high voltage                                                    | V <sub>IN</sub> =5 V                                                     | V <sub>NGATE</sub>      | 8    |      | 10   | V    |

| Output Driver Section                                                |                                                                          |                         |      |      |      |      |

| Output Voltage Low                                                   | V <sub>IN</sub> =5 V, I <sub>GATE</sub> =100 mA                          | $V_{OL}$                |      | 0.16 | 0.25 | V    |

| Output Voltage High                                                  | V <sub>IN</sub> =5 V                                                     | Vон                     | 4.5  |      |      | V    |

| Rising Time <sup>(7)</sup>                                           | V <sub>IN</sub> =5 V, C <sub>L</sub> =3300 pF,<br>GATE=1 V ~ 4 V         | t <sub>R</sub>          |      | 20   | 35   | ns   |

| Falling Time <sup>(7)</sup>                                          | V <sub>IN</sub> =5 V, C <sub>L</sub> =3300 pF,<br>GATE=4 V~ 1 V          | tғ                      |      | 9    |      | ns   |

| Propagation Delay to OUT High (LPC trigger)                          | V <sub>IN</sub> =5 V, GATE=1 V                                           | tpd-HIGH-LPC            |      | 44   | 80   | ns   |

| Propagation Delay to OUT Low (LPC trigger) <sup>(7)</sup>            | V <sub>IN</sub> =5 V, GATE=4 V                                           | t <sub>PD-LOW-LPC</sub> |      | 30   |      | ns   |

| Gate inhibit Time <sup>(7)</sup>                                     |                                                                          | tімнівіт                |      | 1.4  |      | μs   |

| Gate start-up disable time                                           | For FAN602 (FAN6292MX)                                                   | tsR-startup-dis         |      | 60   |      | ms   |

| Gate start-up disable time                                           | For FAN105B (FAN6292BMX)                                                 | tSR-startup-dis         | 1.5  | 2    | 2.5  | ms   |

$V_{IN}$ =5 V, LPC=1.5 V, LPC width=2  $\mu s$  at  $T_J$ = -40~125 °C,  $F_{LPC}$ =100 kHz, unless otherwise specified.

| $V_{IN}$ =5 V, LPC=1.5 V, LPC width=2 $\mu$ s at $T_J$ = -40<br><b>Parameter</b> | Test Conditions                                                            | Symbol                       | Min                   | Тур   | Max                | Unit   |

|----------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------|-----------------------|-------|--------------------|--------|

| Internal RES section                                                             |                                                                            |                              |                       |       |                    |        |

| Internal RES ratio                                                               | V <sub>IN</sub> =5 V, Turn-ratio=15~17                                     | K <sub>RES</sub>             | 0.196                 | 0.200 | 0.204              | V/V    |

| VIN Dropping Protection Ratio with Two Cycle                                     | LPC width=5 μs<br>VIN=5 V to 3.5 V                                         | K <sub>VIN-DROP</sub>        | 70                    |       | 90                 | %      |

| Debounce time for disable SR when VIN dropping protection                        |                                                                            | t <sub>SR_OFF</sub>          | 3.5                   | 5.5   | 7.5                | ms     |

| Debounce time for noise immunity on VIN <sup>(7)</sup>                           |                                                                            | tVIN-Debounce                | 1                     | 2     | 3                  | μs     |

| LPC Section                                                                      |                                                                            |                              |                       |       |                    |        |

| Linear Operation Range of LPC Pin Voltage <sup>(7)</sup>                         | V <sub>IN</sub> -OFF < V <sub>IN</sub> ≤ 5V                                | $V_{LPC}$                    | 0.4                   |       | V <sub>IN</sub> -1 | ٧      |

| LPC Sink Current                                                                 | V <sub>LPC</sub> =1V                                                       | I <sub>LPC-SINK</sub>        |                       | 100   |                    | nA     |

| SR Enabled Threshold Voltage @High Line                                          |                                                                            | V <sub>LPC-HIGH-H</sub>      | 1.418                 | 1.500 | 1.583              | ٧      |

| Threshold Voltage on LPC Rising Edge @High Line <sup>(7)</sup>                   | VLPC-HIGH-H *0.875 = VLPC-TH-H                                             | V <sub>LPC</sub> -TH-H       | 1.205                 | 1.313 | 1.424              | >      |

| SR Enabled Threshold Voltage @ Low Line                                          | V <sub>LPC-HIGH-L-5V</sub> = V <sub>LPC-TH-L-5V</sub> / 0.875              | V <sub>LPC-HIGH-L-5</sub> V  | 0.703                 | 0.743 | 0.783              | V      |

| Threshold Voltage on LPC Rising Edge @ Low Line <sup>(7)</sup>                   | Spec.=0.4+0.05*VIN<br>VIN = 5V                                             | V <sub>LPC-TH-L-5</sub> V    | 0.63                  | 0.650 | 0.67               | V      |

| Falling Edge Threshold Voltage to trigger SR (7)                                 |                                                                            | V <sub>LPC-TH-TRIG</sub>     |                       | 70    |                    | mV     |

| Low to High Line Threshold Voltage on LPC pin                                    | VIN = 5V, Spec.=(0.8+0.03*VIN)*2                                           | V <sub>LINE-H-5</sub> V      | 1.81                  | 1.90  | 1.99               | ٧      |

| High to Low Line Threshold Voltage on LPC pin                                    | VIN = 5V,<br>Spec.=(0.75+0.03*VIN)*2                                       | V <sub>LINE-L-5V</sub>       | 1.72                  | 1.80  | 1.88               | V      |

| Line Change Threshold Hysteresis                                                 | V <sub>LINE-HYS-5V</sub> = V <sub>LINE-H-5V</sub> - V <sub>LINE-L-5V</sub> | V <sub>LINE-HYS-5V</sub>     |                       | 0.1   |                    | V      |

| Higher Clamp Voltage                                                             |                                                                            | VLPC-CLAMP-H                 | 5.4                   | 6.2   | 7.0                | ٧      |

| LPC Threshold Voltage to Disable SR<br>Gate Switching                            | V <sub>IN</sub> = 5V<br>LPC=3V↑                                            | V <sub>LPC-DIS</sub>         | V <sub>IN</sub> - 0.6 |       |                    | V      |

| Enable VLPC-DIS                                                                  | Increasing V <sub>IN</sub>                                                 | V <sub>EN-LPC-DIS</sub>      | 4.25                  | 4.4   | 4.45               | V      |

| Disable VLPC-DIS                                                                 | Decreasing V <sub>IN</sub>                                                 | V <sub>DIS-LPC-DIS</sub>     | 4.1                   | 4.2   | 4.3                | V      |

| Line Change Debounce from Low Line to High Line <sup>(7)</sup>                   | Counts for<br>LPC falling < V <sub>LPC-TH-L-5V</sub>                       | t <sub>LPC-LH-debounce</sub> |                       | 7     |                    | cycles |

| Line Change Debounce from High Line to Low Line <sup>(7)</sup>                   | _                                                                          | tLPC-HL-debounce             |                       | 15    |                    | μs     |

$V_{\text{IN}}\!\!=\!5~\text{V, LPC}\!=\!1.5~\text{V, LPC width}\!=\!2~\mu\text{s at T}_{\text{J}}\!\!=\!-40\sim\!125~^{\circ}\text{C, F}_{\text{LPC}}\!\!=\!100~\text{kHz, unless otherwise specified}$

| Parameter                                                               | Test Conditions                                             | Symbol                     | Min  | Тур   | Max  | Unit |

|-------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------|------|-------|------|------|

| Internal Timing Section                                                 |                                                             |                            |      |       |      |      |

| LPC Transfer Ratio to I <sub>LPC</sub> <sup>(7)</sup>                   |                                                             | Ratio <sub>LPC</sub>       |      | 1     |      | μA/V |

| V <sub>RES</sub> Transfer Ratio to I <sub>RES</sub> <sup>(7)</sup>      |                                                             | Ratiores                   |      | 0.445 |      | μA/V |

| Ratio between V <sub>LPC</sub> & V <sub>RES</sub>                       | VIN=5V, F <sub>LPC</sub> =50 kHz,<br>K <sub>RES</sub> =0.20 | Ratio <sub>LPC-RES</sub>   | 3.15 | 3.37  | 3.59 |      |

| Minimum LPC Time to Enable the SR Gate @ High Line                      | V <sub>LPC</sub> =3V                                        | tlpc-en-h                  | 80   | 180   | 280  | ns   |

| Minimum LPC Time to Enable the SR Gate @ Low Line                       | V <sub>LPC</sub> =1.5V                                      | t <sub>LPC-EN-L</sub>      | 500  | 600   | 700  | ns   |

| Minimum Gate Width                                                      | FAN6292BMX                                                  | t <sub>MIN</sub>           | 1.9  | 2.2   | 2.5  | μs   |

| Max SR On Time <sup>(7)</sup>                                           |                                                             | ton-max                    | 20   |       |      | μs   |

| $t_{on\text{-SR}}(n+1)$ - $t_{on\text{-SR}}(n) < t_{gate\text{-limit}}$ |                                                             | t <sub>gate-limit</sub>    | 350  | 500   | 650  | ns   |

| Maximum Gate Limit On-time)(7)                                          |                                                             | tgate-limit-max            |      | 5     |      | μs   |

| Forced internal CT reset time <sup>(7)</sup>                            |                                                             | tct-reset                  |      | 10    |      | ns   |

| Reverse Current Mode Section                                            |                                                             |                            |      |       |      |      |

| Reverse current mode entry debounce time                                | VIN=5 V, VLPC=0 V                                           | T <sub>reverse-</sub>      | 350  | 500   | 650  | ms   |

| Operating current during reverse current mode                           | V <sub>IN</sub> =5 V, V <sub>LPC</sub> =0 V                 | I <sub>OP.reverse</sub>    |      |       | 1.7  | mA   |

| Source current on CC1 pin during reverse current mode <sup>(7)</sup>    | V <sub>IN</sub> =5 V, V <sub>LPC</sub> =0 V                 | IP-CC1.reverse             |      |       | 10   | μА   |

| Source current on CC2 pin during reverse current mode <sup>(7)</sup>    | V <sub>IN</sub> =5 V, V <sub>LPC</sub> =0 V                 | I <sub>P-CC2.reverse</sub> |      |       | 10   | μА   |

10

I<sub>BLD.reverse</sub>

uΑ

VIN=5 V, VLPC=0 V

AUX pin current during reverse current mode<sup>(7)</sup>

Guaranteed by Design. Guaranteed at -5° ~ 85°C. 7. 8.

Т Υ C Α L C Н Α R Α C T Ε R I S T C S

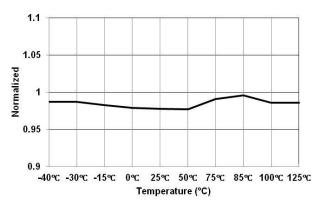

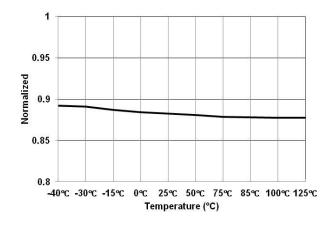

Figure 4 Turn-On Threshold Voltage

(V<sub>IN-ON</sub>) vs. Temperature

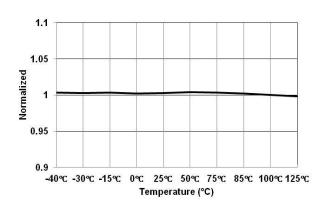

Figure 5 Turn-Off Threshold Voltage (V<sub>IN-OFF</sub>) vs. Temperature

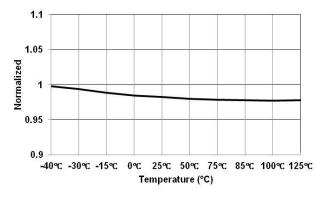

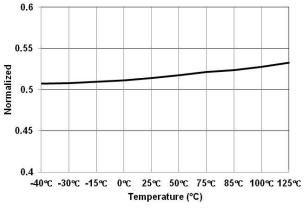

Figure 6 Minimum LPC Time to Enable the SR Gate @ Low-Line  $(t_{LPC-EN-L})$  vs. Temperature

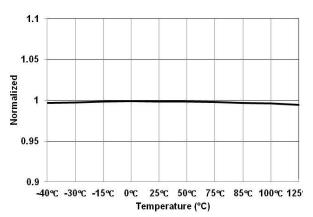

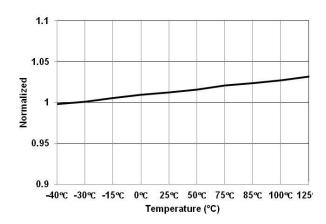

Figure 7 VIN Under-Voltage-Protection Enable  $(V_{IN-AUX})$  vs. Temperature

Figure 8 Minimum LPC Time to Enable the SR Gate @ High-Line ( $t_{\text{LPC-EN-H}}$ ) vs. Temperature

Figure 9 Ratio between  $V_{LPC}$  &  $V_{RES}$  (Ratio  $_{LPC-RES}$ ) vs. Temperature

Т Υ C L C Н Α R Α C T Ε R ı S Τ C S

Figure 10 Source Current on CC1 Pin (I<sub>P-CC1</sub>) vs. Temperature

Figure 12 Operating Current during Reverse Current M o d e ( I O P . r e v e r s e) v s . T e m p e r a t u r e

Figure 11 Source Current on CC2 Pin (Ip.cc2) vs. Temperature

Figure 13 Gate High Voltage (V<sub>NGATE</sub>) vs. Temperature

## **APPLICATIONS INFORMATION**

#### N-channel MOSFET for Load Switch

FAN6292BMX/FAN6292MX implement Type-C block to enable or disable an external load switch. Internally adapted charge pump lets it control N-channel MOSFET as a load switch. It helps system be more cost competitive compared to P-channel MOSFET as a load switch. Since the minimum pumped voltage is  $V_{BUS}+3$  V, it is recommended to use N-channel MOSFET supporting lower gate threshold levels.

#### **Detail of Load Switch Control**

FAN6292BMX/FAN6292MX support output current higher than 1.5 A. In order to meet Type-C specification, 330  $\mu$ A is applied on CC1 pin and CC2 pin. When Rd (5.1 k $\Omega$ ) is attached on either CC1 or CC2, load switch is turned-on after 150 ms debounce time. As soon as load switch is enabled, BC1.2 counter is enabled. To acknowledge detachment, it needs 15 ms (typ.) debounce time. When load switch is turned-off, bleeder is also enabled at the same time.

#### **Green Mode Operation (for FAN6292BMX)**

In order to reduce power consumption at light-load conditions with FAN105B system, FAN6292BMX in green mode will disable LPC internal detection block but SR contiously works at mini on time for FAN105B which is a pure primary side controller to normally regulate output voltage. When  $V_{LPC}$  is smaller than  $V_{LPC-HIGH-L-5V}$  and maintains duration longer than  $t_{Green-EN-Debounce}$ , FAN6292MX enters green mode where current can be reduced to 0.9 mA (typ.). It leaves green mode when  $V_{LPC}$  is larger than  $V_{LPC-HIGH-L-5V}$  and maintains duration shorter than  $t_{Green-DIS-Debounce}$ .

#### **Green Mode Operation(for FAN6292MX)**

In order to reduce power consumption at light-load conditions with FAN602 system, FAN6292MX enters the green mode where some internal blocks are disabled such as Synchronous Rectifier control block. Therefore, the operating current can be largely reduced. It enters Green Mode when  $V_{LPC}$  is smaller than  $V_{LPC\text{-HIGH-L-5V}}$  and maintains duration longer than  $t_{Green\text{-}EN\text{-}Debounce}$ . It leaves green mode when  $V_{LPC}$  is larger than  $V_{LPC\text{-}HIGH\text{-}L\text{-}5V}$  and maintains duration shorter than  $t_{Green\text{-}DIS\text{-}Debounce}$ .

## **Bleeder Function**

When the portable device is detached, BUS voltage should be discharged to zero within a short time to meet TypeC specification. FAN6292BMX/ FAN6292MX support bleeding function by turning on S1 for  $T_{BLD\text{-}max}$  as shown in Figure 14. The amount of bleeding current through BLD/AUX pin can be controlled by the external resistor  $R_{BLD}$  shown in (1).

$$I_{BLD-RType} = \frac{V_{O\_MAX}}{R_{BLD} + R_{Internal}} \tag{1}$$

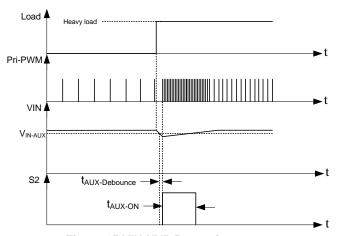

#### VIN-UVP Protection(for FAN6292BMX)

Since pure primary side controller detects and regulates output voltage only when switching, it is not easy maintaining output voltage when load suddenly increases from light load where switching frequency is slow to heavy load. Therefore, as Figure 15, FAN6292BMX automatically detects output voltage. When output undershoot is acknowledged via VIN pin, BLD/AUX pin pull-down current via S2 switch to inform undershoot status to primary controller via a photo-coupler. Since the pull-down current is limited through S2, the current will not affect to the amount of output current.

Figure 14 BLD/AUX Function Diagram

**Figure 15 VIN-UVP Protection**

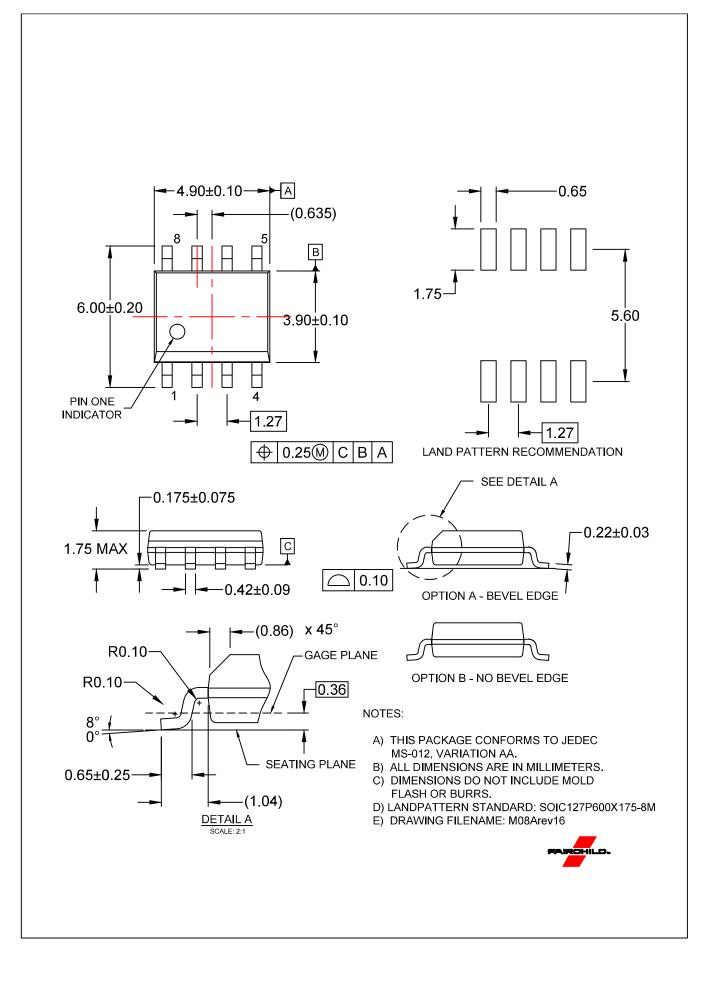

## **ORDERING INFORMATION**

| Part Number | Operating<br>Temperature Range | Package                                                                   | Packing Method |

|-------------|--------------------------------|---------------------------------------------------------------------------|----------------|

| FAN6292BMX  | -40°C to +125°C                | 8-Lead, Small Outline Package (SOIC), JEDEC MS-012, .150-Inch Narrow Body | Tape & Reel    |

| FAN6292MX   | -40°C to +125°C                | 8-Lead, Small Outline Package (SOIC), JEDEC MS-012, .150-Inch Narrow Body | Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D

ON Semiconductor and III) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.

Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

## **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative