## Low Quiescent Current 2 MHz Automotive Synchronous Buck Controller

# NCV891930

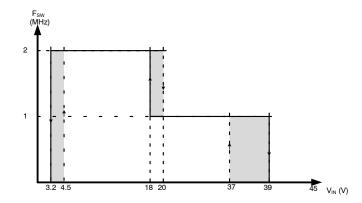

The NCV891930 is a 2 MHz fixed-frequency low quiescent current buck controller with spread spectrum that operates up to 38 V (typical). It may be synchronized to a clock or to separate NCV891930. Peak current mode control is employed for fast transient response and tight regulation over wide input voltage and output load ranges. Feedback compensation is internal to the device, permitting design simplification. The NCV891930 is capable of converting from an automotive input voltage range of 3.5 V (4.5 V during startup) to 18 V at a constant base switching frequency above the sensitive AM band, eliminating the need for costly filters and EMI countermeasures. The switching frequency folds back to 1 MHz for input voltages between 20 V up to 38 V (typical). Under load dump conditions up to 45 V the regulator shuts down. A high voltage bias regulator with automatic switchover to an external 5 V bias supply is used for improved efficiency. Several protection features such as UVLO, current limit, short circuit protection, and thermal shutdown are provided. High switching frequency produces low output voltage ripple even when using small inductor values and an all-ceramic output filter capacitor, forming a space-efficient switching solution.

(410 kHz version offered with NCV881930)

### Features

- 30 µA Operating Current at No Load

- 75 mV Current Limit Sensing

- Capable of 45 V Load Dump

- Board Selectable Fixed Output Voltages With Lockout

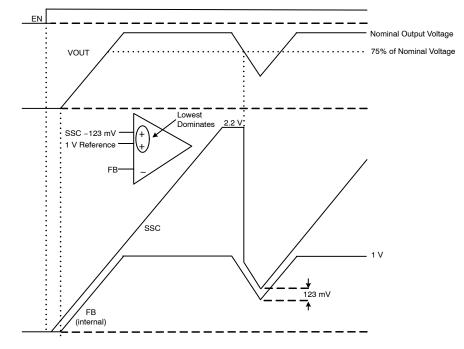

- 2 MHz Operating Frequency

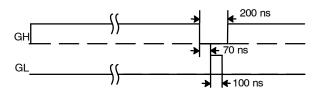

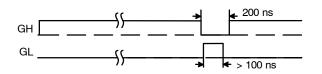

- Adaptive Non–Overlap Circuitry

- Integrated Spread Spectrum

- Logic level Enable Input Can be Tied Directly to Battery

- Short Circuit Protection Pulse Skip

- Battery monitoring for UVLO and Overvoltage Protection

- Thermal Shutdown (TSD)

- Adjustable Soft-Start

- SYNCI, SYNCO, Enable, RSTB, ROSC

- QFN Package with Wettable Flanks (pin edge plating)

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100

- This Device is Pb–Free, Halogen Free/BFR Free and is RoHS Compliant

### **Typical Applications**

- Radio and Infotainment

- Instrumentations & Clusters

- ADAS (safety applications)

- Telematics

## **ON Semiconductor®**

www.onsemi.com

QFNW24 4x4, 0.5P CASE 484AE

Note: With wettable flanks - meets JEDEC MO220

(Note: Microdot may be in either location)

### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 31 of this data sheet.

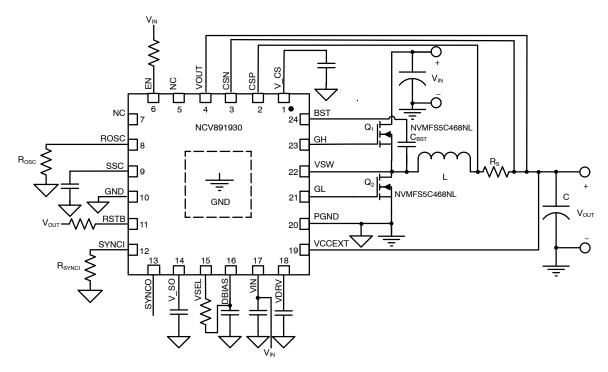

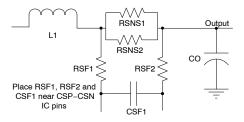

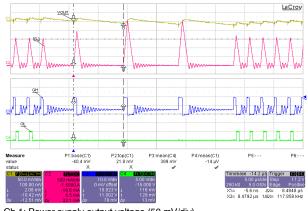

Figure 1. 5 V Application Schematic Example

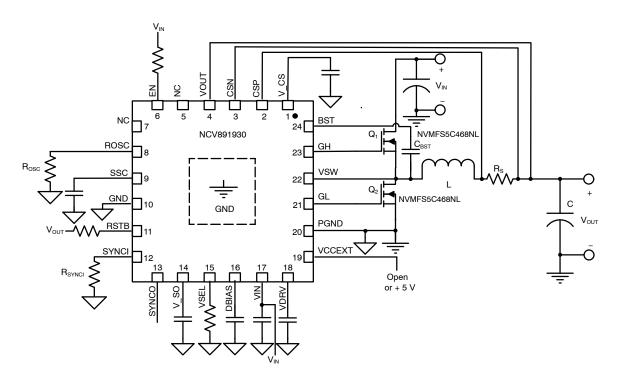

Figure 2. 3.3 V Application Schematic Example

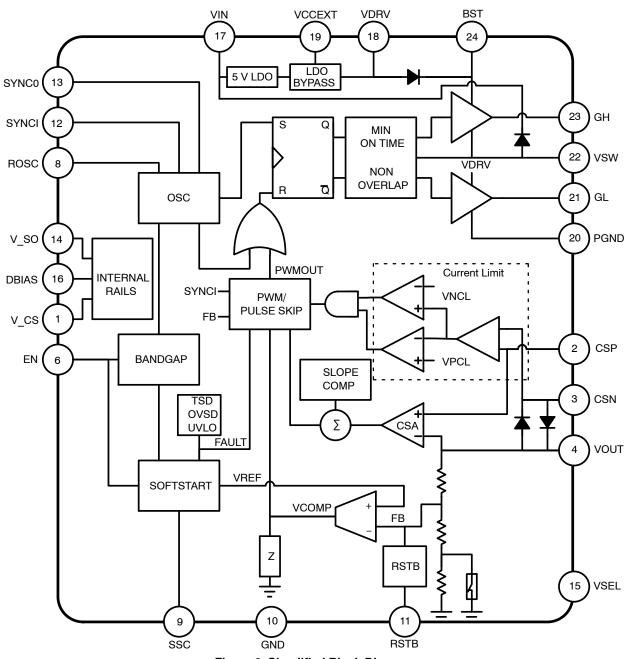

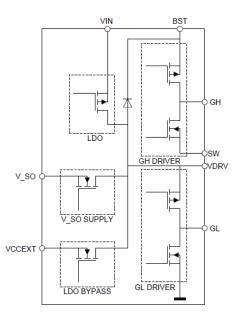

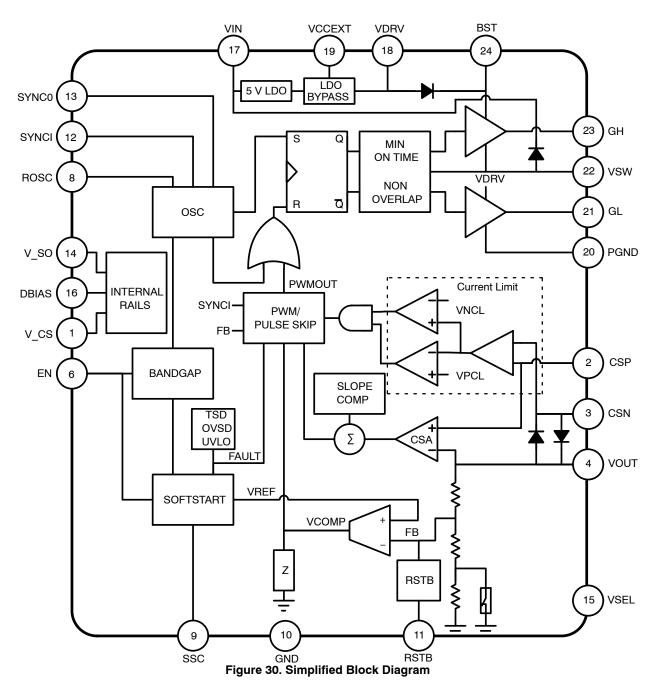

Figure 3. Simplified Block Diagram

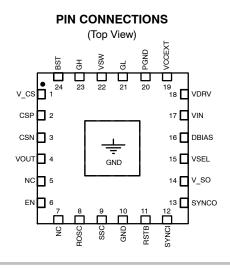

### **PIN FUNCTION DESCRIPTION**

| Pin No.<br>QFN24 | Pin Name | Description                                                                                                                                                                                                                                                                                                                          |

|------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | V_CS     | Supply input for the internal current sense amplifier. Not intended for external use. Application board requires a 0.1 $\mu$ F decoupling capacitor located next to IC referenced to quiet GND                                                                                                                                       |

| 2                | CSP      | Differential current sense amplifier non-inverting input                                                                                                                                                                                                                                                                             |

| 3                | CSN      | Differential current sense amplifier inverting input                                                                                                                                                                                                                                                                                 |

| 4                | VOUT     | SMPS's voltage feedback. Inverting input to the voltage error amplifier. Connect VOUT to nearest point-of-load                                                                                                                                                                                                                       |

| 5                | NC       | No connection (Note 1)                                                                                                                                                                                                                                                                                                               |

| 6                | EN       | Logic level inputs for enabling the controller. May be connected to battery                                                                                                                                                                                                                                                          |

| 7                | NC       | No Connection (Note 1)                                                                                                                                                                                                                                                                                                               |

| 8                | ROSC     | Use a resistor to ground to raise the frequency above default value                                                                                                                                                                                                                                                                  |

| 9                | SSC      | Soft-start current source output. A capacitor to ground sets the soft-start time                                                                                                                                                                                                                                                     |

| 10               | GND      | Signal ground. Ground reference for the internal logic, analog circuitry and the compensators                                                                                                                                                                                                                                        |

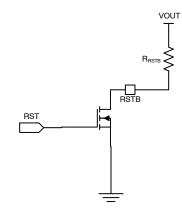

| 11               | RSTB     | Reset with adjustable delay. Goes low when the output is out of regulation                                                                                                                                                                                                                                                           |

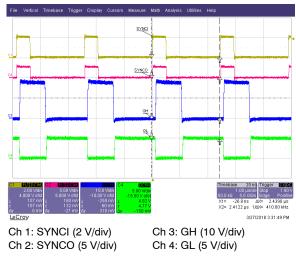

| 12               | SYNCI    | A logic low enables Low $I_Q$ capable operating mode. External synchronization is realized with an external clock. A logic high enables continuous synchronous operating mode (low $I_Q$ mode is disabled). Ground this pin if not used                                                                                              |

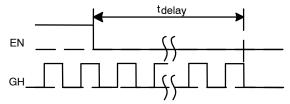

| 13               | SYNCO    | Synchronization output active in synchronous operation mode. Refer to table for activation delay when coming out of low $I_Q$ mode. Connecting to the SYNCI pin of a downstream NCV891930 results in synchronized operation                                                                                                          |

| 14               | V_SO     | Supply voltage for the SYNCO output driver. Not intended for external use. Application board requires a 0.1 $\mu\text{F}$ decoupling capacitor located next to IC referenced to quiet GND                                                                                                                                            |

| 15               | VSEL     | Output programmed to VSEL_LO when connected to ground or when pin is not connected.<br>Output programmed to VSEL_HI when connected to DBIAS via a 10 k $\Omega$ resistor (optional).<br>Voltage setting option will be latched prior to PWM soft-start. Latch will be reset whenever the<br>EN pin is toggled or during a UVLO event |

| 16               | DBIAS    | IC internal power rail. Not intended for external use other than for VSEL. Application board requires a 0.1 $\mu\text{F}$ decoupling capacitor located next to IC referenced to quiet GND                                                                                                                                            |

| 17               | VIN      | Input voltage for controller, may be connected to battery                                                                                                                                                                                                                                                                            |

| 18               | VDRV     | 5 V linear regulator supply for powering NFET gate drive circuitry and supply for bootstrap capacitor                                                                                                                                                                                                                                |

| 19               | VCCEXT   | External 5 V bias supply. Overrides internal high voltage LDO when used. Application board requires a 1 $\mu F$ decoupling capacitor located next to IC referenced to PGND                                                                                                                                                           |

| 20               | PGND     | Power ground. Ground reference for the high-current path including the N-FETs and output capacitor                                                                                                                                                                                                                                   |

| 21               | GL       | Push-pull driver output that swings between VDRV and PGND to drive the gate of an externation low side N-FET of the synchronous buck power supply                                                                                                                                                                                    |

| 22               | VSW      | Terminal of the high side push-pull gate driver connected to the source of the high side N-FE of the synchronous buck power supply                                                                                                                                                                                                   |

| 23               | GH       | Push-pull driver output that swings between SW and BST to drive the gate of an external hig side N-FET of the synchronous buck power supply                                                                                                                                                                                          |

| 24               | BST      | The BST pin is the supply rail for the gate drivers. A 0.1 $\mu$ F capacitor must be connected be-<br>tween this pin and the VSW pin. Bootstrap pin to be connected with an external capacitor for<br>powering the high side NFET gate with SW + (VDRV – 0.5 V) and PGND. Blocking diode is<br>internal to the IC                    |

|                  | 1        |                                                                                                                                                                                                                                                                                                                                      |

1. True no connect. Printed circuit board traces are allowable.

MAXIMUM RATINGS (Voltages with respect to GND unless otherwise indicated)

| Rating                                                                            | Symbol                                    | Value                                            | Unit |

|-----------------------------------------------------------------------------------|-------------------------------------------|--------------------------------------------------|------|

| DC Supply Voltage (Note 2)                                                        | EN, VIN, V_CS                             | –0.3 to 45                                       | V    |

| Pin Voltage $t \le 50$ ns                                                         | VSW                                       | -0.3 to 40<br>-2                                 | V    |

| Pin Voltage                                                                       | GH,BST                                    | -0.3 to 45<br>-0.3 to 7 V with respect to<br>VSW | V    |

| Pin Voltage                                                                       | CSN, CSP, VOUT                            | –0.3 to 10                                       | V    |

| Pin Voltage                                                                       | VDRV, GL,<br>VCCEXT                       | –0.3 to 7                                        | V    |

| Pin Voltage                                                                       | RSTB                                      | –0.3 to 6                                        | V    |

| Pin Voltage                                                                       | DBIAS, ROSC,<br>SSC, SYNCO,<br>V_SO, VSEL | -0.3 to 3.6                                      | V    |

| Operating Junction Temperature                                                    | T <sub>J(max)</sub>                       | -40 to 150                                       | °C   |

| Storage Temperature Range                                                         | T <sub>STG</sub>                          | –65 to 150                                       | °C   |

| ESD Capability, Human Body Model (Note 3)                                         | ESD <sub>HBM</sub>                        | 2                                                | kV   |

| Moisture Sensitivity Level                                                        | MSL                                       | 1                                                | -    |

| Lead Temperature Soldering<br>Reflow (SMD Styles Only), Pb-Free Versions (Note 4) | T <sub>SLD</sub>                          | 260                                              | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

Should not be assumed, damage may occur and reliability may be affected.

Refer to ELECTRICAL CHARACTERISTICS, RECOMMENDED OPERATING RANGES and/or APPLICATION INFORMATION for Safe Operating parameters.

3. This device series incorporates ESD protection and is tested by the following methods:

ESD Human Body Model tested per AEC-Q100-002 (EIA/JESD22-A114).

4. For information, please refer to our Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

### THERMAL CHARACTERISTICS

| Rating                                                                                                                                               | Symbol                  | Value    | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------|------|

| Thermal Characteristics (Note 5)<br>Thermal Resistance, Junction-to-Ambient (Note 6)<br>Thermal Characterization Parameter, Junction-to-Top (Note 6) | R <sub>θJA</sub><br>ΨJT | 50<br>13 | °C/W |

5. Refer to ELECTRICAL CHARACTERISTICS, RECOMMENDED OPERATING RANGES and/or APPLICATION INFORMATION for Safe Operating parameters.

Values based on copper area of 600 mm<sup>2</sup>, 4 layer PCB, 0.062 inch FR-4 board with 2 oz. copper on top/bottom layers and 1 oz. copper on the inside layers in a still air environment with T<sub>A</sub> = 25°C.

**ELECTRICAL CHARACTERISTICS** ( $V_{EN} = V_{BAT} = V_{IN} = 4.5 \text{ V}$  to 37 V,  $V_{BST} = V_{SW} + (V_{DRV} - 0.5V)$ ,  $C_{BST} = 0.1 \mu$ F,  $C_{DRV} = 1 \mu$ F. Min/Max values are valid for the temperature range  $-40^{\circ}$ C <  $T_J$  < 150 °C unless noted otherwise, and are guaranteed by test, design or statistical correlation.

| Parameter                                            | Test Conditions                                                                                                                                                                                                                                                                                                                        | Symbol                                 | Min                            | Тур                          | Max                            | Unit |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--------------------------------|------------------------------|--------------------------------|------|

| VIN_LOW                                              |                                                                                                                                                                                                                                                                                                                                        |                                        |                                |                              |                                |      |

| VIN_low threshold                                    | VIN falling<br>VIN rising                                                                                                                                                                                                                                                                                                              | V <sub>INLF</sub><br>V <sub>INLR</sub> | 7.0<br>7.3                     | 7.31<br>7.65                 | 7.65<br>8.0                    | V    |

| VIN_low hysteresis                                   |                                                                                                                                                                                                                                                                                                                                        | V <sub>INLH</sub>                      | 0.3                            | 0.37                         | 0.45                           | V    |

| Response time                                        |                                                                                                                                                                                                                                                                                                                                        |                                        | -                              | 5.8                          | -                              | μs   |

| VIN FREQUENCY FOLDBACK                               | MONITOR (VIN_HIGH)                                                                                                                                                                                                                                                                                                                     |                                        |                                |                              |                                |      |

| Frequency foldback threshold                         | VIN rising<br>VIN falling                                                                                                                                                                                                                                                                                                              | V <sub>FLR</sub><br>V <sub>FLF</sub>   | 18.4<br>18.0                   |                              | 20<br>19.8                     | V    |

| Frequency foldback<br>hysteresis                     |                                                                                                                                                                                                                                                                                                                                        | V <sub>FLHY</sub>                      | 0.15                           | 0.32                         | 0.45                           | V    |

| Response time                                        |                                                                                                                                                                                                                                                                                                                                        |                                        | -                              | 16                           | -                              | μs   |

| VIN OVERVOLTAGE SHUTDO                               | WN MONITOR                                                                                                                                                                                                                                                                                                                             | •                                      |                                |                              |                                |      |

| Overvoltage stop threshold                           |                                                                                                                                                                                                                                                                                                                                        | V <sub>OVSP</sub>                      | 37.0                           | 38.0                         | 39.0                           | V    |

| Overvoltage hysteresis                               |                                                                                                                                                                                                                                                                                                                                        | V <sub>OVHY</sub>                      | 0.5                            | 1.0                          | 1.5                            | V    |

| QUIESCENT CURRENT                                    |                                                                                                                                                                                                                                                                                                                                        |                                        |                                |                              |                                |      |

| Quiescent current                                    | VIN = 13 V, EN = 0 V, T <sub>J</sub> = 25°C                                                                                                                                                                                                                                                                                            | I <sub>Q,SLEEP</sub>                   | -                              | 6.0                          | -                              | μA   |

|                                                      | VIN = 13 V, EN = 0 V, −40°C ≤ T <sub>J</sub> ≤ 125 <sup>°</sup> C                                                                                                                                                                                                                                                                      | I <sub>Q.SLEEP</sub>                   | -                              | 6.0                          | 10                             | μA   |

|                                                      | VIN = 13 V, EN = 5 V, No switching,<br>T <sub>J</sub> = 25 $^{\circ}$ C                                                                                                                                                                                                                                                                | IQ                                     | -                              | 30                           | 40                             | μA   |

|                                                      | $ \begin{array}{l} \mbox{VIN} = 13 \mbox{ V}, 100  \mu \mbox{A load}, \mbox{VOUT} = 5 \mbox{ V}, \\ \mbox{VCCEXT} = \mbox{VOUT}, \mbox{EN} = \mbox{VIN}, \\ \mbox{T}_{ambient} = 25^{\circ}\mbox{C} \\ \mbox{(Not production tested}. \mbox{Measured on demo} \\ \mbox{board}, \mbox{refer to application note section)} \end{array} $ | I <sub>Q100</sub>                      | -                              | 82                           | 100                            | μΑ   |

| DBIAS                                                |                                                                                                                                                                                                                                                                                                                                        |                                        | •                              | •                            |                                |      |

| DBIAS voltage                                        | C <sub>DBIAS</sub> = 0.1 μF                                                                                                                                                                                                                                                                                                            | V <sub>DBIAS</sub>                     | 2.0                            | -                            | 2.4                            | V    |

| UNDERVOLTAGE LOCKOUT (N                              | ote 8)                                                                                                                                                                                                                                                                                                                                 |                                        |                                | -                            | •                              |      |

| UVLO start threshold                                 | VIN rising                                                                                                                                                                                                                                                                                                                             | V <sub>UVST</sub>                      | 4.0                            | -                            | 4.5                            | V    |

| UVLO stop threshold                                  | VIN falling                                                                                                                                                                                                                                                                                                                            | V <sub>UVSP</sub>                      | 3.2                            | -                            | 3.5                            | V    |

| UVLO hysteresis                                      |                                                                                                                                                                                                                                                                                                                                        | V <sub>UVHY</sub>                      | -                              | 0.9                          | -                              | V    |

| ENABLE                                               |                                                                                                                                                                                                                                                                                                                                        |                                        |                                |                              |                                |      |

| Logic low threshold voltage                          | Will be disabled at maximum value                                                                                                                                                                                                                                                                                                      | V <sub>ENLO</sub>                      | 0                              | -                            | 0.8                            | V    |

| Logic high threshold voltage                         | Will be enabled at minimum value                                                                                                                                                                                                                                                                                                       | V <sub>ENHI</sub>                      | 1.4                            | -                            | -                              | V    |

| Enable pin input Current                             | V <sub>EN</sub> = 5 V                                                                                                                                                                                                                                                                                                                  | E <sub>I,EN</sub>                      | -                              | 0.125                        | 0.26                           | μA   |

| OUTPUT VOLTAGE                                       |                                                                                                                                                                                                                                                                                                                                        |                                        |                                |                              |                                |      |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                                                                                                                                                                                                                                                                                                                        | V <sub>OUT,REG</sub>                   | 3.234<br>4.90<br>3.577<br>3.92 | 3.30<br>5.00<br>3.65<br>4.00 | 3.366<br>5.10<br>3.723<br>4.08 | V    |

| VOUT-GND resistance                                  | $EN = V_{ENLO}, VIN > 4.5 V$                                                                                                                                                                                                                                                                                                           | R <sub>ENLO,VOUT</sub>                 | 70                             | 100                          | 130                            | Ω    |

| VSEL                                                 | •                                                                                                                                                                                                                                                                                                                                      | -                                      | -                              | -                            | -                              | -    |

| VSEL input low threshold voltage                     |                                                                                                                                                                                                                                                                                                                                        | V <sub>LVSEL</sub>                     | 0                              | -                            | 0.8                            | V    |

|                                                      |                                                                                                                                                                                                                                                                                                                                        |                                        |                                |                              |                                |      |

**ELECTRICAL CHARACTERISTICS** ( $V_{EN} = V_{BAT} = V_{IN} = 4.5 \text{ V}$  to 37 V,  $V_{BST} = V_{SW} + (V_{DRV} - 0.5\text{V})$ ,  $C_{BST} = 0.1 \mu\text{F}$ ,  $C_{DRV} = 1 \mu\text{F}$ . Min/Max values are valid for the temperature range  $-40^{\circ}\text{C} < T_J < 150^{\circ}\text{C}$  unless noted otherwise, and are guaranteed by test, design or statistical correlation.

| Parameter                                    | Test Conditions                                                                                                                              | Symbol                                   | Min             | Тур            | Max                      | Unit           |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----------------|----------------|--------------------------|----------------|

| VSEL                                         |                                                                                                                                              |                                          |                 |                |                          |                |

| VSEL input high threshold voltage            |                                                                                                                                              | V <sub>HVSEL</sub>                       | 2.0             | -              | 3.3                      | V              |

| VSEL pin input current                       | VSEL = DBIAS                                                                                                                                 | V <sub>I,SEL</sub>                       | -               | 0.25           | 0.37                     | μA             |

| RESET                                        |                                                                                                                                              |                                          |                 | •              | 4                        |                |

| Reset threshold 1<br>(as a function of VOUT) | VOUT decreasing<br>VOUT increasing                                                                                                           | K <sub>UVFAL</sub><br>K <sub>UVRIS</sub> | 90<br>90.5      | 92.5<br>-      | 95<br>97                 | %              |

| Reset hysteresis (ratio of VOUT)             |                                                                                                                                              | K <sub>RES_HYS</sub>                     | 0.5             | -              | 2                        | %              |

| Noise-filtering delay                        |                                                                                                                                              | t <sub>RES FILT</sub>                    | 5               | -              | 25                       | μs             |

| Reset delay time                             | I <sub>RSTB</sub> = 1 mA<br>I <sub>RSTB</sub> = 500 μA<br>I <sub>RSTB</sub> = 100 μA                                                         | <sup>t</sup> RESET                       | 4<br>17         | 1.0<br>5<br>24 | 6<br>32                  | μs<br>ms<br>ms |

| Reset delay modes                            | Power good mode (no delay)<br>Delay mode<br>(see Detailed Operating Description)                                                             |                                          | 1000<br>-       |                | _<br>600                 | μΑ             |

| Reset output low level                       | I <sub>RSTB</sub> = 1 mA                                                                                                                     | V <sub>RESL</sub>                        | -               | -              | 0.4                      | V              |

| Reset threshold 2<br>(as a function of VOUT) | VOUT increasing<br>VOUT decreasing                                                                                                           | K <sub>OVRIS</sub><br>K <sub>OVFAL</sub> | 105<br>104      | 106.5<br>-     | 110<br>109               | %              |

| VOUT Output Clamp Current                    | VOUT = V <sub>OUT,reg(typ)</sub> + 10 %                                                                                                      | I <sub>CL,OUT</sub>                      | 0.5             | 1.0            | 1.5                      | mA             |

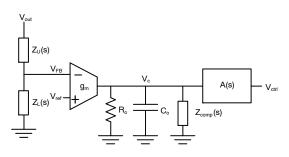

| ERROR AMPLIFIER                              |                                                                                                                                              |                                          |                 |                |                          |                |

| Transconductance (Note 3)                    | Internal to IC                                                                                                                               | 9м,ота                                   | -               | 26.6           | _                        | μS             |

| Compensation network                         | Internal to IC<br>NCV891930MW00DRG<br>3.3 V<br>5.0 V                                                                                         | R <sub>COMP,OTA</sub>                    | _               | 400<br>506     | _                        | kΩ             |

|                                              | 5.0 V<br>NCV891930MW01DRG<br>3.65 V<br>4.0 V                                                                                                 |                                          | _<br>_<br>_     | 360<br>386     |                          |                |

|                                              | Internal to IC<br>(refer to application note section for die<br>distributed capacitance modeling information)                                | C <sub>COMP,OTA</sub>                    | -               | 190            | -                        | pF             |

|                                              | Internal to IC                                                                                                                               | R <sub>0,OTA</sub>                       | -               | 56.7           | -                        | MΩ             |

| Slope compensation                           | NCV891930MW00DRG<br>NCV891930MW01DRG                                                                                                         | S <sub>a</sub>                           | _<br>_          | 29.4<br>39.0   |                          | mV/μs          |

| OSCILLATOR                                   |                                                                                                                                              | -                                        |                 |                | -                        |                |

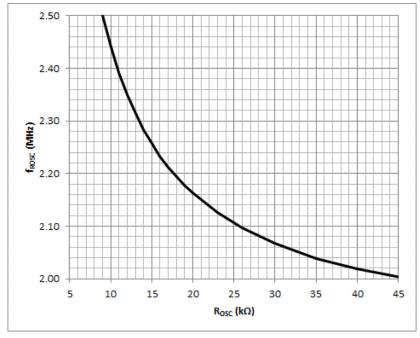

| Switching frequency                          | R <sub>OSC</sub> = open<br>4.5 V < VIN <v<sub>FLR/V<sub>FLF</sub><br/>V<sub>FLR</sub>/V<sub>FLF</sub> &lt; VIN &lt; V<sub>OVSP</sub></v<sub> | f <sub>SW</sub>                          | 1.8<br>0.9      | 2.0<br>1.0     | 2.2<br>1.1               | MHz            |

| Switching frequency – R <sub>OSC</sub>       | 4.5 V< VIN <vflr <math="" vflf,="">R_{OSC} = 9.01 k<math>\Omega</math></vflr>                                                                | f <sub>ROSC</sub>                        | 2.3             | 2.5            | 2.8                      | MHz            |

| R <sub>OSC</sub> reference voltage           | R <sub>OSC</sub> = 9.01 kΩ                                                                                                                   | V <sub>ROSC</sub>                        | 0.36            | 0.40           | 0.44                     | V              |

| Minimum off time                             |                                                                                                                                              | t <sub>OFF,MIN</sub>                     | -               | 49             | 75                       | ns             |

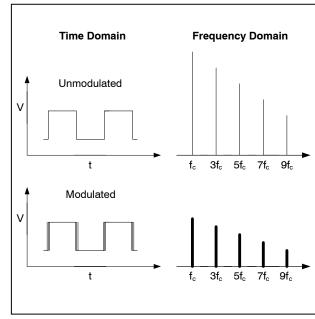

| SPREAD SPECTRUM                              |                                                                                                                                              |                                          |                 |                |                          |                |

| Modulation Frequency Range                   | V <sub>INLF</sub> /V <sub>INLR</sub> < VIN < V <sub>FLR</sub> /V <sub>FLF</sub>                                                              | f <sub>MOD</sub>                         | f <sub>sw</sub> | -              | f <sub>sw</sub> +<br>14% | MHz            |

| SYNCHRONIZATION                              |                                                                                                                                              |                                          |                 |                |                          |                |

| SYNCO output pulse duty ratio                | C <sub>LOAD</sub> = 40 pF. SYNCI = 0 or SYNCI = 1                                                                                            | D <sub>(SYNC)</sub>                      | 40              | -              | 60                       | %              |

| SYNCO output pulse fall time                 | C <sub>LOAD</sub> = 40 pF, 90% to 10%                                                                                                        | t <sub>R(SYNC)</sub>                     | -               | 4.5            | -                        | ns             |

| SYNCO output pulse rise time                 | C <sub>LOAD</sub> = 40 pF, 10% to 90%                                                                                                        | t <sub>F(SYNC)</sub>                     | -               | 7.0            | -                        | ns             |

| SYNCO Logic High                             | I <sub>SYNCO</sub> = 100 μA source current                                                                                                   | V <sub>SYNCOHI</sub>                     | 2.2             | -              | 3.45                     | V              |

**ELECTRICAL CHARACTERISTICS** ( $V_{EN} = V_{BAT} = V_{IN} = 4.5 \text{ V}$  to 37 V,  $V_{BST} = V_{SW} + (V_{DRV} - 0.5\text{V})$ ,  $C_{BST} = 0.1 \mu\text{F}$ ,  $C_{DRV} = 1 \mu\text{F}$ . Min/Max values are valid for the temperature range  $-40^{\circ}\text{C} < T_J < 150^{\circ}\text{C}$  unless noted otherwise, and are guaranteed by test, design or statistical correlation.

| Parameter                                                                                                                                                                                                                                                                    | Test Conditions                                                                                                         | Symbol                | Min    | Тур          | Max  | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------|--------|--------------|------|------|

| SYNCHRONIZATION                                                                                                                                                                                                                                                              |                                                                                                                         |                       |        |              |      |      |

| SYNCO Logic Low                                                                                                                                                                                                                                                              | I <sub>SYNCO</sub> = 2 mA sink current                                                                                  | V <sub>SYNCOLO</sub>  | -      | -            | 0.4  | V    |

| SYNCI pull-down resistance                                                                                                                                                                                                                                                   | CI pull-down resistance                                                                                                 |                       |        |              | 200  | kΩ   |

| SYNCI input low threshold<br>voltage                                                                                                                                                                                                                                         |                                                                                                                         | V <sub>LSYNCI</sub>   | 0      | -            | 0.8  | V    |

| SYNCI input high threshold voltage                                                                                                                                                                                                                                           |                                                                                                                         | V <sub>HSYNCI</sub>   | 2.0    | _            | 5.5  | V    |

| SYNCI high pulse width                                                                                                                                                                                                                                                       |                                                                                                                         | t <sub>HSYNCI</sub>   | 100    | -            | -    | ns   |

| External SYNCI Frequency                                                                                                                                                                                                                                                     |                                                                                                                         | fsynci                | 1.8    | -            | 2.5  | MHz  |

| Master Reassertion Time   Time from last rising SYNCI edge to first un-synchronized turn-on.     SYNCI = VLSYNCI after falling SYNCI edge   SYNCI = VLSYNCI after falling SYNCI edge     SYNCI = VHSYNCI after falling SYNCI edge   SYNCI = VHSYNCI after falling SYNCI edge |                                                                                                                         | ti(SYNC)              | -<br>- | 1.25<br>1.75 | -    | μs   |

| SOFT-START CURRENT                                                                                                                                                                                                                                                           |                                                                                                                         |                       |        |              |      |      |

| Soft-start charge current                                                                                                                                                                                                                                                    |                                                                                                                         | I <sub>SS</sub>       | 6.9    | 10           | 14.3 | μΑ   |

| Soft-start complete threshold                                                                                                                                                                                                                                                |                                                                                                                         | V <sub>SS</sub>       | -      | 1.0          | -    | V    |

| Soft-start delay                                                                                                                                                                                                                                                             | Soft-start delay From EN = 1 until start of charging of soft-<br>start capacitor<br>(DBIAS external capacitor = 0.1 μF) |                       | _      | 190          | _    | μs   |

| PEAK CURRENT LIMITS                                                                                                                                                                                                                                                          | ·                                                                                                                       | •                     | •      |              |      |      |

| Positive current limit threshold<br>voltage                                                                                                                                                                                                                                  | $0 \le (CSP - CSN) \le 200 \text{ mV}$<br>1.2 V $\le CSN \le 10.0 \text{ V}$<br>VIN < VIN_HIGH                          | V <sub>PCL,2M</sub>   | 67.5   | 75           | 82.5 | mV   |

|                                                                                                                                                                                                                                                                              | 0 ≤ (CSP – CSN) ≤ 200 mV<br>1.2 V ≤ CSN ≤ 10.0 V<br>VIN > VIN_HIGH<br>(Guaranteed by design)                            | VPCL,1M               | 72     | 80           | 88   | mV   |

| Current limit response time                                                                                                                                                                                                                                                  | $ \begin{array}{l} Comparator tripped until GH falling edge, \\ (V_{CSP}-V_{CSN}) = V_{CL(typ)} + 5 \ mV \end{array} $  | t <sub>CL</sub>       | -      | 39           | 125  | ns   |

| Negative current limit threshold voltage                                                                                                                                                                                                                                     | $-200 \text{ mV} \le (\text{CSP} - \text{CSN}) \le 0$<br>1.2 V $\le \text{CSN} \le 10.0 \text{ V}$                      | V <sub>NCL</sub>      | -36    | -52          | -71  | mV   |

| Common-mode range                                                                                                                                                                                                                                                            |                                                                                                                         |                       | -      | VOUT         | -    | V    |

| CSP input bias source current                                                                                                                                                                                                                                                |                                                                                                                         |                       | -      | 0.1          | 1.0  | μA   |

| CSN input bias source current                                                                                                                                                                                                                                                |                                                                                                                         | I <sub>BIAS,CSN</sub> | -      | 30           | -    | μA   |

| GATE DRIVERS                                                                                                                                                                                                                                                                 |                                                                                                                         |                       |        |              |      |      |

| GH sourcing ON resistance                                                                                                                                                                                                                                                    | $V_{BST} - V_{GH} = 2 V$                                                                                                | R <sub>GHSOURCE</sub> | 1.6    | 2.5          | 5.3  | Ω    |

| GH sinking ON resistance                                                                                                                                                                                                                                                     | V <sub>GH</sub> – V <sub>SW</sub> = 2 V                                                                                 | R <sub>GHSINK</sub>   | 1.3    | 2.5          | 4.3  | Ω    |

| GH-VSW resistance                                                                                                                                                                                                                                                            |                                                                                                                         | R <sub>GH,VSW</sub>   | -      | 20           | -    | kΩ   |

| GL sourcing ON resistance                                                                                                                                                                                                                                                    | $V_{DRV} - V_{GL} = 2 V$                                                                                                | R <sub>GLSOURCE</sub> | 1.6    | 2.5          | 5.3  | Ω    |

| GL sinking ON resistance V <sub>GL</sub> = 2 V                                                                                                                                                                                                                               |                                                                                                                         | R <sub>GLSINK</sub>   | 1.3    | 2.5          | 4.3  | Ω    |

| GL-PGND resistance                                                                                                                                                                                                                                                           |                                                                                                                         | R <sub>GL,PGND</sub>  | -      | 20           | _    | kΩ   |

| GATE DRIVE SUPPLY                                                                                                                                                                                                                                                            | •                                                                                                                       | -                     | •      | •            |      | •    |

| Driving voltage dropout                                                                                                                                                                                                                                                      | $V_{IN} - V_{DRV}$ , $I_{VDRV}$ = 25 mA                                                                                 | V <sub>DRV,DO</sub>   | -      | 0.3          | 0.6  | V    |

| Driving voltage source current                                                                                                                                                                                                                                               | V <sub>IN</sub> – V <sub>DRV</sub> = 1 V                                                                                | I <sub>DRV</sub>      | 65     | 100          | -    | mA   |

| Backdrive diode voltage drop                                                                                                                                                                                                                                                 | $V_{\text{DRV}} - V_{\text{IN}}$ , $I_{d,\text{bd}} = 5 \text{ mA}$                                                     | V <sub>D,BD</sub>     | _      | -            | 0.7  | V    |

| Driving voltage                                                                                                                                                                                                                                                              | I <sub>VDRV</sub> = 0.1 – 25 mA                                                                                         | V <sub>DRV</sub>      | 4.75   | 5.00         | 5.30 | V    |

|                                                                                                                                                                                                                                                                              |                                                                                                                         | • UNV                 |        | 2.00         | 2.20 |      |

**ELECTRICAL CHARACTERISTICS** ( $V_{EN} = V_{BAT} = V_{IN} = 4.5 \text{ V}$  to 37 V,  $V_{BST} = V_{SW} + (V_{DRV} - 0.5V)$ ,  $C_{BST} = 0.1 \mu$ F,  $C_{DRV} = 1 \mu$ F. Min/Max values are valid for the temperature range  $-40^{\circ}\text{C} < T_J < 150^{\circ}\text{C}$  unless noted otherwise, and are guaranteed by test, design or statistical correlation.

| Parameter                      | Test Conditions Symbol          |                     | Min  | Тур  | Max  | Unit |

|--------------------------------|---------------------------------|---------------------|------|------|------|------|

| GATE DRIVE SUPPLY              | ·                               |                     |      | •    | •    |      |

| VDRV POR start threshold       | (Note 8)                        | V <sub>DRVST</sub>  | 3.75 | 4.0  | 4.25 | V    |

| VDRV POR stop threshold        | (Note 8)                        | V <sub>DRVSP</sub>  | 2.85 | 3.1  | 3.35 | V    |

| LDO bypass start threshold     | VCCEXT rising                   |                     | 4.48 | -    | 4.80 | V    |

| LDO bypass stop threshold      | VCCEXT falling                  |                     | 4.31 | -    | 4.65 | V    |

| LDO bypass input current       | Pulse skip, VCCEXT = 5 V        |                     | -    | 3.1  | -    | μA   |

| LDO bypass R <sub>DS(on)</sub> | VCCEXT = 5 V, VDRV load = 50 mA |                     | 1.07 | 1.93 | 2.79 | Ω    |

| THERMAL SHUTDOWN               |                                 | -                   |      |      |      |      |

| Thermal shutdown threshold     | T <sub>J</sub> rising           | T <sub>SD</sub>     | 155  | 170  | 190  | °C   |

| Thermal shutdown hysteresis    | T <sub>J</sub> falling          | T <sub>SD,HYS</sub> | 5    | 15   | 20   | °C   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless noted. Product

performance may not be indicated by the Electrical Characteristics if operated under different conditions.

7. Spread spectrum function will be disabled when IC operated using external frequency synchronization.

8. Operating with VIN near IC UVLO thresholds may result in insufficient gate drive voltage drive amplitude to permit switching of external MOSFETs. Use of an external bias voltage to maintain sufficient VDRV voltage may be required.

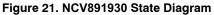

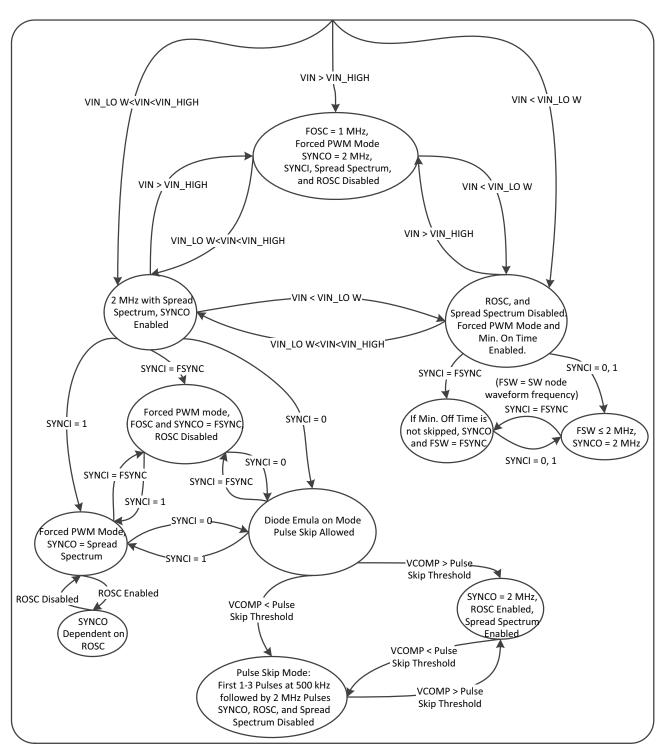

### FUNCTIONALITY INFORMATION TABLE

| VIN (V)                                                  | SYNCI<br>pin      | Behaviour                                                                                                                                              | Frequency                                                                                                                               | SYNCI<br>FUNCTION         | SYNCO                                     | Spread<br>Spectrum                                                                            | ROSC                                                                                    |

|----------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| VIN < Vin_low                                            | Logic-0           | Synchronous mode,<br>recirculation FET turns-off<br>when -50 mV current sense                                                                          | 2 MHz * or less.<br>Minimum off-time may<br>be skipped depending                                                                        | Disabled                  | Enabled,<br>2 MHz                         | Disabled                                                                                      | Disabled                                                                                |

|                                                          | Logic-1           | voltage is detected.<br>Pulse skip not allowed when<br>VIN < Vin low                                                                                   | on VIN, output voltage<br>option and operating<br>current.                                                                              |                           |                                           |                                                                                               |                                                                                         |

|                                                          | F <sub>sync</sub> |                                                                                                                                                        | F <sub>sync</sub> if minimum<br>off-time is not skipped                                                                                 | Enabled                   | F <sub>sync</sub>                         |                                                                                               |                                                                                         |

| Vin_low < VIN <<br>Vin_high (No Pulse<br>Skip Condition) | Logic-0           | Synchronous mode,<br>recirculation FET turns-off<br>when when < 0 V current<br>sense voltage is detected.                                              | f <sub>ROSC</sub> with spread<br>spectrum.<br>Upon exiting Pulse Skip<br>mode, first 1–3 pulses<br>500 kHz followed by<br>2 MHz pulses. | Disabled                  | Enabled,<br>follows<br>spread<br>spectrum | Enabled<br>When exiting<br>Pulse Skip mode,<br>function resumes<br>within 14 2 MHz<br>pulses. | Enabled<br>Disabled during<br>1–3 500 kHz<br>pulses upon<br>exiting Pulse Skip<br>Mode. |

|                                                          | Logic-1           | Forced PWM mode,<br>recirculation FET turns-off<br>when -50 mV current sense                                                                           | f <sub>ROSC</sub> with spread spectrum                                                                                                  | Disabled                  | Enabled                                   | Enabled                                                                                       | Enabled                                                                                 |

|                                                          | F <sub>sync</sub> | voltage is detected.                                                                                                                                   | F <sub>sync</sub>                                                                                                                       | Enabled                   | F <sub>sync</sub>                         | Disabled                                                                                      | Disabled                                                                                |

| Vin_low < VIN <<br>Vin_high (Pulse<br>Skip Condition)    | Logic-0           | Pulse skip mode                                                                                                                                        | Disabled                                                                                                                                | Disabled                  | Disabled                                  | Disabled                                                                                      | Disabled                                                                                |

| VIN > Vin_high                                           | Х                 | Synchronous mode,<br>recirculation FET turns-off<br>when -50 mV current sense<br>voltage is detected.<br>Pulse skip not allowed when<br>VIN > Vin_high | 1 MHz                                                                                                                                   | Disabled                  | Enabled,<br>2 MHz                         | Disabled                                                                                      | Disabled                                                                                |

| Soft-start                                               | х                 | Forced PWM mode with<br>pulse skip allowed,<br>recirculation FET turns-off<br>when when < 0 V current<br>sense voltage is detected                     | 2 MHz                                                                                                                                   | Disabled                  | Disabled                                  | Disabled                                                                                      | Disabled                                                                                |

| Vout undervoltage<br>(K <sub>UV</sub> )                  | х                 | RSTB activated.                                                                                                                                        | Fixed frequency                                                                                                                         | No change in<br>behaviour | No change in<br>behaviour                 | Disabled                                                                                      | No change in<br>behaviour                                                               |

| Vout overvoltage<br>(K <sub>OV</sub> )                   | х                 | RSB activated.                                                                                                                                         | No PWM                                                                                                                                  | No PWM                    | No Change<br>in behaviour                 | No PWM                                                                                        | No PWM                                                                                  |

\*GH off pulses will be skipped to maintain output voltage regulation whenever GH toff is less than toff,MIN occurs.

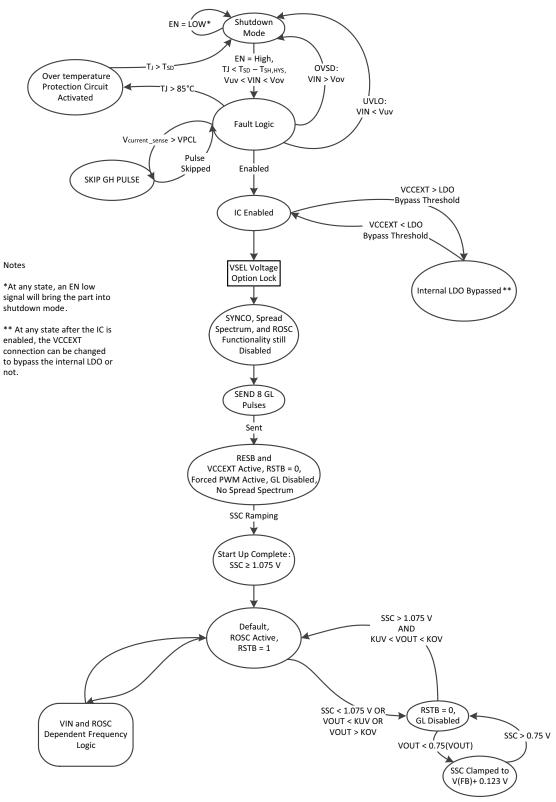

### **DETAILED OPERATING DESCRIPTION**

#### General

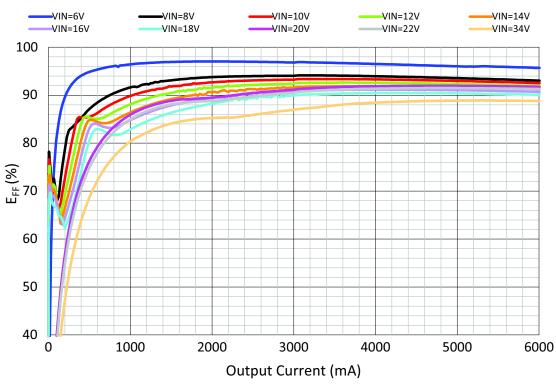

Preset internal slope and feedback loop compensation results in predetermined values for current sense resistors and output filtering.

A capacitor technology mix of ceramic and aluminum polymer or solid aluminum electrolytic capacitors results in a cost effective solution. Non–solid aluminum electrolytic capacitors are not recommended due to their large cold temperature ESR properties. An all ceramic solution filter implementation using 10  $\mu$ F capacitor (like the GCM32DR71C106KA37) was considered for Table 1 and Table 2 for a design objective of ±3% transient voltage for a 50% load transient. Tolerances used in determining the number of required capacitors were:

- Initial tolerance

- ♦ -10%

- Temperature tolerance

- ♦ -10% at 125°C

- DC bias voltage

- → -0.6% for 3.3 V, -1.0% of 3.65 V, -1.5% for 4 V, -3.1% for 5 V

- AC RMS voltage

- ♦ -4.4%

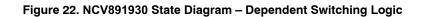

Additional tolerances such as aging may need to be considered during the design phase.

At higher currents, optimal inductor and current sense resistor values may become limited. It may be necessary to parallel 3 resistor values to achieve the desired current sense resistor value. The manufacturer's inductor tolerance and properties must be considered when determining the current sense resistor for desired current limiting under worst case component values.

|                       |              |                        | 3.3 V Option                     |                                         | 5 V Option             |                                  |                                         |

|-----------------------|--------------|------------------------|----------------------------------|-----------------------------------------|------------------------|----------------------------------|-----------------------------------------|

| Output<br>Current (A) | MOSFET       | Inductor<br>Value (μΗ) | Current<br>Sense<br>Resistor (Ω) | Output<br>Capacitance<br>(ceramic) (μF) | Inductor<br>Value (μΗ) | Current<br>Sense<br>Resistor (Ω) | Output<br>Capacitance<br>(Ceramic) (μF) |

| 2                     | NVTFS5C478NL | 2.2                    | 0.028                            | 70                                      | 3.3                    | 0.028                            | 50                                      |

|                       | NVMFD5C470NL |                        |                                  |                                         |                        |                                  |                                         |

| 3                     | NVTFS5C478NL | 1.5                    | 0.018                            | 110                                     | 2.2                    | 0.0195                           | 80                                      |

|                       | NVMFD5C470NL |                        |                                  |                                         |                        |                                  |                                         |

| 4                     | NVTFS5C478NL | 1.0                    | 0.0135                           | 140                                     | 1.5                    | 0.0135                           | 110                                     |

| 5                     | NVMFS5C468NL | 0.80                   | 0.011                            | 180                                     | 1.2                    | 0.011                            | 120                                     |

| 6                     | NVMFS5C468NL | 0.65                   | 0.009                            | 220                                     | 1.0                    | 0.009                            | 150                                     |

#### Table 1. MW891930MW00R2G VALUE RECOMMENDATIONS

|                          |              | 3.65 V Option             |                                     |                                         | 4 V Option                |                                     |                                            |

|--------------------------|--------------|---------------------------|-------------------------------------|-----------------------------------------|---------------------------|-------------------------------------|--------------------------------------------|

| Output<br>Current<br>(A) | MOSFET       | Inductor<br>Value<br>(μΗ) | Current<br>Sense<br>Resistor<br>(Ω) | Output<br>Capacitance<br>(ceramic) (µF) | Inductor<br>Value<br>(μΗ) | Current<br>Sense<br>Resistor<br>(Ω) | Output<br>Capacitance<br>(Ceramic)<br>(μF) |

| 2                        | NVTFS5C478NL | 2.2                       | 0.028                               | 80                                      | 2.2                       | 0.028                               | 70                                         |

|                          | NVMFD5C470NL |                           |                                     |                                         |                           |                                     |                                            |

| 3                        | NVTFS5C478NL | 1.5                       | 0.018                               | 110                                     | 1.5                       | 0.018                               | 100                                        |