## STM6905

### Quintuple, ultralow voltage supervisor with push-button reset

### Features

- Quintuple voltage monitoring

- Accurate ±1.8 % across temperature voltage threshold (±1 % at 25 °C)

- Primary supply (V<sub>CC</sub>) monitor. Fixed (factory programmed) reset thresholds: 3.078 V to 2.866 V

- Second fixed (V2IN) monitor. Fixed (factoryprogrammed) reset thresholds: 2.333 V to 1.050 V

- Three additional adjustable supply monitor inputs (externally adjustable)

## Datasheet - production data

- 600 mV internal reference

- RST output (open drain)

- Output guaranteed for  $V_{CC} \ge 0.8 \text{ V}$

- Reset delay time (T<sub>REC</sub>) on power-up: 210 ms (typ)

- Manual reset input (MR)

- Low supply current of 12 µA (typ)

- Power supply voltage 0.8 V to 5.5 V

- RoHS compliant (green package)

- 8-pin MSOP/TSSOP

- Operating temperature: -40 °C to 85 °C (industrial grade)

### Applications

- Set-top boxes

- Multi-voltage systems

- Cable/satellite applications

- Computer systems

- Data storage equipment

| Order code     | V <sub>RST1</sub> (V) | V <sub>RST2</sub> (V) | t <sub>REC</sub> (ms) | Package        |  |  |

|----------------|-----------------------|-----------------------|-----------------------|----------------|--|--|

| STM6905TZEDS6F |                       | 2.333                 |                       |                |  |  |

| STM6905TWEDS6F | 3.078                 | 1.683                 |                       |                |  |  |

| STM6905TGEDS6F |                       | 1.110                 | 210                   | MSOP8 (TSSOP8) |  |  |

| STM6905SYEDS6F | 2.055                 | 2.188                 | 210                   |                |  |  |

| STM6905SFEDS6F | 2.955                 | 1.050                 |                       |                |  |  |

| STM6905PWEDS6F | 2.866 1.683           |                       |                       |                |  |  |

### Table 1. Device summary<sup>(1)</sup>

1. Other reset threshold voltages and t<sub>REC</sub> time-out periods are offered. Contact local ST sales office for availability.

This is information on a product in full production.

## Contents

| 1  | Desc  | ription                                                                          |  |  |  |  |  |  |  |

|----|-------|----------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 2  | Pin d | Pin descriptions                                                                 |  |  |  |  |  |  |  |

|    | 2.1   | Push-button reset input (MR)                                                     |  |  |  |  |  |  |  |

|    | 2.2   | V <sub>CC</sub> primary supply voltage monitoring input                          |  |  |  |  |  |  |  |

|    | 2.3   | V2IN second fixed voltage monitoring input7                                      |  |  |  |  |  |  |  |

|    | 2.4   | V <sub>SS</sub>                                                                  |  |  |  |  |  |  |  |

|    | 2.5   | V3IN, V4IN, and V5IN                                                             |  |  |  |  |  |  |  |

|    | 2.6   | RST active-low, open drain reset output                                          |  |  |  |  |  |  |  |

| 3  | Oper  | ation                                                                            |  |  |  |  |  |  |  |

|    | 3.1   | Setting the adjustable voltage levels for V3IN, V4IN, and V5IN inputs $\ldots$ 9 |  |  |  |  |  |  |  |

|    | 3.2   | Power on reset (t <sub>REC</sub> )                                               |  |  |  |  |  |  |  |

| 4  | Volta | ge monitoring                                                                    |  |  |  |  |  |  |  |

| 5  | Maxi  | mum rating                                                                       |  |  |  |  |  |  |  |

| 6  | DC a  | nd AC parameters 12                                                              |  |  |  |  |  |  |  |

| 7  | Pack  | age information                                                                  |  |  |  |  |  |  |  |

| 8  | Part  | numbering                                                                        |  |  |  |  |  |  |  |

| 9  | Pack  | age marking information17                                                        |  |  |  |  |  |  |  |

| 10 | Revis | sion history                                                                     |  |  |  |  |  |  |  |

## List of tables

| Table 1. | Device summary                                 |

|----------|------------------------------------------------|

| Table 2. | Signal names and functions                     |

| Table 3. | Absolute maximum ratings                       |

| Table 4. | DC and AC characteristics                      |

| Table 5. | TSSOP8 3 mm x 3 mm, package mechanical data 15 |

| Table 6. | Ordering information scheme                    |

| Table 7. | Marking description                            |

| Table 8. | Document revision history                      |

## List of figures

|           | Logic diagram                                  | 5 |

|-----------|------------------------------------------------|---|

| Figure 2. | MSOP/TSSOP-8 connections                       | 5 |

| Figure 3. | Functional block diagram                       | 3 |

| Figure 4. | Typical hardware hookup application diagram    | 8 |

| Figure 5. | MR timing waveforms                            | C |

| Figure 6. | Voltage monitoring diagram                     | C |

| Figure 7. | TSSOP8 3 mm x 3 mm, package mechanical outline | 5 |

### 1 Description

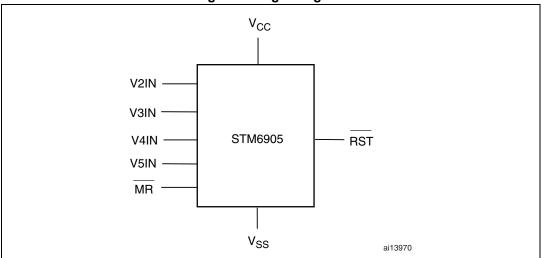

The STM6905 supervisor is a low voltage/low supply current processor supervisor, designed to monitor up to five system power supply voltages. This device is targeted at applications such as set-top boxes (STBs), portable, battery-powered systems, networking and communication systems.

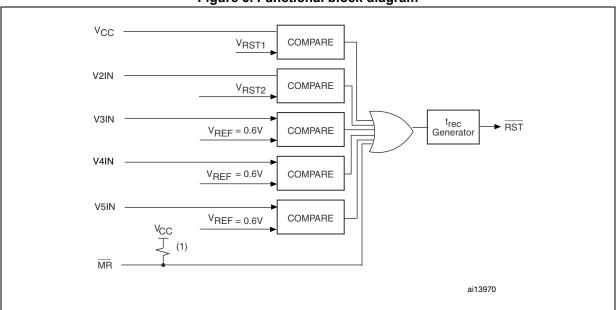

The device supports a push-button type manual reset input ( $\overline{\text{MR}}$ ). Two of the five supply monitors (V<sub>CC</sub> and V2IN) have fixed (customer-selectable, factory-trimmed) thresholds (V<sub>RST1</sub> and V<sub>RST2</sub>). The other three voltage monitor inputs (V3IN, V4IN and V5IN) are monitored using externally adjustable threshold (600 mV internal reference) to meet specific level requirements.

If any of the five monitored voltages drops below its factory-trimmed or adjustable thresholds, or if the  $\overline{\text{MR}}$  is asserted to logic low, the reset output  $\overline{\text{RST}}$  is asserted (driven low). Once asserted,  $\overline{\text{RST}}$  is maintained low for a minimum delay period ( $t_{\text{REC}}$ ) after ALL monitored supplies rise above their respective thresholds and  $\overline{\text{MR}}$  returns to high. The reset output logic state is valid for V<sub>CC</sub> greater than 0.8 V.

The STM6905 is available in a standard 8-lead MSOP (TSSOP) package.

Figure 1. Logic diagram

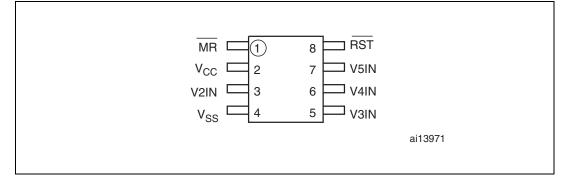

| Pin | Name            | Туре   | Function                                                                              |

|-----|-----------------|--------|---------------------------------------------------------------------------------------|

| 1   | MR              | Input  | Active-low manual reset input with internal pull-up resistor                          |

| 2   | V <sub>CC</sub> | Supply | Primary supply voltage input and integrated fixed threshold under-<br>voltage monitor |

| 3   | V2IN            | Input  | Second fixed threshold input monitor                                                  |

| 4   | $V_{SS}$        | Supply | Ground                                                                                |

| 5   | V3IN            |        | Adjustable third reset comparator input                                               |

| 6   | V4IN            | Input  | Adjustable fourth reset comparator input                                              |

| 7   | V5IN            |        | Adjustable fifth reset comparator input                                               |

| 8   | RST             | Output | Active-low open-drain reset output (10 k $\Omega$ internal pull-up)                   |

Table 2. Signal names and functions

### 2 Pin descriptions

### 2.1 Push-button reset input (MR)

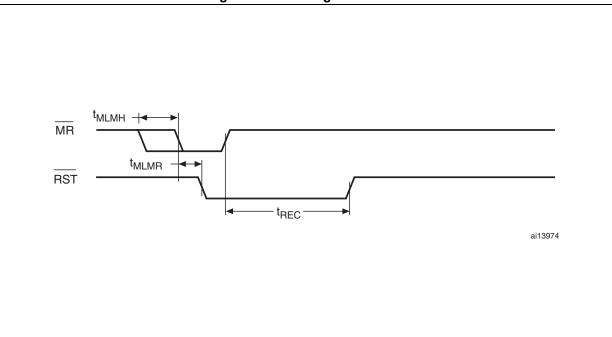

When  $\overline{\text{MR}}$  goes low the  $\overline{\text{RST}}$  output is driven low.  $\overline{\text{RST}}$  remains low as long as  $\overline{\text{MR}}$  is low and for the  $t_{\text{REC}}$  after  $\overline{\text{MR}}$  returns to high. The active-low input has an internal 10 k $\Omega$  pull-up resistor to  $V_{CC}$ . It can be driven from a TTL or CMOS logic line, or with open drain/collector outputs, or connected to  $V_{SS}$  through a switch. If unused, leave this pin open or connect it to  $V_{CC}$ .

Connect a normally open momentary switch from  $\overline{\text{MR}}$  to V<sub>SS</sub>. An external debounce circuitry is not required (if MR is driven from long cables or if the device is used in noisy environments, connecting a 0.1 µF capacitor from MR to V<sub>SS</sub> provides additional noise immunity).

### 2.2 V<sub>CC</sub> primary supply voltage monitoring input

The V<sub>CC</sub> pin is also the input for the primary reset threshold monitor. Fixed (customer-selectable, factory programmed) reset thresholds include 3.078 V to 2.866 V.

### 2.3 V2IN second fixed voltage monitoring input

The V2IN input is the second fixed-voltage input for reset threshold monitoring. Available fixed (customer-selectable, factory programmed) reset thresholds include 2.333 V to 1.050 V.

### 2.4 V<sub>SS</sub>

This pin is the ground pin for the power supply.

### 2.5 V3IN, V4IN, and V5IN

The V3IN, V4IN and V5IN are high impedance inputs. RST is driven low when the voltage (VTRIP) at the pin falls below 600 mV (internal reference voltage at their respective comparators). The monitored voltage reset threshold is set with an external resistor-divider network.

### 2.6 **RST** active-low, open drain reset output

The reset output ( $\overline{\text{RST}}$ ) pin is driven low and stays low whenever V<sub>CC</sub> or V2IN, or V3IN, or V4IN, or V5IN falls below its factory-trimmed or adjustable reset threshold or when MR goes to logic low. It remains low for t<sub>REC</sub> after all supply voltages being monitored rise above their reset thresholds and MR goes from low to high. Connect an external pull-up resistor to V<sub>CC</sub>. A 10 k $\Omega$  pull-up resistor should be sufficient for most applications.

Figure 3. Functional block diagram

1. Internal pull-up on  $\overline{\text{MR}}$  input of 10 k $\Omega$  (typ).

Figure 4. Typical hardware hookup application diagram

8/19

### 3 Operation

The STM6905 can monitor critical voltages such as power-supply and battery voltage levels, while interfacing easily with the system controllers/microprocessors.

*Figure 4* shows the typical hardware hookup for monitoring five voltages: two fixed thresholds (customer-selectable, factory-programmed) and three adjustable monitor inputs. The RST output is open drain and requires a 10 k $\Omega$  pull-up resistor tied to V<sub>CC</sub>.

# 3.1 Setting the adjustable voltage levels for V3IN, V4IN, and V5IN inputs

The user can customize the minimum voltage levels for the three adjustable voltage inputs by connecting an external resistor divider network to the V3IN, V4IN and V5IN pins in order to set the trip point at some voltage above the 600 mv ( $V_{REF}$ ) according to the following formula.

$$VTRIP = 0.6 V \times \frac{R1 + R2}{R2}$$

During normal operation, the STM6905 monitors the voltage levels at all five pins (Vcc, V2IN, V3IN, V4IN, and V5IN).

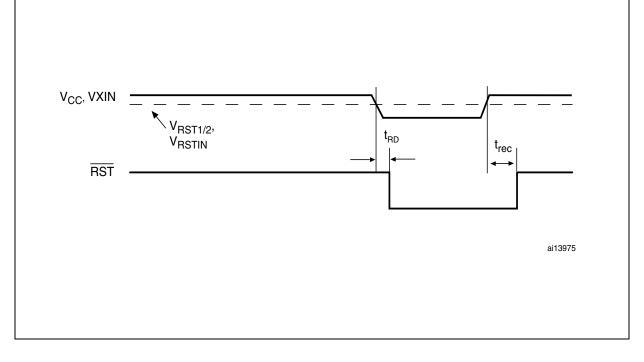

### 3.2 Power on reset (t<sub>REC</sub>)

On power up, the STM6905 activates a power-on reset circuit which asserts the reset pin (i.e. RST goes low). The RST signal remains active until  $V_{CC}$  (and V2IN, V3IN, V4IN, V5IN, and MR) rises above the minimum voltage level for the time period  $t_{REC}$  thereby ensuring that the supply voltage has stabilized to sufficient operating levels.

## 4 Voltage monitoring

### Figure 5. MR timing waveforms

Figure 6. Voltage monitoring diagram

## 5 Maximum rating

Stressing the device above the ratings listed in the "Absolute maximum ratings" table may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE program and other relevant quality documents.

| Symbol                          | Parameter                                 | Value                        | Unit |

|---------------------------------|-------------------------------------------|------------------------------|------|

| T <sub>STG</sub>                | Storage temperature (V <sub>CC</sub> off) | -55 to +150                  | °C   |

| T <sub>SLD</sub> <sup>(1)</sup> | Lead solder temperature for 10 seconds    | 260                          |      |

| V <sub>IO</sub>                 | Input or output voltage                   | -0.3 to V <sub>CC</sub> +0.3 | v    |

| V <sub>CC</sub>                 | Supply voltage                            | -0.3 to 7.0                  | v    |

| Ι <sub>Ο</sub>                  | Output current                            | 20                           | mA   |

| $\theta_{JA}$                   | Thermal resistance (junction to ambient)  | 146                          | °C/W |

| Table 3 | 3. | Absolute | maximum | ratings |

|---------|----|----------|---------|---------|

|---------|----|----------|---------|---------|

Reflow at peak temperature of 255 °C to 260 °C for < 30 seconds (total thermal budget not to exceed 180 °C for between 90 to 150 seconds).</li>

## 6 DC and AC parameters

This section summarizes the operating measurement conditions and the DC and AC characteristics of the device. Designers should check that the operating conditions in their circuit match the operating conditions when relying on the quoted parameters.

| Symbol                           | Alter-<br>native | Description                               | Test condition <sup>(1)</sup>                                        |                               | Min   | Тур   | Мах   | Unit  |  |

|----------------------------------|------------------|-------------------------------------------|----------------------------------------------------------------------|-------------------------------|-------|-------|-------|-------|--|

| V <sub>CC</sub>                  |                  | Operating voltage                         |                                                                      |                               | 0.8   |       | 5.5   | V     |  |

| 1                                |                  | V <sub>CC</sub> supply current            | V <sub>CC</sub>                                                      | ; < 5.5 V                     |       | 12    | 16    |       |  |

| I <sub>CC</sub>                  |                  | V <sub>CC</sub> supply current            | V <sub>CC</sub>                                                      | <sub>2</sub> = 3.3 V          |       | 11    | 15    |       |  |

| I2IN                             |                  | V2IN supply current                       | V2IN                                                                 | N = 3.3 V                     |       | 3     | 5     |       |  |

| ILI                              |                  | Input leakage current (MR) <sup>(2)</sup> | V <sub>IN</sub> = V                                                  | $V_{\rm CC}$ or $V_{\rm SS}$  | -0.5  |       | +0.5  | μA    |  |

| I <sub>LO</sub> <sup>(3)</sup>   |                  | Open drain RST output leakage current     |                                                                      | > VRST,<br>ot asserted        | -0.5  |       | +0.5  |       |  |

|                                  |                  |                                           | $V_{CC} \ge 0.8$                                                     | V, I <sub>SINK</sub> = 1 µA   |       |       | 0.3   |       |  |

|                                  |                  |                                           | $V_{CC} \ge 1.0$ V                                                   | /, I <sub>SINK</sub> = 50 μA  |       |       | 0.3   |       |  |

| V <sub>OL</sub>                  |                  | Output low voltage<br>(RST, open drain)   | V <sub>CC</sub> ≥ 1.2 V                                              | ′, I <sub>SINK</sub> = 100 μA |       |       | 0.3   |       |  |

|                                  |                  |                                           | $V_{CC} \ge 2.7$ V, $I_{SINK}$ = 1.2 mA                              |                               |       |       | 0.3   |       |  |

|                                  |                  |                                           | $V_{CC} \ge 4.5 \text{ V}, \text{ I}_{\text{SINK}} = 3.2 \text{ mA}$ |                               |       |       | 0.4   |       |  |

|                                  |                  | V <sub>CC</sub> reset threshold           | T (falling)                                                          | 25°C                          | 3.047 | 3.078 | 3.109 | -     |  |

|                                  |                  |                                           | T (falling)                                                          | -40 °C to 85 °C               | 3.023 |       | 3.133 |       |  |

| V <sub>RST1</sub> <sup>(4)</sup> | V                |                                           | V rosot throshold                                                    | S (falling)                   | 25 °C | 2.925 | 2.955 | 2.985 |  |

| VRST1                            | VTH1             |                                           | S (lailing)                                                          | -40 °C to 85 °C               | 2.902 |       | 3.008 |       |  |

|                                  |                  |                                           | P (falling)                                                          | 25 °C                         | 2.837 | 2.866 | 2.895 |       |  |

|                                  |                  |                                           | i (iaiiiig)                                                          | -40 °C to 85 °C               | 2.814 |       | 2.918 |       |  |

|                                  |                  |                                           | Z (falling)                                                          | 25 °C                         | 2.310 | 2.333 | 2.356 |       |  |

|                                  |                  |                                           | Z (lainig)                                                           | -40 °C to 85 °C               | 2.291 |       | 2.375 |       |  |

|                                  |                  |                                           | Y (falling)                                                          | 25 °C                         | 2.166 | 2.188 | 2.210 |       |  |

|                                  |                  |                                           | r (ranng)                                                            | -40 °C to 85 °C               | 2.149 |       | 2.227 |       |  |

| V <sub>RST2</sub> <sup>(4)</sup> | V <sub>TH2</sub> | V2IN reset threshold                      | W (falling)                                                          | 25 °C                         | 1.666 | 1.683 | 1.700 |       |  |

| *RS12                            | ♥1H2             |                                           | w (lainig)                                                           | -40 °C to 85 °C               | 1.653 |       | 1.713 |       |  |

|                                  |                  |                                           | G (falling)                                                          | 25 °C                         | 1.099 | 1.110 | 1.121 |       |  |

|                                  |                  |                                           |                                                                      | -40 °C to 85 °C               | 1.090 |       | 1.130 |       |  |

|                                  |                  |                                           | F (falling)                                                          | 25 °C                         | 1.040 | 1.050 | 1.061 |       |  |

|                                  |                  |                                           | i (iaiiiig)                                                          | -40 °C to 85 °C               | 1.031 |       | 1.069 |       |  |

|         |    | -   |    |                 |

|---------|----|-----|----|-----------------|

| Table 4 | DC | and | AC | characteristics |

12/19

| Symbol                           | Alter-<br>native    | Description                             | Test condition <sup>(1)</sup>                                                     | Min                                       | Тур | Мах                 | Unit |

|----------------------------------|---------------------|-----------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------|-----|---------------------|------|

| V <sub>HYST</sub>                |                     | Reset threshold<br>hysteresis           | Referenced to V <sub>RST1</sub> /V <sub>RST2</sub><br>typical                     |                                           | 0.5 |                     | %    |

|                                  |                     |                                         | V <sub>CC</sub> = (V <sub>RST1</sub> + 100 mV) to<br>(V <sub>RST1</sub> – 100 mV) |                                           | 20  |                     | μs   |

| t <sub>RD</sub>                  |                     | V <sub>CC</sub> to RST delay            | V2IN = (V <sub>RST2</sub> + 75 mV) to<br>(V <sub>RST2</sub> – 75 mV)              |                                           | 20  |                     |      |

|                                  |                     |                                         | Option B <sup>(5)</sup>                                                           | 20                                        | 30  | 40                  |      |

|                                  |                     | DOT time, out paried                    | Option C <sup>(5)</sup>                                                           | 80                                        | 120 | 180                 |      |

| t <sub>REC</sub> t <sub>RP</sub> | RST time-out period | Option E                                | 140                                                                               | 210                                       | 280 | ms                  |      |

|                                  |                     |                                         | Option F <sup>(5)</sup>                                                           | 280                                       | 420 | 560                 |      |

| Adjustat                         | ole reset           | comparator input (V3IN, V               | /4IN, V5IN)                                                                       |                                           |     | 1                   |      |

| V <sub>RSTIN</sub>               |                     | V3IN, V4IN, V5IN input threshold        |                                                                                   | 589                                       | 600 | 611                 | mV   |

| I <sub>RSTIN</sub>               |                     | V3IN, V4IN, V5IN input current          | V3IN, V4IN, V5IN > 0.8 V                                                          | -25                                       |     | +25                 | nA   |

|                                  |                     | V3IN, V4IN, V5IN<br>hysteresis          |                                                                                   |                                           | 3   |                     | mV   |

| t <sub>RSTIND</sub>              |                     | V3IN, V4IN, V5IN to<br>RST output delay | VRSTIN to (VRSTIN – 30 mV)                                                        |                                           | 22  |                     | μs   |

| Manual (                         | push-bu             | tton) reset input                       |                                                                                   |                                           |     |                     |      |

| V <sub>IL</sub>                  |                     |                                         |                                                                                   |                                           |     | $0.3 \times V_{CC}$ | v    |

| $V_{\text{IH}}$                  |                     | MR input voltage                        |                                                                                   | $0.7 \mathrm{x} \mathrm{V}_{\mathrm{CC}}$ |     |                     | v    |

| t <sub>MLMH</sub>                | t <sub>MR</sub>     | MR minimum pulse width                  |                                                                                   | 1                                         |     |                     | μs   |

| t <sub>MLRL</sub>                | t <sub>MRD</sub>    | MR to RST output delay                  |                                                                                   |                                           | 200 |                     |      |

|                                  |                     | MR glitch immunity                      |                                                                                   |                                           | 100 |                     | ns   |

|                                  |                     | MR pull-up resistance                   |                                                                                   |                                           | 10  |                     | kΩ   |

### Table 4. DC and AC characteristics (continued)

1. Valid for ambient operating temperature:  $T_A = -40$  °C to +85 °C;  $V_{CC} = 0.8$  V to 5.5 V (except where noted).

2. 10 k $\Omega$  (typ) internal pull-up resistor.

3. The leakage current measured on the  $\overline{RST}$  pin is tested with the reset de-asserted (output high impedance).

4. Other reset threshold voltages are offered. Minimum order quantities may apply. Contact local sales office for availability.

5. Other t<sub>REC</sub> time-out periods are offered. Minimum order quantities may apply. Contact local sales office for availability.

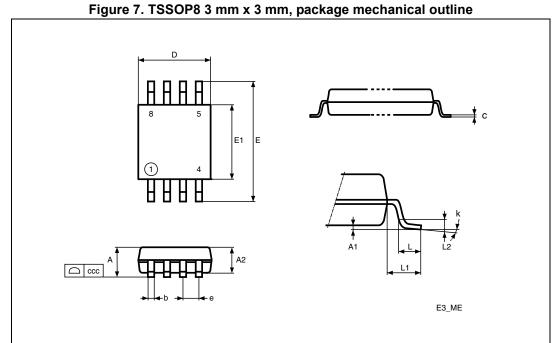

## 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

14/19

| Table 5. TSSOP8 3 mm x 3 mm, package mechanical data |      |      |       |        |       |       |  |

|------------------------------------------------------|------|------|-------|--------|-------|-------|--|

| Cumhal                                               |      | mm   |       | inches |       |       |  |

| Symbol                                               | Min  | Тур  | Мах   | Min    | Тур   | Мах   |  |

| А                                                    |      |      | 1.100 |        |       | 0.043 |  |

| A1                                                   | 0.00 |      | 0.15  | 0.000  |       | 0.006 |  |

| A2                                                   | 0.75 | 0.85 | 0.95  | 0.030  | 0.034 | 0.037 |  |

| b                                                    | 0.22 |      | 0.40  | 0.009  |       | 0.016 |  |

| С                                                    | 0.08 |      | 0.23  | 0.003  |       | 0.009 |  |

| ссс                                                  |      |      | 0.10  |        |       | 0.004 |  |

| D                                                    | 2.80 | 3.00 | 3.20  | 0.110  | 0.118 | 0.126 |  |

| е                                                    |      | 0.65 |       |        | 0.026 |       |  |

| Е                                                    | 4.65 | 4.90 | 5.15  | 0.183  | 0.193 | 0.203 |  |

| E1                                                   | 2.80 | 3.00 | 3.10  | 0.110  | 0.118 | 0.122 |  |

| L                                                    | 0.40 | 0.60 | 0.80  | 0.016  | 0.024 | 0.032 |  |

| L1                                                   |      | 0.95 |       |        | 0.037 |       |  |

| L2                                                   |      | 0.25 |       |        | 0.010 |       |  |

| k                                                    | 0°   | 4    | 6°    | 0°     | 4     | 6°    |  |

| Ν                                                    |      | 8    |       |        | 8     |       |  |

## 8 Part numbering

|                  |                     | Tab                     | le 6. Ordering infor | mation s | cheme |    |       |   |

|------------------|---------------------|-------------------------|----------------------|----------|-------|----|-------|---|

| Exampl           | e:                  |                         | STM6905              | тz<br>   | E<br> | DS | 6<br> | I |

| Device           | type                |                         |                      |          |       |    |       |   |

| STM69            |                     |                         |                      |          |       |    |       |   |

| Reset t          | hreshold            | voltages <sup>(1)</sup> |                      |          |       |    |       |   |

| Suffix           | V <sub>RST1</sub>   | V <sub>RST2</sub>       |                      |          |       |    |       |   |

| ΤZ               | 3.078               | 2.333                   |                      |          |       |    |       |   |

| TW               | 3.078               | 1.683                   |                      |          |       |    |       |   |

| TG               | 3.078               | 1.110                   |                      |          |       |    |       |   |

| SY               | 2.955               | 2.188                   |                      |          |       |    |       |   |

| SF               | 2.955               | 1.050                   |                      |          |       |    |       |   |

| PW               | 2.866               | 1.683                   |                      |          |       |    |       |   |

| t <sub>REC</sub> |                     |                         |                      |          |       |    |       |   |

| B = 30 ı         | ms <sup>(1)</sup>   |                         |                      |          |       |    |       |   |

| C = 120          | ) ms <sup>(1)</sup> |                         |                      |          |       |    |       |   |

| E = 210          | ) ms                |                         |                      |          |       |    |       |   |

| F = 420          | ms <sup>(1)</sup>   |                         |                      |          |       |    |       |   |

| Packag           | le                  |                         |                      |          |       |    |       |   |

| DS = M           | SOP8 (TS            | SSOP8)                  |                      |          |       |    |       |   |

| Tempei           | rature rar          | ige                     |                      |          |       |    |       |   |

| 6: -40 °         | C to 85 °C          | ;                       |                      |          |       |    |       |   |

| Shippir          | ng metho            | d                       |                      |          |       |    |       |   |

| E = EC           | OPACK <sup>®</sup>  | package, tubes          |                      |          |       |    |       |   |

$F = ECOPACK^{\mathbb{R}}$  package, tape and reel

Other reset threshold voltages and t<sub>REC</sub> time-out periods are offered. Minimum order quantities may apply. Contact local sales office for availability.

## 9 Package marking information

| Part marking   | V <sub>RST1</sub> (V) | V <sub>RST2</sub> (V) | Package       | Topside marking |

|----------------|-----------------------|-----------------------|---------------|-----------------|

| STM6905TZEDS6F | 3.078                 | 2.333                 | MSOP (TSSOP8) | STZE            |

| STM6905TWEDS6F |                       | 1.683                 |               | STWE            |

| STM6905TGEDS6F |                       | 1.110                 |               | STGE            |

| STM6905SYEDS6F | 2.955                 | 2.188                 |               | SSYE            |

| STM6905SFEDS6F |                       | 1.050                 |               | SSFE            |

| STM6905PWEDS6F | 2.866                 | 1.683                 |               | SPWE            |

### Table 7. Marking description

## 10 Revision history

| ······································ |          |                                                                                                                                                                  |  |  |

|----------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Date                                   | Revision | Changes                                                                                                                                                          |  |  |

| 19-Dec-2007                            | 1        | Initial release.                                                                                                                                                 |  |  |

| 23-Jan-2008                            | 2        | Document status upgraded to full datasheet.                                                                                                                      |  |  |

| 28-Jan-2008                            | 3        | Updated cover page, Figure 6, and Table 4.                                                                                                                       |  |  |

| 20-Oct-2014                            | 4        | Small text changes to English<br><i>Table 1</i> : updated footnote <i>1</i><br><i>Table 6</i> : updated the reset threshold voltage of "SY" (V <sub>RST2</sub> ) |  |  |

### Table 8. Document revision history

### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2014 STMicroelectronics - All rights reserved