# LB11870

# Monolithic Digital IC For Polygonal Mirror Motors Three-Phase Brushless Motor Driver

## Overview

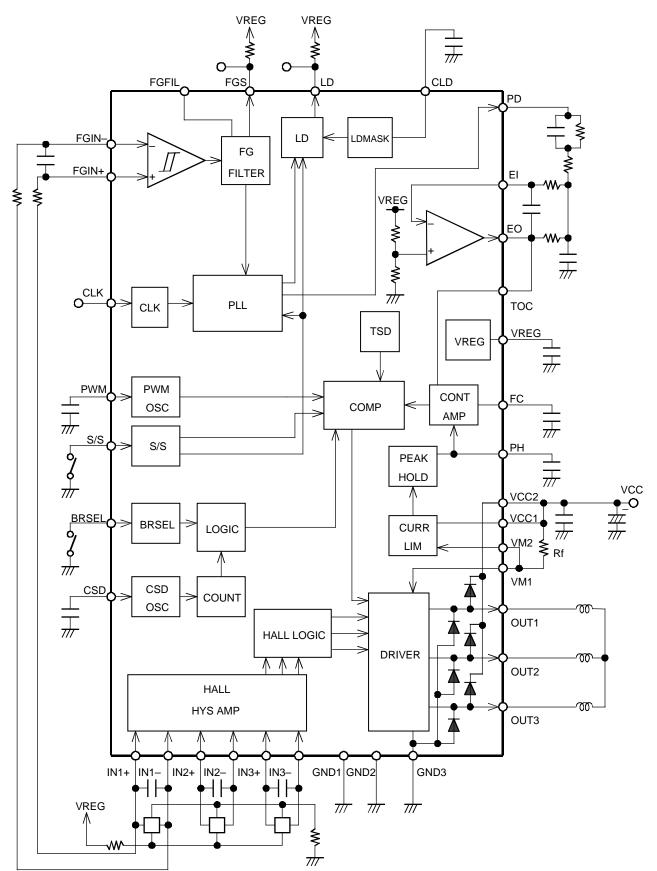

The LB11870 is a three-phase brushless motor driver developed for driving the motors used with the polygonal mirror in laser printers and plain paper copiers. It can implement, with a single IC chip, all the circuits required for polygonal mirror drive, including speed control and driver functions. The LB11870 can implement motor drive with minimal power loss due to its use of direct PWM drive.

## **Functions**

- Three-phase bipolar drive

- Direct PWM drive

- Includes six high and low side diodes on chip.

- Output current control circuit

- PLL speed control circuit

- Phase lock detection output (with masking function)

- Includes current limiter, thermal protection, rotor constraint protection, and low-voltage protection circuits on chip.

- Deceleration type switching circuit (free running or reverse torque)

- PWM oscillator

- Power saving circuit

## **Specifications**

## Absolute Maximum Ratings at $Ta = 25^{\circ}C$

| Parameter                     | Symbol              | Conditions                    | Ratings     | Unit |

|-------------------------------|---------------------|-------------------------------|-------------|------|

| Supply voltage                | V <sub>CC</sub> max |                               | 30          | V    |

| Output current                | I <sub>O</sub> max  | T ≤ 500ms *1                  | 2.3         | А    |

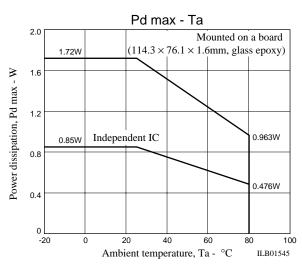

| Allowable power dissipation 1 | Pd max1             | Independent IC                | 0.85        | W    |

| Allowable power dissipation 2 | Pd max2             | Mounted on a circuit board *2 | 1.72        | W    |

| Operating temperature         | Topr                |                               | -20 to +80  | °C   |

| Storage temperature           | Tstg                |                               | -55 to +150 | °C   |

Note \*1: Be sure to perform derating from the standard value by 20% or more before use.

Note \*2: Mounted on a specified board: 114.3mm×76.1mm×1.6mm, glass epoxy

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

#### Allowable Operating Ranges at $Ta = 25^{\circ}C$

| Parameter                          | Symbol | Conditions | Ratings   | Unit |

|------------------------------------|--------|------------|-----------|------|

| Supply voltage range               | VCC    |            | 9.5 to 28 | V    |

| 5V constant voltage output current | IREG   |            | 0 to -20  | mA   |

| LD pin applied voltage             | VLD    |            | 0 to 28   | V    |

| LD pin output current              | ILD    |            | 0 to 15   | mA   |

| FGS pin applied voltage            | VFG    |            | 0 to 28   | V    |

| FGS pin output current             | IFG    |            | 0 to 10   | mA   |

#### **Electrical Characteristics** at $Ta = 25^{\circ}C$ , $V_{CC} = VM = 24V$

| Parameter                           | Symbol                 | Conditions                                                          |      | Ratings |          | unit  |

|-------------------------------------|------------------------|---------------------------------------------------------------------|------|---------|----------|-------|

| Faranielei                          | Symbol                 | Conditions                                                          | min  | typ     | max      | unit  |

| Supply current 1                    | I <sub>CC</sub> 1      |                                                                     |      | 16      | 21       | mA    |

| Supply current 2                    | I <sub>CC</sub> 2      | In stop mode                                                        |      | 3.5     | 5.0      | mA    |

| [5V constant voltage output circuit | :]                     |                                                                     |      |         |          |       |

| Output voltage                      | VREG                   |                                                                     | 4.65 | 5.0     | 5.35     | V     |

| Voltage regulation                  | ∆VREG1                 | V <sub>CC</sub> =9.5 to 28V                                         |      | 80      | 130      | mV    |

| Load regulation                     | $\Delta VREG2$         | I <sub>O</sub> =-5 to -20mA                                         |      | 10      | 60       | mV    |

| Temperature coefficient             | ∆VREG3                 | Design target value*                                                |      | 0       |          | mV/°C |

| [Output Block]                      |                        |                                                                     |      |         |          |       |

| Output saturation voltage 1         | V <sub>O</sub> sat1    | I <sub>O</sub> =0.5A, V <sub>O</sub> (SINK)+V <sub>O</sub> (SOURCE) |      | 1.9     | 2.4      | V     |

| Output saturation voltage 2         | V <sub>O</sub> sat2    | I <sub>O</sub> =1.2A, V <sub>O</sub> (SINK)+V <sub>O</sub> (SOURCE) |      | 2.6     | 3.2      | V     |

| Output leakage current              | I <sub>O</sub> leak    |                                                                     |      |         | 100      | μΑ    |

| Lower diode forward voltage 1       | VD1-1                  | ID=-0.5A                                                            |      | 1.0     | 1.3      | V     |

| Lower diode forward voltage 2       | VD1-2                  | ID=-1.2A                                                            |      | 1.4     | 1.8      | V     |

| Upper diode forward voltage 1       | VD2-1                  | ID=0.5A                                                             |      | 1.2     | 1.6      | V     |

| Upper diode forward voltage 2       | VD2-2                  | ID=1.2A                                                             |      | 1.9     | 2.4      | V     |

| [Hall Amplifier Block]              |                        |                                                                     |      |         |          |       |

| Input bias current                  | IHB                    |                                                                     | -2   | -0.5    |          | μΑ    |

| Common-mode input voltage range     | VICM                   |                                                                     | 0    |         | VREG-2.0 | V     |

| Hall input sensitivity              |                        |                                                                     | 80   |         |          | mVp-p |

| Hysteresis width                    | ∆V <sub>IN</sub> (HA)  |                                                                     | 15   | 24      | 42       | mV    |

| Input voltage: Low to high          | VSLH                   |                                                                     |      | 12      |          | mV    |

| Input voltage: High to low          | VSHL                   |                                                                     |      | -12     |          | mV    |

| [FG Schmitt Block]                  |                        |                                                                     |      |         |          |       |

| Input bias current                  | IB(FGS)                |                                                                     | -2   | -0.5    |          | μΑ    |

| Common-mode input voltage range     | VICM(FGS)              |                                                                     | 0    |         | VREG-2.0 | V     |

| Input sensitivity                   | V <sub>IN</sub> (FGS)  |                                                                     | 80   |         |          | mVp-p |

| Hysteresis width                    | ∆V <sub>IN</sub> (FGS) |                                                                     | 15   | 24      | 42       | mV    |

| Input voltage: Low to high          | VSLH(FGS)              |                                                                     |      | 12      |          | mV    |

| Input voltage: High to low          | VSHL(FGS)              |                                                                     |      | -12     |          | mV    |

\*: These value are design guarantee values, and are not tested.

| Parameter                         | Symbol                | Conditions                                     | Ratings  |          |      | unit |

|-----------------------------------|-----------------------|------------------------------------------------|----------|----------|------|------|

| Falameter                         | Symbol                | Conditions                                     | min      | typ      | max  | unit |

| [PWM Oscillator]                  | -                     |                                                |          |          |      |      |

| High-level output voltage         | V <sub>OH</sub> (PWM) |                                                | 2.65     | 2.95     | 3.25 | V    |

| Low-level output voltage          | V <sub>OL</sub> (PWM) |                                                | 0.9      | 1.2      | 1.5  | V    |

| External capacitor charge current | ICHG                  | VPWM=2V                                        | -60      | -45      | -30  | μA   |

| Oscillator frequency              | f(PWM)                | C=680pF                                        |          | 34       |      | kHz  |

| Amplitude                         | V(PWM)                |                                                | 1.45     | 1.75     | 2.05 | Vp-p |

| [FGS Output]                      |                       |                                                |          |          |      |      |

| Output saturation voltage         | V <sub>OL</sub> (FGS) | IFGS=7mA                                       |          | 0.15     | 0.5  | V    |

| Output leakage current            | IL(FGS)               | V <sub>O</sub> =V <sub>CC</sub>                |          |          | 10   | μA   |

| [CSD Oscillator Circuit]          |                       |                                                |          |          |      |      |

| High-level output voltage         | V <sub>OH</sub> (CSD) |                                                | 3.2      | 3.5      | 3.8  | V    |

| Low-level output voltage          | V <sub>OL</sub> (CSD) |                                                | 0.9      | 1.1      | 1.3  | V    |

| Amplitude                         | V(CSD)                |                                                | 2.15     | 2.4      | 2.65 | Vp-p |

| External capacitor charge current | ICHG1                 |                                                | -13.5    | -9.5     | -5.5 | μA   |

| External capacitor charge         | ICHG2                 |                                                | 6        | 10       | 14   | μA   |

| current                           |                       |                                                |          |          |      |      |

| Oscillator frequency              | f(CSD)                | C=0.068µF                                      |          | 29       |      | Hz   |

| [Phase Comparator Output]         |                       |                                                |          |          |      |      |

| High-level output voltage         | VPDH                  | I <sub>OH</sub> =-100μA                        | VREG-0.2 | VREG-0.1 |      | V    |

| Low-level output voltage          | VPDL                  | I <sub>OL</sub> =100μA                         |          | 0.2      | 0.3  | V    |

| Output source current             | IPD+                  | VPD=VREG/2                                     |          |          | -0.5 | mA   |

| Output sink current               | IPD-                  | VPD=VREG/2                                     | 1.5      |          |      | mA   |

| [Lock Detection Output]           |                       | ·                                              | · ·      | -        |      |      |

| Output saturation voltage         | V <sub>OL</sub> (LD)  | ILD=10mA                                       |          | 0.15     | 0.5  | V    |

| Output leakage current            | IL(LD)                | VO=VCC                                         |          |          | 10   | μA   |

| [Error Amplifier Block]           |                       |                                                |          |          |      |      |

| Input offset voltage              | V <sub>IO</sub> (ER)  | Design target value*                           | -10      |          | 10   | mV   |

| Input bias current                | IB(ER)                |                                                | -1       |          | 1    | μA   |

| Output H level voltage            | V <sub>OH</sub> (ER)  | Ι <sub>ΟΗ</sub> =-500μΑ                        | VREG-1.2 | VREG-0.9 |      | V    |

| Output L level current            | V <sub>OL</sub> (ER)  | I <sub>OL</sub> =500μA                         |          | 0.9      | 1.2  | V    |

| DC bias level                     | VB(ER)                |                                                | -5%      | VREG/2   | 5%   | V    |

| [Current limiter Circuit]         |                       |                                                | I        |          |      |      |

| Drive gain 1                      | GDF1                  | When the phase is locked                       | 0.4      | 0.5      | 0.6  | deg  |

| Drive gain 2                      | GDF2                  | When not locked                                | 0.8      | 1.0      | 1.2  | deg  |

| Limiter voltage                   | VRF                   | V <sub>CC</sub> -VM                            | 0.45     | 0.5      | 0.55 | V    |

| [Thermal Shutdown Operation]      |                       | 60                                             |          |          |      |      |

| Thermal shutdown operating        | TSD                   | Design target value*                           | 150      | 175      |      | °C   |

| temperature                       |                       | (junction temperature)                         |          |          |      |      |

| Hysteresis width                  | ΔTSD                  | Design target value*<br>(junction temperature) |          | 40       |      | °C   |

| [Low-Voltage Protection]          |                       |                                                |          |          |      |      |

| Operating voltage                 | VSD                   |                                                | 8.1      | 8.45     | 8.9  | V    |

| Hysteresis width                  | ΔVSD                  |                                                | 0.2      | 0.35     | 0.5  | V    |

\*: These value are design guarantee values, and are not tested.

| Parameter                 | Complete A              | Constitution of          |          | Ratings |      |      |

|---------------------------|-------------------------|--------------------------|----------|---------|------|------|

| Parameter                 | Symbol                  | Conditions               | min      | typ     | max  | unit |

| [CLD Circuit]             |                         |                          |          |         |      |      |

| External capacitor charge | ICLD                    |                          | -6       | -4.3    | -3   | μΑ   |

| current                   |                         |                          |          |         |      |      |

| Operating voltage         | V <sub>H</sub> (CLD)    |                          | 3.25     | 3.5     | 3.75 | V    |

| [CLK Pin]                 |                         |                          |          |         |      |      |

| External input frequency  | fI(CLK)                 |                          | 0.1      |         | 10   | kHz  |

| High-level input voltage  | V <sub>IH</sub> (CLK)   |                          | 3.5      |         | VREG | V    |

| Low-level input voltage   | V <sub>IL</sub> (CLK)   |                          | 0        |         | 1.5  | V    |

| Input open voltage        | V <sub>IO</sub> (CLK)   |                          | VREG-0.5 |         | VREG | V    |

| Hysteresis width          | V <sub>IS</sub> (CLK)   |                          | 0.35     | 0.5     | 0.65 | V    |

| High-level input current  | I <sub>IH</sub> (CLK)   | VCLK=VREG                | -10      | 0       | 10   | μA   |

| Low-level input current   | I <sub>IL</sub> (CLK)   | VCLK=0V                  | -280     | -210    |      | μΑ   |

| [S/S Pin]                 |                         |                          |          |         |      |      |

| High-level input voltage  | V <sub>IH</sub> (SS)    |                          | 3.5      |         | VREG | V    |

| Low-level input voltage   | V <sub>IL</sub> (SS)    |                          | 0        |         | 1.5  | V    |

| Input open voltage        | V <sub>IO</sub> (SS)    |                          | VREG-0.5 |         | VREG | V    |

| Hysteresis width          | V <sub>IS</sub> (SS)    |                          | 0.35     | 0.5     | 0.65 | V    |

| High-level input current  | I <sub>IH</sub> (SS)    | VS/S=VREG                | -10      | 0       | 10   | μA   |

| Low-level input current   | I <sub>IL</sub> (SS)    | VS/S=0V                  | -280     | -210    |      | μΑ   |

| [BRSEL Pin]               |                         |                          |          |         |      |      |

| High-level input voltage  | V <sub>IH</sub> (BRSEL) |                          | 3.5      |         | VREG | V    |

| Low-level input voltage   | V <sub>IL</sub> (BRSEL) |                          | 0        |         | 1.5  | V    |

| Input open voltage        | V <sub>IO</sub> (BRSEL) |                          | VREG-0.5 |         | VREG | V    |

| High-level input current  | I <sub>IH</sub> (BRSEL) | V <sub>BRSEL</sub> =VREG | -10      | 0       | 10   | μΑ   |

| Low-level input current   | I <sub>IL</sub> (BRSEL) | VBRSEL=0V                | -220     | -160    |      | μA   |

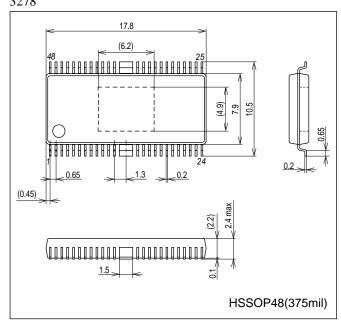

## Package Dimensions

unit : mm (typ) 3278

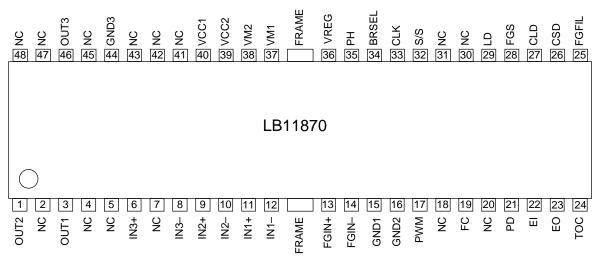

## **Pin Assignment**

## Three-Phase Logic Truth Table (IN = [H] indicates a condition in which: IN+ > IN–)

| IN1 | IN2 | IN3 | OUT1 | OUT2 | OUT3 |

|-----|-----|-----|------|------|------|

| н   | L   | н   | L    | н    | М    |

| н   | L   | L   | L    | М    | Н    |

| н   | н   | L   | М    | L    | н    |

| L   | н   | L   | Н    | L    | М    |

| L   | н   | Н   | Н    | М    | L    |

| L   | L   | Н   | М    | н    | L    |

## **Pin Functions**

| Pin No.  | Symbol                                   | Pin Description                                                                                                                                                                | Equivalent Circuit                             |

|----------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| 3        | OUT1                                     | Motor drive output                                                                                                                                                             | $\frown$                                       |

| 1        | OUT2                                     |                                                                                                                                                                                |                                                |

| 46       | OUT3                                     |                                                                                                                                                                                | V <sub>CC1</sub>                               |

| 44       | GND3                                     | Output block ground                                                                                                                                                            |                                                |

| 37       | VM1                                      | Output block power supply and current                                                                                                                                          |                                                |

| 38       | VM2                                      | detection.<br>Insert the resistor Rf between this pin and<br>$V_{CC}$ 1.<br>The output current will be limited to the current<br>value<br>$I_{OUT} = VRF/Rf$ .                 |                                                |

| 39       | V <sub>CC</sub> 2                        | Upper diode cathode connection. Short this pin to $V_{CC}$ 1.                                                                                                                  |                                                |

| 11       | IN1+                                     | Hall element inputs.                                                                                                                                                           | VEG                                            |

| 12       | IN1-                                     | The high state is when IN+ is greater than IN-,                                                                                                                                |                                                |

| 9        | IN2+                                     | and the low state is the reverse.                                                                                                                                              |                                                |

| 10       | IN2-                                     | An amplitude of at least 100mVp-p (differential)                                                                                                                               |                                                |

| 6        | IN3+                                     | is desirable for the Hall element signal inputs. If                                                                                                                            |                                                |

| 8        | IN3-                                     | noise on the Hall signals is a problem, insert capacitors between the IN+ and IN- inputs.                                                                                      |                                                |

|          |                                          |                                                                                                                                                                                |                                                |

| 13<br>14 | FG <sub>IN</sub> +<br>FG <sub>IN</sub> - | FG input.<br>If noise on the FG signal input is a problem,<br>connect a filter consisting of either a capacitor<br>or a capacitor and a resistor.                              | VREG<br>VREG<br>30000<br>(13)<br>30000<br>(14) |

|          |                                          |                                                                                                                                                                                |                                                |

| 15       | GND1                                     | Control circuit block ground                                                                                                                                                   |                                                |

| 16       | GND2                                     | SUBGND pin                                                                                                                                                                     |                                                |

| 17       | PWM                                      | Sets the PWM oscillator frequency.<br>Insert a capacitor between this pin and ground.<br>The PWM oscillator frequency is set to about<br>34kHz when a 680pF capacitor is used. | VREG                                           |

## LB11870

| Continued f | from precedir |                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.     | Symbol        | Pin Description                                                                                                                                                                                                                                      | Equivalent Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 19          | FC            | Frequency characteristics correction for the current control circuit.<br>Insert a capacitor (about 0.01 to 0.1µF) between this pin and ground.<br>The output duty is determined by comparing the voltage on this pin to the PWM oscillator waveform. | VREG<br>VIEG<br>VIEG<br>VIEG<br>VIEG<br>VIEG<br>VIEG<br>VIEG<br>VI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 21          | PD            | Phase comparator output.<br>The phase error is converted to a pulse duty<br>and output from this pin.                                                                                                                                                | VREG<br>300Ω<br>21)<br>7/7 7/7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 22          | EI            | Error amplifier input.                                                                                                                                                                                                                               | VREG<br>VREG<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 23          | EO            | Error amplifier output.                                                                                                                                                                                                                              | VREG<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS)<br>(CS) |

| 24          | TOC           | Torque command voltage input.<br>This pin is normally connected to the EO pin.<br>When the TOC voltage falls, the lower output<br>transistor on duty is increased.                                                                                   | VREG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Continued f | from precedir | ng page.                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                   |

|-------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| Pin No.     | Symbol        | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                 | Equivalent Circuit                                                                                |

| 25          | FGFIL         | FG filter connection.<br>If noise on the FG signal input is a problem,<br>insert a capacitor (up to about 2200pF)<br>between this pin and ground.                                                                                                                                                                                                                                                                               | VREG<br>(25)<br>(25)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1                       |

| 26          | CSD           | Sets the rotor constraint protection circuit<br>operating time and the initial reset pulse.<br>A protection operating time of about 8 seconds<br>can be set by insert a capacitor of about<br>$0.068\mu$ F between this pin and ground. If the<br>rotor constraint protection circuit is not used,<br>insert a resistor and a capacitor in parallel<br>between this pin and ground. (Values: about<br>220k $\Omega$ and 4700pF) | VREG<br>VREG<br>W<br>W<br>Z<br>Z<br>Z<br>Z<br>Z<br>Z<br>Z<br>Z<br>Z<br>Z<br>Z<br>Z<br>Z<br>Z<br>Z |

| 27          | CLD           | Sets the phase lock state signal mask time.<br>A mask time of about 90ms can be set by<br>inserting a capacitor of about 0.1µF between<br>this pin and ground.<br>Leave this pin open if masking is not required.                                                                                                                                                                                                               | VREG<br>300Ω<br>300Ω<br>27<br>7/7<br>7/7<br>7/7                                                   |

| 28          | FGS           | FG Schmitt output.                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                   |

| 29          | LD            | Phase lock state detection output.<br>This output goes to the on state (low level)<br>when the phase is locked.                                                                                                                                                                                                                                                                                                                 | 29<br>7/7 7/7 7/7                                                                                 |

| Continued f | rom precedir | ng page.                                                                                                                                                                                                                                                                                          |                    |

|-------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Pin No.     | Symbol       | Pin Description                                                                                                                                                                                                                                                                                   | Equivalent Circuit |

| 32          | S/S          | Start/stop control input.<br>Low: 0 to 1.5V<br>High: 3.5V to VREG<br>Hysteresis: 0.5V<br>Low: start.<br>This pin goes to the high level when open.                                                                                                                                                | VREG               |

| 33          | CLK          | Clock input.<br>Low: 0 to 1.5V<br>High: 3.5V to VREG<br>Hysteresis: $0.5V$<br>$f_{CLK} = 10$ kHz (maximum)<br>If noise is a problem, use a capacitor to remove<br>that noise at this input.                                                                                                       | VREG               |

| 34          | BRSEL        | Deceleration switching control input.<br>Low: 0 to 1.5V<br>High: 3.5V to VREG<br>This pin goes to the high level when open.<br>Low: reverse torque control, High: free running.<br>An external Schottky barrier diode is required<br>on the output low side if reverse torque control<br>is used. | VREG               |

| 35          | PH           | RF waveform smoothing.<br>If noise on the RF waveform is a problem,<br>insert a capacitor between this pin and ground.                                                                                                                                                                            | VREG               |

| Pin No.                                                        | Symbol            | Pin Description                                                                                                                    | Equivalent Circuit |

|----------------------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| 36                                                             | VREG              | Stabilized power supply output (5V output).<br>Insert a capacitor of about 0.1µF between this<br>pin and ground for stabilization. |                    |

| 40                                                             | V <sub>CC</sub> 1 | Power supply.<br>Insert a capacitor of at least 10µF between this<br>pin and ground to prevent noise from entering<br>the IC.      |                    |

| 2, 4, 5<br>7, 18<br>20, 30<br>31, 41<br>42, 43<br>45, 47<br>48 | NC                | Since these pins are not connected to the IC internally, they can be used for wiring connections.                                  |                    |

|                                                                | FRAME             | Connect this pin to ground.                                                                                                        |                    |

## Overview of the LB11870

#### 1. Speed Control Circuit

This IC adopts a PLL speed control technique and provides stable motor operation with high precision and low jitter. This PLL circuit compares the phase error at the edges of the CLK signal (falling edges) and FG signal (falling edges on the FGIN+ and FGS signals), and the IC uses the detected error to control motor speed.

During this control operation, the FG servo frequency will be the same as the CLK frequency.

$f_{FG}$  (servo) =  $f_{CLK}$

#### 2. Output Drive Circuit

To minimize power loss in the output circuits, this IC adopts a direct PWM drive technique. The output transistors are always saturated when on, and the IC adjusts the motor drive output by changing the output on duty. The low side output transistor is used for the output PWM switching.

Both the high and low side output diodes are integrated in the IC. However, if reverse torque control mode is selected for use during deceleration, or if a large output current is used and problems occur (such as incorrect operation or waveform disruption due to low side kickback), a Schottky diode should be inserted between OUT and ground. Also, if it is necessary to reduce IC heating during steady-state (constant speed) operation, it may be effective to insert a Schottky diode between  $V_{CC}$  and OUT. (This is effective because the load associated with the regenerative current during PWM switching is born not by the on-chip diode but by the external diode.)

#### 3. Current Limiter Circuit

The current limiter circuit limits the peak level of the current to a level determined by I = VRF/Rf (where VRF = 0.5V (typical) and Rf is the value of the current detection resistor). The current limiter operates by reducing the output on duty to suppress the current.

The current limiter circuit detects the reverse recovery current of the diode due to PWM operation. To assure that the current limiting function does not malfunction, its operation has a delay of about  $2\mu$ s. If the motor coils have a low resistance or a low inductance, current fluctuations at startup (when there is no reactive power in the motor) will be rapid. The delay in this circuit means that at such times the current limiter circuit may operate at a point well above the set current. Designers must take this increase in the current due to the delay into account when setting the current limiter value.

#### 4. Power Saving Circuit

This IC goes into a power saving state that reduces the current drain in the stop state. The power saving state is implemented by removing the bias current from most of the circuits in the IC. However, the 5V regulator output is provided in the power saving state.

#### 5. Reference Clock

Care must be taken to assure that no chattering or other noise is present on the externally input clock signal. Although the input circuit does have hysteresis, if problems do occur, the noise must be excluded with a capacitor. If the IC is set to the start state when the reference clock signal is not present, if the rotor constraint protection circuit is used, the motor will turn somewhat and then motor drive will be shut off. However, if the rotor constraint protection circuit is not used, and furthermore reverse torque control mode is selected for deceleration, the motor will be driven at ever increasing speed in the reverse direction. (This is because the rotor constraint protection circuit oscillator signal is used for clock cutoff protection.) Applications must implement a workaround for this problem if there is any possibility whatsoever for it to occur.

#### 6. Notes on the PWM Frequency

The PWM frequency is determined by the value of the capacitor C (in F) connected to the PWM pin.

$f_{PWM} \approx 1 / (43000 \times C)$

If a 680pF capacitor is used, the circuit will oscillate at about 34kHz. If the PWM frequency is too low, the motor will emit switching noise, and if it is too high, the power loss in the output will be excessive. A PWM frequency in the range 15 to 50kHz is desirable. To minimize the influence of the output on this circuit, the ground lead of this capacitor should be connected as close as possible to the IC control system ground (the GND1 pin).

#### 7. Hall Input Signals

Signals with an amplitude in excess of the hysteresis (42mV maximum) must be provided as the Hall input signals. However, an amplitude of over 100mV is desirable to minimize the influence of noise. If the output waveforms are disturbed (at phase switching) due to noise on the Hall inputs, insert capacitors across these inputs.

#### 8. FG Input Signal

Normally, one phase of the Hall signals is input as the FG signal. If noise is a problem the input must be filtered with either a capacitor or an RC filter circuit. Although it is also possible to remove FG signal noise by inserting a capacitor between the FGFIL pin and ground, the IC may not be able to operate correctly if this signal is damped excessively. If this capacitor is used, its value must be less than about 2200pF. If the location of this capacitor's ground lead is inappropriate, it may, inversely, make noise problems even more likely to occur. Thus the ground lead location must be chosen carefully.

#### 9. Rotor Constraint Protection Circuit

This IC provides a rotor constraint protection circuit to protect the IC itself and the motor when the motor is constrained. If the LD output is high (unlocked) for over a certain fixed period with the IC in the start state, the low side transistor will be turned off. The time constant is determined by the capacitor connected to the CSD pin.

<time constant (in seconds)>  $\approx 120 \times C \ (\mu F)$

If a  $0.068\mu$ F capacitor is used, the protection time will be about 8 seconds. The set time must be selected to have an adequate margin with respect to the motor startup time. This protection circuit will not operate during deceleration when the clock frequency is switched. To clear the rotor constraint protection state, the IC must be set to the stopped state or the power must be turned off and reapplied.

Since the CSD pin also functions as the initial reset pulse generation pin at startup, the logic circuit will go to the reset state and the IC will not be able to function if this pin is connected to ground. Therefore, both a  $220k\Omega$  resistor and a 4700pF capacitor must be inserted between this pin and ground if the rotor constraint protection circuit is not used.

#### 10. Phase Lock Signal

#### (1) Phase lock range

Since this IC does not include a counter or similar functionality in the speed control system, the speed error range in the phase locked state cannot be determined solely by IC characteristics. (This is because the acceleration of the changes in the FG frequency influences the range.) When it is necessary to stipulate this characteristic for the motor, the designer must determine this by measuring the actual motor state. Since speed errors occur easily in states where the FG acceleration is large, it is thought that the speed errors will be the largest during lock pull-in at startup and when unlocked due to switching clock frequencies.

(2) Masking function for the phase lock state signal

A stable lock signal can be provided by masking the short-term low-level signals due to hunting during lock pullin. However, this results in the lock state signal output being delayed by the masking time.

The masking time is determined by the capacitor inserted between the CLD pin and ground.

<masking time (seconds) $> \approx 0.9 \times C (\mu F)$

When a  $0.1\mu$ F capacitor is used, the masking time will be about 90ms. In cases where complete masking is required, a masking time with fully adequate margin must be used. If no masking is required, leave the CLD pin open.

#### 11. Power Supply Stabilization

Since this IC provides a large output current and adopts a switching drive technique, the power supply line level can be disrupted easily. Thus capacitors large enough to stabilize the power supply voltage must be inserted between the  $V_{CC}$  pins and ground. The ground leads of these capacitors must be connected to the three pins that are the power grounds, and they must be connected as close as possible to the pins themselves. If these capacitors (electrolytic capacitors) cannot be connected close to their corresponding pins, ceramic capacitors of about  $0.1\mu$ F must be connected near these pins.

If reverse torque control mode is selected for use during deceleration, since there are states where power is returned to the power supply system, the power supply line levels will be particularly easily disrupted. Since the power line level is most easily disrupted during lock pull-in at high motor speeds, this state needs extra attention; in particular, capacitors that are adequately large to handle this situation must be selected.

If diodes are inserted in the power supply lines to prevent destruction of the device if the power supply is connected with reverse polarity, the power supply line levels will be even more easily disrupted, and even larger capacitors must be used.

#### 12. VREG Stabilization

A capacitor of at least  $0.1\mu$ F must be used to stabilize the VREG voltage, which is the control circuit power supply. The ground lead of that capacitor must be connected as close as possible to the IC control system ground (GND1).

#### 13. Error Amplifier External Component Values

To prevent adverse influence from noise, the error amplifier external components must be located as close to the IC as possible. In particular, they must be located as far from the motor as possible.

#### 14. FRAME Pin and the IC Metallic Rear Surface

The FRAME pin must be connected to the GND1 and GND2 pins, and the ground side of the electrolytic capacitor must be connected to GND3. The IC's metallic rear surface is connected to the FRAME pin internally to the IC. Thermal dissipation can be improved significantly by tightly bonding the metallic surface of the back of the IC package to the PCB with, for example, a solder with good thermal conductivity.

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typical" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affimative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.