### **ON Semiconductor**

#### Is Now

To learn more about onsemi™, please visit our website at www.onsemi.com

onsemi and Onsemi. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/ or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application,

## Fixed Frequency Current Mode Controller for Flyback Converters

The NCP1247 is a new fixed–frequency current–mode controller featuring the Dynamic Self–Supply. This function greatly simplifies the design of the auxiliary supply and the  $V_{CC}$  capacitor by activating the internal startup current source to supply the controller during start–up, transients, latch, stand–by etc. This device contains a special HV detector which detect the application unplug from the AC input line and triggers the X2 discharge current. This HV structure allows the brown–out detection as well.

It features a timer-based fault detection that ensures the detection of overload and an adjustable compensation to help keep the maximum power independent of the input voltage.

Due to frequency foldback, the controller exhibits excellent efficiency in light load condition while still achieving very low standby power consumption. Internal frequency jittering, ramp compensation, and a versatile latch input make this controller an excellent candidate for the robust power supply designs.

A dedicated Off mode allows to reach the extremely low no load input power consumption via "sleeping" whole device and thus minimize the power consumption of the control circuitry.

#### Features

- Fixed-Frequency Current-Mode Operation (65 kHz and 100 kHz frequency options)

- Frequency Foldback then Skip Mode for Maximized Performance in Light Load and Standby Conditions

- Timer-Based Overload Protection with Latched (Options A/C) or Auto-Recovery (Options B/D) Operation

- High-voltage Current Source with Brown-Out Detection and Dynamic Self-Supply, Simplifying the Design of the V<sub>CC</sub> Circuitry

- Frequency Modulation for Softened EMI Signature

- Adjustable Overpower Protection Dependant on the Bulk Voltage

- Latch-off Input Combined with the Overpower Protection Sensing Input

- V<sub>CC</sub> Operation up to 28 V, With Overvoltage Detection

- 500/800 mA Source/Sink Drive Peak Current Capability

- 10 ms Soft-Start

- Internal Thermal Shutdown

- No-Load Standby Power < 30 mW

- X2 Capacitor in EMI Filter Discharging Feature

- These Devices are Pb-Free and Halogen Free/BFR Free

#### ON Semiconductor®

www.onsemi.com

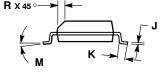

#### MARKING DIAGRAM

SOIC-7 CASE 751U

47Xfff = Specific Device Code

X = A, B, C or D

fff = 065 or 100

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

= Pb-Free Package

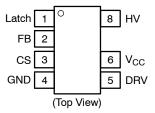

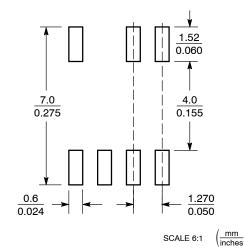

#### PIN CONNECTIONS

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 41 of this data sheet.

#### **Typical Applications**

- AC-DC Adapters for Notebooks, LCD, and Printers

- Offline Battery Chargers

- Consumer Electronic Power Supplies

- Auxiliary/Housekeeping Power Supplies

- Offline Adapters for Notebooks

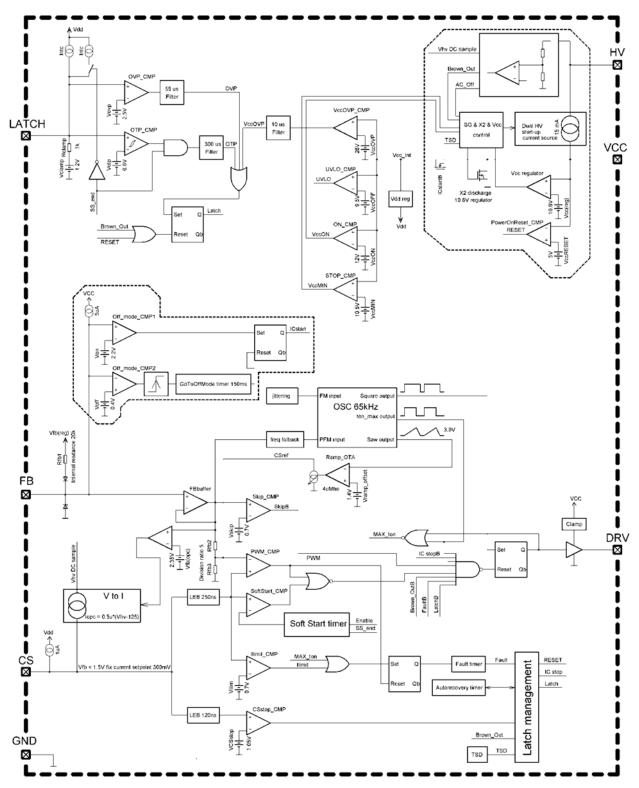

#### **TYPICAL APPLICATION EXAMPLE**

Figure 1. Flyback Converter Application Using the NCP1247

#### **OPTIONS**

| Part      | Option | Frequency | OCP Fault    | V <sub>HV(start)</sub> | V <sub>HV(stop)</sub> |

|-----------|--------|-----------|--------------|------------------------|-----------------------|

|           | А      | 65 kHz    | Latched      | 111 V                  | 103 V                 |

|           | A      | 100 kHz   | Latched      | 111 V                  | 103 V                 |

|           | В      | 65 kHz    | Autorecovery | 111 V                  | 103 V                 |

| NCP1247   | В      | 100 kHz   | Autorecovery | 111 V                  | 103 V                 |

| 1101 1247 | С      | 65 kHz    | Latched      | 95 V                   | 87 V                  |

|           | С      | 100 kHz   | Latched      | 95 V                   | 87 V                  |

|           | D      | 65 kHz    | Autorecovery | 95 V                   | 87 V                  |

|           | D      | 100 kHz   | Autorecovery | 95 V                   | 87 V                  |

#### PIN FUNCTION DESCRIPTION

| Pin No | Pin Name | Function                | Pin Description                                                                                                                                                                                                                                                            |

|--------|----------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | LATCH    | Latch-Off Input         | Pull the pin up or down to latch-off the controller. An internal current source allows the direct connection of an NTC for over temperature detection.                                                                                                                     |

| 2      | FB       | Feedback + Shutdown pin | An optocoupler collector to ground controls the output regulation. The part goes to the low consumption Off mode if the FB input pin is pulled to GND.                                                                                                                     |

| 3      | CS       | Current Sense           | This Input senses the Primary Current for current-mode operation, and offers an overpower compensation adjustment.                                                                                                                                                         |

| 4      | GND      | -                       | The controller ground                                                                                                                                                                                                                                                      |

| 5      | DRV      | Drive output            | Drives external MOSFET                                                                                                                                                                                                                                                     |

| 6      | VCC      | VCC input               | This supply pin accepts up to 28 Vdc, with overvoltage detection. The pin is connected to an external auxiliary voltage. It is not allowed to connect another circuit to this pin to keep low input power consumption.                                                     |

| 8      | HV       | High-voltage pin        | Connects to the rectified AC line to perform the functions of Start-up Current Source, Self-Supply, brown-out detection and X2 capacitor discharge function and the HV sensing for the overpower protection purposes. It is not allowed to connect this pin to DC voltage. |

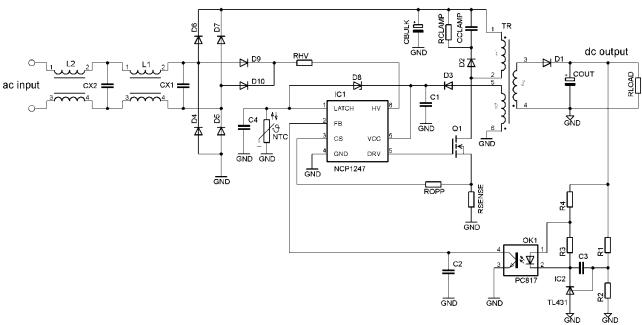

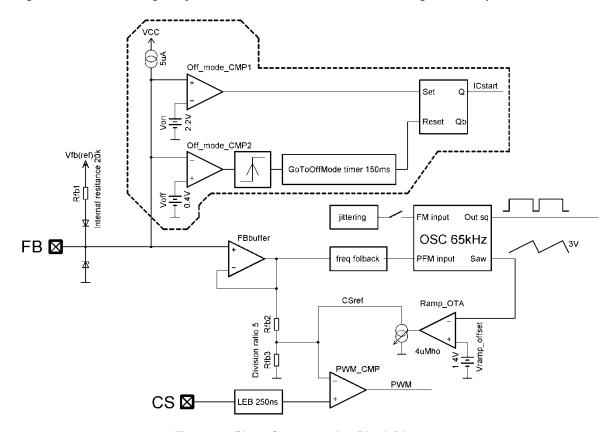

#### SIMPLIFIED INTERNAL BLOCK SCHEMATIC

Figure 2. Simplified Internal Block Schematic

#### **MAXIMUM RATINGS**

| Rating                     | Symbol                                                                                                                                                                     | Value                      | Unit    |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------|

| DRV<br>(pin 5)             | Maximum voltage on DRV pin (Dc-Current self-limited if operated within the allowed range) (Note 1)                                                                         | -0.3 to 20<br>±1000 (peak) | V<br>mA |

| V <sub>CC</sub><br>(pin 6) | V <sub>CC</sub> Power Supply voltage, V <sub>CC</sub> pin, continuous voltage<br>Power Supply voltage, V <sub>CC</sub> pin, continuous voltage (Note 1)                    | -0.3 to 28<br>±30 (peak)   | V<br>mA |

| HV<br>(pin 8)              | Maximum voltage on HV pin (Dc-Current self-limited if operated within the allowed range)                                                                                   | −0.3 to 500<br>±20         | V<br>mA |

| V <sub>max</sub>           | Maximum voltage on low power pins (except pin 5, pin 6 and pin 8) (Dc-Current self-limited if operated within the allowed range) (Note 1)                                  | -0.3 to 10<br>±10 (peak)   | V<br>mA |

| $R_{\theta J-A}$           | Thermal Resistance SOIC-7 Junction-to-Air, low conductivity PCB (Note 2) Junction-to-Air, medium conductivity PCB (Note 3) Junction-to-Air, high conductivity PCB (Note 4) | 162<br>147<br>115          | °C/W    |

| $R_{\theta J-C}$           | Thermal Resistance Junction-to-Case                                                                                                                                        | 73                         | °C/W    |

| $T_{JMAX}$                 | Operating Junction Temperature                                                                                                                                             | -40 to +150                | °C      |

| T <sub>STRGMAX</sub>       | Storage Temperature Range                                                                                                                                                  | -60 to +150                | °C      |

|                            | ESD Capability, HBM model (All pins except HV) per JEDEC Standard JESD22, Method A114E                                                                                     | > 2000                     | V       |

|                            | ESD Capability, Machine Model per JEDEC Standard JESD22, Method A115A                                                                                                      | > 200                      | V       |

|                            | ESD Capability, Charged Device Model per JEDEC Standard JESD22, Method C101D                                                                                               | > 1000                     | V       |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- This device contains latch-up protection and exceeds 100 mA per JEDEC Standard JESD78.

As mounted on a 80 x 100 x 1.5 mm FR4 substrate with a single layer of 50 mm<sup>2</sup> of 2 oz copper traces and heat spreading area. As specified for a JEDEC 51-1 conductivity test PCB. Test conditions were under natural convection or zero air flow.

- 3. As mounted on a 80 x 100 x 1.5 mm FR4 substrate with a single layer of 100 mm<sup>2</sup> of 2 oz copper traces and heat spreading area. As specified for a JEDEC 51-2 conductivity test PCB. Test conditions were under natural convection or zero air flow.

- 4. As mounted on a 80 x 100 x 1.5 mm FR4 substrate with a single layer of 650 mm<sup>2</sup> of 2 oz copper traces and heat spreading area. As specified for a JEDEC 51-3 conductivity test PCB. Test conditions were under natural convection or zero air flow.

$\textbf{ELECTRICAL CHARACTERISTICS} \text{ (For typical values } T_J = 25^{\circ}\text{C}, \text{ for min/max values } T_J = -40^{\circ}\text{C to } + 125^{\circ}\text{C}, \text{ V}_{HV} = 125 \text{ V}, \text{ } 125^{\circ}\text{C}, \text{ } 125^{\circ}\text{$ V<sub>CC</sub> = 11 V unless otherwise noted)

| Characteristics                                                                                          | Test Condition                                                                            | Symbol                                                  | Min         | Тур          | Max         | Unit |

|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------|-------------|--------------|-------------|------|

| HIGH VOLTAGE CURRENT SOURCE                                                                              |                                                                                           |                                                         |             |              |             |      |

| Minimum voltage for current source operation                                                             |                                                                                           | V <sub>HV(min)</sub>                                    | -           | 30           | 40          | ٧    |

| Current flowing out of V <sub>CC</sub> pin (X2 discharge current value is equal to I <sub>start2</sub> ) | $V_{CC} = 0 \text{ V}$ $V_{CC} = V_{CC(on)} - 0.5 \text{ V}$                              | I <sub>start1</sub><br>I <sub>start2</sub>              | 0.2<br>5    | 0.5<br>8     | 0.8<br>11   | mA   |

| Off-state leakage current                                                                                | V <sub>HV</sub> = 500 V, V <sub>CC</sub> = 15 V                                           | I <sub>start(off)</sub>                                 | 10          | 25           | 50          | μΑ   |

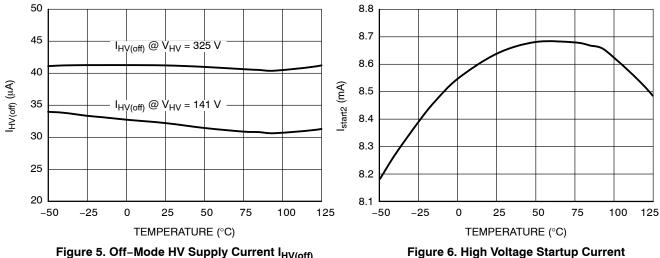

| Off-mode HV supply current                                                                               | $V_{HV}$ = 141 V,<br>$V_{HV}$ = 325 V,<br>$V_{CC}$ loaded by 4.7 $\mu$ F cap              | I <sub>HV(off)</sub>                                    | <u> </u>    | 45<br>50     | 60<br>70    | μΑ   |

| SUPPLY                                                                                                   |                                                                                           |                                                         |             |              |             |      |

| HV current source regulation threshold                                                                   |                                                                                           | V <sub>CC(reg)</sub>                                    | 8           | 11           | -           | V    |

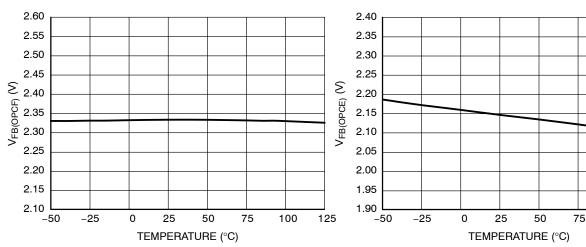

| Turn-on threshold level, V <sub>CC</sub> going up<br>HV current source stop threshold                    |                                                                                           | V <sub>CC(on)</sub>                                     | 11.0        | 12.0         | 13.0        | V    |

| HV current source restart threshold                                                                      |                                                                                           | V <sub>CC(min)</sub>                                    | 9.5         | 10.5         | 11.5        | V    |

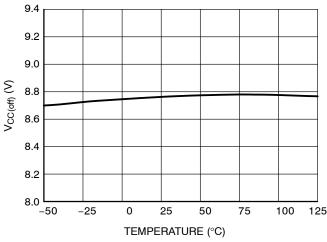

| Turn-off threshold                                                                                       |                                                                                           | V <sub>CC(off)</sub>                                    | 8.5         | 8.9          | 9.3         | V    |

| Overvoltage threshold                                                                                    |                                                                                           | V <sub>CC(ovp)</sub>                                    | 25          | 26.5         | 28          | V    |

| Blanking duration on $V_{CC(off)}$ and $V_{CC(ovp)}$ detection                                           |                                                                                           | t <sub>VCC(blank)</sub>                                 | -           | 10           | -           | μS   |

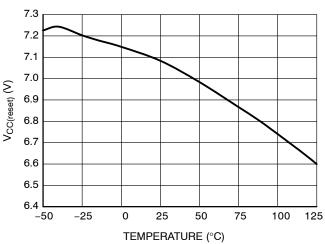

| V <sub>CC</sub> decreasing level at which the internal logic resets                                      |                                                                                           | V <sub>CC(reset)</sub>                                  | 4.8         | 7.0          | 7.7         | V    |

| V <sub>CC</sub> level for I <sub>START1</sub> to I <sub>START2</sub> transition                          |                                                                                           | V <sub>CC(inhibit)</sub>                                | 0.2         | 0.8          | 1.25        | V    |

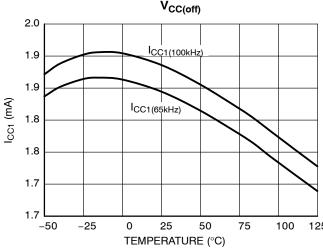

| Internal current consumption (Note 5)                                                                    | DRV open, $V_{FB} = 3 \text{ V}$ , 65 kHz<br>DRV open, $V_{FB} = 3 \text{ V}$ , 100 kHz   | I <sub>CC1</sub><br>I <sub>CC1</sub>                    | 1.3<br>1.3  | 1.85<br>1.85 | 2.2<br>2.2  | mA   |

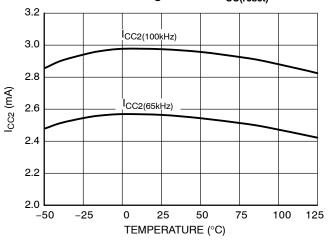

|                                                                                                          | Cdrv = 1 nF, V <sub>FB</sub> = 3 V, 65 kHz<br>Cdrv = 1 nF, V <sub>FB</sub> = 3 V, 100 kHz | I <sub>CC2</sub><br>I <sub>CC2</sub>                    | 1.8<br>2.3  | 2.6<br>2.9   | 3.0<br>3.5  |      |

|                                                                                                          | Off and to fall and to fall and all and                                                   | I <sub>CC3</sub>                                        | 0.67        | 0.9          | 1.13        |      |

|                                                                                                          | Off mode (skip or before start-up)  Fault mode (fault or latch)                           | I <sub>CC4</sub>                                        | 0.3         | 0.6          | 0.9         |      |

| BROWN-OUT                                                                                                |                                                                                           | •                                                       | •           |              |             |      |

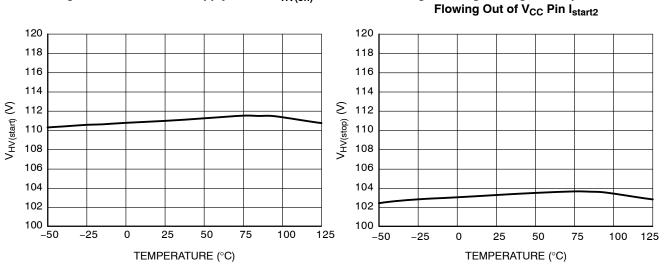

| Brown-Out thresholds (A/B versions)                                                                      | V <sub>HV</sub> going up<br>V <sub>HV</sub> going down                                    | V <sub>HV(start)</sub><br>V <sub>HV(stop)</sub>         | 102<br>94   | 111<br>103   | 120<br>112  | V    |

| Brown-Out thresholds (C/D versions)                                                                      | V <sub>HV</sub> going up<br>V <sub>HV</sub> going down                                    | V <sub>HV(start)</sub><br>V <sub>HV(stop)</sub>         | 87<br>79    | 95<br>87     | 103<br>95   | V    |

| Timer duration for line cycle drop-out                                                                   |                                                                                           | t <sub>HV</sub>                                         | 52          | 73           | 94          | ms   |

| X2 DISCHARGE                                                                                             |                                                                                           | _                                                       |             |              |             |      |

| Comparator hysteresis observed at HV pin                                                                 |                                                                                           | V <sub>HV(hyst)</sub>                                   | 1.5         | 3.5          | 5           | V    |

| HV signal sampling period                                                                                |                                                                                           | T <sub>sample</sub>                                     | -           | 1.0          | -           | ms   |

| Timer duration for no line detection                                                                     |                                                                                           | t <sub>DET</sub>                                        | 21          | 32           | 43          | ms   |

| Discharge timer duration                                                                                 |                                                                                           | t <sub>DIS</sub>                                        | 21          | 32           | 43          | ms   |

| OSCILLATOR                                                                                               |                                                                                           |                                                         |             |              |             |      |

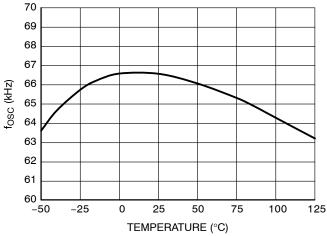

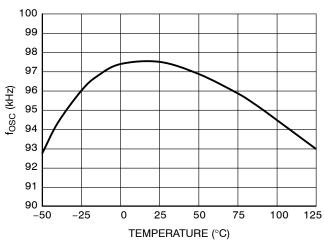

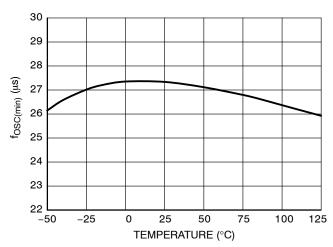

| Oscillator frequency                                                                                     |                                                                                           | fosc                                                    | 58<br>87    | 65<br>100    | 72<br>109   | kHz  |

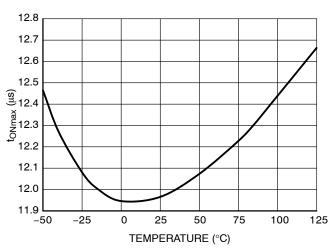

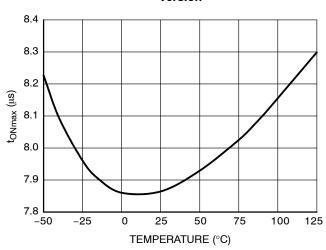

| Maximum on time for $T_J = 25^{\circ}C$ to $+125^{\circ}C$ only                                          | f <sub>OSC</sub> = 65 kHz<br>f <sub>OSC</sub> = 100 kHz                                   | t <sub>ONmax(65kHz)</sub><br>t <sub>ONmax(100kHz)</sub> | 11.5<br>7.5 | 12.3<br>8.0  | 13.1<br>8.5 | μs   |

<sup>5.</sup> Internal supply current only, currents sourced via FB pin is not included (current is flowing in GND pin only).

6. Guaranteed by design.

7. CS pin source current is a sum of I<sub>bias</sub> and I<sub>OPC</sub>, thus at V<sub>HV</sub> = 125 V is observed the I<sub>bias</sub> only, because I<sub>OPC</sub> is switched off.

**ELECTRICAL CHARACTERISTICS** (For typical values  $T_J = 25^{\circ}C$ , for min/max values  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ ,  $V_{HV} = 125$  V, V<sub>CC</sub> = 11 V unless otherwise noted)

| Characteristics                                                                      | Test Condition                                                                                                                                                                        | Symbol                                                    | Min         | Тур          | Max           | Unit       |

|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-------------|--------------|---------------|------------|

| OSCILLATOR                                                                           |                                                                                                                                                                                       |                                                           |             |              |               |            |

| Maximum on time                                                                      | f <sub>OSC</sub> = 65 kHz<br>f <sub>OSC</sub> = 100 kHz                                                                                                                               | t <sub>ONmax</sub> (65kHz)<br>t <sub>ONmax</sub> (100kHz) | 11.3<br>7.4 | 12.3<br>8.0  | 13.1<br>8.5   | μS         |

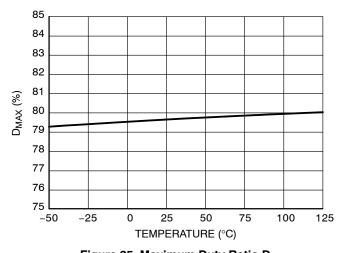

| Maximum duty cycle (corresponding to maximum on time at maximum switching frequency) | f <sub>OSC</sub> = 65 kHz<br>f <sub>OSC</sub> = 100 kHz                                                                                                                               | D <sub>MAX</sub>                                          | -           | 80           | -             | %          |

| Frequency jittering amplitude, in percentage of F <sub>OSC</sub>                     |                                                                                                                                                                                       | A <sub>jitter</sub>                                       | ±4          | ±6           | ±8            | %          |

| Frequency jittering modulation frequency                                             |                                                                                                                                                                                       | F <sub>jitter</sub>                                       | 85          | 125          | 165           | Hz         |

| FREQUENCY FOLDBACK                                                                   |                                                                                                                                                                                       |                                                           |             |              |               |            |

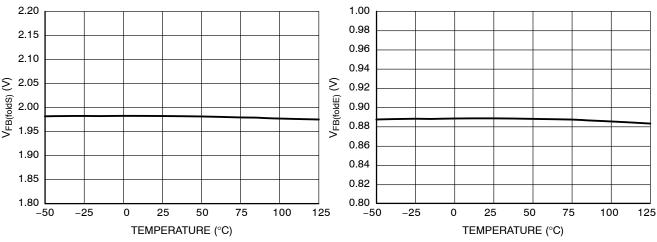

| Feedback voltage threshold below which frequency foldback starts                     |                                                                                                                                                                                       | V <sub>FB(foldS)</sub>                                    | 1.8         | 2.0          | 2.2           | V          |

| Feedback voltage threshold below which frequency foldback is complete                |                                                                                                                                                                                       | V <sub>FB(foldE)</sub>                                    | 0.8         | 0.9          | 1.0           | ٧          |

| Minimum switching frequency                                                          | $V_{FB} = V_{skip(in)} + 0.1$                                                                                                                                                         | f <sub>OSC(min)</sub>                                     | 23          | 27           | 32            | kHz        |

| OUTPUT DRIVER                                                                        |                                                                                                                                                                                       |                                                           |             |              |               |            |

| Rise time, 10% to 90% of $V_{CC}$                                                    | $V_{CC} = V_{CC(min)} + 0.2 \text{ V},$<br>$C_{DRV} = 1 \text{ nF}$                                                                                                                   | t <sub>rise</sub>                                         | -           | 40           | 70            | ns         |

| Fall time, 90% to 10% of V <sub>CC</sub>                                             | $V_{CC} = V_{CC(min)} + 0.2 \text{ V},$ $C_{DRV} = 1 \text{ nF}$                                                                                                                      | t <sub>fall</sub>                                         | -           | 40           | 70            | ns         |

| Current capability                                                                   | $\begin{aligned} V_{CC} &= V_{CC(min)} + 0.2 \text{ V,} \\ C_{DRV} &= 1 \text{ nF} \\ DRV \text{ high, } V_{DRV} &= 0 \text{ V} \\ DRV \text{ low, } V_{DRV} &= V_{CC} \end{aligned}$ | I <sub>DRV(source)</sub><br>I <sub>DRV(sink)</sub>        | -<br>-      | 500<br>800   | <u>-</u><br>- | mA         |

| Clamping voltage (maximum gate voltage)                                              | $V_{CC} = V_{CCmax} - 0.2 \text{ V, DRV high,}$<br>$R_{DRV} = 33 \text{ k}\Omega, C_{load} = 220 \text{ pF}$                                                                          | V <sub>DRV(clamp)</sub>                                   | 11          | 13.5         | 16            | ٧          |

| High-state voltage drop                                                              | $V_{CC} = V_{CC(min)} + 0.2 \text{ V},$<br>$R_{DRV} = 33 \text{ k}\Omega, \text{ DRV high}$                                                                                           | $V_{DRV(drop)}$                                           | -           | =            | 1             | V          |

| CURRENT SENSE                                                                        |                                                                                                                                                                                       |                                                           |             |              |               |            |

| Input Pull-up Current                                                                | V <sub>CS</sub> = 0.7 V                                                                                                                                                               | I <sub>bias</sub>                                         | -           | 1            | -             | μΑ         |

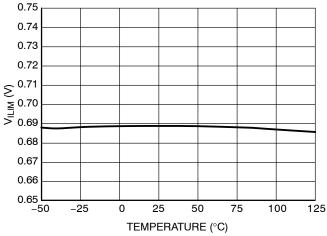

| Maximum internal current setpoint                                                    | V <sub>FB</sub> > 3.5 V                                                                                                                                                               | V <sub>ILIM</sub>                                         | 0.66        | 0.70         | 0.74          | V          |

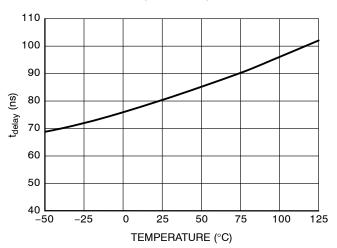

| Propagation delay from $V_{\mbox{\scriptsize llimit}}$ detection to DRV off          | V <sub>CS</sub> = V <sub>ILIM</sub>                                                                                                                                                   | t <sub>delay</sub>                                        | -           | 80           | 110           | ns         |

| Leading Edge Blanking Duration for $V_{\text{ILIM}}$                                 |                                                                                                                                                                                       | t <sub>LEB</sub>                                          | 200         | 250          | 320           | ns         |

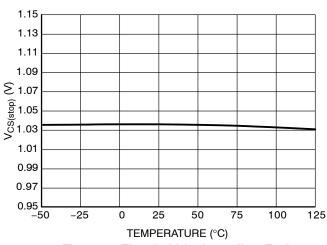

| Threshold for immediate fault protection activation                                  |                                                                                                                                                                                       | V <sub>CS(stop)</sub>                                     | 0.95        | 1.05         | 1.15          | V          |

| Leading Edge Blanking Duration for V <sub>CS(stop)</sub> (Note 6)                    |                                                                                                                                                                                       | t <sub>BCS</sub>                                          | 90          | 120          | 150           | ns         |

| Soft-start duration                                                                  | From 1 <sup>st</sup> pulse to V <sub>CS</sub> = V <sub>ILIM</sub>                                                                                                                     | t <sub>SSTART</sub>                                       | 8           | 11           | 14            | ms         |

| Frozen current setpoint                                                              |                                                                                                                                                                                       | V <sub>I(freeze)</sub>                                    | 275         | 300          | 325           | mV         |

| INTERNAL SLOPE COMPENSATION                                                          |                                                                                                                                                                                       |                                                           |             |              |               |            |

| Slope of the compensation ramp                                                       |                                                                                                                                                                                       | S <sub>comp(65kHz)</sub><br>S <sub>comp(100kHz)</sub>     | -<br>-      | -32.5<br>-50 | -<br>-        | mV /<br>μs |

| FEEDBACK                                                                             |                                                                                                                                                                                       |                                                           |             |              |               | _          |

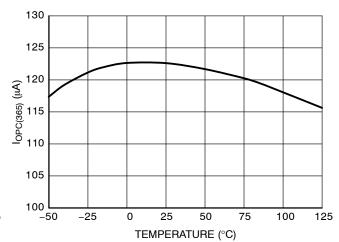

| Internal pull-up resistor                                                            | T <sub>J</sub> = 25°C                                                                                                                                                                 | R <sub>FB(up)</sub>                                       | 15          | 20           | 25            | kΩ         |

|                                                                                      |                                                                                                                                                                                       |                                                           |             |              |               |            |

<sup>5.</sup> Internal supply current only, currents sourced via FB pin is not included (current is flowing in GND pin only).

6. Guaranteed by design.

7. CS pin source current is a sum of I<sub>bias</sub> and I<sub>OPC</sub>, thus at V<sub>HV</sub> = 125 V is observed the I<sub>bias</sub> only, because I<sub>OPC</sub> is switched off.

**ELECTRICAL CHARACTERISTICS** (For typical values  $T_J = 25^{\circ}C$ , for min/max values  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ ,  $V_{HV} = 125$  V, V<sub>CC</sub> = 11 V unless otherwise noted)

| Characteristics                                                                    | Test Condition                                                                                           | Symbol                                                   | Min                | Тур                   | Max                | Unit        |

|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------------|-----------------------|--------------------|-------------|

| FEEDBACK                                                                           |                                                                                                          |                                                          |                    |                       |                    |             |

| V <sub>FB</sub> to internal current setpoint division ratio                        |                                                                                                          | K <sub>FB</sub>                                          | 4.7                | 5                     | 5.3                | _           |

| Internal pull-up voltage on the FB pin (Note 6)                                    |                                                                                                          | V <sub>FB(ref)</sub>                                     | 4.5                | 5                     | 5.5                | V           |

| Feedback voltage below which the peak current is frozen                            |                                                                                                          | V <sub>FB(freeze)</sub>                                  | 1.35               | 1.5                   | 1.65               | V           |

| SKIP CYCLE MODE                                                                    |                                                                                                          |                                                          | I                  |                       |                    |             |

| Feedback voltage thresholds for skip mode                                          | V <sub>FB</sub> going down<br>V <sub>FB</sub> going up                                                   | V <sub>skip(in)</sub><br>V <sub>skip(out)</sub>          | 0.63<br>0.72       | 0.70<br>0.80          | 0.77<br>0.88       | V           |

| REMOTE CONTROL ON FB PIN                                                           |                                                                                                          | •                                                        | 1                  | •                     |                    | .*          |

| The voltage above which the part enters the on mode                                | $V_{CC} > V_{CC(off)}, V_{HV} = 60 \text{ V}$                                                            | V <sub>ON</sub>                                          | -                  | 2.2                   | _                  | V           |

| The voltage below which the part enters the off mode                               | $V_{CC} > V_{CC(off)}$                                                                                   | V <sub>OFF</sub>                                         | 0.35               | 0.40                  | 0.45               | V           |

| Minimum hysteresis between the $V_{ON}$ and $V_{OFF}$                              | $V_{CC} > V_{CC(off)}, V_{HV} = 60 \text{ V}$                                                            | V <sub>HYST</sub>                                        | 500                | _                     | _                  | mV          |

| Pull-up current in off mode                                                        | $V_{CC} > V_{CC(off)}$                                                                                   | I <sub>OFF</sub>                                         | -                  | 5                     | _                  | μА          |

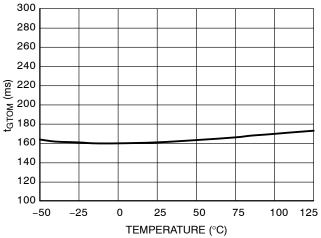

| Go To Off mode timer                                                               | $V_{CC} > V_{CC(off)}$                                                                                   | t <sub>GTOM</sub>                                        | 100                | 150                   | 300                | ms          |

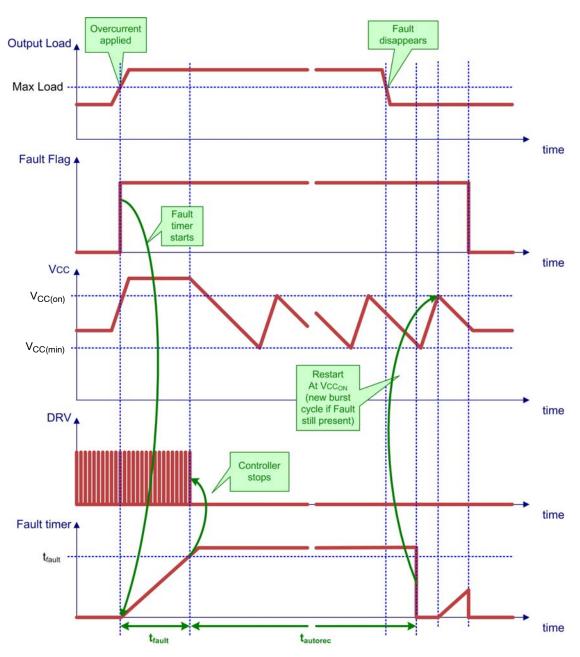

| OVERLOAD PROTECTION                                                                |                                                                                                          | •                                                        |                    |                       |                    |             |

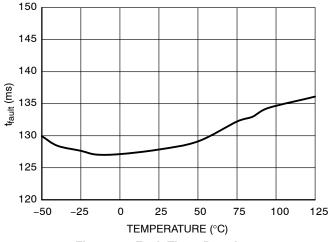

| Fault timer duration                                                               |                                                                                                          | t <sub>fault</sub>                                       | 108                | 128                   | 178                | ms          |

| Autorecovery mode latch-off time duration                                          |                                                                                                          | t <sub>autorec</sub>                                     | 0.85               | 1.00                  | 1.35               | s           |

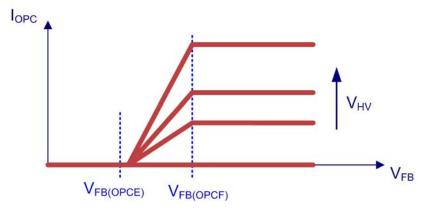

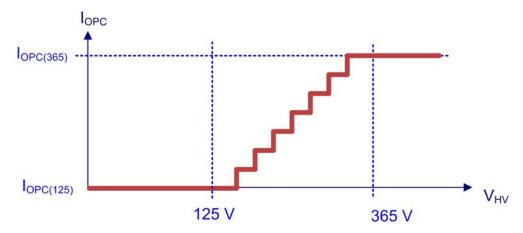

| OVERPOWER PROTECTION                                                               |                                                                                                          | •                                                        |                    |                       |                    |             |

| V <sub>HV</sub> to I <sub>OPC</sub> conversion ratio                               |                                                                                                          | K <sub>OPC</sub>                                         | _                  | 0.54                  | -                  | $\mu A / V$ |

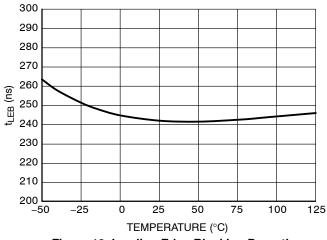

| Current flowing out of CS pin (Note 7)                                             | V <sub>HV</sub> = 125 V<br>V <sub>HV</sub> = 162 V<br>V <sub>HV</sub> = 325 V<br>V <sub>HV</sub> = 365 V | IOPC(125)<br>IOPC(162)<br>IOPC(325)<br>IOPC(365)         | -<br>-<br>-<br>105 | 0<br>20<br>110<br>130 | -<br>-<br>-<br>150 | μΑ          |

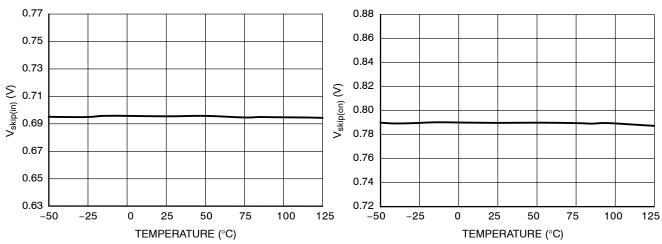

| FB voltage above which I <sub>OPC</sub> is applied                                 | V <sub>HV</sub> = 365 V                                                                                  | V <sub>FB(OPCF)</sub>                                    | 2.12               | 2.35                  | 2.58               | V           |

| FB voltage below which is no I <sub>OPC</sub> applied                              | V <sub>HV</sub> = 365 V                                                                                  | V <sub>FB(OPCE)</sub>                                    | _                  | 2.15                  | -                  | V           |

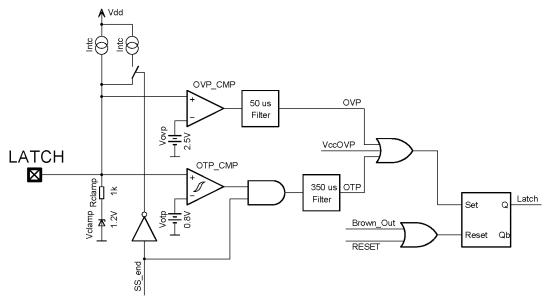

| LATCH-OFF INPUT                                                                    |                                                                                                          | •                                                        |                    |                       | •                  |             |

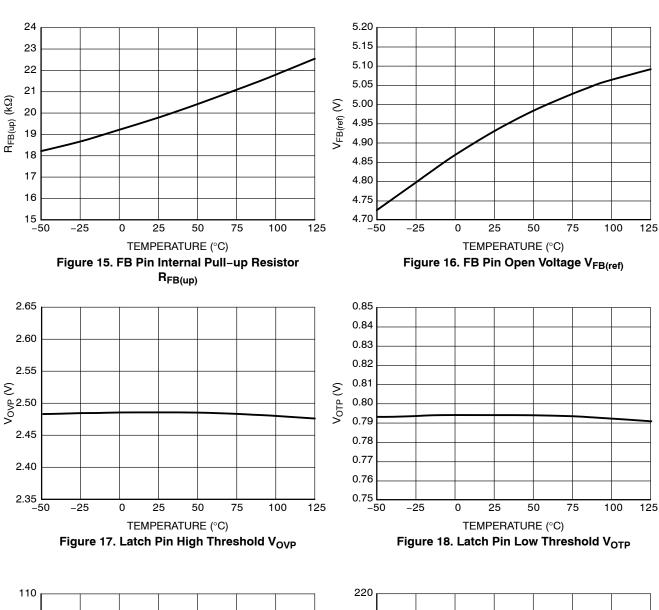

| High threshold                                                                     | V <sub>Latch</sub> going up                                                                              | V <sub>OVP</sub>                                         | 2.35               | 2.5                   | 2.65               | V           |

| Low threshold                                                                      | V <sub>Latch</sub> going down                                                                            | V <sub>OTP</sub>                                         | 0.76               | 0.8                   | 0.84               | V           |

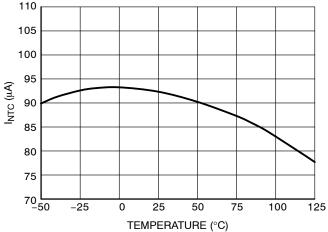

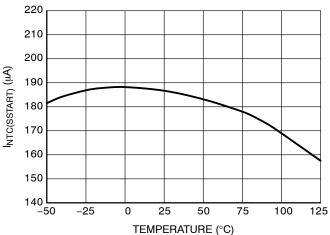

| Current source for direct NTC connection During normal operation During soft–start | V <sub>Latch</sub> = 0 V                                                                                 | I <sub>NTC</sub><br>I <sub>NTC(SSTART)</sub>             | 65<br>130          | 95<br>190             | 105<br>210         | μΑ          |

| Blanking duration on high latch detection                                          | 65 kHz version<br>100 kHz version                                                                        | t <sub>Latch(OVP)</sub>                                  | 35<br>20           | 50<br>35              | 70<br>50           | μs          |

| Blanking duration on low latch detection                                           |                                                                                                          | t <sub>Latch(OTP)</sub>                                  | -                  | 350                   | -                  | μs          |

| Clamping voltage                                                                   | I <sub>Latch</sub> = 0 mA<br>I <sub>Latch</sub> = 1 mA                                                   | V <sub>clamp0(Latch)</sub><br>V <sub>clamp1(Latch)</sub> | 1.0<br>1.8         | 1.2<br>2.4            | 1.4<br>3.0         | V           |

| TEMPERATURE SHUTDOWN                                                               |                                                                                                          |                                                          |                    |                       |                    |             |

| Temperature shutdown                                                               | T <sub>J</sub> going up                                                                                  | T <sub>TSD</sub>                                         | -                  | 150                   | _                  | °C          |

| Temperature shutdown hysteresis                                                    | T <sub>J</sub> going down                                                                                | T <sub>TSD(HYS)</sub>                                    | -                  | 30                    | -                  | °C          |

<sup>5.</sup> Internal supply current only, currents sourced via FB pin is not included (current is flowing in GND pin only).

Guaranteed by design.

CS pin source current is a sum of I<sub>bias</sub> and I<sub>OPC</sub>, thus at V<sub>HV</sub> = 125 V is observed the I<sub>bias</sub> only, because I<sub>OPC</sub> is switched off.

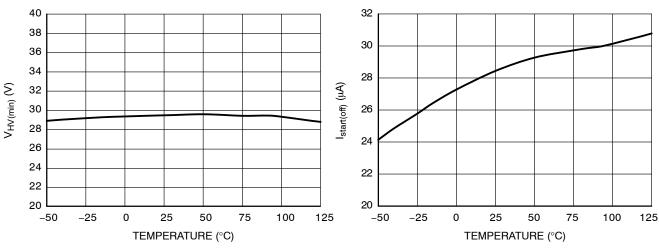

Figure 3. Minimum Current Source Operation V<sub>HV(min)</sub>

Figure 4. Off-State Leakage Current Istart(off)

Figure 5. Off-Mode HV Supply Current I<sub>HV(off)</sub>

Figure 7. Brown-out Device Start Threshold V<sub>HV(start)</sub>

Figure 8. Brown-out Device Stop Threshold V<sub>HV(stop)</sub>

310 308 306 304 £ 302 ) (300 298 298 296 294 292 290 -50 -25 0 25 50 75 100 125 TEMPERATURE (°C)

Figure 9. Maximum Internal Current Setpoint  $V_{\text{ILIM}}$

Figure 10. Frozen Current Setpoint  $V_{l(freeze)}$  for the Light Load Operation

Figure 11. Threshold for Immediate Fault Protection Activation  $V_{CS(stop)}$

Figure 12. Propagation Delay t<sub>delay</sub>

Figure 13. Leading Edge Blanking Duaration  $t_{\text{LEB}}$

Figure 14. Maximum Overpower Compensating Current I<sub>OPC(365)</sub> Flowing Out of CS Pin

Figure 19. Current I<sub>NTC</sub> Sourced from the Latch Pin, Allowing Direct NTC Connection

Figure 20. Current I<sub>NTC(SSTART)</sub> Sourced from the Latch Pin, During Soft-Start

Figure 21. Oscillator f<sub>OSC</sub> for the 65 kHz Version

Figure 22. Oscillator f<sub>OSC</sub> for the 100 kHz Version

Figure 23. Maximum ON Time t<sub>ONmax</sub> for the 65 kHz Version

Figure 24. Maximum ON Time  $t_{ONmax}$  for the 100 kHz Version

Figure 25. Maximum Duty Ratio  $\mathbf{D}_{\mathbf{MAX}}$

Figure 26. Minimum Switching Frequency f<sub>OSC(min)</sub>

#### **TYPICAL CHARACTERISTIC**

Figure 27. FB Pin Voltage Below Which Frequency Foldback Starts V<sub>FB(foldS)</sub>

Figure 28. FB Pin Voltage Below Which Frequency Foldback Complete V<sub>FB(foldE)</sub>

Figure 29. FB Pin Skip-In Level V<sub>skip(in)</sub>

Figure 30. FB Pin Skip-Out Level V<sub>skip(out)</sub>

Figure 31. FB Pin Level V<sub>FB(OPCF)</sub> Above Which is the Overpower Compensation Applied

Figure 32. FB Pin Level V<sub>FB(OPCE)</sub> Below Which is No Overpower Compensation Applied

100

125

Figure 33.  $V_{CC}$  Turn-on Threshold Level,  $V_{CC}$  Going Up HV Current Source Stop Threshold  $V_{CC(on)}$

Figure 34. HV Current Source Restart Threshold V<sub>CC(min)</sub>

Figure 35. V<sub>CC</sub> Turn-off Threshold (UVLO)

Figure 36.  $V_{CC}$  Decreasing Level at Which the Internal Logic Resets  $V_{CC(reset)}$

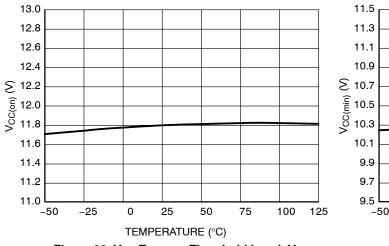

Figure 37. Internal Current Consumption when DRV Pin is Unloaded

Figure 38. Internal Current Consumption when DRV Pin is Loaded by 1 nF

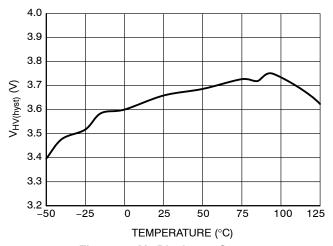

Figure 39. X2 Discharge Comparator Hysteresis Observed at HV Pin  $V_{HV(hyst)}$

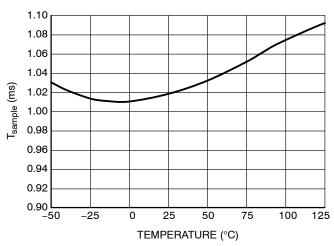

Figure 40. HV Signal Sampling Period T<sub>sample</sub>

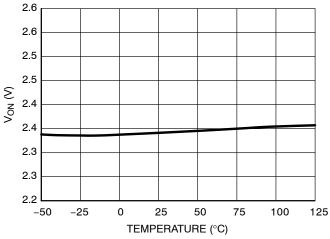

Figure 41. FB Pin Voltage Level Above Which is Entered On Mode V<sub>ON</sub>

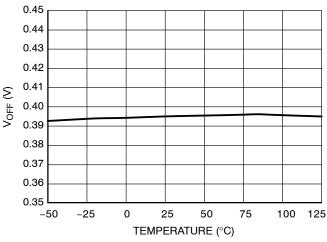

Figure 42. FB Pin Voltage Level Below Which is Entered Off Mode  $V_{\rm OFF}$

Figure 43. Fault Timer Duration t<sub>fault</sub>

Figure 44. Go To Off Mode Timer Duration t<sub>GTOM</sub>

#### APPLICATION INFORMATION

#### **Functional Description**

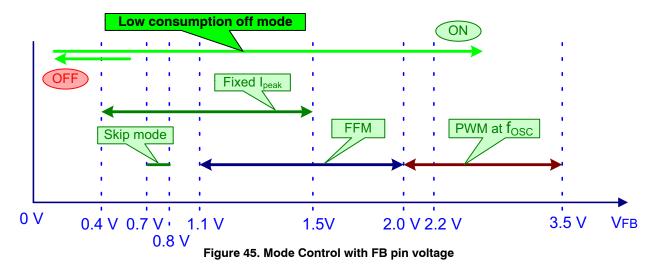

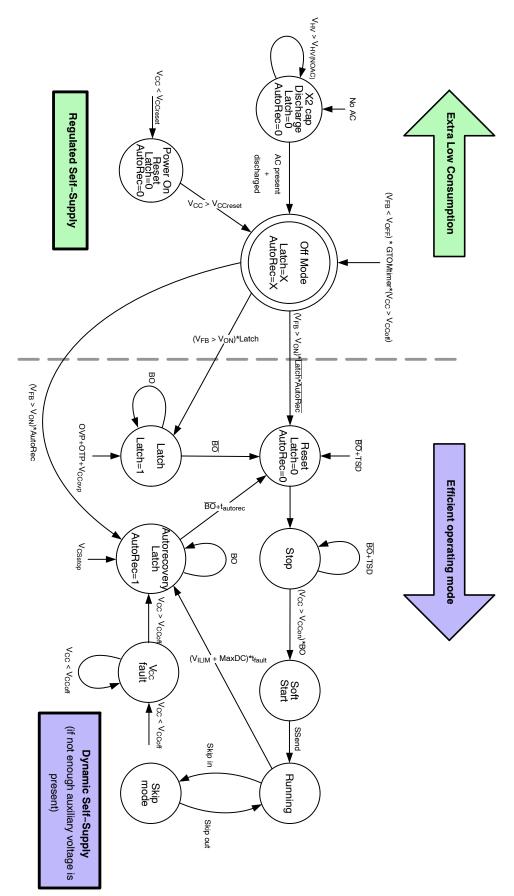

The NCP1247 includes all necessary features to build a safe and efficient power supply based on a fixed-frequency flyback converter. The NCP1247 is a multimode controller as illustrated in Figure 45. The mode of operation depends upon line and load condition. Under all modes of operation, the NCP1247 terminates the DRV signal based on the switch current. Thus, the NCP1247 always operates in current mode control so that the power MOSFET current is always limited.

Under normal operating conditions, the FB pin commands the operating mode of the NCP1247 at the voltage thresholds shown in Figure 45. At normal rated operating loads (from 100% to approximately 33% full rated power) the NCP1247 controls the converter in fixed frequency PWM mode. It can operate in the continuous conduction mode (CCM) or discontinuous conduction mode (DCM) depending upon the input voltage and loading conditions. If the controller is used in CCM with a wide input voltage range, the duty-ratio may increase up to 50%. The build-in slope compensation prevents the appearance of sub-harmonic oscillations in this operating area.

For loads that are between approximately 32% and 10% of full rated power, the converter operates in frequency foldback mode (FFM). If the feedback pin voltage is lower than 1.5 V the peak switch current is kept constant and the output voltage is regulated by modulating the switching frequency for a given and fixed input voltage  $V_{HV}$ .

Effectively, operation in FFM results in the application of constant volt-seconds to the flyback transformer each switching cycle. Voltage regulation in FFM is achieved by varying the switching frequency in the range from 65 kHz (or 100 kHz) to 27 kHz. For extremely light loads (below approximately 6% full rated power), the converter is controlled using bursts of 27 kHz pulses. This mode is called as skip mode. The FFM, keeping constant peak current and skip mode allows design of the power supplies with increased efficiency under the light loading conditions. Keep in mind that the aforementioned boundaries of steady-state operation are approximate because they are subject to converter design parameters.

There was implemented the low consumption off mode allowing to reach extremely low no load input power. This mode is controlled by the FB pin and allows the remote control (or secondary side control) of the power supply shut–down. Most of the device internal circuitry is unbiased in the low consumption off mode. Only the FB pin control circuitry and X2 cap discharging circuitry is operating in the low consumption off mode. If the voltage at feedback pin decreases below the 0.4 V the controller will enter the low

consumption off mode. The controller can start if the FB pin voltage increases above the 2.2 V level.

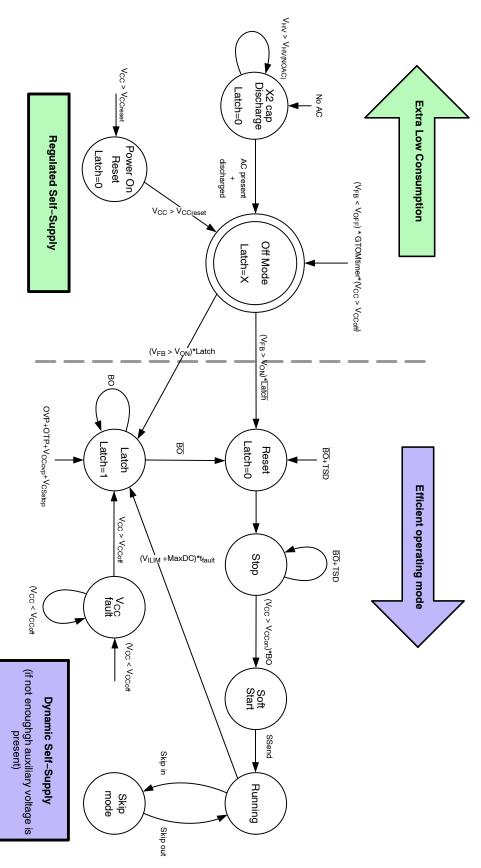

See the detailed status diagrams for the versions fully latched A/C and the autorecovery B/D on the following figures. The basic status of the device after wake—up by the  $V_{\rm CC}$  is the off mode and mode is used for the overheating protection mode if the thermal shutdown protection is activated.

Figure 46. Operating Status Diagram for the Fully Latched Versions A/C of the Device

Figure 47. Operating Status Diagram for the Autorecovery Versions B/D of the Device

The information about the fault (permanent Latch or Autorecovery) is kept during the low consumption off mode due the safety reason. The reason is not to allow unlatch the device by the remote control being in off mode.

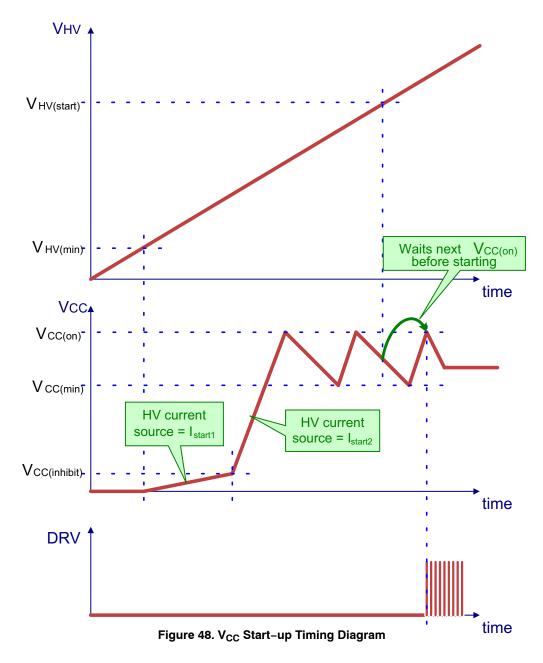

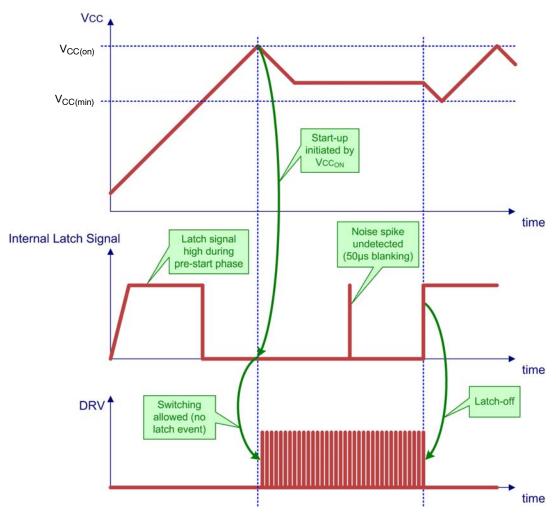

#### Start-up of the Controller

At start-up, the current source turns on when the voltage on the HV pin is higher than  $V_{HV(min)}$ , and turns off when  $V_{CC}$  reaches  $V_{CC(on)}$ , then turns on again when  $V_{CC}$  reaches  $V_{CC(min)}$ , until the input voltage is high enough to ensure a proper start-up, i.e. when  $V_{HV}$  reaches  $V_{HV(start)}$ . The controller actually starts the next time  $V_{CC}$  reaches  $V_{CC(on)}$ . The controller then delivers pulses, starting with a soft–start period  $t_{SSTART}$  during which the peak current linearly increases before the current–mode control takes over.

Even though the Dynamic Self–Supply is able to maintain the  $V_{CC}$  voltage between  $V_{CC(on)}$  and  $V_{CC(min)}$  by turning the HV start–up current source on and off, it can only be used in light load condition, otherwise the power dissipation on the die would be too much. As a result, an auxiliary voltage source is needed to supply  $V_{CC}$  during normal operation.

The Dynamic Self–Supply is useful to keep the controller alive when no switching pulses are delivered, e.g. in brown–out condition, or to prevent the controller from stopping during load transients when the  $V_{CC}$  might drop. The NCP1247 accepts a supply voltage as high as 28 V, with an overvoltage threshold  $V_{CC(ovp)}$  that latches the controller off

For safety reasons, the start–up current is lowered when  $V_{CC}$  is below  $V_{CC(inhibit)}$ , to reduce the power dissipation in case the  $V_{CC}$  pin is shorted to GND (in case of  $V_{CC}$  capacitor failure, or external pull–down on  $V_{CC}$  to disable the controller). There is only one condition for which the current source doesn't turn on when  $V_{CC}$  reaches  $V_{CC(inhibit)}$ : the voltage on HV pin is too low (below  $V_{HV(min)}$ ).

#### **HV Sensing of Rectified AC Voltage**

The NCP1247 features on its HV pin a true ac line monitoring circuitry. It includes a minimum start-up

threshold and an autorecovery brown-out protection; both of them independent of the ripple on the input voltage. It is allowed only to work with an unfiltered, rectified ac input to ensure the X2 capacitor discharge function as well, which is described in following. The brown-out protection thresholds are fixed, but they are designed to fit most of the standard ac-dc conversion applications.

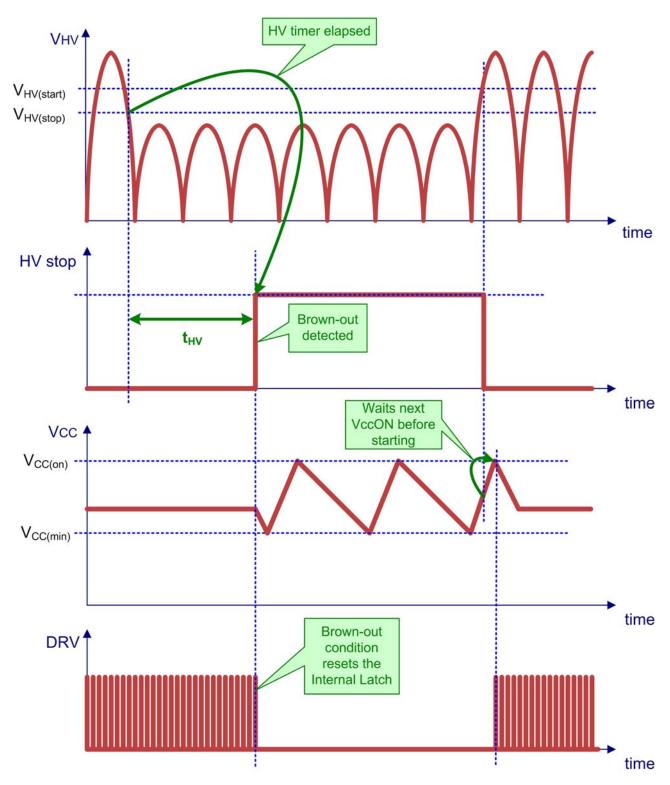

When the input voltage goes below  $V_{HV(stop)}$ , a brown-out condition is detected, and the controller stops. The HV current source maintains  $V_{CC}$  at  $V_{CC(min)}$  level until the input voltage is back above  $V_{HV(start)}$ .

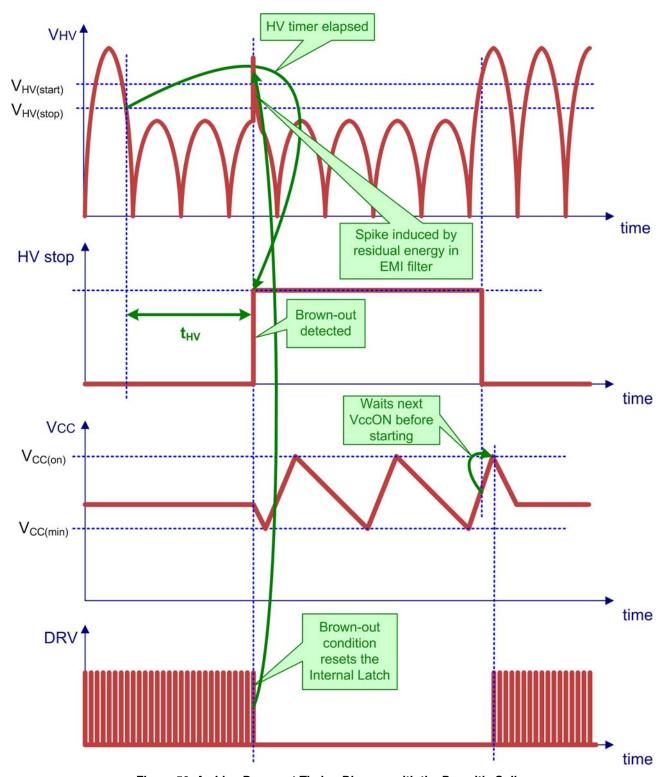

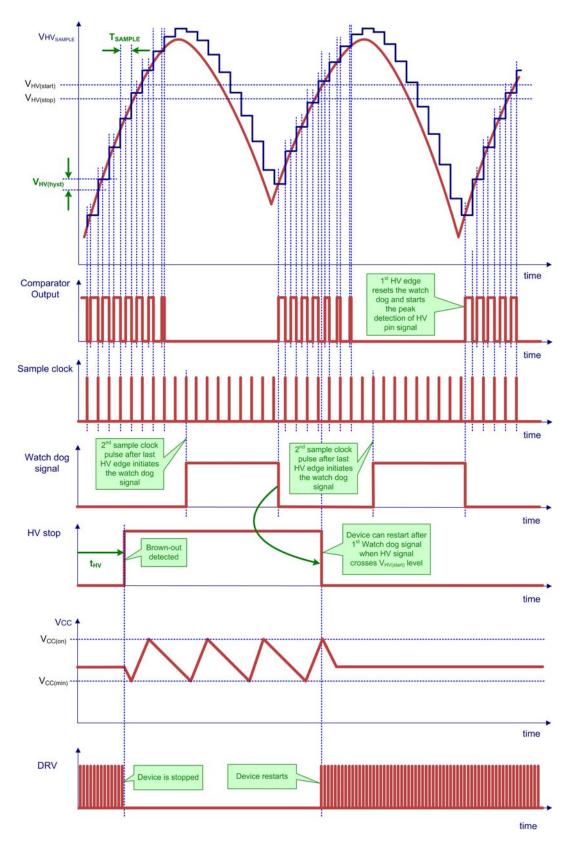

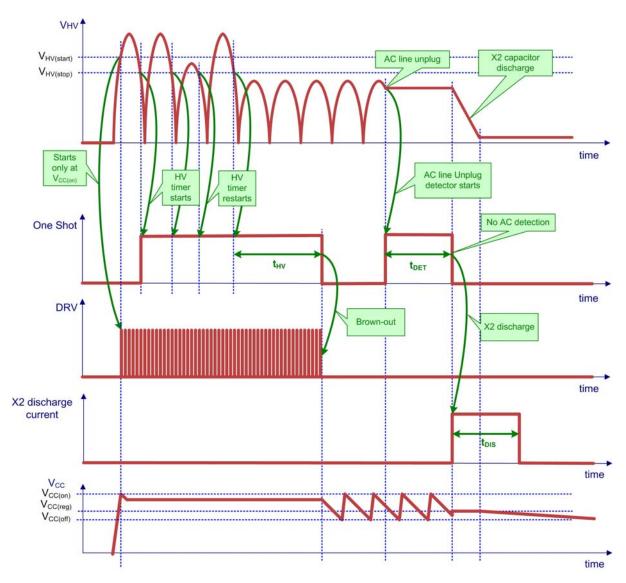

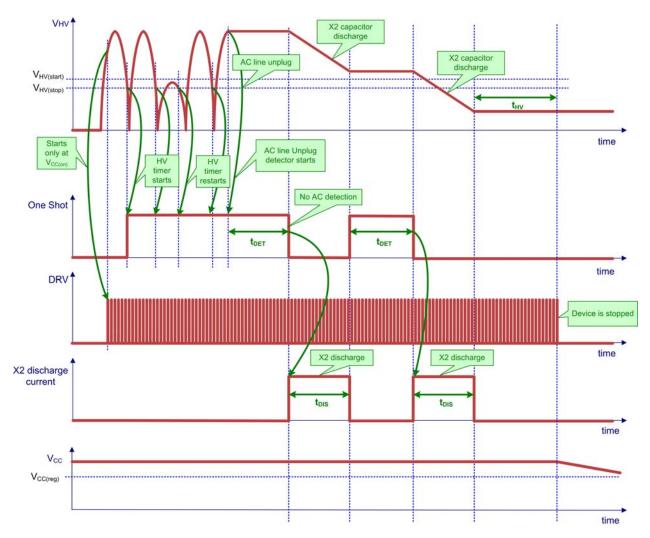

Figure 49. Ac Line Drop-out Timing Diagram

Figure 50. Ac Line Drop-out Timing Diagram with the Parasitic Spike

When  $V_{HV}$  crosses the  $V_{HV(start)}$  threshold, the controller can start immediately. When it crosses  $V_{HV(stop)}$ , it triggers a timer of duration  $t_{HV}$ , this ensures that the controller doesn't stop in case of line cycle drop–out. The device restart after the ac line voltage drop-out is protected to the parasitic restart initiated e.g. the spikes induced at HV pin

immediately after the device is stopped by the residual energy in the EMI filter. The device restart is allowed only after the 1st watch dog signal event. The basic principle is shown at Figure 49 and detail of the device restart is shown at Figure 51.

Figure 51. Detailed Timing Diagram of the Device Restart After the Short ac Line Drop-out

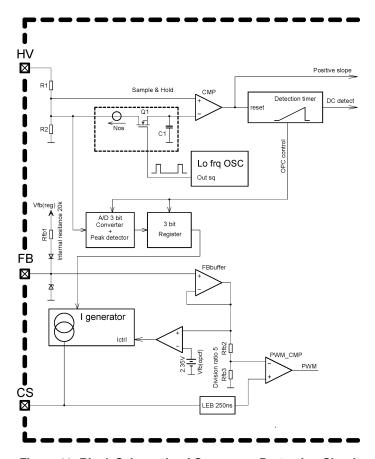

#### X2 Cap Discharge Feature

The X2 capacitor discharging feature is offered by usage of the NCP1247. This feature save approx. 16 mW - 25 mW input power depending on the EMI filter X2 capacitors volume and it saves the external components count as well. The discharge feature is ensured via the start-up current source with a dedicated control circuitry for this function. The X2 capacitors are being discharged by current defined as  $I_{\text{start2}}$  when this discharge event is detected.

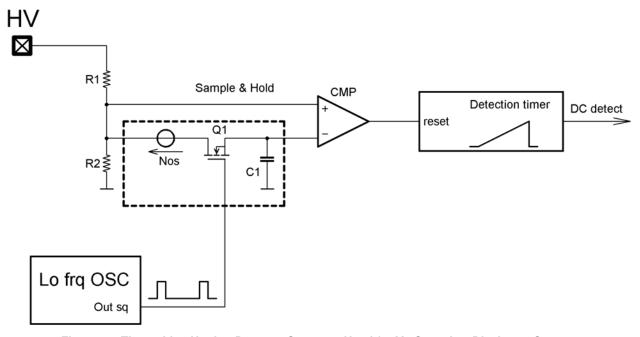

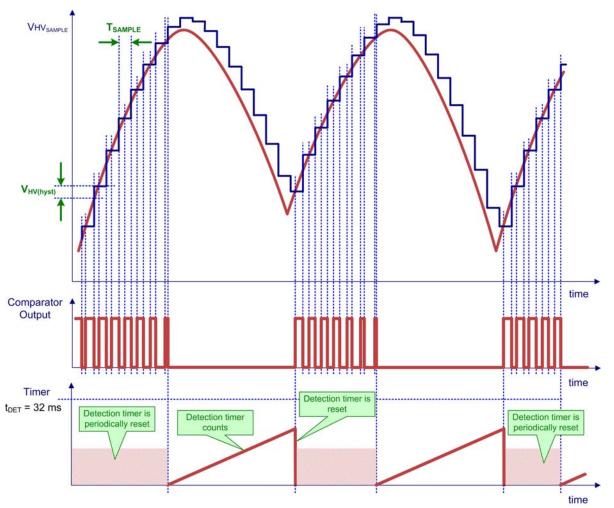

There is used a dedicated structure called ac line unplug detector inside the X2 capacitor discharge control circuitry. See the Figure 52 for the block diagram for this structure and Figures 53, 54, 55 and 56 for the timing diagrams. The basic idea of ac line unplug detector lies in comparison of the direct sample of the high voltage obtained via the high voltage sensing structure with the delayed sample of the high voltage. The delayed signal is created by the sample & hold structure.

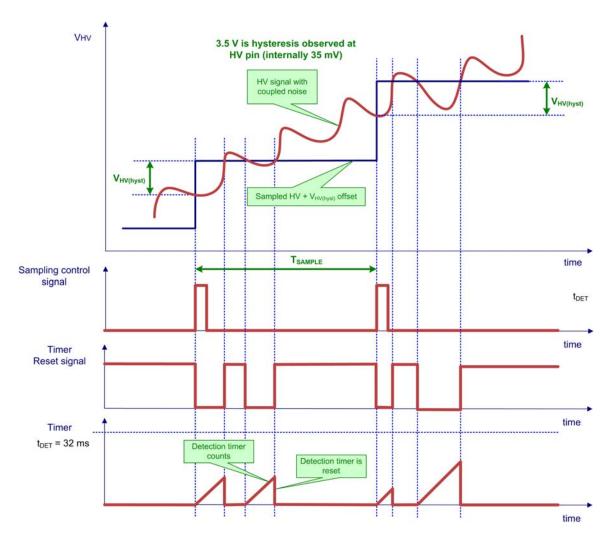

The comparator used for the comparison of these signals is without hysteresis inside. The resolution between the slopes of the ac signal and dc signal is defined by the sampling time  $T_{\mbox{SAMPLE}}$  and additional internal offset  $N_{\mbox{OS}}$ . These parameters ensure the noise immunity as well. The additional offset is added to the picture of the sampled HV signal and its analog sum is stored in the C<sub>1</sub> storage capacitor. If the voltage level of the HV sensing structure output crosses this level the comparator CMP output signal resets the detection timer and no dc signal is detected. The additional offset NOS can be measured as the VHV(hvst) on the HV pin. If the comparator output produces pulses it means that the slope of input signal is higher than set resolution level and the slope is positive. If the comparator output produces the low level it means that the slope of input signal is lower than set resolution level or the slope is negative. There is used the detection timer which is reset by any edge of the comparator output. It means if no edge comes before the timer elapses there is present only dc signal or signal with the small ac ripple at the HV pin. This type of the ac detector detects only the positive slope, which fulfils the requirements for the ac line presence detection.

In case of the dc signal presence on the high voltage input, the direct sample of the high voltage obtained via the high voltage sensing structure and the delayed sample of the high voltage are equivalent and the comparator produces the low level signal during the presence of this signal. No edges are present at the output of the comparator, that's why the detection timer is not reset and dc detect signal appears.

The minimum detectable slope by this ac detector is given by the ration between the maximum hysteresis observed at HV pin  $V_{HV(hyst),max}$  and the sampling time:

$$S_{min} = \frac{V_{HV(hyst),max}}{T_{sample}}$$

(eq. 1)

Than it can be derived the relationship between the minimum detectable slope and the amplitude and frequency of the sinusoidal input voltage:

$$V_{max} = \frac{V_{HV(hyst),max}}{2 \cdot \pi \cdot f \cdot T_{sample}} = \frac{5}{2 \cdot \pi \cdot 35 \cdot 1 \cdot 10^{-3}} \text{ (eq. 2)}$$

The minimum detectable AC RMS voltage is 16 V at frequency 35 Hz, if the maximum hysteresis is 5 V and sampling time is 1 ms.

The X2 capacitor discharge feature is available in any controller operation mode to ensure this safety feature. The detection timer is reused for the time limiting of the discharge phase, to protect the device against overheating. The discharging process is cyclic and continues until the ac line is detected again or the voltage across the X2 capacitor is lower than  $V_{HV(min)}$ . This feature ensures to discharge quite big X2 capacitors used in the input line filter to the safe level. It is important to note that it is not allowed to connect HV pin to any dc voltage due this feature. e.g. directly to bulk capacitor.

During the HV sensing or X2 cap discharging the  $V_{\rm CC}$  net is kept above the  $V_{\rm CC(off)}$  voltage by the Self–Supply in any mode of device operation to supply the control circuitry. During the discharge sequence is not allowed to start–up the device.

Figure 52. The ac Line Unplug Detector Structure Used for X2 Capacitor Discharge System

Figure 53. The ac Line Unplug Detector Timing Diagram

Figure 54. The ac Line Unplug Detector Timing Diagram Detail with Noise Effects

Figure 55. HV Pin ac Input Timing Diagram with X2 Capacitor Discharge Sequence When the Application is Unplugged Under Extremely Low Line Condition

Figure 56. HV Pin ac Input Timing Diagram with X2 Capacitor Discharge Sequence When the Application is Unplugged Under High Line Condition

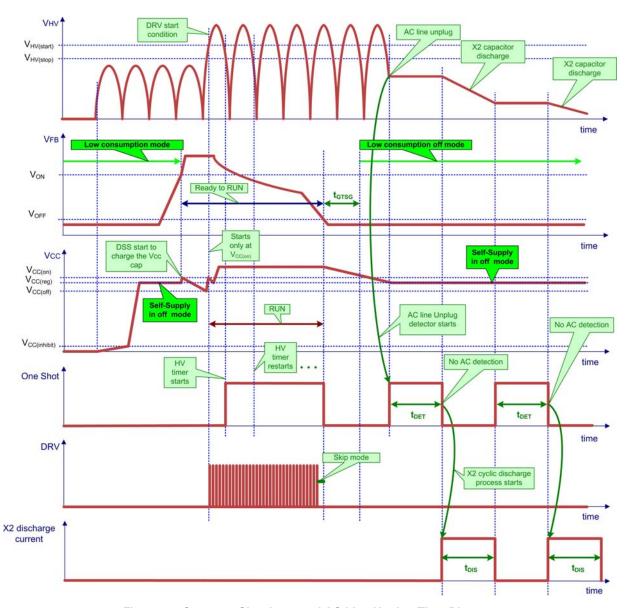

#### The Low Consumption Off Mode

There was implemented the low consumption off mode allowing to reach extremely low no load input power as described in previous chapters. If the voltage at feedback pin decreases below the 0.4 V the controller enters the off mode. The internal  $V_{CC}$  is turned–off, the IC consumes extremely low  $V_{CC}$  current and only the voltage at external  $V_{CC}$  capacitor is maintained by the Self–Supply circuit. The Self–Supply circuit keeps the  $V_{CC}$  voltage at the  $V_{CC(reg)}$  level. The supply for the FB pin watch dog circuitry and FB pin bias is provided via the low consumption current sources from the external  $V_{CC}$  capacitor. The controller can only start, if the FB pin voltage increases above the 2.2 V level. See Figure 57 for timing diagrams.

Only the X2 cap discharge and Self–Supply features is enabled in the low consumption off mode. The X2 cap discharging feature is enable due the safety reasons and the Self–Supply is enabled to keep the  $V_{CC}$  supply, but only very low  $V_{CC}$  consumption appears in this mode. Any other features are disabled in this mode.

The information about the latch status of the device is kept in the low consumption off mode and this mode is used for the TSD protection as well. The protection timer GoToOffMode  $t_{GTOM}$  is used to protect the application against the false activation of the low consumption off mode by the fast drop outs of the FB pin voltage below the 0.4 V level. E.g. in case when is present high FB pin voltage ripple during the skip mode.

Figure 57. Start-up, Shutdown and AC Line Unplug Time Diagram

## Oscillator with Maximum On Time and Frequency Jittering

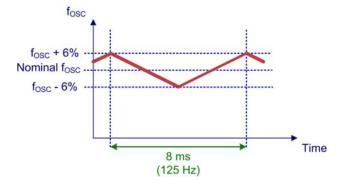

The NCP1247 includes an oscillator that sets the switching frequency 65 kHz or 100 kHz depending on the version. The maximum on time is 12.3  $\mu s$  (for 65 kHz version) or 8  $\mu s$  (for 100 kHz version) with an accuracy of  $\pm 7\%$ . The maximum on time corresponds to maximum duty cycle of the DRV pin is 80% at full switching frequency. In order to improve the EMI signature, the switching frequency jitters  $\pm 6$ % around its nominal value, with a triangle–wave shape and at a frequency of 125 Hz. This frequency jittering is active even when the frequency is decreased to improve the efficiency in light load condition.

Figure 58. Frequency Modulation of the Maximum Switching Frequency

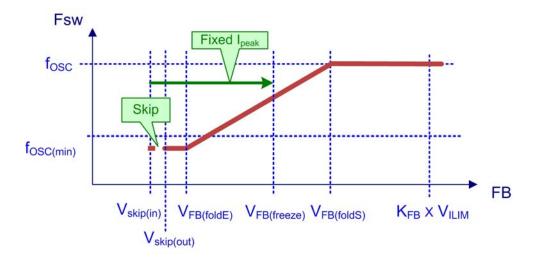

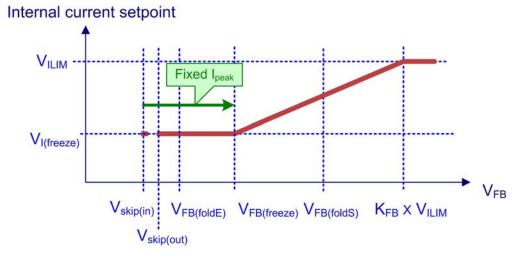

## Low Load Operation Modes: Frequency Foldback Mode (FFM) and Skip Mode

In order to improve the efficiency in light load conditions, the frequency of the internal oscillator is linearly reduced from its nominal value down to  $f_{OSC(min)}$ . This frequency foldback starts when the voltage on FB pin goes below  $V_{FB(foldS)}$ , and is complete when  $V_{FB}$  reaches  $V_{FB(foldE)}$ . The maximum on–time duration control is kept during the

frequency foldback mode to provide the natural transformer core anti–saturation protection. The frequency jittering is still active while the oscillator frequency decreases as well. The current setpoint is fixed to 300 mV in the frequency foldback mode if the feedback voltage decreases below the  $V_{FB(freeze)}$  level. This feature increases efficiency under the light loads conditions as well.

Figure 59. Frequency Foldback Mode Characteristic

Figure 60. Current Setpoint Dependency on the Feedback Pin Voltage

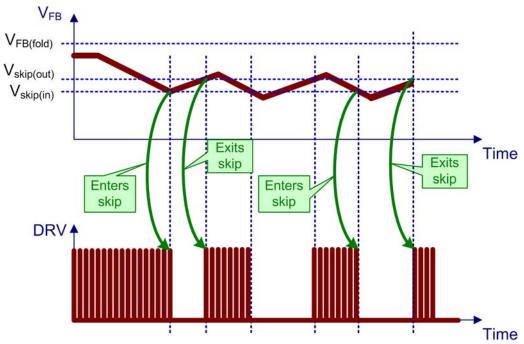

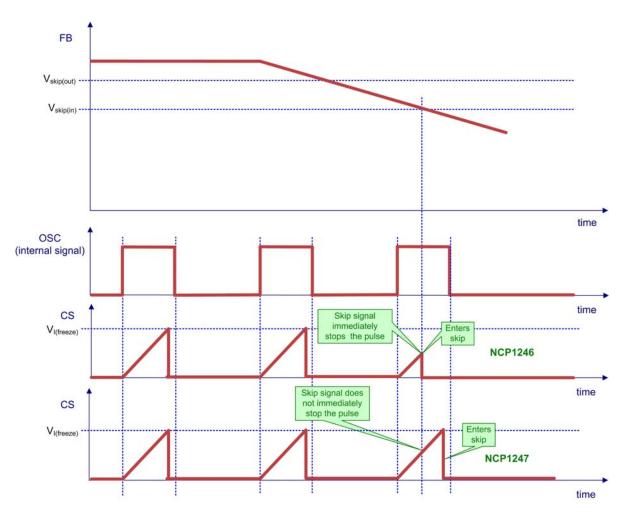

When the FB voltage reaches  $V_{skip(in)}$  while decreasing, skip mode is activated: the driver stops, and the internal consumption of the controller is decreased. While  $V_{FB}$  is

below  $V_{skip(out)}$ , the controller remains in this state; but as soon as  $V_{FB}$  crosses the skip out threshold, the DRV pin starts to pulse again.

Figure 61. Skip Mode Timing Diagram

Figure 62. Technique Preventing Short Pulses in Skip Mode

#### **Clamped Driver**

The supply voltage for the NCP1247 can be as high as 28 V, but most of the MOSFETs that will be connected to the DRV pin cannot accept more than 20 V on their gate. The driver pin is therefore clamped safely below 16 V. This driver has a typical capability of 500 mA for source current and 800 mA for sink current.

## Current-Mode Control With Slope Compensation and Soft-Start

NCP1247 is a current-mode controller, which means that the FB voltage sets the peak current flowing in the inductance and the MOSFET. This is done through a PWM comparator: the current is sensed across a resistor and the

resulting voltage is applied to the CS pin. It is applied to one input of the PWM comparator through a 250 ns LEB block. On the other input the FB voltage divided by 5 sets the threshold: when the voltage ramp reaches this threshold, the output driver is turned off. The maximum value for the current sense is 0.7 V, and it is set by a dedicated comparator.

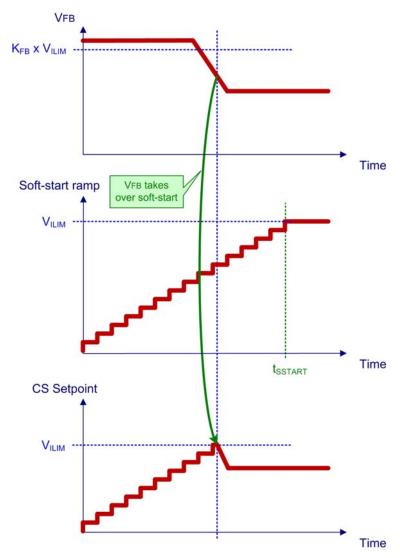

Each time the controller is starting, i.e. the controller was off and starts – or restarts – when  $V_{CC}$  reaches  $V_{CC(on)}$ , a soft–start is applied: the current sense setpoint is increased by 15 discrete steps from 0 (the minimum level can be higher than 0 because of the LEB and propagation delay) until it reaches  $V_{ILIM}$  (after a duration of  $t_{SSTART}$ ), or until the FB loop imposes a setpoint lower than the one imposed by the soft–start (the two comparators outputs are OR'ed).

Figure 63. Soft-Start Feature

Under some conditions, like a winding short-circuit for instance, not all the energy stored during the *on* time is transferred to the output during the *off* time, even if the on time duration is at its minimum (imposed by the propagation delay of the detector added to the LEB duration). As a result,

the current sense voltage keeps on increasing above  $V_{\rm ILIM}$ , because the controller is blind during the LEB blanking time. Dangerously high current can grow in the system if nothing is done to stop the controller. That's what the additional comparator, that senses when the current sense

voltage on CS pin reaches  $V_{CS(stop)}$  (= 1.5 x  $V_{ILIM}$ ), does: as soon as this comparator toggles, the controller immediately enters the protection mode.

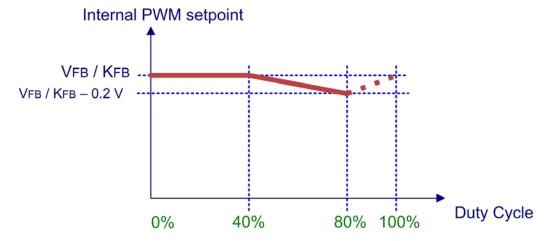

In order to allow the NCP1247 to operate in CCM with a duty cycle above 50%, the fixed slope compensation is internally applied to the current-mode control. The slope appearing on the internal voltage setpoint for the PWM

comparator is -32.5 mV/ $\mu$ s typical for the 65 kHz version, and -50 mV/ $\mu$ s for the 100 kHz version. The slope compensation can be observable as a value of the peak current at CS pin.

The internal slope compensation circuitry uses a sawtooth signal synchronized with the internal oscillator is subtracted from the FB voltage divided by  $K_{\rm FB}$ .

Figure 64. Slope Compensation Block Diagram

Figure 65. Slope Compensation Timing Diagram

#### **Internal Overpower Protection**

The power delivered by a flyback power supply is proportional to the square of the peak current in discontinuous conduction mode:

$$P_{OUT} = \frac{1}{2} \cdot \eta \cdot L_{P} \cdot F_{SW} \cdot I_{P}^{2} \qquad (eq. 3)$$

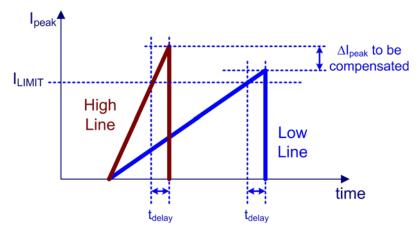

Unfortunately, due to the inherent propagation delay of the logic, the actual peak current is higher at high input voltage than at low input voltage, leading to a significant difference in the maximum output power delivered by the power supply.

Figure 66. Needs for Line Compensation For True Overpower Protection

To compensate this and have an accurate overpower protection, an offset proportional to the input voltage is added on the CS signal by turning on an internal current source: by adding an external resistor in series between the sense resistor and the CS pin, a voltage offset is created across it by the current. The compensation can be adjusted by changing the value of the resistor.

But this offset is unwanted to appear when the current sense signal is small, i.e. in light load conditions, where it would be in the same order of magnitude. Therefore the compensation current is only added when the FB voltage is higher than  $V_{FB(OPCE)}$ . However, because the HV pin is being connected to ac voltage, there is needed an additional circuitry to read or at least closely estimate the actual voltage on the bulk capacitor.

Figure 67. Overpower Protection Current Relation to Feedback Voltage

Figure 68. Overpower Protection Current Relation to Peak of Rectified Input Line AC voltage

Figure 69. Block Schematic of Overpower Protection Circuit

A 3 bit A/D converter with the peak detector senses the ac input, and its output is periodically sampled and reset, in order to follow closely the input voltage variations. The sample and reset events are given by the output from the ac

line unplug detector. The sensed HV pin voltage peak value is validated when no HV edges from comparator are present after last falling edge during two sample clocks. See Figure 70 for details.

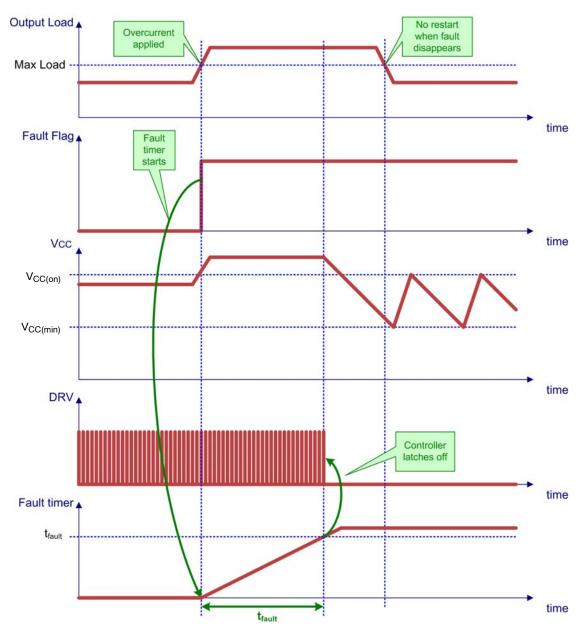

#### **Overcurrent Protection with Fault timer**

The overload protection depends only on the current sensing signal, making it able to work with any transformer, even with very poor coupling or high leakage inductance.

When an overcurrent occurs on the output of the power supply, the FB loop asks for more power than the controller can deliver, and the CS setpoint reaches  $V_{\rm ILIM}$ . When this event occurs, an internal  $t_{\rm fault}$  timer is started: once the timer times out, DRV pulses are stopped and the controller is either latched off (latched protection, options A/C) or this latch can be released in autorecovery mode (options B/D), the controller tries to restart after  $t_{\rm autorec}$ . Other possibilities of

the latch release are the brown–out condition or the  $V_{CC}$  power on reset. The timer is reset when the CS setpoint goes back below  $V_{ILIM}$  before the timer elapses. The fault timer is also started if the driver signal is reset by the maximum on time. The controller also enters the same protection mode if the voltage on the CS pin reaches 1.5 times the maximum internal setpoint  $V_{CS(stop)}$  (allows to detect winding short–circuits) or there appears low  $V_{CC}$  supply. See Figures 71 and 72 for the timing diagram.

In autorecovery mode if the fault has gone, the supply resumes operation; if not, the system starts a new burst cycle.

Figure 70. Overpower Compensation Timing Diagram

#### PROTECTION MODES AND THE LATCH MODE RELEASES

| Event                                                       | Timer Protection         | Next Device Status                                      | Release to Normal Operation Mode                                                             |

|-------------------------------------------------------------|--------------------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------|

| Overcurrent<br>V <sub>ILIM</sub> > 0.7 V                    | Fault timer              | Latch                                                   | Autorecovery – B/D version<br>Brown-out<br>V <sub>CC</sub> < V <sub>CC(reset)</sub>          |

| Maximum on time                                             | Fault timer              | Latch                                                   | Autorecovery – B/D version<br>Brown-out<br>V <sub>CC</sub> < V <sub>CC(reset)</sub>          |

| Winding short<br>V <sub>sense</sub> > V <sub>CS(stop)</sub> | Immediate reaction       | Latch                                                   | Autorecovery – B/D version<br>Brown-out<br>V <sub>CC</sub> < V <sub>CC(reset)</sub>          |

| Low supply<br>V <sub>CC</sub> < V <sub>CC(off)</sub>        | 10 μs timer              | Latch                                                   | Autorecovery – B/D version<br>Brown-out<br>V <sub>CC</sub> < V <sub>CC(reset)</sub>          |

| External OTP, OVP                                           | 55 μs (35 μs at 100 kHz) | Latch                                                   | Brown-out<br>V <sub>CC</sub> < V <sub>CC(reset)</sub>                                        |

| High supply V <sub>CC</sub> > V <sub>CC(ovp)</sub>          | 10 μs timer              | Latch                                                   | Brown-out<br>V <sub>CC</sub> < V <sub>CC(reset)</sub>                                        |

| Brown-out<br>V <sub>HV</sub> < V <sub>HV(stop)</sub>        | HV timer                 | Device stops                                            | $(V_{HV} > V_{HV(start)}) & (V_{CC} > V_{CC(on)})$                                           |

| Internal TSD                                                | 10 μs timer              | Device stops, HV start-up current source stops          | (V <sub>HV</sub> > V <sub>HV(start)</sub> ) & (V <sub>CC</sub> > V <sub>CC(on)</sub> ) & TSI |

| Off mode<br>V <sub>FB</sub> < V <sub>OFF</sub>              | 150 ms timer             | Device stops and internal V <sub>CC</sub> is turned off | $(V_{HV} > V_{HV(start)}) & (V_{CC} > V_{CC(on)}) & (V_{FB} > V_{ON})$                       |

Figure 71. Latched Timer-Based Overcurrent Protection (Options A/C)

Figure 72. Timer-Based Protection Mode with Autorecovery Release from Latch-off (Options B/D)

#### Latch-Off Input

Figure 73. Latch Detection Schematic

The Latch pin is dedicated to the latch-off function: it includes two levels of detection that define a working window, between a high latch and a low latch: within these two thresholds, the controller is allowed to run, but as soon as either the low or the high threshold is crossed, the controller is latched off. The lower threshold is intended to be used with an NTC thermistor, thanks to an internal current source I<sub>NTC</sub>.

An active clamp prevents the voltage from reaching the high threshold if it is only pulled up by the  $I_{NTC}$  current. To reach the high threshold, the pull-up current has to be higher than the pull-down capability of the clamp (typically 1.5 mA at  $V_{OVP}$ ).

To avoid any false triggering, spikes shorter than 50  $\mu$ s (for the high latch and 65 kHz version) or 350  $\mu$ s (for the low latch) are blanked and only longer signals can actually latch the controller.

Reset occurs when a brown-out condition is detected or the  $V_{CC}$  is cycled down to a reset voltage, which in a real application can only happen if the power supply is unplugged from the ac line.

Upon startup, the internal references take some time before being at their nominal values; so one of the comparators could toggle even if it should not. Therefore the internal logic does not take the latch signal into account before the controller is ready to start: once  $V_{\rm CC}$  reaches  $V_{\rm CC(on)}$ , the latch pin High latch state is taken into account and the DRV switching starts only if it is allowed; whereas the Low latch (typically sensing an over temperature) is taken into account only after the soft–start is finished. In addition, the NTC current is doubled to  $I_{\rm NTC(SSTART)}$  during the soft–start period, to speed up the charging of the Latch pin capacitor. The maximum value of Latch pin capacitor is given by the following formula (The standard start–up condition is considered and the NTC current is neglected):

$$C_{\text{LATCH max}} = \frac{t_{\text{SSTART min}} \cdot I_{\text{NTC(SSTART) min}}}{V_{\text{clamp0 min}}} = \frac{8.0 \cdot 10^{-3} \cdot 130 \cdot 10^{-6}}{1.0} F = 1.04 \ \mu F \ \ (\text{eq. 4})$$

Figure 74. Latch Timing Diagram

#### **Temperature Shutdown**

The NCP1247 includes a temperature shutdown protection with a trip point typically at 150°C and the typical hysteresis of 30°C. When the temperature rises above the high threshold, the controller stops switching instantaneously, and goes to the off mode with extremely