# Automotive 130 V High and Low Side Driver with Interlock and Dead Time

# DFNW10 (3x3)

# NCV51513

#### Description

NCV51513 is 130 V half bridge driver with high drive current capabilities and options for DC-DC power supplies and inverters. NCV51513 offers best in class propagation delay, low quiescent current and low switching current at high frequencies of operation.

This device is tailored for highly efficient power supplies operating at high frequencies. NCV51513 is offered in two versions for propagation delays. With filter version, it has a typical 50 ns propagation delay, while without filter version it has a typical propagation delay of 20 ns. Internal 80 ns dead time (xB version) and interlock function protect the output MOSFETs against cross conduction events. Enable functionality provides additional system flexibility and helps reducing power consumption.

#### **Features**

- High Voltage Range: Up to 130 V

- dV/dt Immunity Up to 50 V/ns

- Output Source / Sink Current Capability 2.0 A / 3.0 A

- Rise / Fall Time 9 ns / 7 ns for 1 nF Load

- Independent Logic Inputs 3.3 V and 5 V Compatible

- Enable Input

- Propagation Delay 50 ns Ay Version, 20 ns By Version

- Input Filter Time 30 ns for Ay Version and No Filter for By Version

- Dead Time Option

No Dead Time (xA Version)

Internal Fixed 80 ns Dead Time (xB Version)

- Input Cross-Conduction Prevention

- Extended Allowable Negative Bridge Pin Voltage Swing to -10 V @ Vcc = 10 V

- Matched Propagation Delays Between Both Channels Max 11 ns

- Independent Under Voltage Lock Out (UVLO) for Both Channels

- This is a Pb–Free Device

# **Typical Applications**

- 48 V Automotive DC/DC Converters

- On–Board Chargers

- Electric Power Steering

- 48 V BSB and ISG

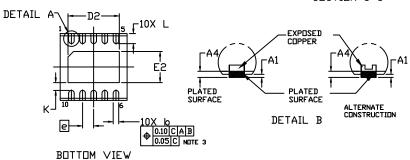

#### MARKING DIAGRAM

**CASE 507AG**

51513 Vxy ALYW

x = Input Noise Filter y = Internal Dead Time A = Assembly Location L = Wafer Lot

Y = Year W = Work Week • = Pb-Free Package

(Note: Microdot may be in either location)

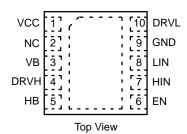

#### **PIN CONNECTION**

#### **ORDERING INFORMATION**

| Device          | Package             | Shipping <sup>†</sup> |

|-----------------|---------------------|-----------------------|

| NCV51513AAMNTWG | DFNW10<br>(Pb-free) | 3000 /<br>Tape & Reel |

| NCV51513ABMNTWG | DFNW10<br>(Pb-free) | 3000 /<br>Tape & Reel |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

# **QUICK SELECTION TABLE**

|                 |         | Drive C | Current<br>\] | _ Dead       |                | UVLO Levels<br>Max [V] |               | t <sub>r</sub> and t <sub>f</sub> at 1 nF<br>[ns] |      | Prop Delay<br>[ns] |     | Delay         |

|-----------------|---------|---------|---------------|--------------|----------------|------------------------|---------------|---------------------------------------------------|------|--------------------|-----|---------------|

| OPN             | Package | Source  | Sink          | Time<br>[ns] | Filter<br>[ns] | Vcc/Vb<br>ON           | Vcc/Vb<br>OFF | Rise                                              | Fall | ON                 | OFF | Match<br>[ns] |

| NCV51513AAMNTWG | DFNW10  | 2.0     | 3.0           | NA           | 30             | 7.1                    | 6.6           | 9                                                 | 7    | 50                 | 50  | 11            |

| NCV51513ABMNTWG | DFNW10  | 2.0     | 3.0           | 80           | 30             | 7.1                    | 6.6           | 9                                                 | 7    | 50                 | 50  | 11            |

# **OPTION TABLE**

| Suffix | Value | Description                        |

|--------|-------|------------------------------------|

| х      | А     | Input filter time 30 ns            |

| х      | В     | No input filter (on demand)        |

| у      | А     | No dead time                       |

| у      | В     | 80 ns fixed dead time              |

| у      | С     | 200 ns fixed dead time (on demand) |

**Table 1. PIN DESCRIPTION**

| Pin Out | Name | Function                                 |  |

|---------|------|------------------------------------------|--|

| 1       | VCC  | Power Ground                             |  |

| 2       | NC   | Not Connected                            |  |

| 3       | VB   | High Side Supply                         |  |

| 4       | DRVH | High Side Output                         |  |

| 5       | НВ   | High Side Supply Return, Half Bridge Pin |  |

| 6       | EN   | Enable Input                             |  |

| 7       | HIN  | High Side Input                          |  |

| 8       | LIN  | Low Side Input                           |  |

| 9       | GND  | Low Side and Logic Supply                |  |

| 10      | DRVL | Low Side Output                          |  |

| EP      | EP   | Connect the EP Flag to GND               |  |

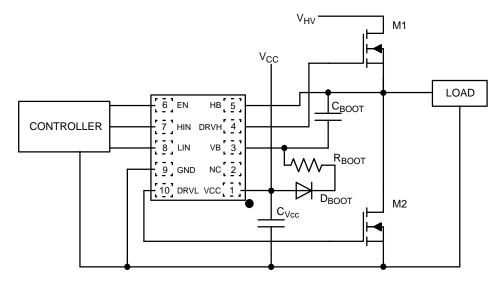

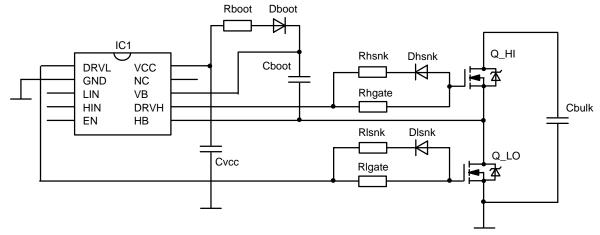

Figure 1. Typical Application Schematic

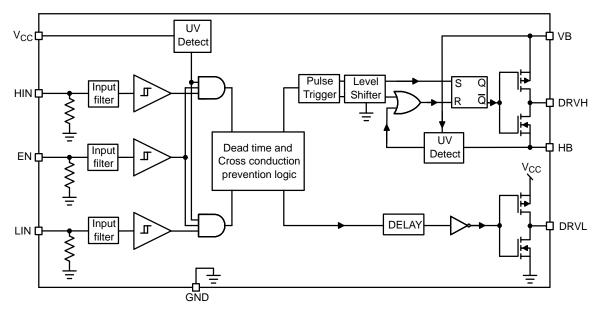

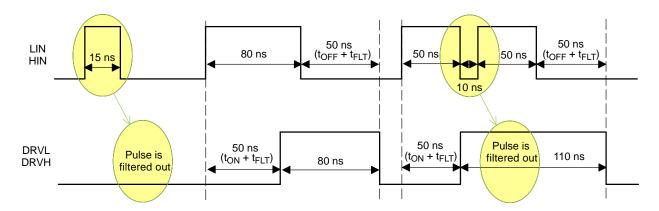

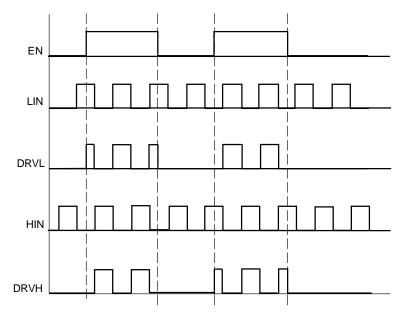

Figure 2. NCV51513Ay Version

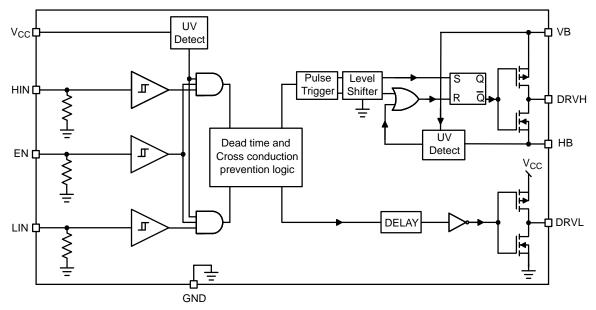

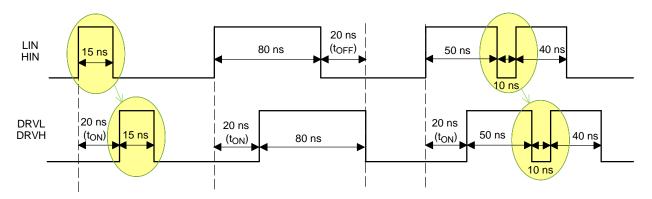

Figure 3. NCV51513By Version

#### **MAXIMUM RATINGS**

| Rating                                                                            | Symbol                              | Value                            | Units |

|-----------------------------------------------------------------------------------|-------------------------------------|----------------------------------|-------|

| Supply Voltage Range                                                              | V <sub>CC</sub>                     | -0.3 to 20                       | V     |

| High Side Boot Pin Voltage                                                        | V <sub>B</sub>                      | -0.3 to 150                      | V     |

| High Side Floating Voltage                                                        | $V_B-V_{HB}$                        | -0.3 to 20                       | V     |

| High Side Bridge Pin Voltage                                                      | V <sub>HB</sub>                     | $V_B - 20 \text{ to } V_B + 0.3$ | V     |

| High Side Drive Output Voltage                                                    | $V_{DRVH}$                          | $V_{HB}$ –0.3 to $V_{B}$ + 0.3   | V     |

| Low Side Output Voltage                                                           | $V_{DRVL}$                          | -0.3 to V <sub>CC</sub> + 0.3    | V     |

| Allowable Output Slew Rate                                                        | dV <sub>HB</sub> /dt                | 50                               | V/ns  |

| Inputs HIN, LIN                                                                   | V <sub>LIN</sub> , V <sub>HIN</sub> | −5 to V <sub>CC</sub> + 0.3      | V     |

| Input EN                                                                          | V <sub>EN</sub>                     | -0.3 to V <sub>CC</sub> + 0.3    | V     |

| Junction Temperature                                                              | T <sub>J_max</sub>                  | +150                             | °C    |

| Storage Temperature Range                                                         | T <sub>ST</sub>                     | −55 to +150                      | °C    |

| ESD Capability (Note 1):  - HBM Model  - CDM Model                                |                                     | 2000<br>1000                     | V     |

| Lead Temperature Soldering<br>Reflow (SMD Styles ONLY), Pb–Free Versions (Note 2) |                                     | 260                              | °C    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

Latchup Current Maximum Rating: ≤100 mA per JEDEC standard: JESD78E.

#### THERMAL CHARACTERISTICS

| Rating                                        | Symbol | Value | Units |

|-----------------------------------------------|--------|-------|-------|

| Thermal Resistance Junction to Air (Note 3)   | RθJA   | 157   | °C/W  |

| Junction to Top Characterization Parameter    | ΨЈ−Т   | 8.5   | °C/W  |

| Junction to Bottom Characterization Parameter | ΨЈ−В   | 0.12  | °C/W  |

<sup>3.</sup> Values based on copper area of 100 mm<sup>2</sup> 1 oz copper thickness and FR4 PCB substrate

# RECOMMENDED OPERATING CONDITIONS

| Rating                                | Symbol             | Min      | Max             | Unit |

|---------------------------------------|--------------------|----------|-----------------|------|

| Supply Voltage Range                  | V <sub>CC</sub>    | 8        | 19              | V    |

| Floating Supply Voltage Range         | $V_B-V_{HB}$       | 8        | 19              | V    |

| Bridge Pin Voltage Range @ Vcc = 10 V | $V_{HB}$           | -2       | 110             | V    |

| High Side Driver Voltage              | $V_{DRVH}$         | $V_{HB}$ | V <sub>B</sub>  | V    |

| Low Side Driver Voltage               | $V_{DRVL}$         | GND      | V <sub>CC</sub> | V    |

| Input Signal Voltage                  | $V_{HIN}, V_{LIN}$ | -3       | V <sub>CC</sub> | V    |

| Input Signal Voltage                  | V <sub>EN</sub>    | GND      | V <sub>CC</sub> | V    |

| Operating Junction Temperature Range  | $T_J$              | -40      | +125            | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

This device series incorporates ESD protection and is tested by the following methods. ESD Human Body Model tested perAEC-Q100-002(EIA/JESD22-A114)

ESD Charged Device Model tested per AEC-Q100-11(EIA/JESD22-C101E)

<sup>2.</sup> For information, please refer to our Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

# **ELECTRICAL CHARACTERISTICS**

$(VCC = VB = 12 \text{ V}, VGND = VHB, -40^{\circ}C < Tj < 125^{\circ}C, Outputs loaded with 1 nF, typical values are valid for 25^{\circ}C.$  All voltages are referenced to GND pin)

| Parameter                                                          | Symbol                               | Test Condition                                                    | Min | Тур  | Max  | Unit |

|--------------------------------------------------------------------|--------------------------------------|-------------------------------------------------------------------|-----|------|------|------|

| SUPPLY SECTION                                                     |                                      |                                                                   |     |      |      |      |

| V <sub>CC</sub> Current Consumption in Active Mode                 | I <sub>CC1</sub>                     | f <sub>SW</sub> = 100 kHz                                         | _   | 1.8  | 2.3  | mA   |

| V <sub>B</sub> Current Consumption in Active Mode                  | I <sub>B1</sub>                      | f <sub>SW</sub> = 100 kHz                                         | -   | 1.8  | 2.3  | mA   |

| V <sub>CC</sub> Current Consumption in Active Mode                 | I <sub>CC1_noload</sub>              | $f_{SW} = 100 \text{ kHz}, C_{LOAD} = 0$                          | -   | 0.6  | 1.2  | mA   |

| V <sub>B</sub> Current Consumption in Active Mode                  | I <sub>B1_noload</sub>               | $f_{SW} = 100 \text{ kHz}, C_{LOAD} = 0$                          | -   | 0.3  | 0.5  | mA   |

| Vcc Current Consumption in Active Mode                             | I <sub>CC2_EN_H</sub>                | $f_{SW} = 0 Hz, V_{EN} = 3 V$                                     | -   | 150  | 250  | μΑ   |

| V <sub>B</sub> Current Consumption in Active Mode                  | I <sub>B2_EN_H</sub>                 | $f_{SW} = 0 Hz, V_{EN} = 3 V$                                     | -   | 100  | 150  | μΑ   |

| V <sub>CC</sub> Current Consumption in Inhibition Mode             | I <sub>CC2</sub>                     | V <sub>EN</sub> = 0 V                                             | -   | 150  | 250  | μΑ   |

| V <sub>B</sub> Current Consumption in Inhibition Mode              | I <sub>B2</sub>                      | V <sub>EN</sub> = 0 V                                             | -   | 100  | 150  | μΑ   |

| Leakage Current on High Voltage Pins to GND                        | I <sub>HV_LEAK</sub>                 | V <sub>B</sub> = HB = DRVH = 130 V                                | -   | 2    | 5    | μΑ   |

| INPUT SECTION                                                      |                                      |                                                                   |     |      |      |      |

| Low Level Input Voltage Threshold                                  | $V_{xINL}$ , $V_{ENL}$               |                                                                   | _   | -    | 0.8  | V    |

| Input Pull-Down Resistor                                           | R <sub>xIN</sub>                     | $V_{xIN} = 5 \text{ V}, V_{EN} = 0 \text{ V}$                     | 100 | 175  | 250  | kΩ   |

| High Level Input Voltage Threshold                                 | V <sub>xINH</sub> , V <sub>ENH</sub> |                                                                   | 2.3 | -    | -    | V    |

| Enable Pin Pull-Down Resistor                                      | R <sub>EN</sub>                      | V <sub>EN</sub> = 5 V                                             | 60  | 95   | 135  | kΩ   |

| Logic "1" Input Bias Current                                       | I <sub>xIN+</sub>                    | V <sub>xIN</sub> = 5 V, V <sub>EN</sub> = 5 V                     | -   | 30   | 50   | μΑ   |

| Logic "0" Input Bias Current                                       | I <sub>xIN</sub> _                   | $V_{XIN} = 0 \text{ V}, V_{EN} = 0 \text{ V}$                     | -   | -    | 2.0  | μΑ   |

| Logic "1" Input Bias Current                                       | I <sub>EN+</sub>                     | V <sub>EN</sub> = 5 V                                             | -   | 50   | 85   | μΑ   |

| Logic "0" Input Bias Current                                       | I <sub>EN-</sub>                     | V <sub>EN</sub> = 0 V                                             | -   | -    | 2.0  | μΑ   |

| UVLO SECTION                                                       |                                      |                                                                   |     |      |      |      |

| V <sub>CC</sub> UV Start-Up Voltage Threshold                      | $V_{CCon}$                           |                                                                   | 5.8 | 6.4  | 7.0  | V    |

| V <sub>CC</sub> UV Shut-Down Voltage Threshold                     | $V_{CCoff}$                          |                                                                   | 5.3 | 5.9  | 6.5  | V    |

| Hysteresis on V <sub>CC</sub>                                      | V <sub>CChyst</sub>                  |                                                                   | 0.2 | 0.5  | -    | V    |

| Vboot Start-Up Voltage Threshold Reference to Bridge Pin           | V <sub>Bon</sub>                     | $V_{Bon} = V_{B} - HB$                                            | 5.8 | 6.4  | 7.0  | V    |

| Vboot UV Shut-Down Voltage Threshold                               | $V_{Boff}$                           |                                                                   | 5.3 | 5.9  | 6.5  | V    |

| Hysteresis on Vboot                                                | V <sub>Bhyst</sub>                   |                                                                   | 0.2 | 0.5  | _    | V    |

| Time between Vboot > V <sub>Bon</sub> & 1 <sup>st</sup> DRVH Pulse | t <sub>startup</sub>                 |                                                                   | -   | -    | 10   | μS   |

| OUTPUT SECTION                                                     |                                      |                                                                   |     |      |      |      |

| Output High Short Circuit Pulsed Current (Note 4)                  | I <sub>DRVxsource</sub>              | $V_{DRVx} = 0 \text{ V, PW} = 300 \text{ ns}$                     | -   | 2.0  | _    | Α    |

| Output Low Short Circuit Pulsed Current (Note 4)                   | I <sub>DRVxsink</sub>                | $V_{DRVx} = V_{CC} (V_B)$ , PW = 300 ns                           | -   | 3.0  | -    | Α    |

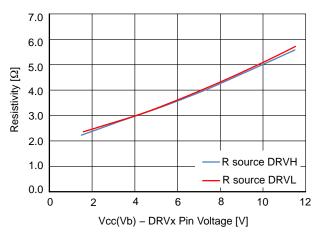

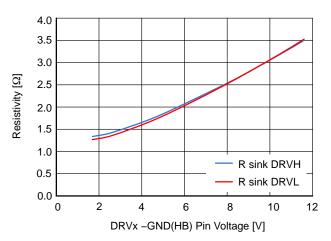

| Output Resistance Source                                           | R <sub>OH</sub>                      | I <sub>DRVx</sub> = 30 mA                                         | _   | 2.5  | 7    | Ω    |

| Output Resistance Sink                                             | R <sub>OL</sub>                      | I <sub>DRVx</sub> = 30 mA                                         | _   | 1.5  | 5    | Ω    |

| High Level Output Voltage                                          | V <sub>DRVx H</sub>                  | V <sub>BIAS</sub> – V <sub>DRVx</sub> @ I <sub>DRVx</sub> = 20 mA | _   | 0.06 | 0.25 | V    |

| Low Level Output Voltage                                           | V <sub>DRVx L</sub>                  | V <sub>DRVx</sub> @ I <sub>DRVx</sub> = 20 mA                     | _   | 0.04 | 0.15 | V    |

| OUTPUT RISE AND FALL TIME                                          | •                                    |                                                                   |     | •    | •    | -    |

| Output Voltage Rise Time (from 10% to 90%)                         | t <sub>r</sub>                       | V <sub>XIN</sub> = 3 V                                            | -   | 9    | 30   | ns   |

| Output Voltage Fall Time (from 90% to 10%)                         | t <sub>f</sub>                       | V <sub>XIN</sub> = 0 V                                            | _   | 7    | 25   | ns   |

# **ELECTRICAL CHARACTERISTICS** (continued)

$(VCC = VB = 12 \text{ V}, VGND = VHB, -40^{\circ}\text{C} < Tj < 125^{\circ}\text{C}, \text{ Outputs loaded with 1 nF, typical values are valid for 25^{\circ}\text{C}. All voltages are referenced to GND pin)}$

| Parameter                                                         | Symbol             | Test Condition                                                        | Min | Тур | Max | Unit |

|-------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------|-----|-----|-----|------|

| PROPAGATION DELAY NCV51513Ay                                      |                    |                                                                       |     |     |     |      |

| Turn-On Propagation Delay                                         | t <sub>ON</sub>    | HB = 0 V, 50 V or 130 V,<br>Cload = 0 pF, $V_{xIN}$ = 3 V             | -   | 50  | 100 | ns   |

| Turn-Off Propagation Delay                                        | t <sub>OFF</sub>   | HB = 0 V, 50 V or 130 V,<br>Cload = 0 pF                              | -   | 50  | 100 | ns   |

| Enable High Signal Propagation Delay                              | t <sub>EN</sub>    | HB = 0 V, 50 V or 130 V,<br>Cload = 0 pF, V <sub>xIN</sub> = 3 V      | -   | 50  | 100 | ns   |

| Enable Low Signal Propagation Delay                               | t <sub>ENoff</sub> | HB = 0 V, 50 V or 130 V,<br>Cload = 0 pF, V <sub>xIN</sub> = 3 V      | -   | 50  | 100 | ns   |

| Minimum Input Filter Time                                         | t <sub>FLT</sub>   | V <sub>xIN</sub> = 3 V                                                | 20  | 30  | -   | ns   |

| PROPAGATION DELAY NCV51513By                                      |                    |                                                                       |     |     |     |      |

| Turn-On Propagation Delay                                         | t <sub>ON</sub>    | HB = 0  V, 50  V or  130  V,<br>Cload = 0 pF, $V_{xIN} = 3 \text{ V}$ | -   | 20  | 40  | ns   |

| Turn-Off Propagation Delay                                        | t <sub>OFF</sub>   | HB = 0 V, 50 V or 130 V,<br>Cload = 0 pF                              | -   | 20  | 40  | ns   |

| Enable High Signal Propagation Delay                              | t <sub>EN</sub>    | HB = 0 V, 50 V or 130 V,<br>Cload = 0 pF, V <sub>XIN</sub> = 3 V      | -   | 20  | 40  | ns   |

| Enable Low Signal Propagation Delay                               | t <sub>ENoff</sub> | HB = 0 V, 50 V or 130 V,<br>Cload = 0 pF, V <sub>xIN</sub> = 3 V      | -   | 20  | 40  | ns   |

| DELAY MATCHING                                                    |                    |                                                                       |     |     |     |      |

| Propagation Delay Matching between the High Side and the Low Side | Δt                 | V <sub>XIN</sub> = 3 V                                                | -   | 0   | 11  | ns   |

| TIMING                                                            |                    |                                                                       | _   |     |     |      |

| Minimum Input Width that Changes the Output (B Version Only)      | t <sub>PW</sub>    | V <sub>xIN</sub> = 3 V                                                | -   | -   | 10  | ns   |

| Internal Dead Time (B Version Only)                               | t <sub>DT</sub>    | V <sub>xIN</sub> = 3 V                                                | 60  | 80  | 100 | ns   |

| Dead Time Matching (B Version Only)                               | $\Delta t_{DT}$    |                                                                       | -   | 2   | 20  | ns   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

4. Parameter guaranteed by design.

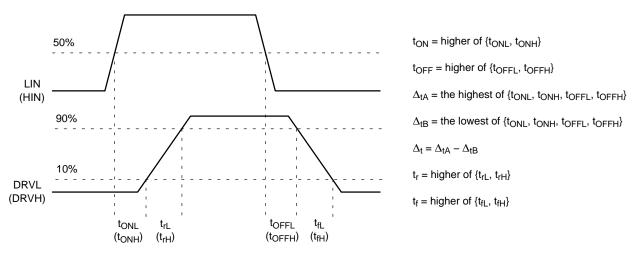

Figure 4. Propagation Delay, Propagation Delay Matching, Rise Time and Fall Time Testing

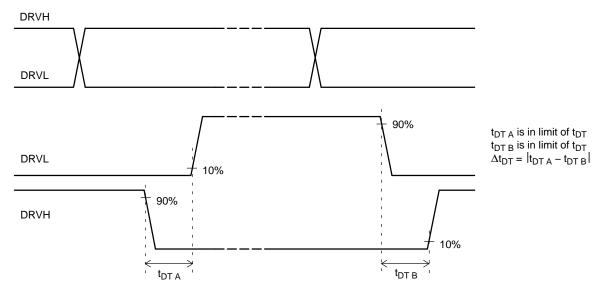

Figure 5. Dead Time and Dead Time Matching Measurement (xB Version Only)

# TYPICAL ELECTRICAL CHARACTERISTICS

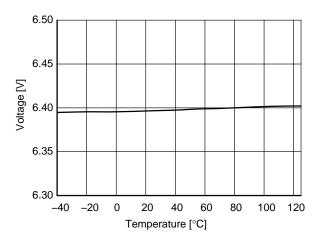

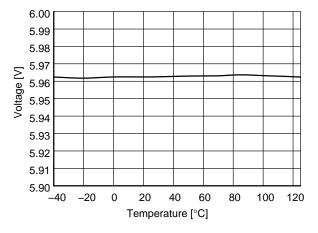

Figure 6.  $V_{CCon}$  vs. Temperature

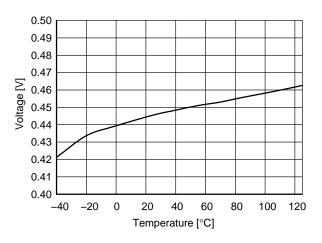

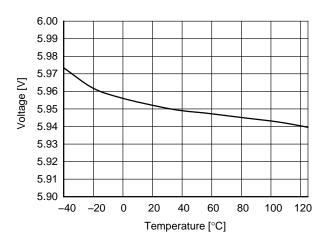

Figure 8. V<sub>CChyst</sub> vs. Temperature

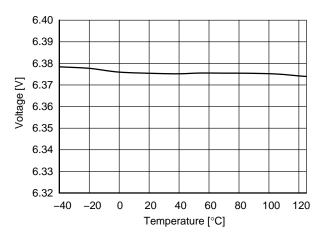

Figure 10.  $V_{Boff}$  vs. Temperature

Figure 7.  $V_{CCoff}$  vs. Temperature

Figure 9. V<sub>Bon</sub> vs. Temperature

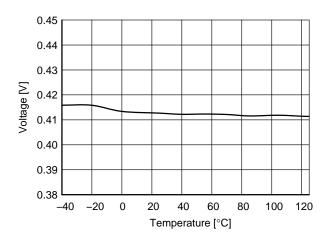

Figure 11. V<sub>Bhyst</sub> vs. Temperature

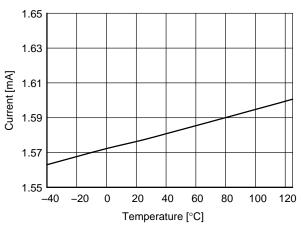

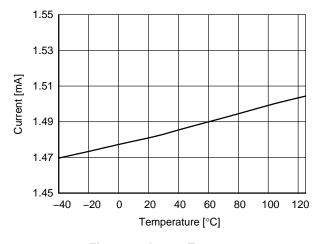

Figure 12.  $I_{CC1}$  vs. Temperature

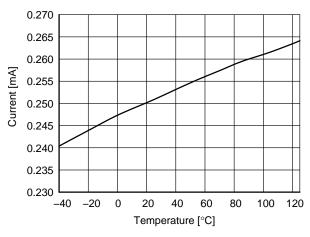

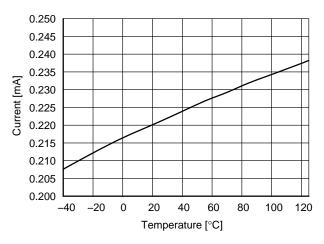

Figure 13.  $I_{CC1 \ noload}$  vs. Temperature

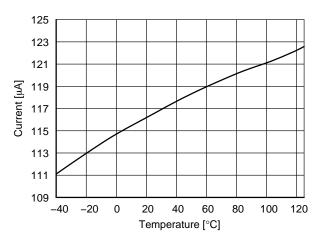

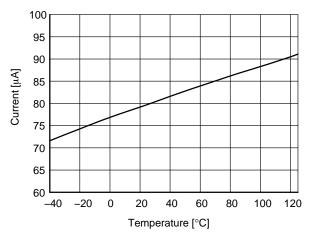

Figure 14. I<sub>CC2 EN H</sub> vs. Temperature

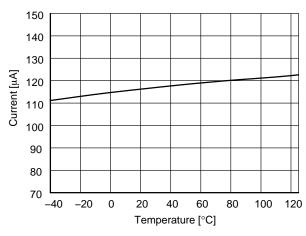

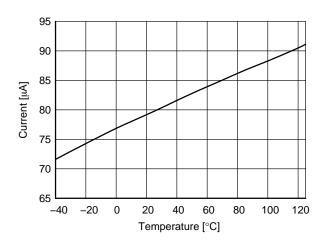

Figure 15. I<sub>CC2</sub> vs. Temperature

Figure 16. I<sub>B1</sub> vs. Temperature

Figure 17.  $I_{B1 \ noload}$  vs. Temperature

Figure 18. I<sub>B2 EN H</sub> vs. Temperature

Figure 19. I<sub>B2</sub> vs. Temperature

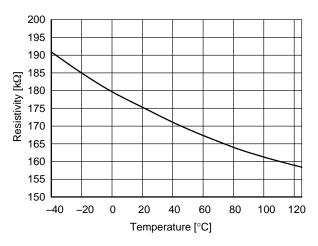

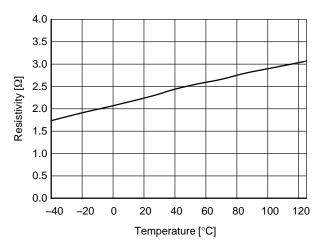

Figure 20. R<sub>xIH</sub> vs. Temperature

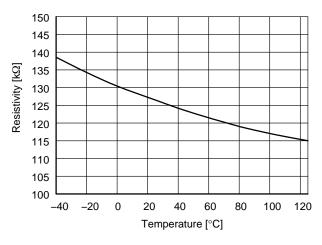

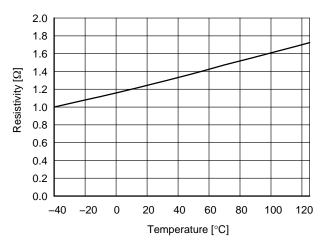

Figure 21. R<sub>EN</sub> vs. Temperature

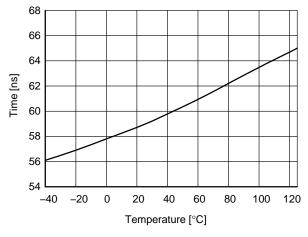

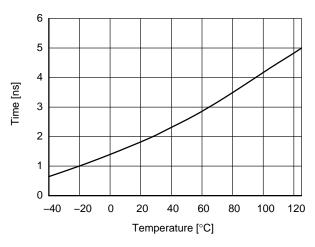

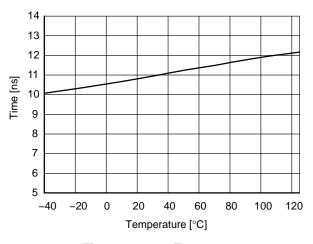

Figure 22. t<sub>ON</sub> vs. Temperature (Ay Version Only)

Figure 23. t<sub>OFF</sub> vs. Temperature (Ay Version Only)

Figure 24.  $\Delta t$  vs. Temperature

Figure 25. t<sub>EN</sub> vs. Temperature (Ay Version Only)

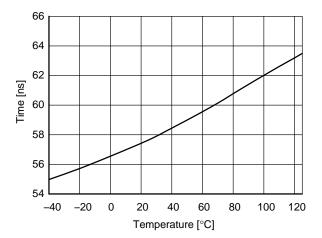

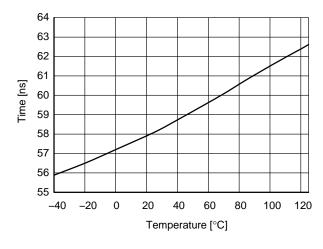

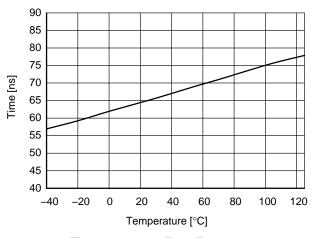

Figure 26. t<sub>DT</sub> vs. Temperature (xB Version Only)

Figure 27.  $\Delta t_{DT}$  vs. Temperature (xB Version Only)

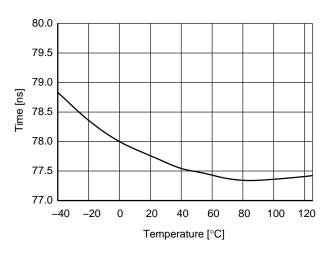

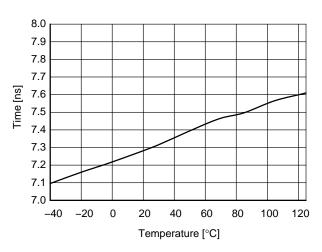

Figure 28. t<sub>r</sub> vs. Temperature

Figure 29. t<sub>f</sub> vs. Temperature

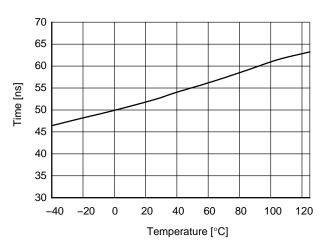

Figure 30. t<sub>r</sub> 10 nF vs. Temperature

Figure 31. tf 10 nF vs. Temperature

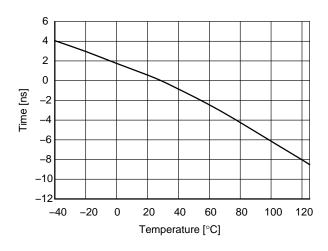

Figure 32. R<sub>OH</sub> vs. Temperature

Figure 33. R<sub>OL</sub> vs. Temperature

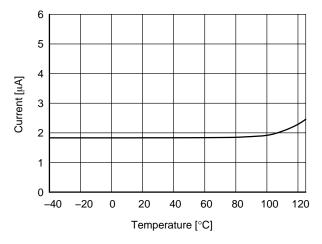

Figure 34.  $I_{HV\_leak}$  vs. Temperature

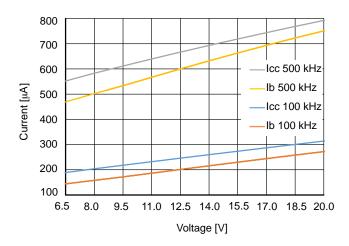

Figure 35. Current Consumption vs. Voltage. Cload = 0 nF

#### TYPICAL ELECTRICAL CHARACTERISTICS (continued)

Figure 36. DRVx Source Resistance. 25°C. GBD

#### **General Description**

For popular topologies like LLC, half bridge full brige converters, synchronous buck converters, etc. low—side and high—side drivers are needed which perform the function of both buffer and level shifter. These devices can drive the gate of the topside MOSFETs whose source node is a dynamically changing node. The bias for the high side driver in these devices is usually provided through a bootstrap circuit.

In a bid to make modern power supplies more compact and efficient, power supply designers are increasingly opting for high frequency operations. High frequency operation causes higher losses in the drivers, hence reducing the efficiency of the power supply.

NCV51513 are 130 V high side-low side drivers for DC-DC power supplies and inverters. NCV51513 offer best in class propagation delay, low quiescent current and low switching current at high frequencies of operation. This device thus enables highly efficient power supplies operating at high frequencies.

NCV51513 are available in two versions, NCV51513Ay or By. The Ay version includes a 30 ns input filter time, so propagation delay is 50 ns, the By version is without any filter, the propagation delay is reduced to 20 ns.

NCV51513 also offers Dead Time options. There are versions without any dead time (xA version) that let designers insert the dead time their application needs and versions (xB version) with an internal 80 ns dead time to eliminate cross conduction of the output MOSFETs. Interlock function is available in both versions.

NCV51513 have three input pins HIN, LIN and EN, allowing it to be used in a variety of applications. This device also includes features where in case of floating input, the

Figure 37. DRVx Sink Resistance. 25°C. GBD

logic is still defined. Driver inputs are compatible with both CMOS and TTL logic hence it provides easy interface with analog and digital controllers. NCV51513 has under voltage lock out feature for both high and low side drivers which ensures operation at correct  $V_{CC}$  and  $V_{B}$  voltage levels.

The output stage of NCV51513 has 2.0/3.0 A source/sink capability which can effectively charge and discharge a 1nF load in 9/7 ns.

#### **Features**

#### **Input Stages**

NCV51513 driver have three input pins HIN, LIN and EN, allowing it to be used in a variety of applications. The input stages of NCV51513 are TTL and CMOS compatible. This ensures that the inputs of NCV51513 can be driven with 3.3 V or 5 V logic signals from analog or digital PWM controllers or logic gates.

The input pins have Schmitt triggers to avoid noise induced logic errors.

NCV51513 come with an important feature wherein outputs (DRVH, DRVL) stays low in case any of the input pin is floating. At all the input pins there is an internal pull down resistor to define its logic value in case the pin is left open or NCV51513 are driven by open drain signal.

NCV51513Ay features a noise rejection function to ensure that any pulse glitch shorter than 30 ns will not produce any output change. This feature is well illustrated in the Figure 39.

NCV51513By have no such filter in the input stages. The timing diagram NCV51513By is depicted in Figure 39.

Enable pin in L state sets both outputs to L state. Enable pin in H state lets outputs to switch according to input signals. See Figure 40 for more details.

Figure 38. Version with Input Filter (NCV51513Ay)

Figure 39. Version without Input Filter (NCV51513By)

Figure 40. Enable Pin Function

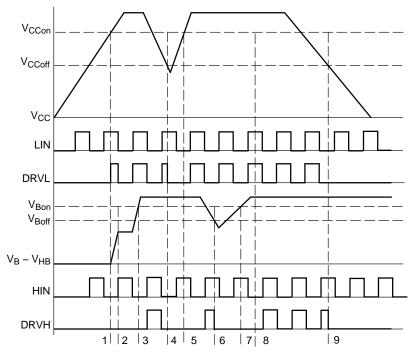

#### **Under Voltage Lock-Out**

NCV51513 has under voltage lockout protection on both the high side and the low side driver. The function of the UVLO circuits is to ensure that there is enough supply voltages ( $V_{CC}$  and  $V_{B}$ ) to correctly bias high side and low side circuits. This also ensures that the gate of external MOSFETs are driven at an optimum voltage. If the  $V_{CC}$  is below the  $V_{CC}$  UVLO voltage, the low side driver output (DRVL) and high side driver output (DRVH) both remain low. If  $V_{B}$  is below  $V_{Boff}$  UVLO voltage the high side driver output (DRVH) remains low. However if the  $V_{CC}$  is above  $V_{CCon}$  UVLO voltage level, the low side driver output

(DRVL) can still turn on and off based on the low side driver input (LIN) and is not affected by the  $V_B$  status. This ensures proper charging of the bootstrap capacitor to bring the high side bias supply  $V_B$  above UVLO voltage. Both the  $V_{CC}$  and  $V_B$  UVLO circuits are provided with hysteresis feature. This hysteresis feature avoids errors due to ground noise in the power supply. The hysteresis also ensures continuous operation in case of a small drop in the bias voltage. This drop in the bias can happen when device starts switching MOSFET and the operating current of the device increases. The UVLO feature of the device is explained in the Figure 41.

#### Legend:

- 1. Vcc crossed Vcc ON level, LIN is set to H. The DRVH is set to H immediately. Current starts to flow from Vcc to Cboot via bootstrap diode.

- 2. Cboot is not fully charged in first pulse.

- Vb cross Vbon level. HIN is in L, output stays in L. Both UVLOs are activated, pulses Can pass the driver.

- 4. Vccoff level is activated, DRVL is set to L, DRVH had been in L, it stayes in L

- 5. Vccon level crossed, HS UVLO had been activated earlier, the pulse is ignored.

- Vboff level crossed while DRVH is H. DRVH is set to L immediately.

- 7. Vbon level crossed. Current (ongoing) HIN pulse is ignored.

- 8. Both UVLOs are activated, all pulses passes the driver. Steady state conditions.

- 9. Vccoff level is croosed while DRVH is in H. Both drivers are inhibited, DRVH is set to L immediately. From now on, no pulse will pass the driver (LS nor HS).

Figure 41. UVLO Timing Diagram

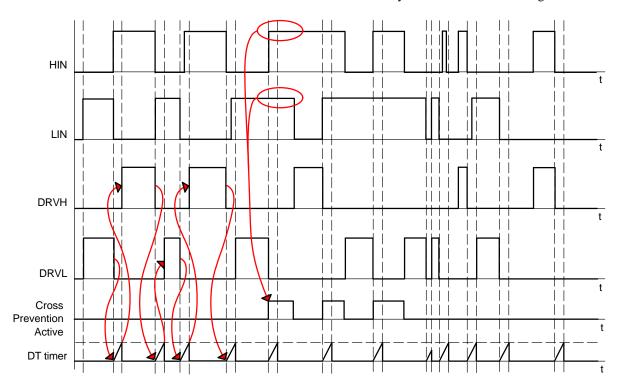

#### **Dead Time Control & Interlock**

NCV51513xB features inbuild 80 ns dead control logic. The logic inserts the 80 ns delay after any driver turn off to postpone turn on of the opposite one. The delay helps to minimize cross conduction current through the MOSFETs when one is switched off and simultaneously other one is

switched on. Version NCV51513xA offer no dead time, this version is better for high frequency application with external dead time control. Both versions NCV51513xA and xB are equipped with cross conduction prevention logic (interlock), which does not let to set both drivers to High simultaneously. See detail function in Figure 42.

Figure 42. Dead Time Timing Diagram, NCV51513xB

Figure 43. Interlock Timing Diagram, NCV51513xA

**Table 2. TRUE TABLE**

| #  | Vcc Supply           | Vb Supply          | EN | LIN | HIN | DRVL       | DRVH       |

|----|----------------------|--------------------|----|-----|-----|------------|------------|

| 1  | Vcc < Vccoff         | Vb = x             | х  | х   | х   | L (Note 7) | L (Note 7) |

| 2  | Vcc > Vccon (Note 5) | Vb = x             | L  | х   | х   | L          | L (Note 7) |

| 3  | Vcc > Vccon (Note 5) | Vb < Vboff         | Н  | L   | х   | L          | L          |

| 4  | Vcc > Vccon (Note 5) | Vb < Vboff         | Н  | Н   | L   | Н          | L          |

| 5  | Vcc > Vccon (Note 5) | Vb > Vbon (Note 5) | Н  | L   | L   | L          | L          |

| 6  | Vcc > Vccon (Note 5) | Vb > Vbon (Note 5) | Н  | Н   | L   | Н          | L          |

| 7  | Vcc > Vccon (Note 5) | Vb > Vbon (Note 5) | Н  | L   | Н   | L          | Н          |

| 8  | Vcc > Vccon (Note 5) | Vb > Vbon (Note 5) | Н  | Н   | Н   | L          | L          |

| 9  | Vcc ↑ Vccon (Note 6) | Vb < Vboff         | Н  | L   | х   | L          | L          |

| 10 | Vcc ↑ Vccon (Note 6) | Vb < Vboff         | Н  | Н   | L   | L↑H        | L          |

| 11 | Vcc ↑ Vccon (Note 6) | Vb > Vbon (Note 5) | Н  | L   | L   | L          | L          |

| 12 | Vcc ↑ Vccon (Note 6) | Vb > Vbon (Note 5) | Н  | L   | Н   | L          | L          |

| 13 | Vcc > Vccon (Note 6) | Vb ↑ Vbon (Note 6) | Н  | L   | Н   | L          | L          |

| 14 | Vcc ↓ Vccoff         | Vb > Vbon (Note 5) | Н  | Н   | L   | H↓L        | L          |

| 15 | Vcc ↓ Vccoff         | Vb > Vbon (Note 5) | Н  | L   | Н   | L          | H↓L        |

| 16 | Vcc > Vccon (Note 5) | Vb ↓ Vboff         | Н  | Н   | L   | Н          | L          |

| 17 | Vcc > Vccon (Note 5) | Vb ↓ Vboff         | Н  | L   | Н   | L          | H↓L        |

<sup>5.</sup> The voltage has crossed Vcc/Vb on level and it is higher than Vcc/Vb off level. 6. The voltage is rising from 0 V. 7. If the Vcc/Vb is lower than 3 V, the driver is pulled down via 150 k $\Omega$ .

NOTE: x – Any value

#### **Output Stages**

NCV51513 are equipped with two independent drivers with typical source/sink current is 2.0/3.0 A. The driver can effectively charge/discharge a 1 nF load in 9/7 ns. NCV51513 output drivers can not be turned on at the same time. The xB version feature internal dead time generator, which inserts 80 ns dead time to eliminate short through current through the MOSFETs. See Figure 42.

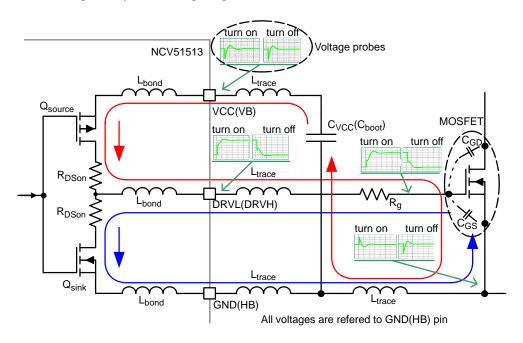

The Figure 44 shows the output stage structure and the charging and discharging path of the external power MOSFET. The bias supply  $V_{CC}$  or  $V_B$  supplies energy to charge the gate capacitance  $C_{gs}$  of the low side or the high side external MOSFETs respectively. When a logic high is

received from input stage, Qsource turns on and  $V_{CC}/V_B$  starts charging  $C_{gs}$  through  $R_g$ . Once the  $C_{gs}$  is charged to the drive voltage level, the external power MOSFET turns on and connects HB pin either to GND node (low side switch) or to HV line (high side switch).

When a logic low signal is received from the input stage, Qsource turns off and Qsink turns on providing a path for gate terminal discharging.

As seen in the Figure 44, there are parasitic inductances in charging and discharging path of the  $C_{gs}$ . This can result in a little dip in the bias voltages  $V_{CC}/V_B$ . If the  $V_{CC}/V_B$  drops below UVLO level, the power supply can shut down the device

Figure 44. NCV51513 Turn ON-OFF Paths

## **Short Propagation Delay**

NCV51513 boast short propagation delay between input and output. NCV51513Ay have a typical of 50 ns propagation delay. The best in class propagation delay in NCV51513 makes it suitable for high frequency operation.

Since NCV51513By doesn't have the input filter included, the propagation delays are even faster.

NCV51513By offers 20 ns propagation delay between input and output.

The device allows 100 % duty cycle operation. The DRVH or DRVL can be continuously in H or L state. It is necessary to have a floating source to supply DRVH driver when using the driver under this 100% DC.

# **Negative Transient Immunity (NTI) Operating Conditions**

In any HB switching applications the HB node is often pulled under the ground during the switching operation because of parasitic inductances and inductive load. These negative spikes may lead to malfunction or damage of the circuit.

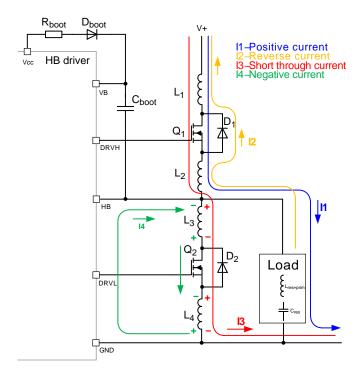

Below schematics depicts parasitic and current circulation during switching operations that could create the negative deep of the HB node.

Figure 45. HB Negative Voltage in an LLC Configuration

# **NTI Robustness Measurement**

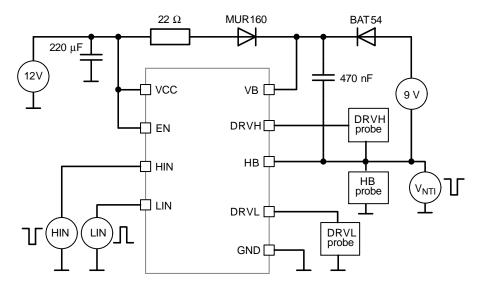

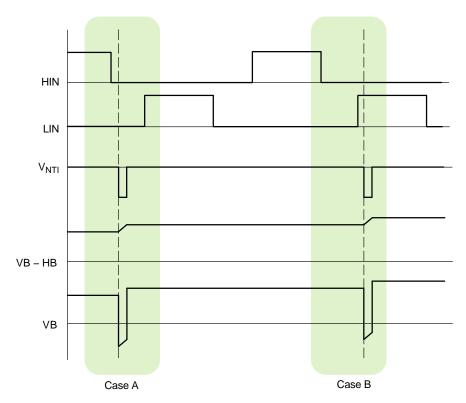

The capability of NCV51513 to operate under negative voltage conditions is reported in NTI graph using below test set up.

Figure 46. NTI Test Set Up

Figure 47. Timing Diagram

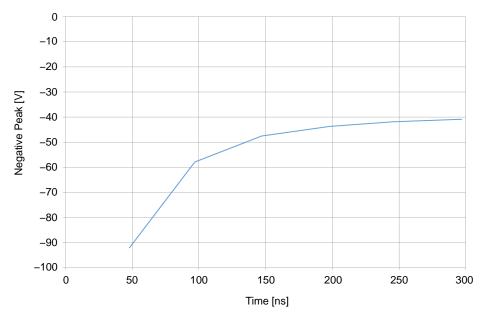

NCV51513 robustness against negative spikes is shown in Figure 48. The result is a curve which shows negative

voltage level for specific pulse width under which driver could still operate properly.

Figure 48. Indicative Negative Transient Immunity

## Important note:

Even though above figure shows that NCV51513 is able to handle negative transient voltage conditions, it is highly recommended that the application circuit design is such that

it removes or at least always limit the negative transient voltage on VB pin as much as possible via careful PCB layout and proper component selection.

#### **Applications information & Component Selection**

This section outlines the key design steps and components selection to get full benefit of NCV51513 performances. It

includes as well some power dissipation considerations and layout recommendations.

Figure 49. Recommended Schematic

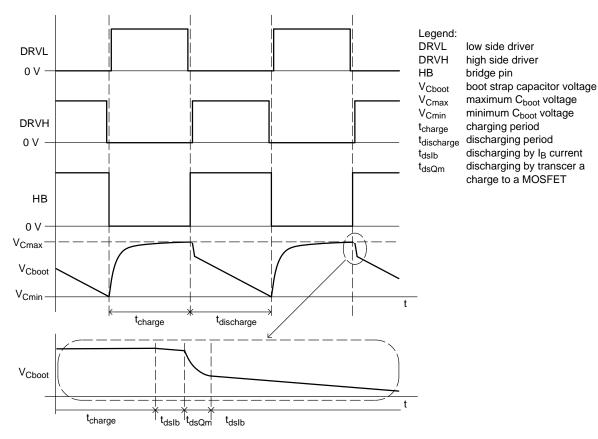

## **C**boot Capacitor Value Calculation

The device features two independent drivers. The low side driver (DRVL) supplies a MOSFET whose source is connected to ground. The driver is powered from  $V_{CC}$  line. The high side driver (DRVH) supplies a MOSFET whose source is floating from GND to bulk voltage. The floating driver is powered from  $C_{boot}$  capacitor. The capacitor is charged only when HB pin is pulled to GND (by inductance or the low side MOSFET when turned on). If too small  $C_{boot}$  capacitor is used the high side UVLO protection can disable the high side driver which leads to improper switching.

Expected voltage on Cboot is pictured in Figure 50. The curves are valid for ZVS (Zero Voltage Switching) observed in LLC applications. For hard switch the curves are slightly different, but from charge on C<sub>boot</sub> point of view more favorable. Under the hard switch conditions the energy to

charge  $Q_g$  (from zero voltage to  $V_{th}$  of the MOSFET) is taken from  $V_{CC}$  capacitor (through an external boot strap diode) so the voltage drop on  $C_{boot}$  is smaller. For the calculation of  $C_{boot}$  value the ZVS conditions are taken account.

The switching cycle is divided into two parts, the charging ( $t_{charge}$ ) and the discharging ( $t_{discharge}$ ) of the  $C_{boot}$  capacitor. The discharging can be divided even more to discharging by floating driver current consumption  $I_{B2}$  ( $t_{dsIb}$ ), and to discharging by transfering energy from  $C_{boot}$  to gate terminal of the MOSFET ( $t_{dsQm}$ ) and discharging by leakage current of the bootstrap diode (not taken account). Discharging by  $I_{CC4}$  becoming more dominant when driver runs at lower frequencies and/or during skip mode operation. To calculate  $C_{boot}$  value, follow these steps:

Figure 50. Boot Strap Capacitor Charging

- 1. For example, let's have a MOSFET with  $Q_g = 49$  nC,  $V_{DD} = 10$  V.

- 2. Charge stored in  $C_{boot}$  necessary to cover the period the  $C_{boot}$  is not supplied from  $V_{CC}$  line (which is basically the period the high side MOSFET is turned on). Let's say the application is switching at 100 kHz, 50% duty cycle, which means the upper MOSFET is conductive for 5  $\mu$ s. It means the  $C_{boot}$  is discharged by  $I_{B2}$  current (100  $\mu$ A typ) for 5  $\mu$ s, so the charge consumed by floating driver is:

$$Q_b = I_{B2} \cdot t_{discharge} = 100 \ \mu \cdot 5 \ \mu = 500 \ pC \qquad \text{(eq. 1)}$$

Total charge loss during one switching cycle is sum of charge to supply the high side driver and MOSFET's gate charge:

$$Q_{tot} = Q_g + Q_b = 49 \text{ n} + 500 \text{ p} = 49.5 \text{ nC}$$

(eq. 2)

4. Let's determine acceptable voltage ripple on  $C_{boot}$  to 1% of nominal value, which is 100 mV. To cover charge losses from Eq. 2.

$$C_{boot} = \frac{Q_{tot}}{V_{ripple}} = \frac{49.5 \text{ n}}{0.1} = 495 \text{ nF}$$

(eq. 3)

# **R**boot Resistor Value Calculation

To keep the application running properly, it is necessary to charge the  $C_{boot}$  again. This is done by external diode from  $V_{CC}$  line to VB pin. In serial with the diode a resistor is placed to reduce the current peaks from  $V_{CC}$  line. The

resistor value selection is critical for proper function of the high side driver. If too small high current peaks are drown from  $V_{CC}$  line, if too high the capacitor will not be charged to appropriate level and the high side driver can be disabled by internal UVLO protection.

First of all keep in mind the capacitor is charged through the external bootstrap diode, so it can be charged to a maximum voltage level of  $V_{CC} - V_f$ . The resistor value is calculated using this equation:

$$\begin{split} R_{boot} &= \frac{t_{charge}}{C_{boot} \cdot ln \bigg( \frac{V_{max} - V_{Cmin}}{V_{max} - V_{Cmax}} \bigg)} \\ &= \frac{5 \, \mu}{1 \, \mu \cdot ln \bigg( \frac{9.4 - 9.25}{9.4 - 9.35} \bigg)} \cong 4.6 \, \Omega \end{split}$$

(eq. 4)

Where:

$V_{max}$

t<sub>charge</sub> time period the Cboot is being charged, usually the period the low side MOSFET

is turned on,

C<sub>boot</sub> boot strap capacitor value,

maximum voltage the  $C_{boot}$  capacitor can be theoretically charged to. Usually the  $V_{CC} - V_f$ . The  $V_f$  is forward voltage of used diode,

the voltage level the capacitor is charge  $V_{Cmin}$ from,

$V_{Cmax}$

the voltage level the capacitor is charged to. It is necessary to determine the target voltage for charging, because in theory, when a capacitor is charged from a voltage source through a resistor, the capacitor can never reach the voltage of the source. In this particular case a 50 mV difference (between the voltage behind the diode and  $V_{Cmax}$ ) is used.

The resistor value obtained from Eq. 4 does not count with the quiescent current I<sub>B2</sub> of the high side driver. This current will create another voltage drop of:

$$V_{IB2\_drop} = \, R_{boot} \cdot I_{B2} = \, 4.6 \, \cdot \, 100 \, \mu \, \cong \, 460 \, \mu V \quad \text{(eq. 5)}$$

The current consumed by high side driver will be higher, because the I<sub>B2</sub> is valid when the device is not switching. While switching, losses by charging and discharging internal transistors as well as the level shifters will be added. This current will increase with frequency.

The additional 460  $\mu V$  drop will be added to  $V_{Cmax}$  value. The additional 460 µV drop can be either accepted or the R<sub>boot</sub> value can be recalculated to eliminate this additional drop.

The resistor R<sub>boot</sub> calculated in Eq. 4 is valid under steady state conditions. During start and/or skip operation the starting point voltage value is different (lower) and it takes more time to charge the boot strap capacitor. More over it is not counted with temperature and voltage variability during normal operation or the dynamic resistance of the boot strap diode (approximately 0.34  $\Omega$  for MURA160). From these reasons the resistor value should be decreased especially with respect to skip operation.

Boot strap resistor loss calculation.

$$P_{Rboot} \cong Q_{tot} \cdot V_{max} \cdot f = 49.5 \text{ n} \cdot 9.4 \cdot 100 \text{ k} \cong 46.3 \text{ mW}$$

(eq. 6)

Boot strap diode loss calculation.

$$P_{Dboot} \cong Q_{tot} \cdot V_f \cdot f = 49.5 \text{ n} \cdot 0.6 \cdot 100 \text{ k} \cong 3 \text{ mW}$$

(eq. 7

Please keep in mind the value is temperature and voltage dependent. Especially Cboot voltage can be higher than calculated value. See "Layout recommendation" section for more details. Also keep in mind, the Boot strap resistor power dissipation calculated in Eq. 6 is valid for steady state conditions. For first Cboot charging, the power loss (the current) is much higher.

$$I_{Rboot} = \frac{C_{Vcc} - V_{Dboot} - V_{Cboot}}{R_{boot}} = \frac{10 - 0.6 - 0}{4.6} \cong 2 \text{ A}$$

(eq. 8)

$$P_{Rboot} = (C_{Vcc} - V_{Dboot} - V_{Cboot}) \cdot I_{Rboot}$$

$$= (10 - 0.6 - 0) \cdot 2 \cong 18.8 \text{ W}$$

(eq. 9)

The Boot strap resistor must be designed to accept the current from Eq. 8 and power loss from Eq. 9 for a while.

#### **V<sub>CC</sub>** Capacitor Selection

V<sub>CC</sub> capacitor value should be selected at least ten times the value of  $C_{boot}$ . In this case thus  $C_{Vcc} > 10 \mu F$ .

Very close to the driver should be placed a ceramic capacitor at least the same value of C<sub>boot</sub>, to cover current peaks for low side MOSFET gate charging.

#### R<sub>gate</sub> Selection

The R<sub>gate</sub> are selected to limit the peak gate current during charging and discharging of the gate capacitance. This resistance also helps to damp the ringing due to the parasitic inductances, reduce dV/dt on HB pin to safe level and attenuate EMI radiation. If high dV/dt (during rise/fall edge and/or ringing after switching) is applied on HB pin, it can cause unexpected behavior of the driver.

On the other hand, too high resistor will increase power loss on MOSFETs, which leads to lower efficiency. It is recommended to start evaluation with a high resistor value and decrease the value if behavior is safe under all conditions. We recommend to have at least a 4.7  $\Omega$  resistor between NCV51513 outputs and MOSFET's gate.

The resistors also help to decrease power dissipation of the driver, because part of the energy from charging and discharging  $C_{gs}$  is radiated on the resistors  $R_{xgate}$  (and on R<sub>xsnk</sub> if they are used) outside the driver see Figure 49. The gate resistor selection is tricky task. It depends on application, topology, on used MOSFETs, layout etc.

For example for an  $R_{xgate}$  value of 4.7  $\Omega$ , the peak source and sink currents would be limited to the following values.

$$I_{DRVL\_Source} = \frac{V_{cc}}{R_{Lgate} + R_{LOL} + R_g} = \frac{10 \text{ V}}{12.7 \Omega} = 787 \text{ mA}$$

(eq. 10)

$$I_{DRVL\_Sink} = \frac{V_{cc}}{R_{Lgate} + R_{LOL} + R_g} = \frac{10 \text{ V}}{10.7 \Omega} = 935 \text{ mA}$$

(eq. 11)

Where:

R<sub>DSon</sub> of internal source MOSFET  $R_{LOH}$ (see parametric table R<sub>OH</sub> parameter),

R<sub>DSon</sub> of internal sink MOSFET  $R_{LOL}$ (see parametric table R<sub>OL</sub> parameter),

Rg internal gate resistance of external MOSFET (see appropriate DS), in this

case 1  $\Omega$ .

In some applications it is desired/advantageous to use separated current paths for charging and discharging the gate capacitance. For this purpose external MOSFET gate connection must be extended (see Figure 49). Two components Rxsnk and Dxsnk can be added in parallel to Rxgate resistor. The charging path is now only through

Rxgate resistor, while discharging path is through Rxsnk and Rxgate in parallel combination. Consider both resistors are the same value  $10~\Omega$ . The source current is calculated using Eq. 10. The current is 556 mA.

$$R_{lgate} = 10 \Omega$$

$$\begin{split} I_{DRVL_{Sink}} &= \frac{V_{cc}}{R_{lgate} + (R_{LOL} + R_g) \cdot 2} + \frac{V_{cc} - V_{Dlsnk}}{R_{lsnk} + (R_{LOL} + R_g) \cdot 2} \\ &= \frac{10 \text{ V}}{22 \Omega} + \frac{9.4 \text{ V}}{22 \Omega} = 882 \text{ mA} \end{split}$$

(eq. 12)

For high side driver current calculation use the same method. Use Eq. 10 to Eq. 12, but use  $V_{Cboot}$  voltage (usually diminished by  $V_f$  of used bootstrap diode).

## **Total Power Dissipation**

Total power dissipation of NCV51513 is sum of partial dissipations which can be calculated as follows. For more details, please refer to AND90004.

Power loss of device (except drivers) while switching at appropriate frequency is calculated from current consumption at given voltage for specific frequency. The current can be estimated from Figure 35, or it could be calculated using these formulas:

lcc = 21.1

$$\mu \cdot f \cdot V$$

+ 7.01 m  $\cdot$  V + 783  $\mu \cdot f$  + 53.6 m (eq. 13)

lb = 28.6  $\mu \cdot f \cdot V$  + 6.75 m  $\cdot$  V + 633  $\mu \cdot f$  + 17.6 m (eq. 14)

Where:

f is frequency in kHz,

V is voltage in V,

Calculated current will be in mA.

The power dissipation of device (without drivers) is equal to.

$$\begin{aligned} \mathsf{P}_{\mathsf{logic}} &= \mathsf{P}_{\mathsf{HS}} + \mathsf{P}_{\mathsf{LS}} = \left(\mathsf{V}_{\mathsf{boot}} \cdot \mathsf{I}_{\mathsf{B1}_{\mathsf{noload}}}\right) + \left(\mathsf{V}_{\mathsf{CC}} \cdot \mathsf{I}_{\mathsf{CC1}_{\mathsf{noload}}}\right) \\ &= \left(9.4 \cdot 0.171 \, \mathsf{m}\right) + \left(10 \cdot 0.223 \, \mathsf{m}\right) \cong 3.8 \, \mathsf{mW} \end{aligned} \tag{eq. 15}$$

2. Power loss of drivers

$$P_{drivers} = ((Q_g \cdot V_{boot}) + (Q_g \cdot V_{CC})) \cdot f$$

$$= ((49 \text{ n} \cdot 9.4) + (49 \text{ n} \cdot 10)) \cdot 100 \text{ k}$$

$$\cong 95.1 \text{ mW} \qquad (eq. 16)$$

3. Level shifter power loss

$$\begin{aligned} P_{\text{lvlshft}} &= (V_{\text{HV}} + V_{\text{B}}) \cdot f_{\text{SW}} \cdot (Q_{\text{S}} + Q_{\text{R}}) \\ &= (100 + 9.4) \cdot 100 \, \text{k} \cdot (190 \, \text{p} + 190 \, \text{p}) \\ &\cong 4.2 \, \text{mW} \end{aligned}$$

(eq. 17)

Where:

$\begin{array}{lll} V_{HV} & \text{is DC link voltage, here 100 V,} \\ V_{B} & \text{is boot strap voltage, here 9.6 V,} \\ f_{SW} & \text{is duty frequency, here 100 kHz,} \\ Q_{S}, Q_{R} & \text{is energy needed to transfer information from LS part to HS part of the driver.} \\ & \text{The worst case is ZVS mode. In hard switch mode is } Q_{S} \text{ very small, as the set pulse} \end{array}$

4. HS leakage power loss

$$\begin{split} \text{P}_{\text{leak}} &= \text{I}_{\text{HV}_{\text{LEAK}}} \cdot (\text{V}_{\text{HV}} + \text{V}_{\text{B}}) \cdot \text{DC} \\ \\ &= 1.8 \, \mu \cdot \left(100 \, + \, 9.4\right) \cdot 0.5 \, \cong \, 0.1 \, \text{mW} \end{split} \tag{eq. 18}$$

come when HB pin is on low voltage.

Where:

V<sub>HV</sub> is DC link voltage, here 100 V,

V<sub>B</sub> is boot strap voltage, here 9.4 V,

DC is duty cycle, here 50%.

5. Total power losses

$$P_{total} = P_{logic} + P_{drivers} + P_{lvlshft} + P_{leak}$$

$$= 3.8 \text{ m} + 95.1 \text{ m} + 4.2 \text{ m} + 0.1 \text{ m}$$

$$\approx 103 \text{ mW}$$

(eq. 19)

6. Junction temperature rises for calculated power

$$t_J = R_{tJa} \cdot P_{total} = 157 \cdot 0.103 \cong 16 \text{ K}$$

(eq. 20)

The temperature calculated in Eq. 15 is the value which has to be added to ambient temperature. In case the ambient temperature is 30°C, the junction temperature will be 46°C.

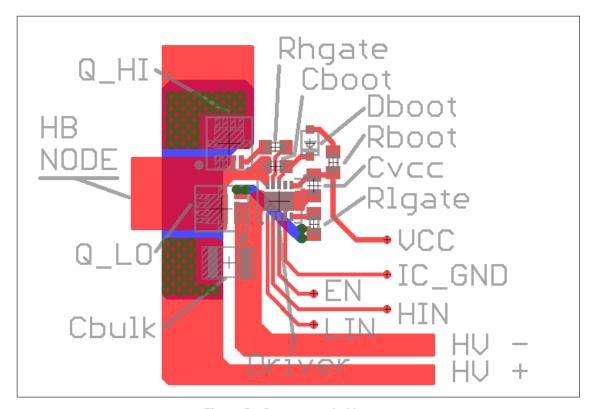

#### **Layout Recommendations**

The NCV51513 are high speed drivers suitable for mid-high power application. To avoid any damage and/or malfunction during switching (and/or during transients, overloads, shorts etc.) it is very important to avoid a high parasitic inductances in high current paths (see "MOSFET turn on and turn off current path" section). It is recommended to fulfill some rules in layout. One of a possible layout for the IC is depictured in Figure 51.

- Keep loop HB\_pin GND\_pin Q\_LO as small as possible. This loop (parasitic inductance) has potential to increase negative spike on HB pin which can cause malfunction or damage of HB driver. The negative voltage presented on HB pin is added to V<sub>CC</sub>-V<sub>f</sub> voltage so V<sub>Cboot</sub> is increased. In extreme case the C<sub>boot</sub> voltage can be so high it will cross maximum rating value which can lead to device damage.

- Keep loop VCC\_pin GND\_pin C<sub>VCC</sub> as small as possible (locate C<sub>VDD</sub> as close to the IC as possible).

The IC features high current capability driver. Any parasitic inductance in this path will result in slow Q\_LO turn on and voltage drop on VCC pin which can result in UVLO activation.

- To avoid switching current (a noise) from the driver to disturb the Vcc line a small resistance in serie with C<sub>VCC</sub> and V<sub>CC</sub> supply line is good to add.

- Keep loop VB\_pin HB\_pin C<sub>boot</sub> as small as possible (locate C<sub>boot</sub> as close to the IC as possible). The IC

- featured high current capability driver. Any parasitic inductance in this path will result in slow Q\_HI turn on and voltage drop on VB pin which can result in UVLO activation.

- To limit bootstap switching current from the C<sub>VCC</sub> it is recommended to add a resistor in serial with bootstrap diode. The resistor also protect HS driver against overvoltage on V<sub>B</sub> – HB pins in case of negative spikes on HB pin.

- Do not let high current flow through trace between GND\_pin and C<sub>VCC</sub>.Even a small parasitic inductance here will create high voltage drop if high current flows through this path. This voltage is added or subtracted from HIN, LIN and EN signal, which results in incorrect thresholds or device damaging.

- Keep loops DRVL\_pin Q\_LO GND\_pin and DRVH\_pin - Q\_HI - HB\_pin as small as possible. A high parasitic inductance in these paths will result in slow MOSFET switching and undesired resonance on gate terminal.

- The high side driver is jumping up and down with high dV/dt at high frequency. The generated noise can influence devices and traces around. Do not place low voltage and sensitive traces into the vicinity of this HV node.

Figure 51. Recommended Layout

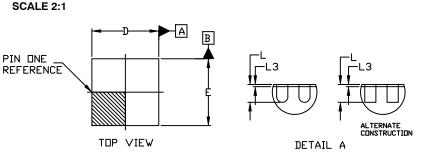

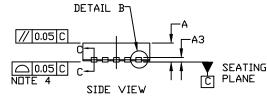

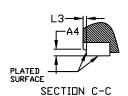

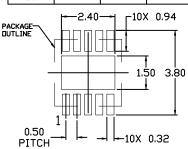

# **DFNW10, 3x3, 0.5P** CASE 507AG ISSUE B

**DATE 14 APR 2020**

# NOTES:

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 2009.

- 2. CONTROLLING DIMENSION: MILLIMETERS

- 3. DIMENSION 6 APPLIES TO PLATED TERMINALS AND IS MEASURED BETWEEN 0.15 AND 0.30MM FROM THE TERMINAL TIP.

- 4. COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

- 5. THIS DEVICE CONTAINS WETTABLE FLANK

DESIGN FEATURES TO AID IN FILLET

FORMATION ON THE LEADS DURING MOUNTING.

|     | MILLIMETERS |          |      |  |  |

|-----|-------------|----------|------|--|--|

| DIM | MIN.        | N□M.     | MAX. |  |  |

| Α   | 0.80        | 0.85     | 0.90 |  |  |

| A1  | 0.00        |          | 0.05 |  |  |

| A3  |             | 0.20 REF | -    |  |  |

| Α4  | 0.10        |          |      |  |  |

| b   | 0.20        | 0.25     | 0.30 |  |  |

| D   | 2.90        | 3.00     | 3.10 |  |  |

| D2  | 2.20        | 2.30     | 2.40 |  |  |

| Ε   | 2.90        | 3.00     | 3.10 |  |  |

| E2  | 1.30        | 1.40     | 1.50 |  |  |

| e   | 0.50 BSC    |          |      |  |  |

| K   | 0.35 REF    |          |      |  |  |

| L   | 0.35        | 0.45     | 0.55 |  |  |

| L3  |             |          | 0.09 |  |  |

# RECOMMENDED MOUNTING FOOTPRINT

For additional information on our Pb-Free strategy and soldering details, please download the IDN Semiconductor Soldering and Mounting Techniques Reference Manual, SDLDERRM/D.

# GENERIC MARKING DIAGRAM\*

XXXXX = Specific Device Code

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

■ Pb-Free Package

(Note: Microdot may be in either location)

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " •", may or may not be present. Some products may not follow the Generic Marking.

| DOCUMENT NUMBER: | 98AON73716G       | Electronic versions are uncontrolled except when accessed directly from the Document Reposit<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| DESCRIPTION:     | DFNW10, 3x3, 0.5P |                                                                                                                                                                                 | PAGE 1 OF 1 |  |  |

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI., and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer p

# PUBLICATION ORDERING INFORMATION

LITERATURE FULFILLMENT: Email Requests to: orderlit@onsemi.com

TECHNICAL SUPPORT North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support: Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative

onsemi Website: www.onsemi.com