# onsemi

## **PWM Buck Regulator, Synchronous, Voltage Mode, High Performance, 65 V, 10 A**

# FAN65008B

#### Description

FAN65008B is a wide VIN highly efficient synchronous buck regulator, with integrated high side and low side power MOSFETs. The device incorporates a fixed frequency voltage mode PWM controller supporting a wide voltage range from 4.5 V to 65 V and can handle continuous currents up to 10 A.

FAN65008B includes a 0.67% accurate reference voltage to achieve tight regulation. The switching frequency can be programmed from 100 kHz to 1 MHz. To improve efficiency at light load condition, the device can be set to discontinuous conduction mode with pulse skipping operation.

FAN65008B has dual LDOs to minimize power loss and integrated current sense circuit that provides cycle-by-cycle current limiting. This single phase buck regulator offers complete protection features including Over current protection, Thermal shutdown, Under-voltage lockout, Over voltage protection, Under voltage protection and Short-circuit protection.

FAN65008B uses ON Semiconductor's high performance PowerTrench<sup>®</sup> MOSFETs that reduces ringing in switching applications. FAN65008B integrates the controller, driver, and power MOSFETs into a thermally enhanced, compact 6 x 6 mm PQFN package. With an integrated approach, the complete DC/DC converter is optimized from the controller and driver to MOSFET switching performance, delivering a high power density solution.

#### Features

- Wide Input Voltage Range: 4.5 V to 65 V

- Continuous Output Current: 10 A

- Fixed Frequency Voltage Mode PWM Control with Input Voltage Feed–forward

- 0.6 V Reference Voltage with 0.67% Accuracy

- Adjustable Switching Frequency: 100 kHz to 1 MHz

- Dual LDOs for Single Supply Operation and to Reduce Power Loss

- Selectable CCM PWM Mode or PFM Mode for Light Loads

- External Compensation for Wide Operation Range

- Adjustable Soft-Start & Pre-Bias Startup

- Enable Function with Adjustable Input Voltage Under-Voltage-Lock-Out (UVLO)

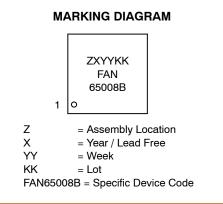

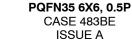

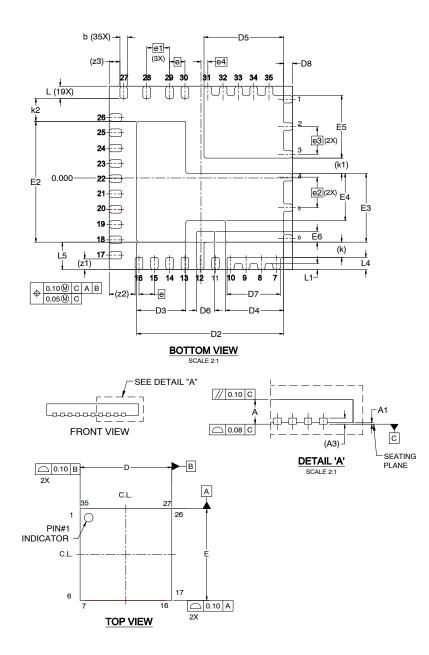

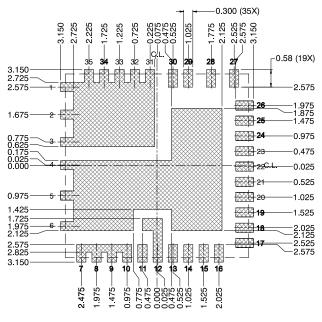

CASE 483BE

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 23 of this data sheet.

- Power Good Indicator

- Over Current Protection, Thermal Shutdown, Over Voltage Protection, Under Voltage Protection and Short-circuit Protection

- High Performance Low Profile 6 mm x 6 mm PQFN Package

- This Device is Pb-Free and RoHS Compliant

#### Applications

- High Voltage POL Module

- Telecommunications: Base Station Power Supplies

- Networking: Computing, Battery Management Systems, USB-PD

- Industrial Equipment: Automation, Power Tools, Slot Machines

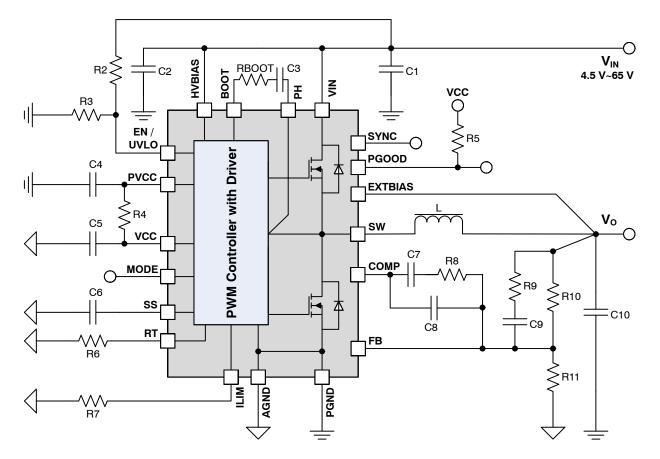

#### **TYPICAL APPLICATION**

Figure 1. Typical Application

| V <sub>IN</sub> (V) | V <sub>o</sub> (V) | L (µH) | L to be<br>used (μH) | C <sub>O</sub> from<br>V <sub>O_RIPPLE</sub><br>(μF) | C <sub>O</sub> from<br>V <sub>OS</sub> (μF) | C <sub>O</sub> from<br>V <sub>US</sub> (μF) | C <sub>O</sub> to be<br>used | R10 (Ω) | R11<br>(Ω) | R9<br>(Ω) | R8<br>(Ω) | C9<br>(F) | C7<br>(F) | C8<br>(F) | f <sub>CO</sub><br>(Hz) | Phase<br>margin<br>(º) | RT<br>(=R6) (Ω) |

|---------------------|--------------------|--------|----------------------|------------------------------------------------------|---------------------------------------------|---------------------------------------------|------------------------------|---------|------------|-----------|-----------|-----------|-----------|-----------|-------------------------|------------------------|-----------------|

| 35                  | 24                 | 16.762 |                      | 2.6                                                  | 30.9                                        | 65.2                                        |                              |         | 718.2      |           |           |           |           |           | 18.0k                   | 69.4                   |                 |

| 35                  | 28                 | 12.444 | 1                    | 2.2                                                  | 22.7                                        | 83.5                                        |                              |         | 613.4      | 1         |           |           |           |           | 22.6k                   | 67.5                   | 1               |

| 35                  | 30                 | 9.524  | 1                    | 2.1                                                  | 19.8                                        | 103.6                                       |                              |         | 571.6      | 1         |           |           |           |           | 22.6k                   | 67.5                   | 1               |

| 48                  | 24                 | 26.667 | 1                    | 2.6                                                  | 30.9                                        | 30.9                                        |                              |         | 718.2      | 1         |           |           |           |           |                         |                        | 1               |

| 48                  | 28                 | 25.926 | 22.00                | 2.2                                                  | 22.7                                        | 31.4                                        | 75.2                         | 28010   | 613.4      | 365       | 1.0k      | 2.7n      | 220n      | 470p      |                         |                        | 3.75E+04        |

| 48                  | 30                 | 25.000 |                      | 2.1                                                  | 19.8                                        | 32.3                                        |                              |         | 571.6      |           |           |           |           |           |                         |                        |                 |

| 60                  | 24                 | 32.000 | 1                    | 2.6                                                  | 30.9                                        | 20.8                                        |                              |         | 718.2      | 1         |           |           |           |           |                         |                        |                 |

| 60                  | 28                 | 33.185 | 1                    | 2.2                                                  | 22.7                                        | 19.9                                        |                              |         | 613.4      | 1         |           |           |           |           |                         |                        |                 |

| 60                  | 30                 | 33.333 | 1                    | 2.1                                                  | 19.8                                        | 19.8                                        |                              |         | 571.6      | 1         |           |           |           |           |                         |                        |                 |

#### Table 1. APPLICATION DESIGN EXAMPLE

NOTE: \*lout = 5 A, Fsw = 300 KHz

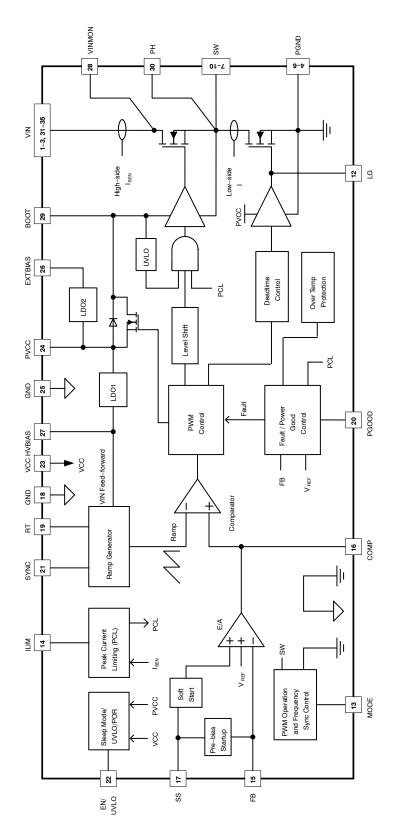

#### **BLOCK DIAGRAM**

Figure 2. Block Diagram

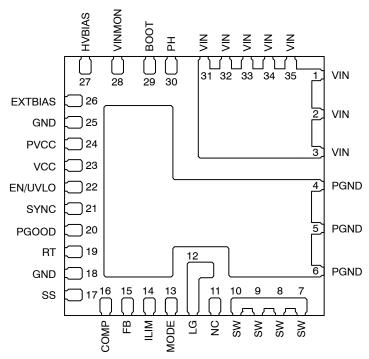

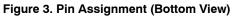

#### **PIN CONFIGURATION**

#### Table 2. PIN DESCRIPTION

| Name    | Pin/Pad                | Description                                                                                                                                                                                                                                                                                                    |

|---------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VIN     | 1–3, 31–35,<br>VIN Pad | Input voltage to power stage                                                                                                                                                                                                                                                                                   |

| PGND    | 4-6, PGND Pad          | Power ground for power stage and PVCC                                                                                                                                                                                                                                                                          |

| SW      | 7–10                   | Switching node, junction of high- and low-side MOSFETs                                                                                                                                                                                                                                                         |

| NC      | 11                     | No Connection                                                                                                                                                                                                                                                                                                  |

| LG      | 12                     | Gate of low side MOSFET                                                                                                                                                                                                                                                                                        |

| MODE    | 13                     | Configures pulse modulation/frequency synchronization modes. See MODE description for details                                                                                                                                                                                                                  |

| ILIM    | 14                     | Connect a resistor to GND to set the high-side MOSFET peak current limit                                                                                                                                                                                                                                       |

| FB      | 15                     | Feedback Voltage Input                                                                                                                                                                                                                                                                                         |

| COMP    | 16                     | Output of internal error amplifier for external compensation                                                                                                                                                                                                                                                   |

| SS      | 17                     | Set up soft-start time. Connect a capacitor between SS and PGND to set the soft start time                                                                                                                                                                                                                     |

| GND     | 18, 25                 | Analog ground for VCC, RT, SYNC, MODE, etc.                                                                                                                                                                                                                                                                    |

| RT      | 19                     | Connect a resistor to GND to set switching frequency                                                                                                                                                                                                                                                           |

| PGOOD   | 20                     | Power good indicator, open-drain output. Level HIGH indicates VOUT is within set limits                                                                                                                                                                                                                        |

| SYNC    | 21                     | The pin is used to synchronize frequency in when in Non-Master mode or out when in master mode                                                                                                                                                                                                                 |

| EN/UVLO | 22                     | Enable/VIN Under-Voltage-Lockout set pin. When used as enable function in-dependent of input voltage, connect this pin to a voltage > 1.22 V to enable or PGND to disable. When used as enable function at specific input voltage level, connect a resistor divider between input voltage and PGND to this pin |

| VCC     | 23                     | Bias power for internal analog circuits                                                                                                                                                                                                                                                                        |

| PVCC    | 24                     | LDO output and the bias supply for gate driver circuit                                                                                                                                                                                                                                                         |

| EXTBIAS | 26                     | Input voltage to the secondary LDO. Typically connect to $V_O$ when $V_O \geq 5 \ V$                                                                                                                                                                                                                           |

| HVBIAS  | 27                     | Input voltage to the primary LDO. Also used for the feed-forward function. Connect it to power stage input with a small RC filter                                                                                                                                                                              |

| VINMON  | 28                     | Current sense positive pin. Do NOT connect anything                                                                                                                                                                                                                                                            |

| BOOT    | 29                     | Bootstrap supply for high-side driver. Connect a low impedance capacitor between this pin and PH pin                                                                                                                                                                                                           |

| PH      | 30                     | High-side source connection (SW node) for the bootstrap capacitor                                                                                                                                                                                                                                              |

| Symbol                       | Parameter                                           | Min. | Max.                    | Unit |

|------------------------------|-----------------------------------------------------|------|-------------------------|------|

| V <sub>IN</sub>              | VIN Pin Voltage (System Supply) with regard to PGND | -0.3 | 70                      | V    |

| V <sub>HVBIAS</sub>          | HVBIAS Pin Voltage with regard to PGND              | -0.3 | 70                      |      |

| V <sub>EXTBIAS</sub>         | EXTBIAS Pin Voltage with regard to PGND             | -0.3 | 70                      |      |

| V <sub>EN/UVLO</sub>         | EN/UVLO Pin Voltage with regard to PGND             | -0.3 | 8.4                     |      |

| V <sub>PH</sub>              | PH Pin Voltage with regard to PGND                  | -0.3 | 70                      |      |

| V <sub>SW</sub>              | SW Pin Voltage with regard to PGND                  | -0.3 | 70                      |      |

|                              | SW Pin Voltage with regard to PGND (Pulse, 100 ns)  | -5.0 | 75                      |      |

|                              | SW Pin Voltage with regard to PGND (Pulse, 30 ns)   | -7.5 | 75                      |      |

| V <sub>BOOT</sub>            | BOOT Pin Voltage with regard to PGND                | -0.3 | 75                      |      |

|                              | BOOT Pin Voltage with regard to PH Pin              | -0.3 | 6.5                     |      |

| V <sub>ILIM</sub>            | ILIM Pin Voltage with regard to GND                 | -0.3 | 6.5                     |      |

| V <sub>PVCC</sub>            | PVCC Pin Voltage with regard to PGND                | -0.3 | 6.5                     |      |

| $V_{FB}$                     | FB Pin Voltage with regard to GND                   | -0.3 | V <sub>CC</sub> + 0.3   |      |

| V <sub>COMP</sub>            | COMP Pin Voltage with regard to GND                 | -0.3 | V <sub>CC</sub> + 0.3   |      |

| V <sub>PGOOD</sub>           | PGOOD Pin Voltage with regard to GND                | -0.3 | V <sub>CC</sub> + 0.3   |      |

| $V_{LG}$                     | LG Pin Voltage with regard to PGND                  | -0.3 | V <sub>PVCC</sub> + 0.3 |      |

| V <sub>MODE</sub>            | MODE Pin Voltage with regard to GND                 | -0.3 | V <sub>CC</sub> + 0.3   |      |

| V <sub>RT</sub>              | RT Pin Voltage with regard to GND                   | -0.3 | V <sub>CC</sub> + 0.3   |      |

| $V_{SS}$                     | SS Pin Voltage with regard to PGND                  | -0.3 | V <sub>CC</sub> + 0.3   |      |

| V <sub>SYNC</sub>            | SYNC Pin Voltage with regard to GND                 | -0.3 | V <sub>CC</sub> + 0.3   |      |

| V <sub>GND</sub>             | GND Pin Voltage with regard to PGND                 | -0.3 | 0.3                     |      |

| ESD                          | Human Body Model, ANSI/ESDA/JEDEC JS-001-2012       | -    | 1000                    |      |

|                              | Charged Device Model, JESD22-C101                   | -    | 500                     |      |

| R <sub>θJA</sub><br>(Note 1) | Junction-to-Ambient Thermal Resistance              | -    | 16                      | °C/W |

| R <sub>θJC</sub><br>(Note 1) | Junction-to-Case (Top) Thermal Resistance           | -    | 7.3                     | °C/W |

| R <sub>θJB</sub><br>(Note 1) | Junction-to-Board Thermal Resistance                | -    | 3.4                     | °C/W |

| TJ                           | Junction Operating Temperature                      | -55  | 150                     | °C   |

| T <sub>STG</sub>             | Device Storage Temperature                          | -55  | 150                     |      |

#### **Table 3. ABSOLUTE MAXIMUM RATINGS**

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected. 1. Measured on 6-layer applications board with 0 LFM at  $T_A = 25^{\circ}C$ .

| Symbol               | Parameter                                                    | Min. | Тур. | Max.            | Unit |

|----------------------|--------------------------------------------------------------|------|------|-----------------|------|

| V <sub>IN</sub>      | VIN Pin Voltage (System Supply) with regard to PGND          | 4.5  | -    | 65              | V    |

| V <sub>HVBIAS</sub>  | V <sub>HVBIAS</sub> HVBIAS Pin Voltage with regard to PGND   |      | -    | 65              |      |

| V <sub>SW</sub>      | V <sub>SW</sub> SW Pin Voltage with regard to PGND (DC)      |      | -    | V <sub>IN</sub> |      |

| V <sub>EXTBIAS</sub> | V <sub>EXTBIAS</sub> EXTBIAS Pin Voltage with regard to PGND |      | -    | 65              |      |

| V <sub>EN/UVLO</sub> | EN/UVLO Pin Voltage with regard to PGND                      | -    | -    | 7.5             |      |

| V <sub>PG_SPLY</sub> | PGOOD Pin Voltage with regard to GND                         | -    | -    | 5.4             |      |

| T <sub>A</sub>       | Operating Ambient Temperature                                |      | -    | 125             | °C   |

| Τ <sub>J</sub>       | Junction Operating Temperature                               | -40  | -    | 125             | °C   |

#### Table 4. RECOMMENDED OPERATING CONDITIONS

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

Table 5. ELECTRICAL CHARACTERISTICS(Typical application circuit shown in Figure 1 is used. Unless otherwise noted,  $V_{IN} = V_{HVBIAS} = 48$  V,  $V_{OUT} = 5$  V,  $V_{PVCC} = V_{CC} = 5$  V, $-40^{\circ}C < T_J = T_A < +125^{\circ}C$ .  $T_A = T_J = +25^{\circ}C$  for typical values)

| Symbol Parameter          |                                                | Conditions                                                                        | Min. | Тур  | Max. | Unit |  |  |  |  |

|---------------------------|------------------------------------------------|-----------------------------------------------------------------------------------|------|------|------|------|--|--|--|--|

| SUPPLY                    | SUPPLY                                         |                                                                                   |      |      |      |      |  |  |  |  |

| I <sub>HVBIAS_Q_PWM</sub> | Forced CCM Quiescent Cur-<br>rent              | $V_{EN}$ = 2.0 V, MODE = 5 V through a 100 k $\Omega$ resistor, $V_{FB}$ = 0.64 V | -    | 1.2  | -    | mA   |  |  |  |  |

| I <sub>HVBIAS_Q_PSM</sub> | DCM with Pulse Skipping Qui-<br>escent Current | $V_{EN}$ = 2.0 V, MODE = 0 V through a 100 k $\Omega$ resistor, $V_{FB}$ = 0.64 V | -    | 1.4  | -    |      |  |  |  |  |

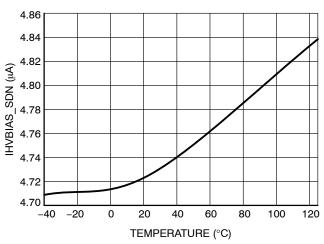

| I <sub>HVBIAS</sub> SDN   | Shutdown Current                               | V <sub>EN</sub> = 0 V                                                             | -    | 5    | 9    | μA   |  |  |  |  |

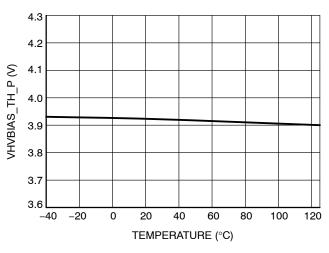

| V <sub>HVBIAS_TH</sub>    | HVBIAS UVLO Threshold                          | HVBIAS Rising                                                                     | -    | 3.92 | -    | V    |  |  |  |  |

| V <sub>HVBIAS_HYS</sub>   | HVBIAS UVLO Hysteresis                         | HVBIAS Falling                                                                    | -    | 1.0  | -    |      |  |  |  |  |

#### LDOs

| V <sub>PVCC</sub>       | LDO Output Voltage                                                        | I <sub>PVCC</sub> = 1 mA and EXTBIAS pin is<br>open          | 4.75 | 5.00 | 5.25 | V  |

|-------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------|------|------|------|----|

|                         |                                                                           | V <sub>EXTBIAS</sub> = 12 V, I <sub>PVCC</sub> = 1 mA        | 4.75 | 5.00 | 5.25 |    |

| V <sub>HVBIAS_D</sub>   | LDO1 Dropout Voltage                                                      | V <sub>HVBIAS</sub> = 5.0 V, LDO Output<br>Current = 150 mA  | -    | 1.0  | 2.0  |    |

| V <sub>EXTBIAS_D</sub>  | LDO2 Dropout Voltage                                                      | V <sub>EXTBIAS</sub> = 5.0 V, LDO Output<br>Current = 150 mA | -    | 0.33 | 0.66 |    |

| V <sub>LDOSWO</sub>     | Switchover Voltage above<br>which LDO1 is Disabled and<br>LDO2 is Enabled | V <sub>EXTBIAS</sub> is rising                               | -    | 4.7  | -    |    |

| V <sub>LDOSWO_HYS</sub> | Switchover Voltage Hysteresis                                             | V <sub>EXTBIAS</sub> is falling                              | -    | 100  | -    | mV |

| V <sub>SWTOLDO</sub>    | Threshold Voltage above which the LDO is in LDO mode                      | $V_{HVBIAS}$ or $V_{EXTBIAS}$ is rising                      | -    | 5.5  | -    | V  |

| V <sub>LDOTOSW</sub>    | Threshold Voltage below which the LDO is in switch mode                   | $V_{HVBIAS}$ or $V_{EXTBIAS}$ is falling                     | -    | 5.4  | -    |    |

#### VCC SUPPLY

| V <sub>CC_ON</sub>       | V <sub>CC</sub> Start Voltage   | V <sub>CC</sub> Rising  | 3.8 | 4.0 | 4.4 | V |

|--------------------------|---------------------------------|-------------------------|-----|-----|-----|---|

| V <sub>CC_UVLO</sub>     | V <sub>CC</sub> UVLO Threshold  | V <sub>CC</sub> Falling | 3.6 | 3.8 | 4.1 |   |

| V <sub>CC_UVLO_HYS</sub> | V <sub>CC</sub> UVLO Hysteresis |                         | -   | 0.2 | -   |   |

**Table 5. ELECTRICAL CHARACTERISTICS** (continued)(Typical application circuit shown in Figure 1 is used. Unless otherwise noted,  $V_{IN} = V_{HVBIAS} = 48$  V,  $V_{OUT} = 5$  V,  $V_{PVCC} = V_{CC} = 5$  V, $-40^{\circ}C < T_J = T_A < +125^{\circ}C$ .  $T_A = T_J = +25^{\circ}C$  for typical values)

| Symbol                   | Parameter                                                                  | Conditions                                                | Min.  | Тур        | Max.  | Unit   |

|--------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------|-------|------------|-------|--------|

| REFERENCE VC             | DLTAGE                                                                     |                                                           |       |            |       |        |

| V <sub>REF</sub>         | Reference Voltage                                                          | $T_J$ = 25°C, $V_{IN}$ = 4.5 V to 65 V                    | 0.596 | 0.600      | 0.604 | V      |

|                          |                                                                            | $T_{J} = -40^{\circ}C$ to 125°C (Note 2)                  | 0.594 | -          | 0.606 |        |

| ENABLE AND U             | NDER VOLTAGE LOCK OUT                                                      |                                                           |       |            |       |        |

| V <sub>EN_TH</sub>       | EN/UVLO Threshold                                                          | EN/UVLO Rising                                            | 1.141 | 1.22       | 1.296 | V      |

| V <sub>EN_HYS</sub>      | EN/UVLO Hysteresis                                                         | EN/UVLO Falling                                           | -     | 115        | -     | mV     |

| $R_{EN_{PD}}$            | EN/UVLO Internal Pull down<br>Resistance                                   |                                                           | -     | 500        | -     | kΩ     |

| V <sub>EN_CLP</sub>      | EN/UVLO Clamp Voltage                                                      | TBD                                                       | -     | 2.5        | -     | V      |

| R <sub>EN_CLP</sub>      | EN/UVLO Clamp Resistance                                                   |                                                           | -     | 200        | -     | kΩ     |

| I <sub>EN_CLP</sub>      | EN/UVLO Clamp Current                                                      | V <sub>EN</sub> = 2.5 V                                   | -     | 22         | -     | μA     |

| MODE                     | ·                                                                          | ·                                                         |       |            |       |        |

| R <sub>MASTER</sub>      | Resistor Connected to Mode<br>Pin for Master<br>Synchronization Mode       |                                                           | 70    | 100        | 130   | kΩ     |

| R <sub>NON_MASTER</sub>  | Resistor Connected to Mode<br>Pin for Non-Master Synchro-<br>nization Mode |                                                           | 1     | -          | 5     | kΩ     |

| OSCILLATOR               | ·                                                                          | ·                                                         |       |            |       |        |

| f <sub>SW</sub>          | Frequency Range                                                            |                                                           | 100   | -          | 1000  | kHz    |

| f <sub>SW1</sub>         | Switching Frequency Set by                                                 | R <sub>T</sub> = 199 kΩ                                   | 85    | 100        | 125   |        |

| f <sub>SW2</sub>         | RT I                                                                       | R <sub>T</sub> = 8.0 kΩ                                   | 900   | 1000       | 1200  | -      |

| f <sub>SW3</sub>         |                                                                            | RT Pin is Short-Circuited to VCC Pin                      | 215   | 250        | 280   |        |

| f <sub>SW4</sub>         |                                                                            | RT Pin is Short-Circuited to GND Pin                      | 425   | 25 500 575 |       |        |

| FREQUENCY SY             | (NCHRONIZATION                                                             |                                                           |       |            |       |        |

| V <sub>SYNC_IN_H</sub>   | SYNC Input Logic HIGH                                                      |                                                           | 2     | -          | -     | V      |

| V <sub>SYNC_IN_L</sub>   | SYNC Input Logic LOW                                                       |                                                           | -     | -          | 0.8   |        |

| t <sub>HIGH_IN_MIN</sub> | Input HIGH Level Pulse Width                                               |                                                           | 150   | -          | -     | ns     |

| t <sub>LOW_IN_MIN</sub>  | Input LOW Level Pulse Width                                                |                                                           | 150   | -          | -     |        |

| <b>f</b> SYNC            | Synchronizable Frequency                                                   | Percentage of frequency set by RT                         | 70    | -          | 130   | %      |

| <sup>t</sup> RT_SYNC_DL  | Transition Delay from RT Set<br>Frequency to Sync Frequency                | In Number of External Clock Cycles<br>in 2 ms time period | -     | 64         | -     | Cycles |

| R <sub>SYNC_PD</sub>     | SYNC Pin Pull down Resis-<br>tance                                         |                                                           | -     | 100        | -     | kΩ     |

| R <sub>SYNC_DR_PU</sub>  | SYNC output Driver Pull-up<br>Resistance                                   |                                                           | -     | 10         | _     | Ω      |

| R <sub>SYNC_DR_PD</sub>  | SYNC output Driver Pull-down<br>Resistance                                 |                                                           | -     | 13         | -     | 1      |

| D <sub>SYNC_OUT</sub>    | SYNC Output Frequency Duty<br>Cycle                                        |                                                           | -     | 50         | -     | %      |

| C <sub>L_SYNC</sub>      | SYNC Pin Lead Capacitance                                                  |                                                           | -     | _          | 200   | pF     |

**Table 5. ELECTRICAL CHARACTERISTICS** (continued)(Typical application circuit shown in Figure 1 is used. Unless otherwise noted,  $V_{IN} = V_{HVBIAS} = 48$  V,  $V_{OUT} = 5$  V,  $V_{PVCC} = V_{CC} = 5$  V, $-40^{\circ}C < T_J = T_A < +125^{\circ}C$ .  $T_A = T_J = +25^{\circ}C$  for typical values)

| Symbol                   | Parameter                                                                                                           | Conditions                                                                                        | Min. | Тур  | Max. | Unit              |

|--------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------|------|------|-------------------|

| RAMP AND PWI             | MMODULATOR                                                                                                          | ·                                                                                                 |      |      | •    |                   |

| k <sub>PWM</sub>         | PWM Modulator Gain,<br>V <sub>IN</sub> /ΔV <sub>RAMP</sub>                                                          | $V_{IN} = V_{HVBIAS} = 4.5$ to 65 V                                                               | _    | 25   | -    | V/V               |

| T <sub>ON_MIN</sub>      | PWM Minimum ON time                                                                                                 |                                                                                                   | _    | 150  | 200  | ns                |

| T <sub>OFF_MIN</sub>     | PWM Minimum OFF time                                                                                                |                                                                                                   | -    | 150  | 200  | -                 |

| ERROR AMPLIF             | IER                                                                                                                 |                                                                                                   |      | 1    |      | 1                 |

| GBW                      | Unit Gain Bandwidth                                                                                                 |                                                                                                   | -    | 10   | -    | MHz               |

| G                        | DC Gain                                                                                                             |                                                                                                   | -    | 80   | -    | dB                |

| I <sub>FB</sub>          | FB Bias Current                                                                                                     | V <sub>FB</sub> = 0.6 V                                                                           | -50  | 5    | 50   | nA                |

| ICOMP_SOURCE             | COMP Source Current                                                                                                 |                                                                                                   | 2    | 7    | -    | mA                |

| I <sub>COMP_SINK</sub>   | COMP Sink Current                                                                                                   |                                                                                                   | 2    | 8.5  | -    | mA                |

| SOFT START               | 1                                                                                                                   | 1                                                                                                 |      | 1    | 1    | 1                 |

| tss_dL                   | Enable High to Soft Start<br>Ramp Start Delay                                                                       |                                                                                                   | -    | 1    | 3    | ms                |

| I <sub>SS</sub>          | Charging Current to SS<br>Capacitor                                                                                 |                                                                                                   | 4.3  | 5    | 5.9  | μΑ                |

| воот                     |                                                                                                                     |                                                                                                   |      | Į    | !    |                   |

| VBT SWITCH               | Bootstrap Switch Voltage Drop                                                                                       | BOOT Current, I <sub>BOOT</sub> = 50 mA                                                           | _    | 0.1  | -    | V                 |

| V <sub>BT_UVLO_TH</sub>  | BOOT UVLO Voltage with re-<br>gard to PH                                                                            | BOOT Falling                                                                                      | -    | 3.20 | -    | -                 |

| V <sub>BT_UVLO_HYS</sub> | BOOT UVLO Hysteresis with<br>regard to PH                                                                           | BOOT Rising                                                                                       | -    | 0.35 | -    |                   |

| CURRENT PRO              | TECTION                                                                                                             |                                                                                                   |      | ļ    | Į    | ļļ                |

| I <sub>LIM_S</sub>       | Current Source Creating<br>Current Limit Reference<br>Voltage on R_ILIM                                             |                                                                                                   | _    | 8.5  | _    | μΑ                |

| k <sub>ILIM_HS</sub>     | High-side MOSFET current<br>limit scale factor<br>(I <sub>LIM_HS</sub> = k <sub>ILIM_HS</sub> × R <sub>ILIM</sub> ) |                                                                                                   | -    | 83.9 | -    | μΑ/Ω              |

| k <sub>ILIM_LS</sub>     | Low-side MOSFET current<br>limit scale factor<br>(I <sub>LIM_LS</sub> = k <sub>ILIM_LS</sub> × R <sub>ILIM</sub> )  |                                                                                                   | _    | 24.6 | _    |                   |

| n <sub>CYCLE_OCP</sub>   | Number of Switching Cycle(s)                                                                                        | $I_{\text{LIM}_{\text{HS}}} \leq I_{\text{SEN}_{\text{PEAK}}} < 130\% I_{\text{LIM}_{\text{HS}}}$ | -    | 1024 | -    | Cycle             |

| n <sub>CYCLE_SCP</sub>   | before Entering Hiccup Mode                                                                                         | I <sub>SEN PEAK</sub> ≥130%I <sub>LIM HS</sub>                                                    | _    | 1    | -    |                   |

| POWER GOOD               |                                                                                                                     |                                                                                                   |      |      |      |                   |

| V <sub>FB_NPG_TH</sub>   | FB Pin Voltage for PGOOD to<br>Be De-asserted When Down<br>from Regulation                                          | FB Falling                                                                                        | 88   | 92   | 96   | %V <sub>REF</sub> |

|                          | FB Pin Voltage for PGOOD to<br>Be De-asserted When up into<br>OVP1                                                  | FB Rising                                                                                         | 110  | 115  | 120  |                   |

| V <sub>FB_PG_TH</sub>    | FB Pin Voltage for PGOOD to<br>Be Asserted When Down from<br>OVP1                                                   | FB Falling                                                                                        | _    | 110  | _    |                   |

|                          | FB Pin Voltage for PGOOD to<br>Be Asserted When up<br>into Regulation                                               | FB Rising                                                                                         | _    | 94   | _    |                   |

Thermal Shutdown Hysteresis

**Table 5. ELECTRICAL CHARACTERISTICS** (continued)(Typical application circuit shown in Figure 1 is used. Unless otherwise noted,  $V_{IN} = V_{HVBIAS} = 48$  V,  $V_{OUT} = 5$  V,  $V_{PVCC} = V_{CC} = 5$  V, $-40^{\circ}C < T_J = T_A < +125^{\circ}C$ .  $T_A = T_J = +25^{\circ}C$  for typical values)

| Symbol                 | Parameter                                            | Conditions                                                                       | Min. | Тур | Max. | Unit              |

|------------------------|------------------------------------------------------|----------------------------------------------------------------------------------|------|-----|------|-------------------|

| POWER GOOD             |                                                      | ·                                                                                |      | •   |      |                   |

| t <sub>PG_DL</sub>     | PGOOD Delay                                          | Time from when FB Reaches<br>V <sub>FB_PG_TH</sub> to when PGOOD<br>becomes HIGH | -    | 500 | -    | μs                |

| tpg_flt                | PGOOD De-glitch Filter<br>Duration                   |                                                                                  | -    | 5   | _    | μs                |

| V <sub>PG_L</sub>      | PGOOD Output LOW<br>Voltage                          | $V_{FB} = 70\% V_{REF}$ , $I_{PGOOD} = -1$ mA                                    | -    | 6   | 10   | mV                |

| VOLTAGE PROT           | TECTION                                              | ·                                                                                |      | •   |      |                   |

| V <sub>FB_OVP1</sub>   | FB Pin Voltage for Level 1<br>Over Voltage Detection | FB Voltage Rising                                                                | 110  | 115 | 120  | %V <sub>REF</sub> |

| $V_{FB_OVP2}$          | FB Pin Voltage for Level 2<br>Over Voltage Detection |                                                                                  | 124  | 130 | 136  |                   |

| V <sub>FB_UVP_TH</sub> | FB Pin Voltage for Under<br>Voltage Detection        | FB Voltage Falling                                                               | -    | 35  | _    |                   |

| HICCUP                 |                                                      | •                                                                                |      |     |      |                   |

| t <sub>HICCUP</sub>    | Hiccup Time                                          |                                                                                  | -    | 1   | -    | S                 |

| THERMAL SHU            | TDOWN                                                |                                                                                  |      |     |      |                   |

| $T_{J\_SD}$            | Thermal Shutdown Threshold                           | Temperature Rising                                                               | -    | 150 | -    | °C                |

$T_{J\_SD\_HYS}$ Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions. 2. Guaranteed by design

20

\_

Temperature Falling

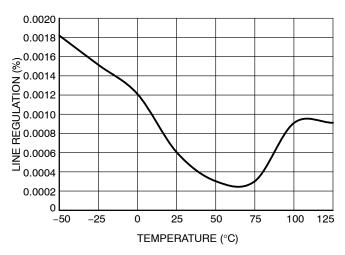

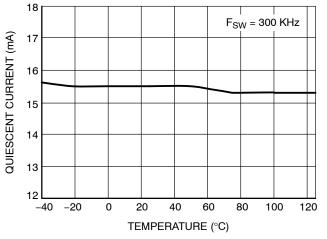

#### **TYPICAL PERFORMANCE CHARACTERISTICS**

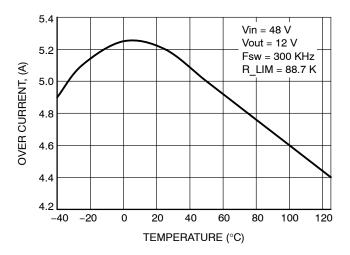

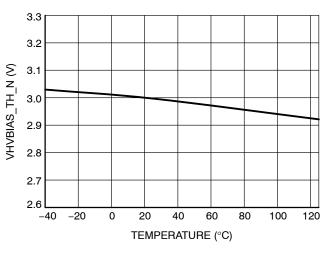

(Test at T<sub>A</sub> = 25°C, V<sub>HVBIAS</sub> = V<sub>IN</sub> = 48 V and V<sub>O</sub> = 28 V unless otherwise specified)

Figure 8. HVBIAS Rising Threshold vs. T

Figure 5. VIN Quiescent Current vs. Temperature

Figure 7. Shutdown Current vs. T at  $V_{HVBIA}S = 48 V$

$V_{HVBIAS} = 48$  V and RT = 8.06 k $\Omega$

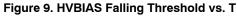

#### **TYPICAL PERFORMANCE CHARACTERISTICS (CONTINUED)**

(Test at T<sub>A</sub> = 25°C, V<sub>HVBIAS</sub> = V<sub>IN</sub> = 48 V and V<sub>O</sub> = 28 V unless otherwise specified)

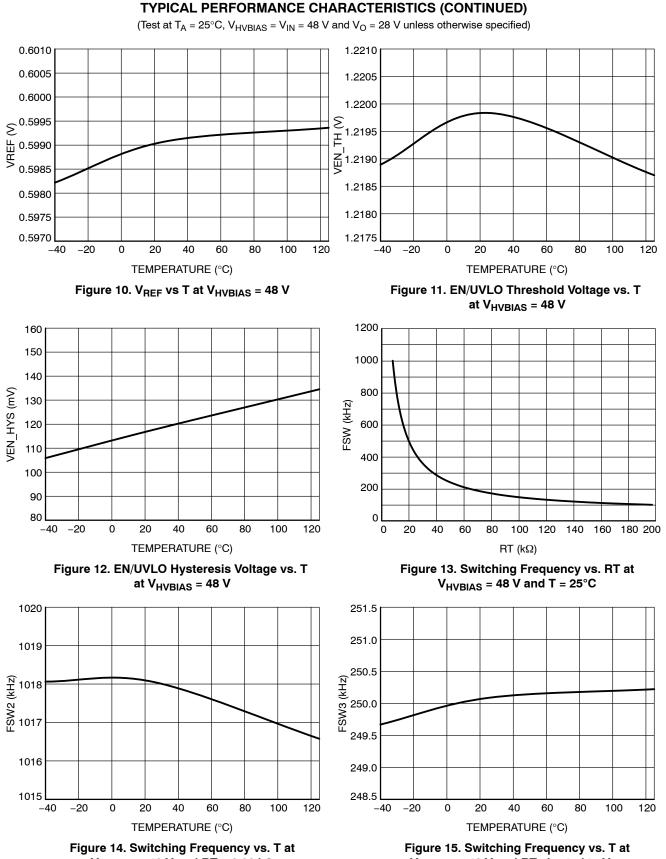

#### **TYPICAL PERFORMANCE CHARACTERISTICS (CONTINUED)**

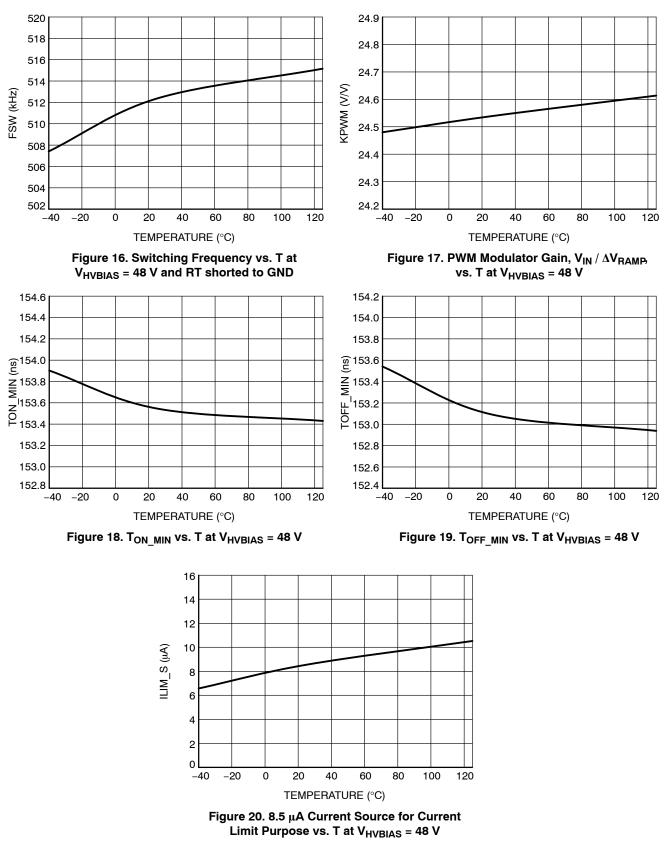

(Test at  $T_A$  = 25°C,  $V_{HVBIAS}$  =  $V_{IN}$  = 48 V and  $V_O$  = 24 V unless otherwise specified)

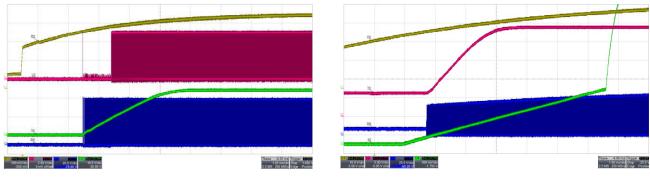

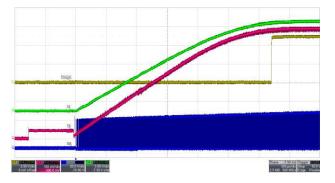

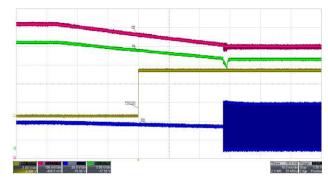

Figure 21. System Startup with No Load

Figure 22. System Startup with No Load

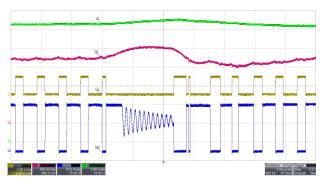

Figure 23. System Startup with 25% Pre-bias

#### **TYPICAL PERFORMANCE CHARACTERISTICS (CONTINUED)**

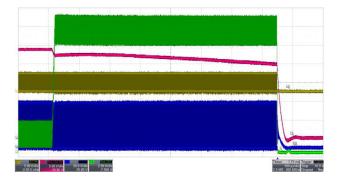

(Test at T<sub>A</sub> = 25°C, V<sub>HVBIAS</sub> = V<sub>IN</sub> = 48 V and V<sub>O</sub> = 24 V unless otherwise specified)

Figure 24. System Startup with 75% Pre-bias

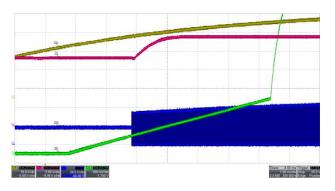

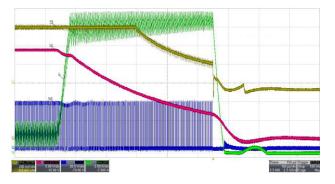

Figure 25. Transition from Native Frequency to Sync Frequency in Non-Master Mode

Figure 26. SYNC Output Frequency Duty Cycle in Master Mode

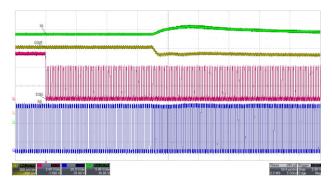

Figure 28. Power Good at Startup with No Load

Figure 27. Over-current Protection with 280 kHz Switching Frequency

Figure 29. Power Good at Startup with No Load

#### **TYPICAL PERFORMANCE CHARACTERISTICS (CONTINUED)**

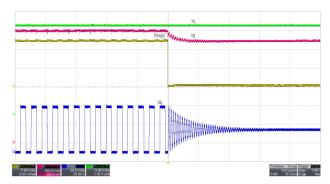

(Test at  $T_A$  = 25°C,  $V_{HVBIAS}$  =  $V_{IN}$  = 48 V and  $V_O$  = 24 V unless otherwise specified)

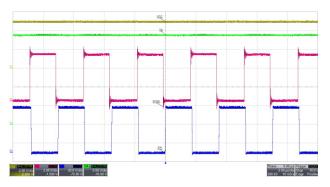

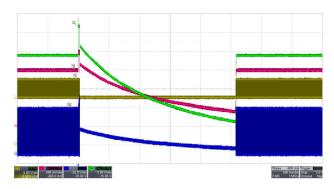

Figure 30. OVP1 at  $V_{FB} \ge 115\% V_{REF}$

Figure 31. OVP1 Release at  $V_{FB} \le 110\% V_{REF}$

Figure 32. OVP2 at V<sub>FB</sub>  $\ge$  130% V<sub>REF</sub>

Figure 34. UVP due to Deep Over-current

Figure 33. OVP2 Release at V<sub>FB</sub>  $\leq$  100% V<sub>REF</sub>

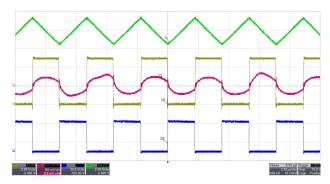

Figure 35. Switching and Voltage Ripple

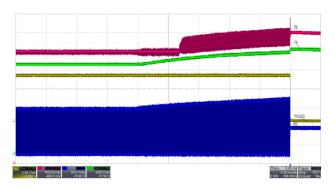

#### **TYPICAL PERFORMANCE CHARACTERISTICS (CONTINUED)**

(Test at  $T_A = 25^{\circ}C$ ,  $V_{HVBIAS} = V_{IN} = 48$  V and  $V_O = 24$  V unless otherwise specified)

6

5

4

3

2

0

System Power Loss (W)

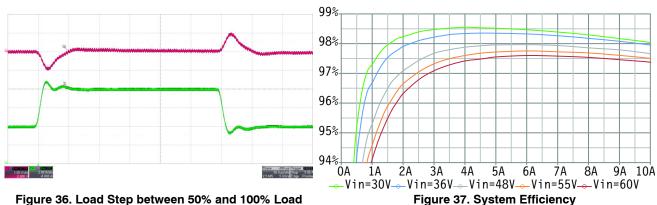

Figure 36. Load Step between 50% and 100% Load

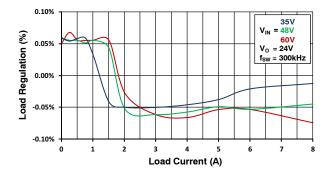

Figure 38. Load Regulation

NOTE: EXTBIAS is connected to Vo for Figures 21-39

#### **Functional Description**

FAN65008B is a high-efficiency synchronous buck converter with integrated controller, driver and two power MOSFETs. It can operate over a 4.5 V to 65 V input voltage range, and delivers 10 A load current. The internal reference voltage is  $0.6 \text{ V} \pm 1\%$  over  $-40^{\circ}\text{C}$  to  $125^{\circ}\text{C}$  temperature range.

FAN65008B uses voltage mode PWM control scheme with input voltage feed-forward feature for the wide input voltage range. The high bandwidth error amplifier monitors the output voltage and generates the control signal for the pulse width modulation block. By adjusting the external compensation network, the system performance can be optimized based on the application parameters.

The switching frequency is set by an external resistor and can be synchronized to an external clock signal. To improve light load efficiency (low IQ mode), either low-side MOSFET is turned off when the inductor current drops to zero or pulse skipping is implemented when load current further decreases. The high-side MOSFET current sense circuit is adopted for the peak current limiting function and

0 2 3 4 5 6 7 Load Current (A)

35V

٧IN = 48V

٧o = 24V f<sub>SW</sub> = 300kHz

Figure 39. System Power Loss

the output voltage will be reduced in current limiting condition. Other protection functions include over temperature shut-down and over-voltage protection.

At the beginning of each switching cycle, the clock signal initiates a PWM signal to turn on high-side MOSFET, and at the same time, the ramp signal starts to rise up. A reset pulse is generated by the comparator when the ramp signal intercepts the COMP signal. This reset pulse turns off high-side MOSFET and turns on low-side MOSFET until next clock cycle comes. In the case that current limit is hit, a peak current limiting (PCL) signal is generated to turn off the high-side MOSFET until the next PWM signal. This is cycle by cycle current limit protection. When certain faulty condition is met, the device enters hiccup mode to further protect itself.

#### LDOs

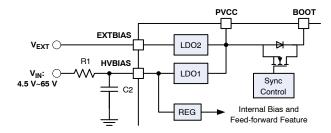

Two LDOs are included in FAN65008B to provide internal supply and to balance power loss from them. The LDO block diagram is shown below.

Figure 40. LDO Block Diagram

Since LDO1 input, HVBIAS, is also used for initial internal bias and for input voltage feed-forward compensation, system input voltage, VIN, should always be connected to HVBIAS pin and an RC filter is recommended between VIN and HVBIAS to filter any noise from high frequency switching. During power up, LDO1 is always selected. After the system finishes soft start, which LDO block is selected depends on voltages appearing on both HVBIAS and EXTBIAS pins. If there is a voltage at EXTBIAS pin and it is above 4.7 V, LDO2 will be selected, otherwise LDO1 will continue to supply power to the device. EXTBIAS can be left open for single LDO operation all the time. In the case that EXTBIAS is connected to a voltage,  $V_{EXT}$ , and  $V_{EXT} > 4.7$  V and also  $V_{EXT} > V_{HVBIAS}$ , LDO2 will be selected. This makes power loss on LDO2 greater than that on LDO1 if LDO1 were selected. So it's the designer's responsibility to make sure  $V_{EXT} < V_{HVBIAS}$ while  $V_{EXT} > 4.7$  V. Both LDOs work in switch mode when their input voltages are lower than 5.5 V. This allows very low voltage drop on both LDOs and ensures high enough voltage level on PVCC for internal bias and MOSFET drive.

Assuming  $V_{EXT} < V_{HVBIAS}$  while  $V_{EXT} > 4.7$  V, Table 6 shows which LDO will be selected and the LDO work status. (• indicates which LDO and mode are selected and × means disabled)

| Table 6. LDO SELE | <b>CTION AND</b> | WORK MODE |

|-------------------|------------------|-----------|

|-------------------|------------------|-----------|

|               |                | Work Mode |     |        |     |  |  |

|---------------|----------------|-----------|-----|--------|-----|--|--|

| Inp           | out            | LD        | 01  | LDO2   |     |  |  |

| HVBIAS<br>(V) | EXTBIAS<br>(V) | Switch    | LDO | Switch | LDO |  |  |

| 4.5-4.7       | 4.5-4.7        | •         | ×   | ×      | ×   |  |  |

| 4.7–5.5       | 4.5–4.7        | •         | ×   | ×      | х   |  |  |

|               | 4.7–5.5        | ×         | ×   | •      | ×   |  |  |

| 5.5-65        | 4.5–4.7        | ×         | •   | ×      | х   |  |  |

|               | 4.7–5.5        | ×         | ×   | •      | ×   |  |  |

|               | 5.5–50         | ×         | ×   | ×      | •   |  |  |

Both LDOs are designed to deliver up to 150 mA current. A 4.7  $\mu$ F ceramic capacitor between PVCC and PGND placed as close as possible to PVCC pin is recommended to decouple any noise from high frequency driver currents. A 1  $\Omega$  resistor can be used between PVCC and VCC

together with a ceramic capacitor between VCC and AGND to form a filter for the VCC bias supply for the internal control circuits. When VCC voltage drops below its UVLO, the regulator control circuit blocks are disabled.

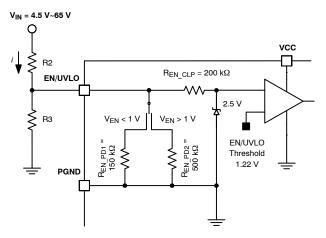

#### Enable and Under Voltage Lock-Out

EN/UVLO signal is used for device enable/disable when its voltage is higher/lower than the threshold,  $V_{EN_TH}$ , which is typical 1.22 V. The precision threshold voltage of this signal can also be used to set a system input voltage level, above which FAN65008B will be enabled and below which disabled. Figure 41 shows the EN/UVLO block diagram and application configuration.

A resistor divider (R2 and R3, as shown in Figure 1) can be used to set the level of input voltage,  $V_{IN\_UVLO}$ , which enables the device. Selection of R3 is determined by Equation 1.

$$R3 = \frac{V_{EN_{TH}} \times R2 \times R_{EN_{PD1}}}{V_{IN_{UVLO}} \times R_{EN_{PD1}} - V_{EN_{TH}} \times R2 - V_{EN_{TH}} \times R_{EN_{PD1}}}$$

R2 and R3 are both in  $k\Omega$ .

Assuming *i*, in mA, is the current flowing through R2 when working input voltage is  $V_{IN}$ , then R2 is determined by Equation 2.

$$R2 = \frac{V_{IN\_UVLO} - V_{EN\_TH}}{V_{IN\_UVLO}} \times \frac{V_{IN}}{i}$$

(eq. 2)

Figure 41. EN/UVLO Block Diagram

For example, a converter has nominal input voltage of  $V_{IN} = 48$  V. It's desired that the device is enabled when input voltage is above 35 V, which makes  $V_{IN\_UVLO} = 35$  V. If 50  $\mu$ A is chosen, then Equations 1 and 2 yield R2 and R3 in Equations 3 and 4 respectively:

$$R2 = \frac{48 \times (35 - 1.22)}{35 \times 50 \times 10^{-6} \times 10^3} = 926.5 \text{ k}\Omega \quad (\text{eq. 3})$$

$$R3 = \frac{1.22 \times 926.5 \times 150}{35 \times 150 - 1.22 \times 926.5 - 1.22 \times 150}$$

$$= 43.1 \text{ k}\Omega$$

(eq. 4)

Choose the closest standard 1% resistor values of R1 = 931 k $\Omega$  and R2 = 43.2 k $\Omega$ . What value is chosen for *i* is a power loss matter. The greater the *i* is, the greater the power loss will be, and vice versa. But if the current is too low, the EN/UVLO signal will be vulnerable to noise. Choose the highest possible current that only creates negligible power loss to the system. In the example shown above, the power loss in this EN/UVLO branch is P = V<sub>IN</sub> ×  $i = 48 \text{ V} \times 50 \text{ }\mu\text{A} = 2.4 \text{ mW}.$

When the device is disabled, only a few micro-ampere current is required to support essential blocks like bandgap. Only after the device is enabled, major functions like, LDO, oscillator, soft start, driver, logic control, start to run. The device is disabled if the EN/UVLO pin is floating.

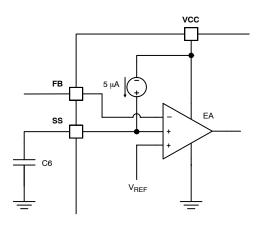

#### Soft Start

The soft start block diagram is shown in Figure 42.

Figure 42. Soft Start Block Diagram

The soft start function is enabled with a delay of maximum 3 ms after EN is high. During the delay, the SS capacitor is discharged if there is any residual voltage. If SS voltage is still not 0 after this delay, a fault condition is created and the device enters hiccup mode, otherwise soft start process is initiated. A typical 5 µA constant current flows out of SS pin to charge the capacitor at SS pin. The error amplifier regulates the converter output voltage according to the lower value of SS pin voltage and the fixed 0.6 V reference voltage. With the constant current, SS voltage linearly ramps up from 0, and the regulator output voltage follows the SS voltage to ramp up. SS voltage continues to rise after it exceeds the 0.6 V reference voltage, at which point, the SS voltage is out of the loop and the converter output voltage is regulated to the reference voltage of 0.6 V. When SS capacitor is charged to 1.5 V, the SS timer stops counting and the device checks if FB has reached 94%  $V_{REF}$ . If not, the device enters hiccup mode, otherwise, the device considers the soft start successful and continues to charge SS capacitor until it reaches VCC.

If the SS pin is floating, device enters hiccup.

#### **Pre-bias Startup**

A pre-biased regulator is one that, before the regulator is powered, has output voltage above 0, and so for the FB pin. FAN65008B is able to start in such a case. When soft start is initiated, both high- and low-side MOSFETs are forced off until the SS pin is charged up to the pre-biased FB voltage. The following startup process will be a normal soft start process as stated in "Soft Start" section.

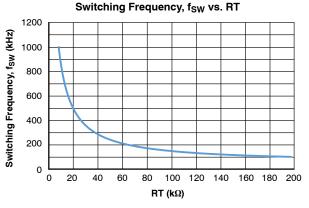

#### **Switching Frequency**

The internal clock generator can be programmed from 100 kHz to 1 MHz by a resistor connected between the  $R_T$  pin and the AGND pin. To set the desired switching frequency, the resistor can be calculated by Equation 5 as shown below:

$$f_{\rm SW} = \min\left[\frac{10^4}{\rm RT + 2.5} + 50, \ 1000\right]$$

(eq. 5)

where  $f_{SW}$  is in kHz and RT is in k $\Omega$ .

The switching frequency vs. the external resistor curve is shown below.

Figure 43. Relationship between RT and f<sub>SW</sub>

As soon as the device is enabled, it will go through a set of routine to check the RT pin configuration to determine the switching frequency or if there is any fault. If RT is tied to VCC, the switching frequency is 250 kHz, and 500 kHz if short-circuited to AGND. If RT pin is floating initially or becomes open from any non-open state, the device enters hiccup mode.

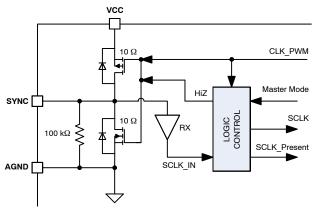

#### **Frequency Synchronization**

FAN65008B can be set to work in either master mode or non-master mode. When in master mode, it sends out clock signal through SYNC pin; when in non-master mode, it either takes in clock signal from an external source on SYNC pin in  $\pm 30\%$  of RT set frequency or uses RT to set its clock. Both modes are configured via MODE pin.

1. Master mode: A 100 k $\Omega$  resistor connected between MODE pin and either VCC or AGND

will enable master mode. In this mode, FAN65008B generates its ramp and PWM signal by its own and sends out PWM clock through SYNC pin with 180 degree phase shift and 50% duty cycle. If an external clock is detected on SYNC pin that is in conflict with the internal one, FAN65008B makes SYNC pin high impedance until fault is cleared.

2. Non-master mode: The MODE pin connected to either VCC or AGND through a 1 k $\Omega$ ~5 k $\Omega$ resistor or left floating enables this mode. In this mode, the device keeps checking the SYNC pin for incoming clocks every 2 ms. If 64 cycles of clock are detected and the clock frequency is in  $\pm 30\%$  of RT set frequency, the device is in sync with the clock appearing on SYNC pin. If no clocks are detected, the number of clocks in 2 ms does not reach 64, or the clock frequency is not within  $\pm 30\%$  of RT set frequency, the device uses RT to set the clock. The synchronization block diagram is shown below.

Figure 44. Frequency Synchronization Block Diagram

FAN65008B implements fault protection in case SYNC pin is short-circuited to either AGND or VCC. The logic checks voltage levels of both internal driving clock and SYNC pin except for a 100 ns time period at every clock transition, which is used to mask the transition glitches due to propagation delay. These 2 logic levels are expected to be the same when there is no pin fault. When SYNC pin fault is detected, the driver is disabled by using high impedance for 8 clock cycles, which makes worst case duty cycle of ~1.67% with 1 MHz frequency.

SYNC pin fault is only a local fault and doesn't trigger global hiccup or stop device operation. Figure 44 shows the frequency synchronization block diagram.

#### **Operation Modes**

The MODE pin controls 2 functions: pulse modulation and frequency synchronization.

Pulse modulation refers to continuous conduction fixed frequency pulse width modulation (short-formed Forced CCM) and discontinuous conduction with pulse skipping modulation (Short-formed DCM with Pulse Skipping). When in DCM with Pulse Skipping, device works in discontinuous conduction mode when inductor current hit 0 and may skip pulses when load becomes even lighter; device transits to fixed frequency operation and works in continuous conduction mode when inductor current valley is higher than 0. Frequency synchronization refers to master or non-master mode.

If low output voltage ripple is desired, Forced CCM PWM operation can be selected. In this mode, continuous conduction fixed switching frequency applies regardless of light load or heavy load and negative current appears at light load condition. This results in greater power loss at light load.

To reduce the power loss at light load, DCM with Pulse Skipping can be chosen. When at light load, the device works in discontinuous conduction mode and skips pulses, so that the power loss is reduced.

The relationship between the MODE configuration and the actual mode is illustrated in the following table:

| CONFIGURATION                                                                                                                     |                            |            |  |

|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------|--|

| MODE Pin                                                                                                                          | Operation Mode             |            |  |

| Configuration                                                                                                                     | Pulse Modulation           | Freq Sync  |  |

| $\begin{array}{c} \text{VCC} \leftarrow \\ \text{R} = 1  k\Omega {\sim} 5  \text{k}\Omega \rightarrow \\ \text{MODE} \end{array}$ | Forced CCM                 | Non-master |  |

| $ \begin{array}{c} VCC \leftarrow \\ R = 100 \ k\Omega \ \pm 30\% \\ \rightarrow MODE \end{array} $                               | Forced CCM                 | Master     |  |

| $\begin{array}{c} GND \leftarrow \\ R = 1 \ k\Omega {\sim} 5 \ k\Omega \rightarrow \\ MODE \end{array}$                           | DCM with Pulse<br>Skipping | Non-master |  |

| $\begin{array}{c} GND \leftarrow \\ R = 100 \ k\Omega \ \pm 30\% \\ \rightarrow MODE \end{array}$                                 | DCM with Pulse<br>Skipping | Master     |  |

| Floating                                                                                                                          | Forced CCM                 | Non-master |  |

#### Table 7. OPERATION MODES WITH MODE CONFIGURATION

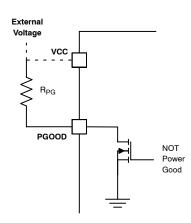

#### Power Good

A comparator monitors the FB voltage and controls an open drain MOSFET. The PGOOD pin is connected to the Drain of this MOSFET. To correctly use the PGOOD signal, a pull-up resistor connected to an external voltage source is required. When FB voltage exceeds 94% of  $V_{REF}$  (typical 0.6 V), PGOOD signal is asserted after a delay,  $t_{PG}$  DL, and when it's below 92% of  $V_{REF}$  it is de-asserted. PGOOD signal is valid only after device is enabled and soft start is completed (SS ramps above 0.6 V). When OVP1 is detected, PGOOD is de-asserted. PGOOD is re-asserted with 5% hysteresis. Figure 45 shows the internal circuitry connected to PGOOD pin.

Figure 45. PGOOD Block Diagram

#### **Setting Current Limit**

A resistor, R ILIM, connected between ILIM pin and GND is used to set the current limit for both high- and low-side MOSFETs. An 8.5 µA internal current source flows through R ILIM, creating a reference voltage, and the voltage drops on R<sub>DSON</sub> of both high- and low-side MOSFETs are used to compare with this reference voltage. This comparison generates an over current event. The high-side MOSFET current is monitored in forward direction, i.e. current flows from drain to source, while low-side MOSFET current is monitored in a reverse direction. When low-side MOSFET turns on in a normal condition, its current flows from ground to switching node. Current is NOT monitored in this case. If current flows from switching node to ground, it is considered abnormal and is monitored. The current limit for both high- and low-side MOSFETs is calculated the same way,  $I_{LIM} = k_{ILIM} \times R_{ILIM}$ , and kILIM parameters for both high- and low-side MOSFETs are shown in the Electrical Characteristic Table. If ILIM is tied to VCC, system is in standby mode, enabling all blocks except driver.

R\_ILIM below 60 k $\Omega$  is defined as short-circuit, above 350 k $\Omega$  is considered to be open.

#### Over Current Protection (OCP) and Short Circuit Protection (SCP)

FAN65008B implements over current protection for highand low-side MOSFETs in a different way.

For high-side MOSFET, FAN65008B sets two levels of over load protection according to the current limit setting: over current protection (OCP) and short circuit protection (SCP). OCP happens when the high-side MOSFET current,  $i_{DS}$  HS, is in the range of 100%  $I_{LIM}$  HS  $\leq i_{DS}$  HS < 130%  $I_{LIM}$  HS, and SCP occurs when  $i_{DS}$  HS < 130%  $I_{LIM}$  HS. FAN65008B monitors MOSFET current constantly and provides cycle by cycle peak current limit. The high-side MOSFET is turned off whenever its current exceeds the limit.

Once the current limit is hit, FAN65008B counts. If 1024 consecutive OCP events have reached, regardless of the FB voltage, the system enters hiccup mode.

The worst case of over current is such conditions as short-circuited output or saturated inductor, in which the current exceeds 130% of current limit. In this case, device initiates short circuit protection and enters hiccup mode immediately.

For low-side MOSFET, FAN65008B performs cycle by cycle protection if its current limit is hit. At each cycle of low-side MOSFET turn-on, its current is checked. If the current exceeds its current limit,  $I_{LIM}$  LS, the low-side MOSFET will be turned off immediately and remains off until next switching cycle. This process repeats until the over current event is released (low-side MOSFET current becomes less than  $I_{LIM}$  LS). Low-side MOSFET over current protection doesn't affect high-side MOSFET switching i high-side MOSFET over current event does not occur.

#### **Hiccup Mode**

Hiccup mode is described as follows. When a fault condition is met, both high- and low-side MOSFETs turn off for a period of time,  $t_{\rm HICCUP}$  (typical 1 s), and soft start capacitor is discharged. Then device enters soft start. After soft start, if the fault condition is met again, both high- and low-side MOSFETs turn off for  $t_{\rm HICCUP}$  again and soft start capacitor is discharged...System returns to normal operation after the fault event is released.

#### **Over Voltage Protection (OVP)**

There are 2 levels of over voltage protection: over voltage protection 1 (OVP1) and over voltage protection 2 (OVP2), which are defined below respectively.

- 1. OVP1 is protection when FB voltage is above 115% but below 130% of  $V_{REF}$ . When OVP1 is triggered, both high- and low-side MOSFETs are turned off immediately. When FB falls to or below  $V_{REF}$ , the system returns to normal operation and initiates a new PWM signal at the next clock cycle.

- 2. OVP2 is protection when FB voltage is above 130% of V<sub>REF</sub>. When OVP2 is triggered, the high-side MOSFET is turned off immediately while the low-side MOSFET is turned ON. If over current event occurs during the low-side MOSFET ON time, cycle by cycle protection will be performed as described in "Over Current Protection (OCP) and Short Circuit Protection (SCP)" section. As soon as over current event is released, the low-side MOSFET will be kept on again until FB voltage drops to or below V<sub>REF</sub>. One hiccup cycle is initiated once output voltage reaches 100% level. After the hiccup, the part will go into a soft start sequence and try to regulate. If OVP2 happens during the hiccup timing period, nothing will happen.

In the case of OVP, power good signal is de-asserted and re-asserted after  $V_{FB}$  comes down to 110%  $V_{REF}\!.$

#### **Under Voltage Protection (UVP)**

Under voltage is a condition when output voltage is below 35% of its regulated level (checked on FB pin). If  $V_{FB} \le 35\%$  is met, then under voltage protection (UVP) is initiated, where IC enters hiccup mode.

#### **Over Temperature Protection (OTP)**

The device keeps monitoring the junction temperature. When the sensed temperature is above the protection point,  $T_{J\_SD}$ , over temperature protection (OTP) event occurred and the system shuts down. OTP is released when the sensed temperature is 20° lower than the trip point,  $T_{J\_SD}$ , where the system resets through soft-start.

#### **Output Inductor Selection**

The output inductor is selected to meet the output ripple requirements. The inductor value determines the converter's ripple current  $\Delta$ IL. Largest ripple current occurs at highest Vin voltage.

$$\Delta IL = \frac{\left(V_{IN} - V_{OUT}\right) \left(V_{OUT}\right)}{F_{SW} \cdot L \cdot V_{IN}}$$

(eq. 6)

Lower ripple current reduced core losses in the inductor and output voltage ripple. Highest efficiency is obtained at low frequency with small ripple current, however with a disadvantage of using a large inductor. Inductor value can be chosen based on the equation below in order to not exceed a max ripple current (usually 30% to 70% of max inductor current)

$$L \geq \frac{\left(V_{IN} - V_{OUT}\right)}{F_{SW} \cdot \Delta I_{L}} \cdot D \qquad (eq. 7)$$

#### **Output Capacitor Selection**

In general, the output capacitors should be selected to meet the dynamic regulation requirements including ripple voltage and load transients.

1. For ripple voltage considerations; the output bulk maintains the DC output voltage. The use of ceramic capacitors is recommended to sustain a low output voltage ripple. At switching frequency the ceramic capacitors are capacitance dominante use the following equation for calculating  $C_{out}$  where the ripple output voltage is within 1% of Vout.

$$\Delta_{\text{OUT}} = \frac{V_{\text{OUT}} \cdot (1 - D)}{8 \cdot F_{\text{SW}}^2 \cdot L \cdot C_{\text{OUT}}}$$

(eq. 8)

And the RMS current through it is

$$I_{\text{COUT(RMS)}} = I_{\text{OUT}} \cdot \frac{\Delta I_{\text{L}}(\text{pp})}{\sqrt{12}}$$

(eq. 9)

2. The maximum capacitor value required to provide the full, rising step, transient load current during the response time of the inductor is shown

$$C_{MIN} = \frac{L \cdot I_{PK}^{2}}{(V_{OV} + V_{OUT})^{2} - V_{OUT}^{2}}$$

(eq. 10)

where  $I_{PK}$  is defined as:

$$I_{\text{PEAK}} = I_{\text{OUT,MAX}} - \frac{\Delta I_{\text{L}}}{2}$$

(eq. 11)

Where CMIN is the minimum value of output capacitor required, L is the output inductor, IPK is the peak load current, VOV is the increase in output voltage during a load release, VOUT is output voltage.

#### Input Capacitor Selection

Voltage and RMS current rating of the input capacitors are critical factors. Typically input capacitor is designed based on input voltage ripple of 2%. Capacitor voltage rating must be at least 1.25x greater than max input voltage . Maximum RMS current supplied by the input capacitance occurs at 50% duty cycle and when Vin =2 x Vout.

RMS current varies with load as shown below:

$$I_{\text{CIN(RMS)}} = I_{\text{OUT}} \cdot \sqrt{D \cdot \left(1 - D + \frac{\Delta IL(pp)^2}{12}\right)}$$

(eq. 12)

Ceramic capacitors are best known for low ESR and are highly recommended.

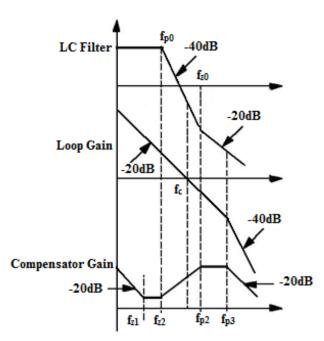

#### Loop Compensation

#### Selecting External Compensation:

The FAN65008B is a voltage mode buck regulator with an error amplifier compensated by external components to achieve accurate output voltage regulation and to respond to fast transient events. The goal of the compensation network is to provide a loop gain function with the highest cross–over frequency at adequate phase and gain margins.

The output stage (LC) of the buck regulator is a double pole system. The resonance frequency of this lowpass filter is shown below:

$$f_{\rm p0} = \frac{1}{2\pi \cdot \sqrt{\rm LC_{\rm OUT}}} \tag{eq. 13}$$

The output filter has a zero that is calculated from the output capacitance and output capacitor ESR:

$$f_{z0} = \frac{1}{2\pi \cdot \text{ESR} \cdot \text{C}_{\text{OUT}}} \quad (\text{eq. 14})$$

The bode plot of the power stage, error amplifier and the desired loop gain are drawn in the figure below. The first zero ( $f_{z1}$ ) compensates the phase lag of the pole located at the origin followed by a second zero ( $f_{z2}$ ) to compensate for one of the poles of the LC filter in order to crossover ( $f_c$ ) at -20 dB slope. The second pole ( $f_{p2}$ ) is aimed to cancel the ESR zero and finally the third pole ( $f_{p3}$ ) is to provide attenuation for frequencies above  $f_{sw/2}$ .

Figure 46. Power Stage, Loop Gain and Compensator Bode Plots

For ease of calculation, with C1 >> C3:

$$f_{z1} = \frac{1}{2\pi \cdot (\text{R10} + \text{R9}) \cdot \text{C9}}$$

$$f_{z2} = \frac{1}{2\pi \cdot \text{R8} \cdot \text{C7}}$$

$$f_{p2} = \frac{1}{2\pi \cdot \text{R9} \cdot \text{C9}}$$

$$f_{p3} = \frac{1}{2\pi \cdot \text{R9} \cdot \text{C9}}$$

$$f_{c} = \frac{V_{\text{IN}}}{2\pi \cdot \text{V}_{\text{Bamp}} \cdot \text{R10} \cdot \text{C7}}$$

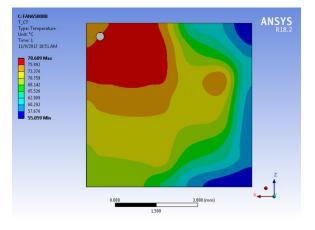

#### **Thermal Considerations**

The temperature gradients on the FAN65004B are shown below. While measuring the thermal performance, place the thermocouple at the hottest spot of the IC (not at the center of the part).

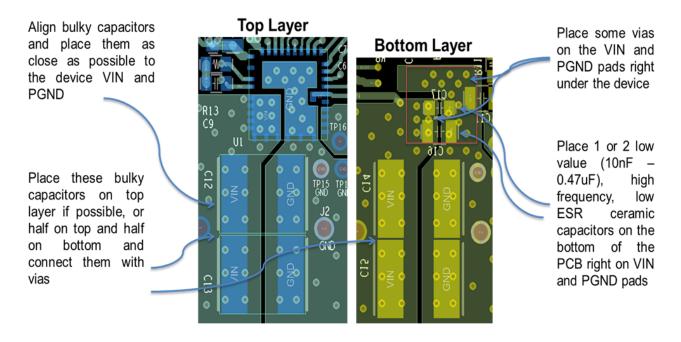

#### Layout Guidelines

- 1. Place RT resistor and SS capacitor close to RT and SS pins.

- 2. Use a low impedance source such as a logic gate to drive the SYNC pin and keep the PCB trace as short as possible.

- 3. Components of digital signals like EN/UVLO, PGOOD and SYNC can be placed far away from device.

- 4. Place BOOT capacitor right next to BOOT and PH pins. If flexibility of high-side MOSFET driving strength is desired, place a resistor in series with this BOOT capacitor. For Vin > 40 V, use Rboot = 2 ohm.

- 5. Place inductor on top layer. Restrict the SW trace to only cover the inductor pin but keep its trace as wide as possible for thermal relief.

- 6. Avoid all the compensation components from passing through, above or underneath switching trace.

- 7. Keep the switching nodes away from sensitive small signal nodes (FB). Ideally the switch nodes printed circuit traces should be routed away and separated from the IC and especially the quiet side of the IC. Separate the high dv/dt traces from sensitive small–signal nodes with ground traces or ground planes.

- 8. Place decoupling caps right next to PVCC, VCC, HVBIAS and EXTBIAS.

- The output capacitors should be placed as close to the load as possible. Use short wide copper regions to connect output capacitors to load to avoid inductance and resistances.

#### Table 8. ORDERING INFORMATION

| Part Number | Current Rating (A) | Input Voltage Max. (V) | Frequency Max. (kHz) | Package                  |

|-------------|--------------------|------------------------|----------------------|--------------------------|

| FAN65008B   | 8                  | 65                     | 1000                 | PQFN 6.0 $\times$ 6.0 mm |

DATE 06 JUL 2021

| DIM | MILLIMETERS |          |      |  |

|-----|-------------|----------|------|--|

|     | MIN.        | NOM.     | MAX. |  |

| A   | 0.70        | 0.75     | 0.80 |  |

| A1  | 0.00        | -        | 0.05 |  |

| A3  |             | 0.20 REF |      |  |

| b   | 0.20        | 0.25     | 0.30 |  |

| D   | 5.90        | 6.00     | 6.10 |  |

| D2  | 4.70        | 4.80     | 4.90 |  |

| D3  | 1.50        | 1.60     | 1.70 |  |

| D4  | 1.65        | 1.90     | 2.00 |  |

| D5  | 2.50        | 2.60     | 2.70 |  |

| D6  | 0.50        | 0.60     | 0.70 |  |

| D7  | 1.65        | 1.75     | 1.85 |  |

| D8  | 0.20        | 0.30     | 0.40 |  |

| E   | 5.90        | 6.00     | 6.10 |  |

| E2  | 3.85        | 3.95     | 4.05 |  |

| E3  | 2.15        | 2.25     | 2.35 |  |

| E4  | 2.45        | 1.55     | 1.65 |  |

| E5  | 1.95        | 2.05     | 2.15 |  |

| E6  | 0.25        | 0.35     | 0.45 |  |

| е   |             | 0.50 BSC | ;    |  |

| e1  |             | 0.75 BSC | ;    |  |

| e2  | 1.00 BSC    |          |      |  |

| e3  | 0.90 BSC    |          |      |  |

| e4  | 0.225 BSC   |          |      |  |

| k   | 0.50 REF    |          |      |  |

| k1  | 0.50 REF    |          |      |  |

| k2  | 0.75 REF    |          |      |  |

| L   | 0.30        | 0.40     | 0.50 |  |

| L1  | 0.10        | 0.20     | 0.30 |  |

| L4  | 0.30        | 0.40     | 0.50 |  |

| L5  | 0.80        | 0.90     | 1.00 |  |

| z1  |             | 0.35 REF |      |  |

| z2  | 0.84 REF    |          |      |  |

| z3  | 0.35 REF    |          |      |  |