**ON Semiconductor**

Is Now

## Onsemí

To learn more about onsemi<sup>™</sup>, please visit our website at <u>www.onsemi.com</u>

onsemi and ONSEMI: and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product factures, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application is the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application, Buyer shall indemnify and hold ons

### LV8413GP

# ON Semiconductor®

### **BI-CMOS LSI** For DSC, and Cell Phone Camera Modules H-Bridge × 2-channel Motor Driver Application Note

#### Overview

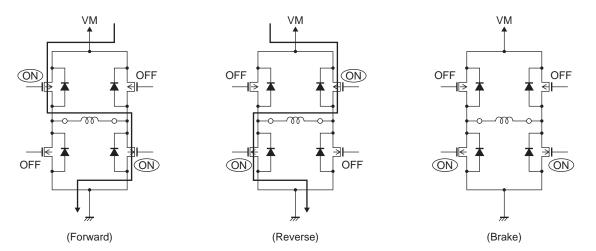

The LV8413GP is an H-bridge, 2-channel motor driver IC and is able to control 4 modes of forward, reverse, brake, and standby.

This IC housed in a miniature package is optimum for use in a stepping motor driving system for DSC or a camera module of cell phones.

#### Function

- Saturation drive H-bridge : 2-channels

- Built-in thermal protection circuit

- Built-in low voltage malfunction prevention circuit

- Incorporates a transistor for driving photosensors

#### **Typical Applications**

- DSC

- Security camera

- CCTV

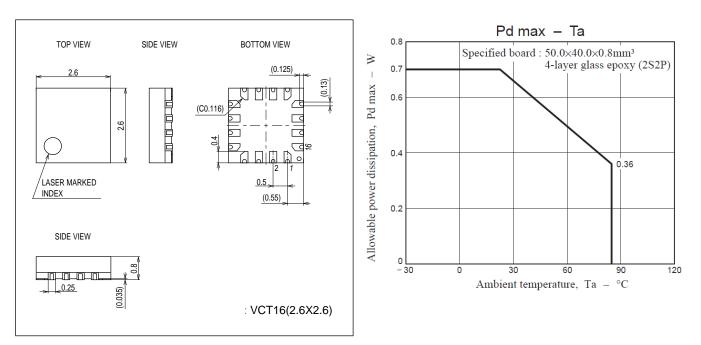

#### **Package Dimensions**

unit : mm (typ)

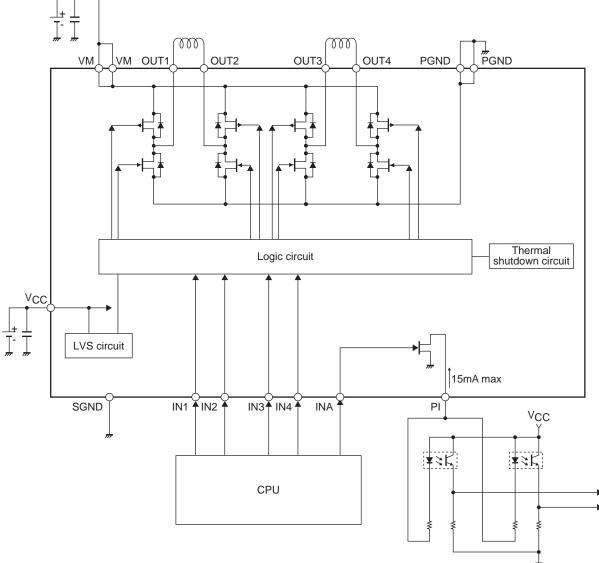

#### **Block Diagram**

Notes on Wiring and Lines

- 1. Connect both the PGND pins and both the VM pins. Although both the PGND and VM lines are connected internally, both must be connected to provide even lower on-resistance output.

- 2. Since large currents flow in the VM and PGND lines, these lines should be made thicker, and line impedance reducing capacitors should be inserted in the vicinity of the IC.

- 3. Since SGND is the ground for the control system, rather than using the same wiring as the PGND line, it is preferable to connect this pin to the CPU ground line.

- 4. No restriction on priority among applied voltages of VM and VCC.

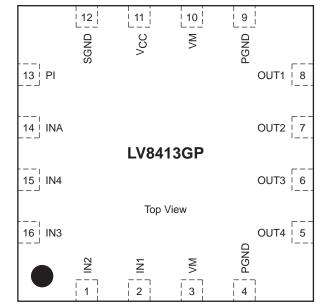

#### **Pin Assignment**

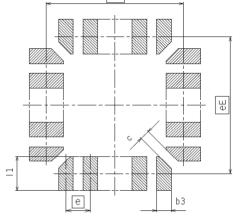

Recommended Soldering Footprint

(Unit:mm) Packages name VCT/UCT2D(3,0X3,0) Reference symbol VCT/UCT16(2,6X2,6) VCT/UCT20 (2.6X2.6) T24 (3. OX3. O) VCT/UCT24 (3, 5X3, 5) 2, 30 2, 30 2,70 2,70 0,50 2, 70 2, 70 0, 40 3,2[ 3,2[ еD <u>2,30</u> 2,30 e E e 0,40 0,50 0,50 0, 30 0,30 bз 0,19 D, 19 0**,** 3D 0, 70 0, 20 0, 70 0, 20 U<u>. 70</u> 0, 70 0, 20 0,7D 0,2D | 1 D, 20 C

#### Specifications

#### Absolute Maximum Ratings at Ta = 25°C

| Parameter                   | Symbol              | Conditions                                       | Ratings     | Unit |

|-----------------------------|---------------------|--------------------------------------------------|-------------|------|

| Power supply voltage 1      | VM max              |                                                  | 6           | V    |

| Power supply voltage 2      | V <sub>CC</sub> max |                                                  | 6           | V    |

| Output peak current         | I <sub>O</sub> peak | Outs 1 to 4, t $\leq$ 10msec, ON-duty $\leq$ 20% | 600         | mA   |

| Output continuous current 1 | I <sub>O</sub> max1 | Outs 1 to 4                                      | 400         | mA   |

| Output continuous current 2 | I <sub>O</sub> max2 | PI                                               | 15          | mA   |

| Allowable power dissipation | Pd max              | Mounted on a circuit board*                      | 0.7         | W    |

| Operating temperature       | Topr                |                                                  | -30 to +85  | °C   |

| Storage temperature         | Tstg                |                                                  | -55 to +150 | °C   |

\* Specified circuit board : 50.0mm  $\times$  40.0mm  $\times$  0.8mm : glass epoxy four-layer board (2S2P)

Caution 1) Absolute maximum ratings represent the value which cannot be exceeded for any length of time.

Caution 2) Even when the device is used within the range of absolute maximum ratings, as a result of continuous usage under high temperature, high current, high voltage, or drastic temperature change, the reliability of the IC may be degraded. Please contact us for the further details.

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

#### Recommended Operating Conditions at Ta = 25°C

| Descenter                    | Querra ha a l   | Que d'itiene  |     | Ratings |                      |      |  |  |

|------------------------------|-----------------|---------------|-----|---------|----------------------|------|--|--|

| Parameter                    | Symbol          | Conditions    | min | typ     | max                  | Unit |  |  |

| Power supply voltage range 1 | VM              |               | 2.5 |         | 5.5                  | V    |  |  |

| Power supply voltage range 2 | V <sub>CC</sub> |               | 2.5 |         | 5.5                  | V    |  |  |

| Logic input voltage range    | V <sub>IN</sub> |               | 0   |         | V <sub>CC</sub> +0.3 | V    |  |  |

| Input frequency              | fIN             | IN1 to 4, INA |     |         | 100                  | kHz  |  |  |

#### **Electrical Characteristics** at Ta = $25^{\circ}$ C, VM = 5V, V<sub>CC</sub> = 3.3V, unless otherwise specified.

| Deservation                                | Ourseland           |                                             |      | Ratings |      | L I a it |

|--------------------------------------------|---------------------|---------------------------------------------|------|---------|------|----------|

| Parameter                                  | Symbol              | Conditions                                  | min  | typ     | max  | Unit     |

| Standby mode current drain                 | Istn                | IN1 to 4 = "L"                              |      |         | 1.0  | μΑ       |

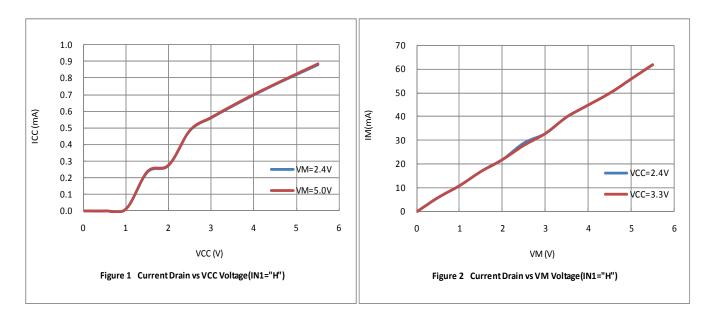

| VM current drain                           | IM                  | Any one of IN1 to 4 = "H", with no load     |      | 70      | 150  | μA       |

| V <sub>CC</sub> current drain              | ICC                 | Any one of IN1 to 4 = "H"                   |      | 0.6     | 1.2  | mA       |

| V <sub>CC</sub> low-voltage cutoff voltage | VthV <sub>CC</sub>  |                                             | 1.85 | 2.10    | 2.35 | V        |

| Low-voltage hysteresis voltage             | VthHYS              |                                             | 100  | 150     | 200  | mV       |

| Thermal shutdown temperature               | TSD                 | Design guarantee value *                    | 160  | 180     | 200  | °C       |

| Thermal hysteresis width                   | ΔTSD                | Design guarantee value *                    | 10   | 30      | 50   | °C       |

| OUT1 to 4                                  |                     | •                                           |      |         |      |          |

| Logic pin internal pull-down resistance    | Rin                 | IN1 to 4                                    | 50   | 100     | 200  | kΩ       |

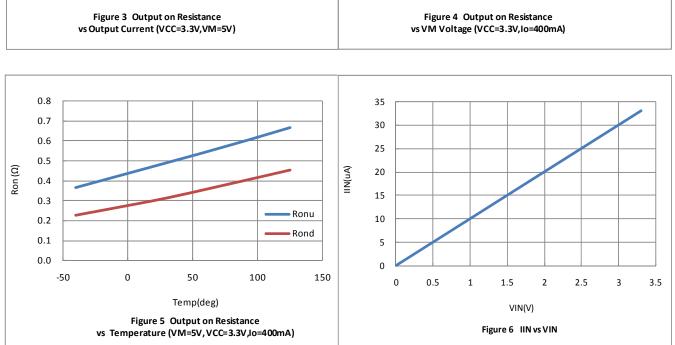

| Logic pin input current                    | linL                | $V_{IN} = 0$ , IN1 to 4                     |      |         | 1.0  | μA       |

|                                            | linH                | V <sub>IN</sub> = 3.3V, IN1 to 4            | 20   | 33      | 60   | μA       |

| Logic input high-level voltage             | VinH                | IN1 to 4                                    | 2.5  |         |      | V        |

| Logic input low-level voltage              | VinL                | IN1 to 4                                    |      |         | 1.0  | V        |

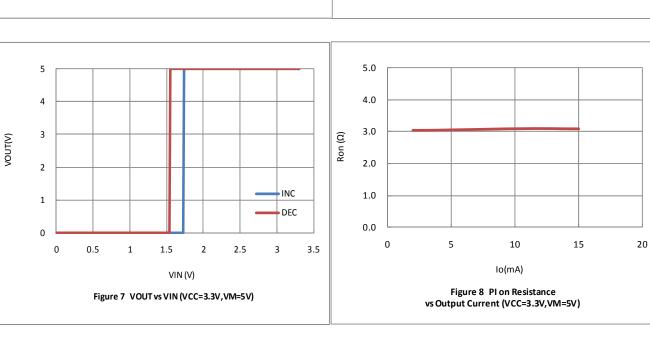

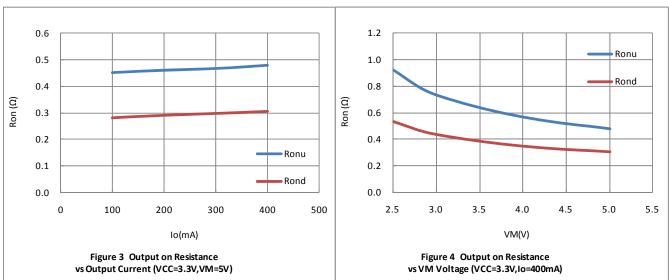

| Output on-resistance                       | Ronu                | I <sub>O</sub> = 400mA, upper ON resistance |      | 0.5     | 0.8  | Ω        |

|                                            | Rond                | I <sub>O</sub> = 400mA, lower ON resistance |      | 0.3     | 0.5  | Ω        |

| Output leakage current                     | l <sub>O</sub> leak |                                             |      |         | 1    | μA       |

| Diode forward voltage                      | VD                  | ID = -400mA                                 |      | 1.0     |      | V        |

| PI                                         |                     | •                                           |      |         |      |          |

| Logic pin internal pull-down resistance    | Rin                 | INA                                         | 50   | 100     | 200  | kΩ       |

| Logic pin input current                    | linL                | V <sub>IN</sub> = 0, INA                    |      |         | 1.0  | μA       |

|                                            | linH                | V <sub>IN</sub> = 3.3V, INA                 | 20   | 33      | 50   | μA       |

| Logic input high-level voltage             | VinH                | INA                                         | 2.5  |         |      | V        |

| Logic input low-level voltage              | VinL                | INA                                         |      |         | 1.0  | V        |

| Output on-resistance                       | Ron                 | I <sub>O</sub> = 10mA                       |      | 4       | 6    | Ω        |

| Output leakage current                     | lOleak              |                                             |      |         | 1    | μA       |

#### **Pin Functions**

| Pin No. | Pin name        | Pin Function                      | Equivalent Circuit |

|---------|-----------------|-----------------------------------|--------------------|

| 2       | IN1             | Control signal input pin          |                    |

| 1       | IN2             | Control signal input pin          |                    |

| 16      | IN3             | Control signal input pin          |                    |

| 15      | IN4             | Control signal input pin          |                    |

| 14      | INA             | Control signal input pin          |                    |

|         |                 |                                   |                    |

| 8       | OUT1            | Outpin                            | 104                |

| 7       | OUT2            | Outpin                            | VM<br>O            |

| 6       | OUT3            | Outpin                            |                    |

| 5       | OUT4            | Outpin                            |                    |

|         |                 |                                   | •                  |

|         |                 |                                   | ↓ → ↓              |

|         |                 |                                   |                    |

|         |                 |                                   |                    |

|         |                 |                                   |                    |

|         |                 |                                   |                    |

|         |                 |                                   |                    |

|         |                 |                                   |                    |

|         |                 |                                   |                    |

|         |                 |                                   |                    |

|         |                 |                                   |                    |

|         |                 |                                   |                    |

|         |                 |                                   |                    |

|         |                 |                                   | PGND               |

|         |                 |                                   |                    |

| 13      | PI              | Outpin                            | $\frown$           |

|         |                 |                                   |                    |

|         |                 |                                   |                    |

|         |                 |                                   |                    |

|         |                 |                                   |                    |

|         |                 |                                   |                    |

|         |                 |                                   |                    |

|         |                 |                                   | GND                |

|         |                 |                                   | GND                |

| 11      | V <sub>CC</sub> | Logic system power supply         |                    |

|         |                 | connection pin                    |                    |

| 3       | VM              | Motor power supply connection pin |                    |

| 10      | VM              | Motor power supply connection pin |                    |

| 12      | SGND            | Signal ground                     |                    |

| 4       | PGND            | Power ground                      |                    |

| 9       | PGND            | Power ground                      |                    |

#### **Operation explanation**

Common channels 1 to 2 ch1 : IN1 to IN2, OUT1 to OUT2 ch2 : IN3 to IN4, OUT3 to OUT4

| Inj | put | Out  | tput |                |  |  |

|-----|-----|------|------|----------------|--|--|

| IN1 | IN2 | OUT1 | OUT2 | Operation mode |  |  |

| L   | L   | OFF  | OFF  | Standby        |  |  |

| н   | L   | н    | L    | CW (forward)   |  |  |

| L   | Н   | L    | Н    | CCW (reverse)  |  |  |

| Н   | Н   | L    | L    | Brake          |  |  |

• Current limit control timing chart

#### Photo sensor driving transistor

By setting the INA pin to "H", the photosensor dirving transisitor is activated. The photosensor current is decided by an external resistance value.

| Input | Photo sensor driving |

|-------|----------------------|

| INA   | PI                   |

| L     | OFF                  |

| н     | ON                   |

• Overheating protection function (Thermal Shutdown circuit)

The overheating protection circuit is built into. OUT1 through OUT4 are turned off when junction temperature Tj exceeds 180°C. The value of hysteresis and when it falls, the temperature drives the output again (automatic restoration).

The overheating protection circuit doesn't secure protection and the destruction prevention of the set because it becomes operation by the area where ratings  $Tjmax = 150^{\circ}C$  of the junction temperature was exceeded.

$$TSD = 180^{\circ}C (typ)$$

$$\Delta TSD = 30^{\circ}C (typ)$$

• Low voltage protection function (Low voltage malfunction prevention circuit)

When the VCC voltage is as below typical 2.1V in LV8413GP, OUT1 through OUT4 are turned off. When the VCC voltage is as above typical 2.25V, OUT1 through OUT4 are turned on.

\*When overheating protection function or low voltage protection function is activated, OUT1 through OUT4 are turned off under control of the internal circuit. But the output (PI) of photo sensor driving transistor continues operation.

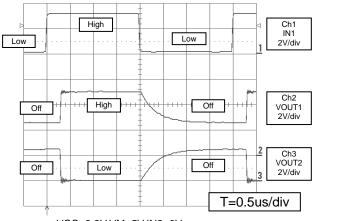

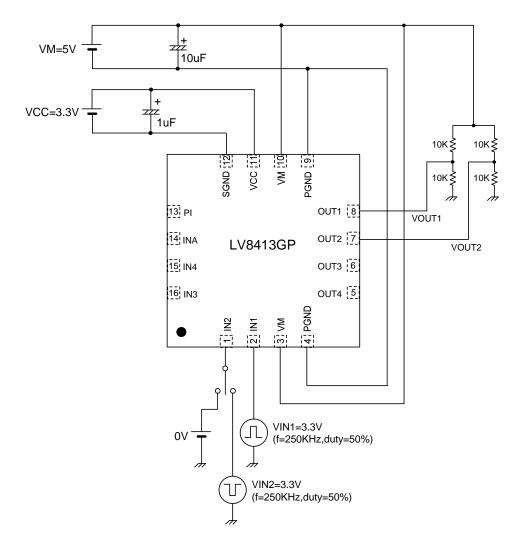

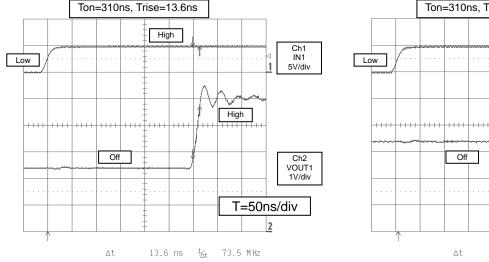

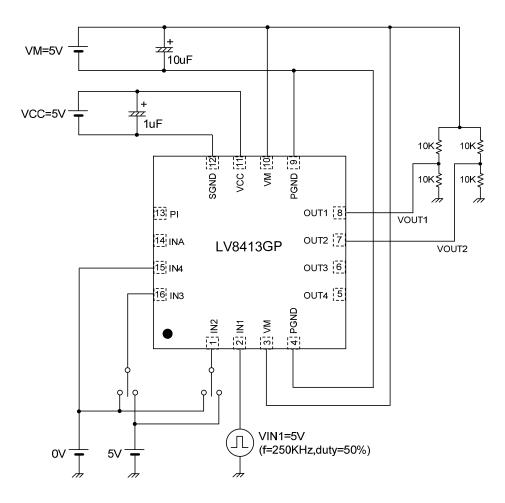

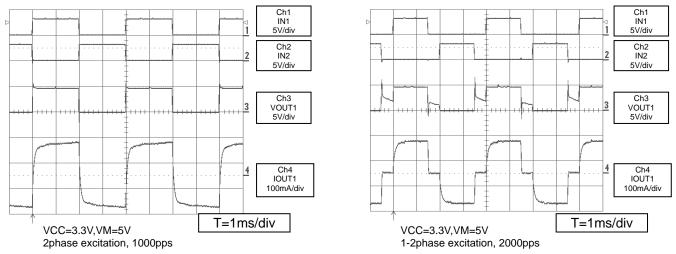

•PWM switching waveform example

\*Please refer to the following test circuit diagram1.

VCC=3.3V,VM=5V,IN2=0V VIN1=3.3V(f=250KHz,duty=50%) OUT1.2=Pull-up&down(10Kohm)

(Test Circuit Diagram1)

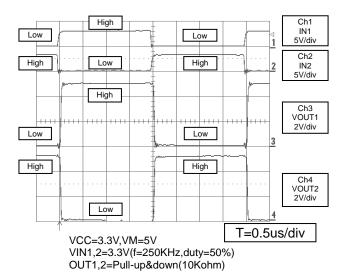

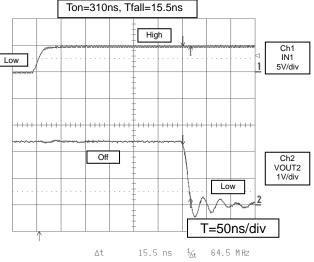

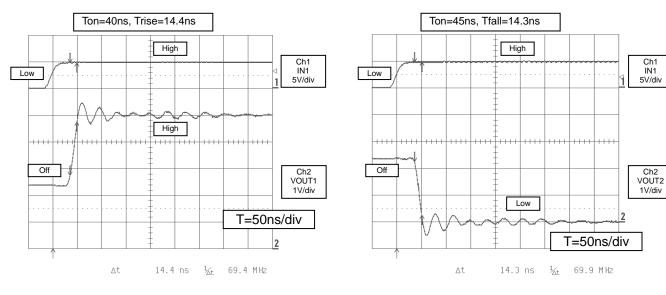

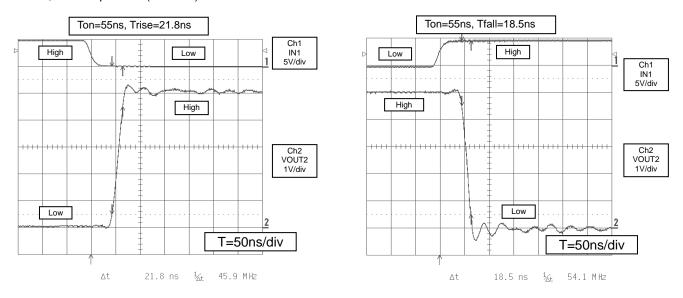

•Macrograph of the PWM switching waveform example \*Please refer to the following Test Circuit diagram2.

[Fast Decay\_1]

VCC=5V, VM=5V, IN2=IN3=IN4=0V VIN1=5V (f=250KHz, duty=50%) OUT1, 2=Pull-up&down (10Kohm)

[Fast Decay\_2] VCC=5V, VM=5V, IN2=IN4=0V, IN3=5V VIN1=5V (f=250KHz, duty=50%) OUT1, 2=Pull-up&down (10Kohm)

Ch1

#### [Slow Decay] VCC=5V, VM=5V, IN2=5V, IN3=IN4=0V VIN1=5V (f=250KHz, duty=50%) OUT1, 2=Pull-up&down (10Kohm)

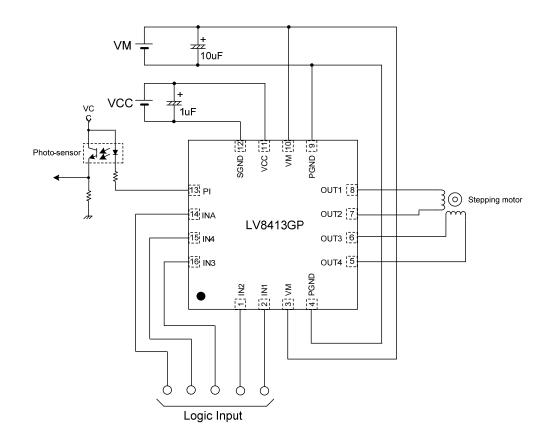

#### (Test Circuit Diagram2)

Application Circuit ExampleExample of application circuit with one stepping motor driving

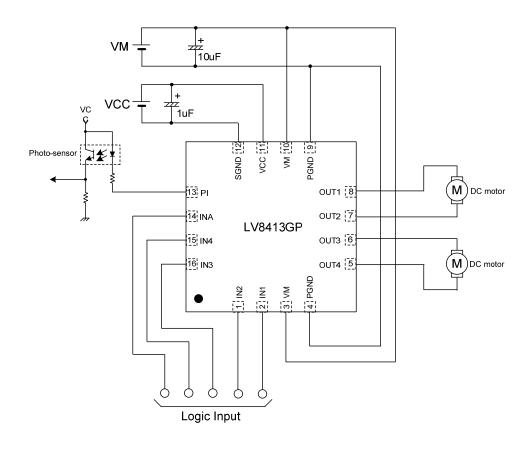

• Example of application circuit with two DC motors driving

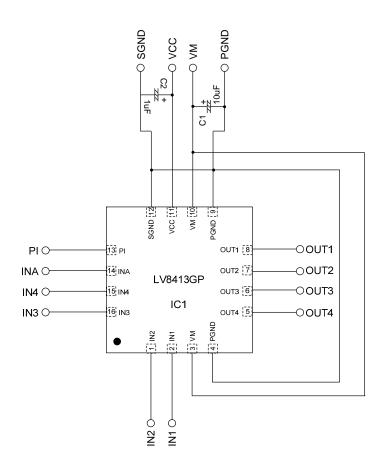

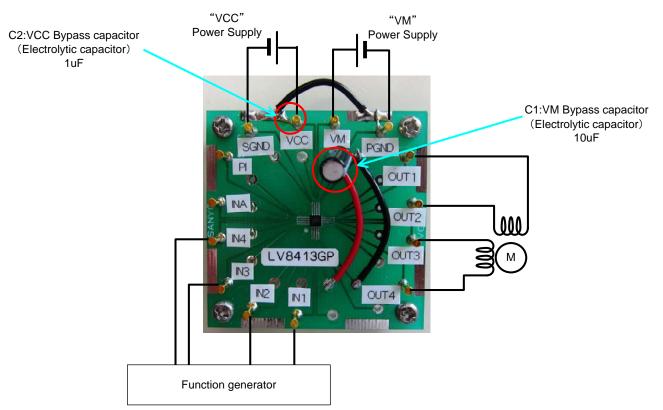

#### Evaluation board manual

•Overview

#### •Circuit diagram

#### Bill of Materials for LV8413GP Evaluation Board

| Designator | Qty | Description             | Value         | Tol  | Footprint          | Manufacturer                 | Manufacturer<br>Part Number | Substitution<br>Allowed | Lead<br>Free |

|------------|-----|-------------------------|---------------|------|--------------------|------------------------------|-----------------------------|-------------------------|--------------|

|            |     |                         |               |      |                    |                              |                             |                         |              |

| IC1        | 1   | Motor Driver            |               |      | VCT16<br>(2.6X2.6) | ON<br>Semiconductor          | LV8413GP                    | No                      | Yes          |

| C1         | 1   | VM Bypass capacitor     | 10µF<br>50V   | ±20% |                    | SUN Electronic<br>Industries | 50ME10HC                    | Yes                     | Yes          |

| C2         | 1   | VCC Bypass<br>Capacitor | 0.1µF<br>100V |      |                    | Murata                       | GRM188R72A10<br>4KA35D      | Yes                     | Yes          |

| TP1-TP14   | 14  | Test points             |               |      |                    | MAC8                         | ST-1-3                      | Yes                     | Yes          |

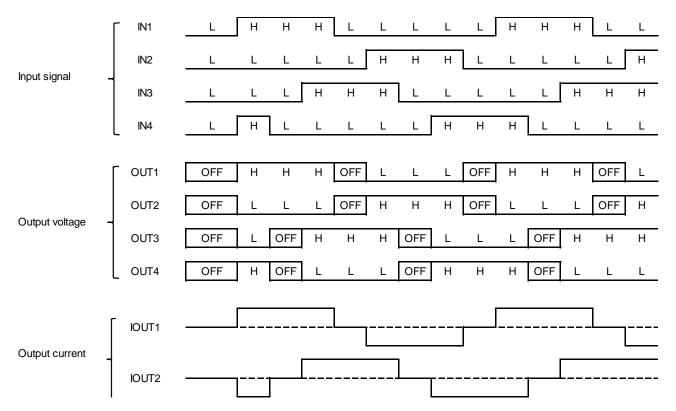

#### •Stepping motor driving method

- Connect a stepping motor with OUT1, OUT2, OUT3 and OUT4.

- Connect the motor power supply with the terminal VM, the control power supply with the terminal VCC. Connect the GND line with the terminal PGND and SGND.

- Stepping motor drives it in 2-phase excitation or 1-2phase excitation by inputting a signal such as follows into IN1, IN2, IN3 and IN4.

- Check the stepping motor if rotating.

- Check the waveform of the output voltage and current.(Please refer to the following waveform example.)

| (2phase ex     | citatio | on)   |    | _ |   |      |   |   |   |             |   |   |   |   | _ |   |   |   |

|----------------|---------|-------|----|---|---|------|---|---|---|-------------|---|---|---|---|---|---|---|---|

| Input signal   | Γ       | IN1   | L  |   | Н | Н    |   | L |   | L           |   | Н |   | Н |   | L |   | L |

|                |         | IN2   | L  |   | L | L    |   | H |   | н           | 1 | L |   | L |   | н |   | Н |

|                | 1       | IN3   | L  |   | L | Н    |   | Н | 1 | L           |   | L |   | н |   | Н |   | L |

|                |         | IN4   | L  |   | Н | L    |   | L |   | Н           |   | Н | ] | L |   | L |   | Н |

|                | ſ       | OUT1  | OF | F | Н | Н    | 1 | L |   | L           |   | Н |   | Н | 1 | L |   | L |

|                |         | OUT2  | OF | F | L | L    |   | Н |   | н           |   | L |   | L |   | Н |   | Н |

| Output voltage | 1       | OUT3  | OF | F | L | Н    |   | H | ] | L           |   | L |   | Н |   | н | 1 | L |

|                | Ĺ       | OUT4  | OF | F | Н | L    |   | L |   | Н           |   | Н | 1 | L |   | L |   | Н |

| Output current | ſ       | IOUT1 |    | [ |   | <br> | ] |   |   |             |   |   |   |   | ] |   |   |   |

|                |         | IOUT2 |    |   |   | <br> |   |   | ] | · <b></b> . |   |   |   |   |   |   |   |   |

#### (1-2phase excitation)

#### •Stepping motor driving waveform example

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equa