### **ESDA14V2-1BF3**

# Single-line bidirectional Transil™ array for ESD protection

#### **Features**

- ESD Protection: IEC61000-4-2 level 4

- Low leakage current

- Very small PCB area < 0.4 mm²</p>

- 400 micron pitch

#### Complies with the following standards

- IEC61000-4-2 level 4

- 15 kV (air discharge)

- 8 kV (contact discharge)

### **Applications**

Where transient overvoltage protection of ESD sensitive equipment is required, such as:

- Computers

- Printers

- Communications systems and cellular phones

- Video equipment

### **Description**

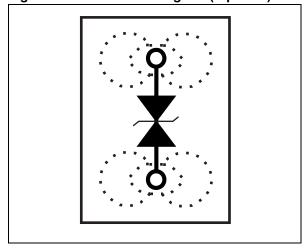

The ESDA14V2-1BF3 is a monolithic bidirectional diode designed to protect 1 line against ESD transients.

The device is ideally suited for applications where both reduced line capacitance and board space saving are required.

Figure 1. Schematic diagram (top view)

TM: Transil is a trademark of STMicroelectronics

June 2009 Doc ID 15894 Rev 1 1/9

Characteristics ESDA14V2-1BF3

### 1 Characteristics

Table 1. Absolute maximum ratings ( $T_{amb} = 25 \, ^{\circ}C$ )

| Symbol           | Parameter                                                                            | Value        | Unit |

|------------------|--------------------------------------------------------------------------------------|--------------|------|

|                  | Peak pulse voltage:                                                                  |              |      |

| $V_{PP}$         | IEC61000-4-2 air discharge                                                           | ±15          | kV   |

|                  | IEC61000-4-2 contact discharge                                                       | ±8           |      |

| P <sub>PP</sub>  | Peak pulse power dissipation (8/20 $\mu$ s) <sup>(1)</sup> $T_{j initial} = T_{amb}$ | 50           | W    |

| T <sub>j</sub>   | Junction temperature                                                                 | 125          | °C   |

| T <sub>stg</sub> | Storage temperature range                                                            | - 55 to +150 | °C   |

| T <sub>L</sub>   | Maximum lead temperature for soldering during 10 s                                   | 260          | °C   |

| T <sub>op</sub>  | Operating junction temperature range                                                 | -40 to +125  | °C   |

<sup>1.</sup> For a surge greater than the maximum values, the diode will fail in short-circuit

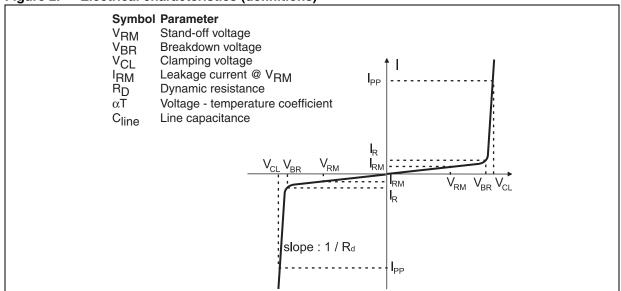

Figure 2. Electrical characteristics (definitions)

Table 2. Electrical characteristics (values, T<sub>amb</sub> = 25 °C)

| Symbol            | Test condition                                                                  |      | Тур. | Max  | Unit                 |  |

|-------------------|---------------------------------------------------------------------------------|------|------|------|----------------------|--|

| $V_{BR}$          | I <sub>R</sub> = 1 mA                                                           | 14.2 | -    | 18.0 | ٧                    |  |

| I <sub>RM</sub>   | V <sub>RM</sub> = 12 V                                                          | -    | -    | 0.5  |                      |  |

|                   | V <sub>RM</sub> = 3 V                                                           | -    | -    | 0.1  | μA                   |  |

| R <sub>d</sub>    | Square pulse, $I_{PP} = 3 \text{ A t}_p = 2.5 \mu \text{s}$                     | -    | 2.2  | -    | Ω                    |  |

| αΤ                | $\Delta V_{BR} = \alpha T(T_{amb} - 25 ^{\circ}C) \times V_{BR} (25 ^{\circ}C)$ | -    | -    | 6.5  | 10 <sup>-4</sup> /°C |  |

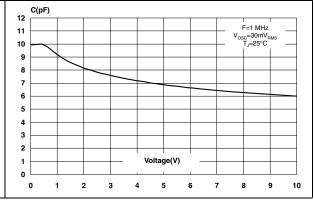

| C <sub>line</sub> | $V_R = 0 \text{ V, F} = 1 \text{ MHz, } V_{osc} = 30 \text{ mV}$                | -    | 10   | -    | pF                   |  |

ESDA14V2-1BF3 Characteristics

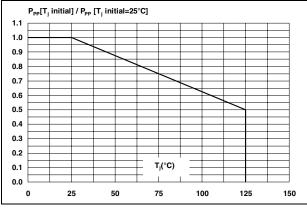

Figure 3. Relative variation of peak pulse power versus initial junction temperature

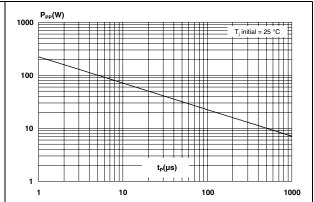

Figure 4. Peak pulse power versus exponential pulse duration

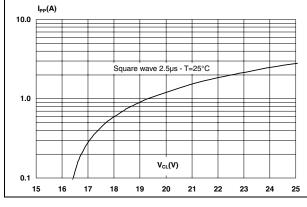

Figure 5. Clamping voltage versus peak pulse current (square pulse, typical values)

Figure 6. Junction capacitance versus reverse applied voltage (typical values)

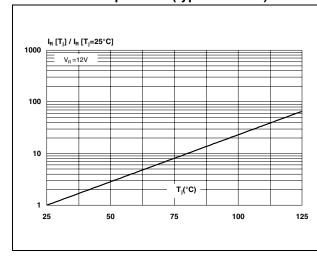

Figure 7. Relative variation of leakage current versus junction temperature (typical values)

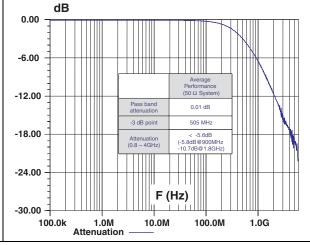

Figure 8. S21 attenuation measurements

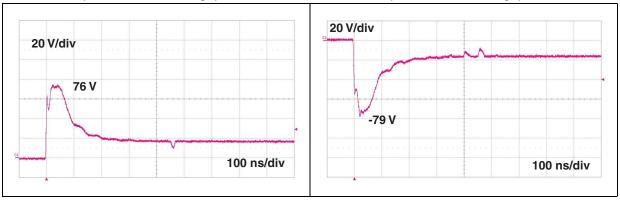

Figure 9. ESD response to IEC61000-4-2 (+15 kV air discharge)

Figure 10. ESD response to IEC61000-4-2 (-15 kV air discharge)

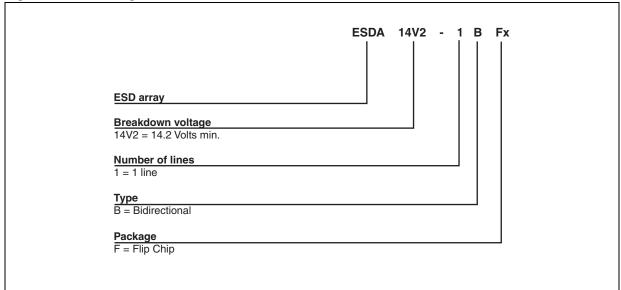

# 2 Ordering information scheme

Figure 11. Ordering information scheme

577

ESDA14V2-1BF3 Package information

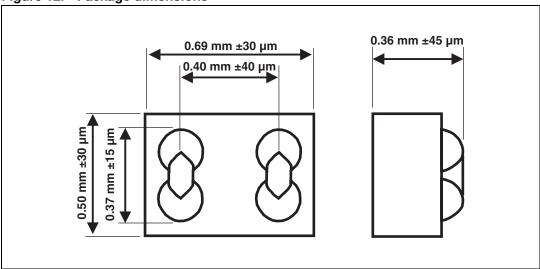

## 3 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: <a href="https://www.st.com">www.st.com</a>. ECOPACK<sup>®</sup> is an ST trademark.

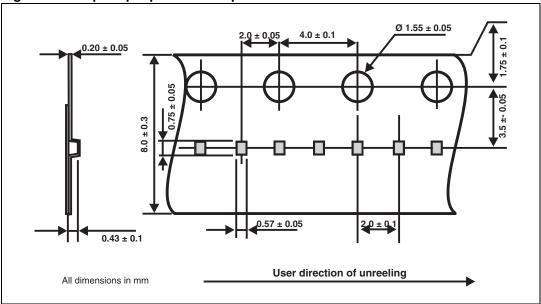

Figure 12. Package dimensions

Figure 13. Flip Chip tape and reel specification

5/

Doc ID 15894 Rev 1

PCB recommendations ESDA14V2-1BF3

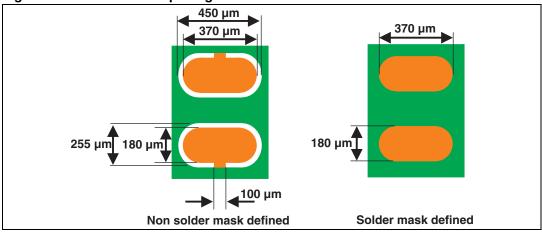

#### 4 PCB recommendations

### 4.1 Design

For optimum electrical performance and highly reliable solder joints, STMicroelectronics recommends the PCB design recommendations listed in *Table 3*.

Table 3. PCB design recommendations for solder bar pitch 400 µm

|                                 | <u>,                                      </u>                                                                                                                                          |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| For NSMD PCB                    | Oblong pad: 370 x 180 µm  - Micro via SSBU allowed  - Micro via SBU to be avoided  - Micro via SBU filled (under qualification)                                                         |

| non solder mask defined         | Track:  - Only one track per pad  - Maximum track width = 100 µm  Track layout must be symmetrical to the die axis (to homogenize stress and welding attraction during reflow assembly) |

| For SMD PCB solder mask defined | Oblong pad:  - Micro via SSBU allowed  - Micro via SBU to be avoided  - Micro via SBU filled (under qualification)                                                                      |

| PCB Pad Finishing               | Cu – Ni (2-6 μm) - Au (0.2 μm max)                                                                                                                                                      |

Note:

A gold layer finishing on the PCB pad that is too thick (0.2 μm maximum) is not recommended (low joint reliability).

To optimize the natural self centering effect of CSP on the PCB, PCB pad positioning and size have to be properly designed (see *Figure 14*)

#### Micro vias

An alternative to routing on the top surface is to route out on buried layers. To achieve this, the pads are connected to the lower layers using micro vias. Only SSBU via technology is approved.

Figure 14. Solder mask opening

57

ESDA14V2-1BF3 PCB recommendations

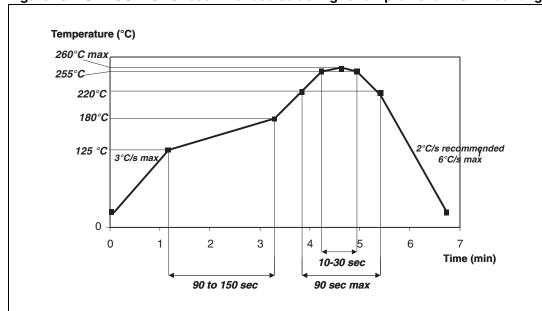

### 4.2 Assembly

For chip scale package mounting on the PCB, STMicroelectronics recommends the use of a solder stencil aperture of 330 x 330  $\mu$ m² maximum and a typical stencil thickness of 75 or 80  $\mu$ m. Chip scale packages are fully compatible with the use of near eutectic 95.5 Sn, 4 Ag, 0.5 Cu solder paste with no-clean flux. ST's recommendations for chip scale package board mounting are illustrated on the soldering reflow profile shown in *Figure 15*.

Figure 15. ST ECOPACK® recommended soldering reflow profile for PCB mounting

Dwell time in the soldering zone (with temperature higher than 220  $^{\circ}$ C) has to be kept as short as possible to prevent component and substrate damages. Peak temperature must not exceed 260  $^{\circ}$ C. Controlled atmosphere (N2 or N2H2) is recommended during the whole reflow, especially above 150  $^{\circ}$ C.

Chip scale packages are able to withstand three times the previous recommended reflow profile in order to be compatible with a double reflow when SMDs are mounted on both sides of the PCB and one additional repair.

A maximum of three soldering reflows are allowed for these lead-free packages (with repair step included).

The use of a no-clean flux is highly recommended to avoid any cleaning operation. To prevent any bump cracks, ultrasonic cleaning methods are not recommended.

# 5 Ordering information

Table 4. Ordering information

| Order code    | Marking | Package   | Weight  | Base qty | Delivery mode    |

|---------------|---------|-----------|---------|----------|------------------|

| ESDA14V2-1BF3 | None    | Flip Chip | 0.37 mg | 15 000   | Tape and reel 7" |

# 6 Revision history

Table 5. Document revision history

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 25-Jun-2009 | 1        | Initial release. |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2009 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

Doc ID 15894 Rev 1

9/9