# 3.3 V powered, 15 kV ESD protected, up to 12 Mbps true RS-485/RS-422 transceiver

SO8

#### **Features**

- ESD protection

- ±15 kV human body model

- ±8 kV IEC 1000-4-2 contact discharge

- Operates from a single 3.3 V supply no charge pump required

- Interoperable with 5 V logic

- 1 μA low current shutdown mode max.

- · Guaranteed 12 Mbps data rate

- -7 to 12 common mode input voltage range

- · Half duplex versions available

- Industry standard 75176 pinout

- Current limiting and thermal shutdown for driver overload protection

- Guaranteed high receiver output state for floating, shorted or terminated inputs with no signal present

- · Allows up to 64 transceivers on the bus

#### **Description**

lectronics sales office

The ST1480US is  $\pm 15$  kV ESD protected, 3.3 V low power transceiver for RS-485 and RS-422 communications. The device contains one driver and one receiver in half duplex configuration. The ST1480US transmits and receives at a guaranteed data rate of at least 12 Mbps. All transmitter outputs and receiver inputs are protected to  $\pm 15$  kV using human body model. Driver is short-circuit current limited and is protected against excessive power dissipation by thermal shutdown circuitry that places the driver outputs into a high-impedance state.

The ST1480US input has a true fail-safe feature that guarantees a logic high output if both inputs are open circuit, shorted together or in the presence of a termination with no signal on the bus.

#### Product status link

ST1480US

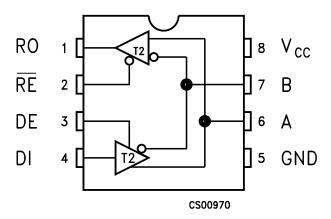

# 1 Pin configuration

Figure 1. Pin connections

**Table 1. Pin description**

| Pin | Symbol | Name and function                                                                                                                                                                                                                                                                                                                         |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | RO     | Receiver output. If A>B by 200 mV, RO is high; if A< B by 200 mV, RO is low.                                                                                                                                                                                                                                                              |

| 2   | RE     | Receiver output enable. RO is enabled when RE is low; RO is high impedance when RE is high. If RE is high and DE is low, the device enters a low power shutdown mode.                                                                                                                                                                     |

| 3   | DE     | Driver output enable. The driver outputs are enabled by bringing DE high. They are high impedance when DE is low. If RE is high DE is low, the device enters a low-power shutdown mode. If the driver outputs are enabled, the part functions as line driver, while they are high impedance, it functions as line receivers if RE is low. |

| 4   | DI     | Driver input. A low on DI forces output A low and output B high. Similarly, a high on DI forces output A high and output B low.                                                                                                                                                                                                           |

| 5   | GND    | Ground                                                                                                                                                                                                                                                                                                                                    |

| 6   | Α      | Non-inverting receiver input and non-inverting driver output.                                                                                                                                                                                                                                                                             |

| 7   | В      | Inverting receiver input and inverting driver output.                                                                                                                                                                                                                                                                                     |

| 8   | VCC    | Supply voltage: VCC=3 V to 3.6 V.                                                                                                                                                                                                                                                                                                         |

DS13697 - Rev 1 page 2/21

#### 2 Truth tables

Table 2. Truth table (driver)

|    | Inputs |    |   | puts | Mode     |  |  |

|----|--------|----|---|------|----------|--|--|

| RE | DE     | DI | В | Α    | Mode     |  |  |

| Х  | Н      | Н  | L | Н    | Normal   |  |  |

| X  | Н      | L  | Н | L    | Normal   |  |  |

| L  | L      | Х  | Z | Z    | Normal   |  |  |

| Н  | L      | Х  | Z | Z    | Shutdown |  |  |

Note: X= do not care; Z= high impedance

|    |    | Inputs         | Output | Mode     |

|----|----|----------------|--------|----------|

| RE | DE | A-B            | RO     | Wode     |

| L  | L  | ≥+0.2V         | Н      | Normal   |

| L  | L  | ≤-0.2V         | L      | Normal   |

| L  | L  | Inputs open    | Н      | Normal   |

| L  | L  | Inputs shorted | Н      | Normal   |

| Н  | L  | X              | Z      | Shutdown |

Note: X= do not care; Z= high impedance

# 3 Maximum ratings

Table 3. Absolute maximum ratings

| Symbol          |                                | Parameter                      |           |      |  |

|-----------------|--------------------------------|--------------------------------|-----------|------|--|

| V <sub>CC</sub> | Supply voltage                 |                                | 7         | V    |  |

| VI              | Control input voltage (RE, DE) |                                | -0.3 to 7 | V    |  |

| V <sub>DI</sub> | Driver input voltage (DI)      | Driver input voltage (DI)      |           |      |  |

| $V_{DO}$        | Driver output voltage (A, B)   | Driver output voltage (A, B)   |           |      |  |

| V <sub>RI</sub> | Receiver input voltage (A, B)  |                                | ± 14      | V    |  |

| V <sub>RO</sub> | Receiver output voltage (RO)   | Receiver output voltage (RO)   |           | V    |  |

| ESD             | ESD protection voltage         | Human body model               | ±15       | kV   |  |

| ESD             | ESD protection voltage         | IEC-1000-4-2 contact discharge | ±8        | , KV |  |

Note:

Absolute maximum ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied.

#### 4 Electrical characteristics

$V_{CC}$  = 3 V to 3.6 V,  $T_A$  = -40 to 85 °C, unless otherwise specified. Typical values are referred to  $T_A$  = 25 °C).

**Table 4. Electrical characteristics**

| Symbol            | Parameter                            | Test conditions             |                                                              |  | Тур.  | Max. | Unit |

|-------------------|--------------------------------------|-----------------------------|--------------------------------------------------------------|--|-------|------|------|

| louppuy           | V <sub>CC</sub> power supply current | No Load,                    | DE = $V_{CC}$ , $\overline{RE}$ = 0 V or $V_{CC}$            |  | 1.3   | 2.2  | mA   |

| ISUPPLY           | v.C.C bower subbiy current           | DI = 0 V or V <sub>CC</sub> | DE=0 V, RE=0 V                                               |  | 1.2   | 1.9  | mA   |

| I <sub>SHDN</sub> | Shutdown supply current              | DE = 0 V, RE = $V_{CO}$     | DE = 0 V, RE = V <sub>CC</sub> , DI = 0 V or V <sub>CC</sub> |  | 0.002 | 1    | μA   |

Table 5. Logic input electrical characteristics

| Symbol           | Parameter                  | Test conditions                     |            | Min. | Тур. | Max. | Unit |

|------------------|----------------------------|-------------------------------------|------------|------|------|------|------|

| V <sub>IL</sub>  | Input logic threshold low  | DE, DI, RE                          |            |      |      | 0.8  | V    |

| V <sub>IH</sub>  | Input logic threshold high | DE, DI, RE                          |            | 2    |      |      | V    |

| I <sub>IN1</sub> | Logic input current        | DE, DI, RE                          |            |      |      | ±2.0 | μΑ   |

| livio            | Input current (A, B)       | DE=0 V, V <sub>CC</sub> =0 or 3.6 V |            |      |      | 1    | mA   |

| I <sub>IN2</sub> | input current (A, D)       | 52 0 v, v <sub>CC</sub> 0 01 0.0 v  | VIN = -7 V |      |      | -0.8 | mA   |

Table 6. Transmitter electrical characteristics

| Symbol           | Parameter Test conditions                                                                     |                                                                          | Min. | Тур. | Max. | Unit |

|------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------|------|------|------|

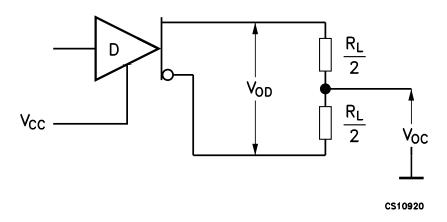

|                  |                                                                                               | R <sub>L</sub> = 100 $\Omega$ (RS-422) (Figure 1. Pin connections)       | 2    |      |      | V    |

| V <sub>OD</sub>  | Differential drive output                                                                     | $R_L$ = 54 Ω (RS-485) (Figure 1. Pin connections)                        | 1.5  |      |      | V    |

|                  |                                                                                               | $R_L$ = 60 $\Omega$ (RS-485) (Figure 2. Driver and $V_{OC}$ test load)   | 1.5  |      |      | V    |

| ΔV <sub>OD</sub> | Change in magnitude of driver differential output voltage for complementary output states (1) | R <sub>L</sub> = 54 $\Omega$ or 100 $\Omega$ (Figure 1. Pin connections) |      |      | 0.2  | V    |

| V <sub>OC</sub>  | Driver common mode output voltage                                                             | $R_L$ = 54 $\Omega$ or 100 $\Omega$ (Figure 1. Pin connections)          |      |      | 3    | V    |

| ΔV <sub>OC</sub> | Change in magnitude of driver common mode output voltage <sup>(1)</sup>                       | R <sub>L</sub> = 54 $\Omega$ or 100 $\Omega$ (Figure 1. Pin connections) |      |      | 0.2  | V    |

| I <sub>OSD</sub> | Driver short-circuit output current                                                           |                                                                          |      |      | ±250 | mA   |

<sup>1.</sup>  $\triangle$ VOD and  $\triangle$ VOC are the changes in VOD and VOC, respectively, when the DI input changes state.

DS13697 - Rev 1 page 5/21

Table 7. Receiver electrical characteristics

| Symbol           | Parameter                                           | Test conditions                                                                                                                   | Min. | Тур. | Max.   | Unit |

|------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------|------|--------|------|

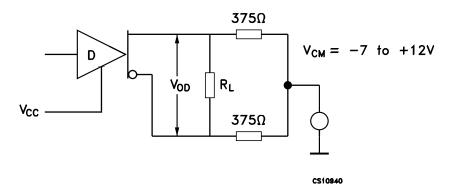

| V <sub>TH</sub>  | Receiver differential threshold voltage             | V <sub>CM</sub> =-7 V to 12 V, DE = 0                                                                                             | -0.2 |      | -0.015 | V    |

| $\Delta V_{TH}$  | Receiver input hysteresis                           | V <sub>CM</sub> =0 V                                                                                                              |      | 30   |        | μV   |

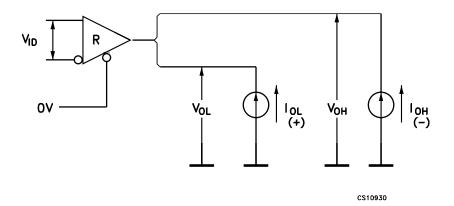

| V <sub>OH</sub>  | Receiver output high voltage                        | $I_{OUT}$ = -4 mA, $V_{ID}$ = 200 mV, (Figure 8. Drive enable and disable times waveforms)                                        | 2    |      |        | V    |

| V <sub>OL</sub>  | Receiver output low voltage                         | I <sub>OUT</sub> = 4 mA, V <sub>ID</sub> = -200 mV, (Figure 3. Driver V <sub>OD</sub> with varying common mode voltage test load) |      |      | 0.4    | V    |

| I <sub>OZR</sub> | 3-state (high impedance) output current at receiver | $V_{CC}$ = 3.6 V, $V_{O}$ = 0 V to $V_{CC}$                                                                                       |      |      | ±1     | μA   |

| R <sub>RIN</sub> | Receiver input resistance                           | V <sub>CM</sub> = -7 V to 12 V                                                                                                    | 24   |      |        | kΩ   |

| I <sub>OSR</sub> | Receiver short-circuit current                      | V <sub>RO</sub> = 0 V to V <sub>CC</sub>                                                                                          | 7    |      | 60     | mA   |

Table 8. Driver switching characteristics

| Symbol                               | Parameter                                                                     | Test conditions                                                                                                                                                          |    | Тур. | Max. | Unit |

|--------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------|------|------|

| $D_R$                                | Maximum data rate                                                             |                                                                                                                                                                          | 12 | 15   |      | Mbps |

| t <sub>DD</sub>                      | Differential output delay                                                     | $R_L$ = 60 Ω, $C_L$ = 15 pF, (Figure 4. Receiver $V_{OH}$ and $V_{OL}$ test circuit and Figure 5. Drive differential output delay transition time test circuit)          |    | 18   | 30   | ns   |

| t <sub>TD</sub>                      | Differential output transition time                                           | $R_L$ = 60 Ω, $C_L$ = 15 pF, (Figure 4. Receiver $V_{OH}$ and $V_{OL}$ test circuit and Figure 5. Drive differential output delay transition time test circuit)          |    | 12   | 20   | ns   |

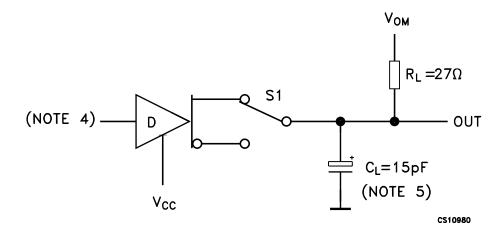

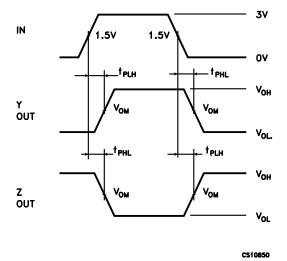

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay                                                             | $R_L$ = 27 $\Omega$ , $C_L$ = 15 pF, (Figure 8. Drive enable and disable times waveforms and Figure 9. Drive propagation time test circuit)                              |    | 18   | 30   | ns   |

| t <sub>PDS</sub>                     | t <sub>PLH</sub> - t <sub>PHL</sub>  propagation<br>delay skew <sup>(1)</sup> | $R_L$ = 27 $\Omega$ , $C_L$ = 15 pF, (Figure 8. Drive enable and disable times waveforms and Figure 9. Drive propagation time test circuit)                              |    | 2    | 5    | ns   |

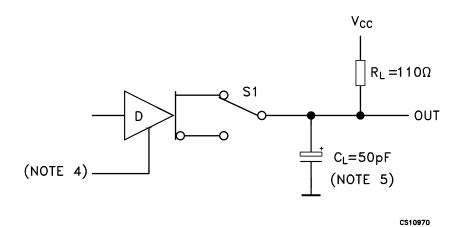

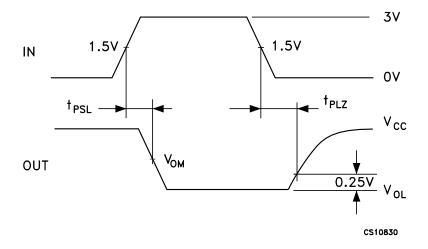

| t <sub>PZL</sub>                     | Output enable time                                                            | R <sub>L</sub> = 110 $\Omega$ , (Figure 10. Drive propagation time waveform and Figure 11. Drive enable and disable times test circuit (R <sub>L</sub> = 110 $\Omega$ )) |    | 19   | 35   | ns   |

| t <sub>PZH</sub>                     | Output enable time                                                            | R <sub>L</sub> = 110 $\Omega$ , (Figure 10. Drive propagation time waveform and Figure 11. Drive enable and disable times test circuit (R <sub>L</sub> = 110 $\Omega$ )) |    | 30   | 50   | ns   |

| t <sub>PHZ</sub>                     | Output disable time                                                           | R <sub>L</sub> = 110 , (Figure 6. Drive differential output delay transition time waveform and Figure 7. Drive enable and disable times test circuit)                    |    | 19   | 35   | ns   |

| t <sub>PLZ</sub>                     | Output disable time                                                           | R <sub>L</sub> = 110 $\Omega$ (Figure 10. Drive propagation time waveform and Figure 11. Drive enable and disable times test circuit (R <sub>L</sub> = 110 $\Omega$ ))   |    | 30   | 50   | ns   |

| t <sub>SKEW</sub>                    | Differential output delay skew                                                |                                                                                                                                                                          |    | 1    | 3    | ns   |

| t <sub>ZH(SHDN)</sub>                | Driver enable from shutdown to output high                                    |                                                                                                                                                                          |    | 30   | 50   | ns   |

| t <sub>ZL(SHDN)</sub>                | Driver enable from shutdown to output low                                     |                                                                                                                                                                          |    | 19   | 35   | ns   |

<sup>1.</sup> Measured on  $|t_{PLH}(A)-t_{PHL}(A)|$  and  $|t_{PLH}(B)-t_{PHL}(B)|$

DS13697 - Rev 1 page 6/21

Table 9. Receiver switching characteristics

| Symbol                               | Parameter                                                                                                                                                                                 | Test conditions                                                                                                                                                            | Min. | Тур. | Max. | Unit |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay                                                                                                                                                                         | V <sub>ID</sub> = 0 V to 3 V, C <sub>L1</sub> =15 pF (Figure 12. Drive enable and disable times waveforms (B) and Figure 13. Receiver propagation delay time test circuit) |      | 30   | 50   | ns   |

| t <sub>RPDS</sub>                    | tPLH - tPHL <br>propagation delay<br>skew                                                                                                                                                 | V <sub>ID</sub> = 0 V to 3 V, C <sub>L1</sub> =15 pF (Figure 12. Drive enable and disable times waveforms (B) and Figure 13. Receiver propagation delay time test circuit) |      | 1    | 3    | ns   |

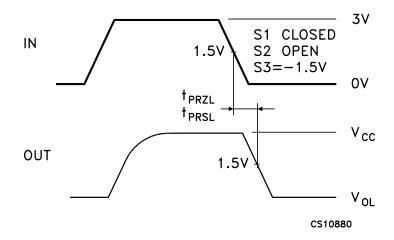

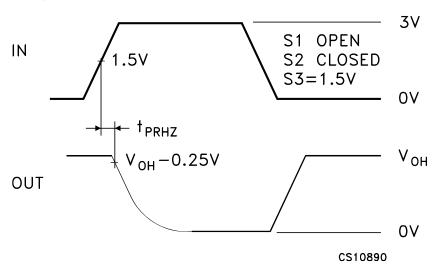

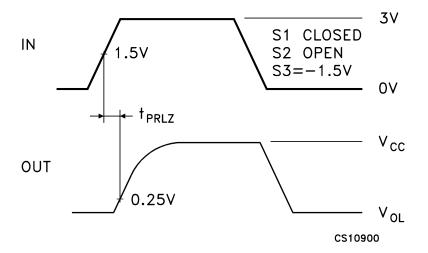

| t <sub>PZL</sub>                     | Outputenable time  C <sub>RL</sub> = 15 pF, (Figure 14. Receiver propagation delay time waveforms and Figure 18. Receiver enable and disable times waveform (S2 closed))                  |                                                                                                                                                                            |      |      | 20   | ns   |

| t <sub>PZH</sub>                     | Outputenable time                                                                                                                                                                         | C <sub>RL</sub> = 15 pF, (Figure 14. Receiver propagation delay time waveforms and Figure 18. Receiver enable and disable times waveform (S2 closed))                      |      | 10   | 20   | ns   |

| t <sub>PHZ</sub>                     | Outputdisable time                                                                                                                                                                        | C <sub>RL</sub> = 15 pF, (Figure 14. Receiver propagation delay time waveforms and Figure 18. Receiver enable and disable times waveform (S2 closed))                      |      | 10   | 20   | ns   |

| t <sub>PLZ</sub>                     | t <sub>PLZ</sub> Outputdisable time C <sub>RL</sub> = 15 pF, (Figure 14. Receiver propagation delay time waveforms and Figure 18. Receiver enable and disable times waveform (S2 closed)) |                                                                                                                                                                            |      | 10   | 20   | ns   |

| t <sub>ZH(SHDN)</sub>                | Receiver enable from shutdown to output high                                                                                                                                              | C <sub>RL</sub> = 15 pF, (Figure 14. Receiver propagation delay time waveforms and Figure 18. Receiver enable and disable times waveform (S2 closed))                      |      | 10   | 20   | ns   |

| t <sub>ZL(SHDN)</sub>                | Receiver enable from shutdown to output low                                                                                                                                               | C <sub>RL</sub> = 15 pF, (Figure 14. Receiver propagation delay time waveforms and Figure 18. Receiver enable and disable times waveform (S2 closed))                      |      | 20   | 40   | μs   |

DS13697 - Rev 1 page 7/21

5

# Test circuits and typical characteristics

Figure 2. Driver and V<sub>OC</sub> test load

Figure 3. Driver  $V_{\mbox{\scriptsize OD}}$  with varying common mode voltage test load

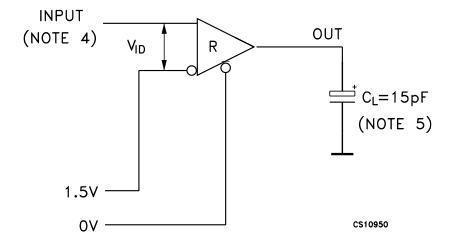

Figure 4. Receiver  $V_{\mbox{\scriptsize OH}}$  and  $V_{\mbox{\scriptsize OL}}$  test circuit

DS13697 - Rev 1 page 8/21

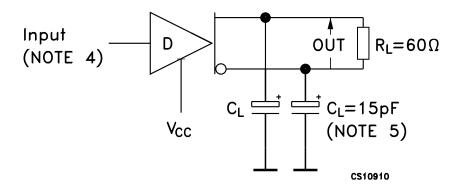

Figure 5. Drive differential output delay transition time test circuit

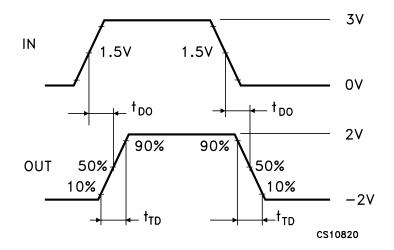

Figure 6. Drive differential output delay transition time waveform

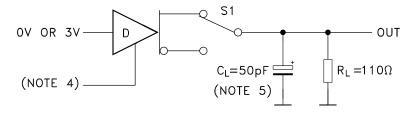

Figure 7. Drive enable and disable times test circuit

CS10960

DS13697 - Rev 1 page 9/21

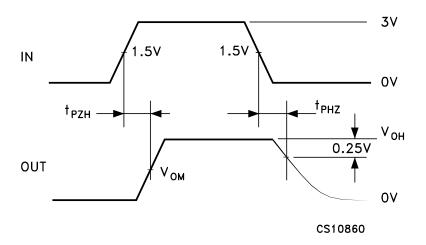

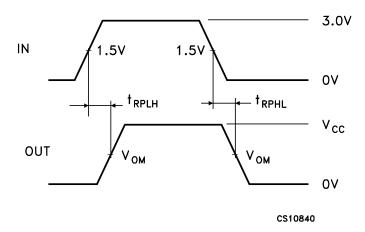

Figure 8. Drive enable and disable times waveforms

Figure 9. Drive propagation time test circuit

Figure 10. Drive propagation time waveform

DS13697 - Rev 1 page 10/21

Figure 11. Drive enable and disable times test circuit ( $R_L$ = 110  $\Omega$ )

Figure 12. Drive enable and disable times waveforms (B)

Figure 13. Receiver propagation delay time test circuit

DS13697 - Rev 1 page 11/21

Figure 14. Receiver propagation delay time waveforms

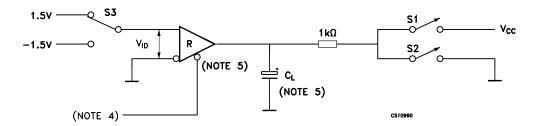

Figure 15. Receiver enable and disable times test circuit (B)

Figure 16. Receiver enable and disable times waveform (S1 open)

DS13697 - Rev 1 page 12/21

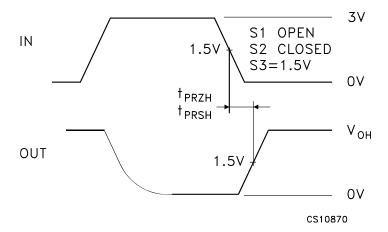

Figure 17. Receiver enable and disable times waveform (S1 closed)

Figure 18. Receiver enable and disable times waveform (S2 closed)

Figure 19. Receiver enable and disable times waveform (S2 open)

DS13697 - Rev 1 page 13/21

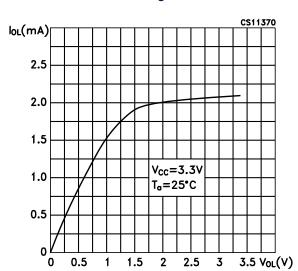

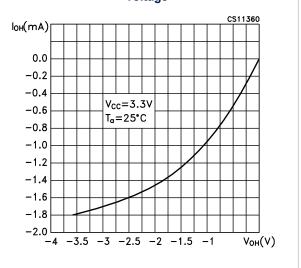

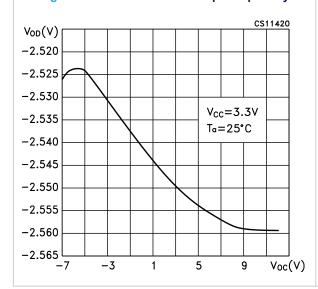

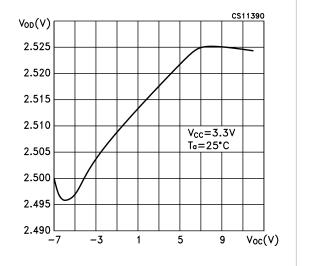

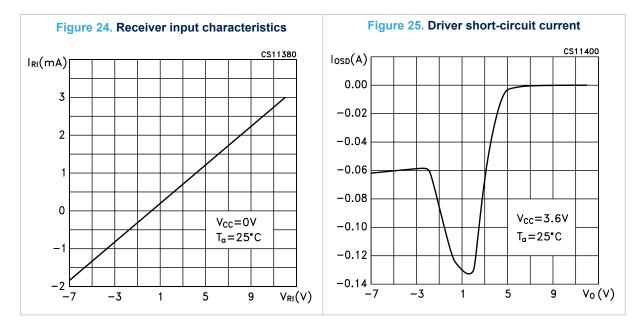

Figure 20. Receiver output current vs. output low voltage

Figure 21. Receiver output current vs. output high voltage

Figure 22. Low level driver output capability

Figure 23. High level driver output capability

DS13697 - Rev 1 page 14/21

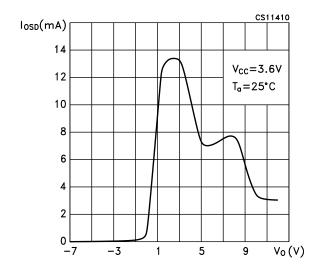

Figure 26. Driver short-circuit current

DS13697 - Rev 1 page 15/21

# 6 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

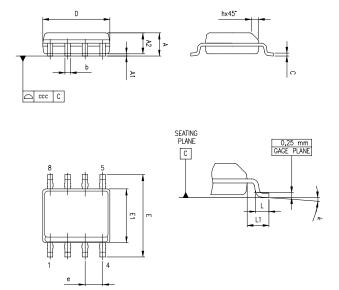

#### 6.1 SO8 package information

Figure 27. SO8 package outline

Table 10. SO-8 mechanical data

| Dim.   | m    | m    |      | Inches |       |       |

|--------|------|------|------|--------|-------|-------|

| Dilli. | Min. | Тур. | Max. | Min.   | Тур.  | Max.  |

| А      |      |      | 1.75 |        |       | 0.069 |

| A1     | 0.1  |      | 0.25 | 0.004  |       | 0.01  |

| A2     | 1.25 |      |      | 0.049  |       |       |

| b      | 0.28 |      | 0.48 | 0.011  |       | 0.019 |

| С      | 0.17 |      | 0.23 | 0.007  |       | 0.01  |

| D      | 4.8  | 4.9  | 5    | 0.189  | 0.193 | 0.197 |

| E      | 5.8  | 6    | 6.2  | 0.228  | 0.236 | 0.244 |

| E1     | 3.8  | 3.9  | 4    | 0.15   | 0.154 | 0.157 |

| е      |      | 1.27 |      |        | 0.05  |       |

| h      | 0.25 |      | 0.5  | 0.01   |       | 0.02  |

| L      | 0.4  |      | 1.27 | 0.016  |       | 0.05  |

| L1     |      | 1.04 |      |        | 0.04  |       |

| k      | 0    |      | 8 °  | 1 °    |       | 8 °   |

| ccc    |      |      | 0.1  |        |       | 0.004 |

DS13697 - Rev 1 page 16/21

# 7 Ordering information

**Table 11. Ordering information**

| Order codes   | Order codes Temperature range |                    | Packing             |

|---------------|-------------------------------|--------------------|---------------------|

| ST1480ACDR/US | 0 to 70 °C                    | SO-8 tape and reel | 2500 parts per reel |

DS13697 - Rev 1 page 17/21

# **Revision history**

Table 12. Document revision history

| Date        | Version | Changes          |

|-------------|---------|------------------|

| 06-Apr-2021 | 1       | Initial release. |

### **Contents**

| 1   | Pin configuration                         | 2  |

|-----|-------------------------------------------|----|

| 2   | Truth tables                              | 3  |

| 3   | Maximum ratings                           | 4  |

| 4   | Electrical characteristics                | 5  |

| 5   | Test circuits and typical characteristics | 8  |

| 6   | Package information                       | 16 |

|     | 6.1 SO8 package information               | 16 |

| 7   | Ordering information                      | 17 |

| Rev | vision history                            | 18 |

### **List of tables**

| Table 1.  | Pin description                        |

|-----------|----------------------------------------|

|           | Truth table (driver)                   |

| Table 3.  | Absolute maximum ratings               |

| Table 4.  | Electrical characteristics             |

| Table 5.  | Logic input electrical characteristics |

| Table 6.  | Transmitter electrical characteristics |

| Table 7.  | Receiver electrical characteristics    |

| Table 8.  | Driver switching characteristics       |

| Table 9.  | Receiver switching characteristics     |

|           | SO-8 mechanical data                   |

| Table 11. | Ordering information                   |

|           | Document revision history              |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2021 STMicroelectronics - All rights reserved

DS13697 - Rev 1 page 21/21