# **INERTIAL SENSOR:** 3Axis - 2g/6g LINEAR ACCELEROMETER

#### FEATURES

- 2.4V TO 3.6V SINGLE SUPPLY OPERATION

- 0.5mg RESOLUTION OVER 100Hz BW

- 2g/6g USER SELECTABLE FULL-SCALE

- OUTPUT VOLTAGE, OFFSET AND SENSITIVITY RATIOMETRIC TO THE SUPPLY VOLTAGE

- FACTORY TRIMMED DEVICE SENSITIVITY AND OFFSET

- EMBEDDED SELF TEST

- **HIGH SHOCK SURVIVABILITY**

#### 2 **DESCRIPTION**

The LIS3L02AQ is a low-power three-axis linear accelerometer that includes a sensing element and an IC interface able to take the information from the sensing element and to provide an analog signal to the external world.

The sensing element, capable to detect the acceleration, is manufactured using a dedicated process called THELMA (Thick Epi-Poly Layer for Microactuators and Accelerometers) developed by ST to produce inertial sensors and actuators in silicon.

The IC interface instead is manufactured 'siny' a CMOS process that allows high level of in earta ion to design a dedicated circuit which is trin med to better match the sensing element characteristics.

Figure 1. Package

Table 1. Order Codes

| Figure 1. Package  QFN  Table 1. Order Codes | -44     | 200lucit(s) |

|----------------------------------------------|---------|-------------|

| Part Number                                  | Package | 400         |

| LIS3L02AQ                                    | QFN-44  | X VOVI      |

|                                              | 4.4     |             |

The LIS3L02AQ has a user selectal to the scale of 2g, 6g and it is capable of measuring receierations over a maximum bandwidth of 4.0 KH, for the X and Y axis and 2.5KHz for the 7 xis. The device bandwidth may be reduce a by u in g external capacitances. A self-test cap ab it, a ows the user to check the functioning of the system.

The LIS3I Oz No is available in plastic SMD package and it is main ed over a temperature range extending ໂປ. ເປັນ C to +85°C.

The LiS3L02AQ belongs to a family of products suitbie for a variety of applications:

- Motion activated functions in mobile terminals

- Gaming and Virtual Reality input devices

- Free-fall detection and Data protection

- Antitheft systems and Inertial Navigation

- Appliance Control and Robotics

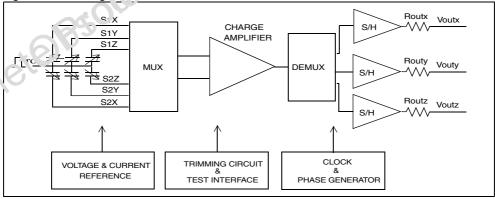

Figure 2. Block Diagonal

Rev. 4 November 2004 1/9

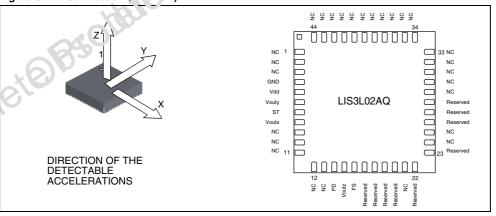

**Table 2. Pin Description**

| N°     | Pin      | Function                                                              |           |

|--------|----------|-----------------------------------------------------------------------|-----------|

| 1 to 3 | NC       | Internally not connected                                              |           |

| 4      | GND      | 0V supply                                                             |           |

| 5      | Vdd      | Power supply                                                          |           |

| 6      | Vouty    | Output Voltage                                                        |           |

| 7      | ST       | Self Test (Logic 0: normal mode; Logic 1: Self-test)                  | .16       |

| 8      | Voutx    | Output Voltage                                                        | apduct(s) |

| 9-13   | NC       | Internally not connected                                              | 41/10     |

| 14     | PD       | Power Down (Logic 0: normal mode; Logic 1: Power-Down mode)           | 200,0     |

| 15     | Voutz    | Output Voltage                                                        | 331       |

| 16     | FS       | Full Scale selection (Logic 0: 2g Full-scale; Logic 1: 6g Full-scale) |           |

| 17-18  | Reserved | Leave unconnected                                                     |           |

| 19     | NC       | Internally not connected                                              |           |

| 20     | Reserved | Leave unconnected                                                     |           |

| 21     | NC       | Internally not connected                                              |           |

| 22-23  | Reserved | Leave unconnected                                                     |           |

| 24-25  | NC       | Internally not connected                                              |           |

| 26     | Reserved | Connect to Vdd or GND                                                 |           |

| 27     | Reserved | Leave unconnected or connect to V.'d                                  |           |

| 28     | Reserved | Leave unconnected or cor nec. to GND                                  |           |

| 29-44  | NC       | Internally not so, nested                                             |           |

Figure 3. Pin Connection (Tc o view)

**Table 3. Electrical Characteristics**

(Temperature range -40°C to +85°C) All the parameters are specified @ Vdd =3.3V, T=25°C unless otherwise noted

| Symbol  | Parameter                                       | Test Condition                                         | Min.       | Typ. <sup>1</sup> | Max.       | Unit       |

|---------|-------------------------------------------------|--------------------------------------------------------|------------|-------------------|------------|------------|

| Vdd     | Supply voltage                                  |                                                        | 2.4        | 3.3               | 3.6        | ٧          |

| ldd     | Supply current                                  | mean value<br>PD pin connected<br>to GND               |            | 0.85              | 1.5        | mA         |

| IddPdn  | Supply current in Power Down<br>Mode            | rms value<br>PD pin connected<br>to Vdd                |            | 2                 | 5          | μΑ         |

| Voff    | Zero-g level <sup>2</sup>                       | T = 25°C                                               | Vdd/2-10%  | Vdd/2             | Vdd/2+10%  | ٧          |

| OffDr   | Zero-g level Vs temperature                     | Delta from +25°C                                       |            | ±1.5              |            | mg/°C      |

| Ar      | Acceleration range <sup>3</sup>                 | FS pin connected to GND                                | ±1.8       | ±2.0              |            | g          |

|         |                                                 | FS pin connected to Vdd                                | ±5.4       | ±6.0              |            | 9          |

| So      | Sensitivity <sup>2</sup>                        | Full-scale = 2g                                        | Vdd/5-10%  | Vdd/5             | Yud/5+10%  | V/g        |

|         |                                                 | Full-scale = 6g                                        | Vdd/15-10% | Vdc <u>.</u> /15  | 'au/15+10% | V/g        |

| SoDr    | Sensitivity drift Vs<br>temperature             | Delta from +25°C                                       | ۵.0        | ± \.01            | ,          | %/°C       |

| NL      | Non Linearity <sup>4</sup>                      | Best fit straight line<br>Full-scale = 2g<br>X, Y axis | 459        | ±0.3              | ±1.5       | % FS       |

|         | ad a                                            | Best fit straight line;<br>Full-scale = 20,<br>Z aris  |            | ±0.6              | ±2         | % FS       |

| CrossAx | Cross-Axis <sup>5</sup>                         | 951                                                    |            | ±2                | ±4         | %          |

| fuc     | Sensing Element Roso 12.1t                      | X, Y axis                                              | 3.2        | 4.0               | 4.8        | KHz        |

|         | Frequency <sup>6</sup>                          | Z axis                                                 | 1.8        | 2.5               | 3.2        | KHz        |

| an      | Acceleration noise density                      | Vdd=3.3V;<br>Full-scale = 2g                           |            | 50                |            | μg/<br>√Hz |

| Vt      | Vt S eli rest output voltage delta change 7,8,9 | T = 25°C<br>Vdd=3.3V<br>Full-scale = 2g<br>X axis      | -20        | -40               |            | mV         |

| ~       |                                                 | T = 25°C<br>Vdd=3.3V<br>Full-scale = 2g<br>Y axis      | 20         | 40                |            | mV         |

|         |                                                 | T = 25°C<br>Vdd=3.3V<br>Full-scale = 2g<br>Z axis      | 20         | 50                |            | mV         |

### Table 3. Electrical Characteristics (continued)

(Temperature range -40°C to +85°C) All the parameters are specified @ Vdd =3.3V, T=25°C unless otherwise noted

| Symbol                                                       | Parameter                                                                                                                                                                                                                                                                                                                      | Test Condition                                                                                                                                   | Min.                                                                                   | Typ. <sup>1</sup> | Max.           | Unit      |          |

|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------|----------------|-----------|----------|

| Vst                                                          | Self test input                                                                                                                                                                                                                                                                                                                | Logic 0 level                                                                                                                                    | 0                                                                                      |                   | 0.8            | V         |          |

|                                                              |                                                                                                                                                                                                                                                                                                                                | Logic 1 level                                                                                                                                    | 2.2                                                                                    |                   | Vdd            | V         |          |

| Rout                                                         | Output impedance                                                                                                                                                                                                                                                                                                               |                                                                                                                                                  | 80                                                                                     | 110               | 140            | kΩ        |          |

| Cload                                                        | Capacitive load drive <sup>10</sup>                                                                                                                                                                                                                                                                                            |                                                                                                                                                  | 320                                                                                    |                   |                | pF        | *(5)     |

| Ton                                                          | Ton Turn-On Time at exit from Power Down mode Cload in μF 550*Cload +0.3                                                                                                                                                                                                                                                       |                                                                                                                                                  |                                                                                        |                   |                |           | AUCIC    |

| 3. G<br>4. G<br>5. C<br>6. G<br>7. S<br>8. S<br>9. W<br>10.B | iffset and sensitivity are essentially re uaranteed by wafer level test and me uaranteed by design through measu ontribution to the measuring output ouaranteed by design elf test "output voltage delta change" elf test "output voltage delta change" /hen full-scale is set to 6g, self-test "oandwidth=1/(2"π*110KΩ*Cload) | easurement of initial offse<br>rements done up to 1g<br>of the inclination/accelerat<br>is defined as Vout(vst=Lor<br>varies cubically with supp | t and sensitivity<br>ion along the perposicol<br>gic1)-Vout(Vst=Logical<br>oly voltage | 0)                | 350th          | jei       |          |

|                                                              | TE MAXIMUM RATING                                                                                                                                                                                                                                                                                                              |                                                                                                                                                  | LO                                                                                     |                   |                |           |          |

| Stresses :                                                   | above those listed as "absolu                                                                                                                                                                                                                                                                                                  | te maximum ratinos                                                                                                                               | may caus a r                                                                           | ermanent dan      | nage to the de | vice This | <u>.</u> |

- Notes: 1. Typical specifications are not guaranteed

2. Offset and sensitivity are essentially ratiometric to supply voltage

3. Guaranteed by wafer level test and measurement of initial offset and sensitivity

- 4. Guaranteed by design through measurements done up to 1g

5. Contribution to the measuring output of the inclination/acceleration along the perpendicular axis

- Self test "output voltage delta change" is defined as Vout<sub>(Vst=Logict)</sub>-Vout<sub>(Vst=Logict)</sub>-Vout<sub>(Vst=Logict)</sub>

Self test "output voltage delta change" varies cubically with supply voltage

When full-scale is set to 6g, self-test "output delta change" is one third of the specified value

- 10.Bandwidth=1/( $2^*\pi^*110K\Omega^*Cload$ )

#### **ABSOLUTE MAXIMUM RATING**

Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device of these conditions is not implied. Exposure to maximum rating conditions for extended periods may after device reliability.

**Table 4. Absolute Maximum Rating**

| Symbol           | R iti. gs                                        | Maximum Value     | Unit |

|------------------|--------------------------------------------------|-------------------|------|

| Vdd              | Supply voltage                                   | -0.3 to 7         | V    |

| Vin              | Input voltage ca. ac. / control pin (FS, PD, ST) | -0.3 to Vdd +0.3  | V    |

| A <sub>POW</sub> | Acceleration 'Arry axis, Powered, Vdd=3.3V)      | 3000g for 0.5 ms  |      |

|                  | 25                                               | 10000g for 0.1 ms |      |

| AU VP            | Coeleration (Any axis, Unpowered)                | 3000g for 0.5 ms  |      |

| 2/10             |                                                  | 10000g for 0.1 ms |      |

| T <sub>OP</sub>  | Operating Temperature Range                      | -40 to +85        | °C   |

| T <sub>STG</sub> | Storage Temperature Range                        | -40 to +105       | °C   |

| ESD              | Electrostatic discharge protection               | 2KV HBM           |      |

### **FUNCTIONALITY**

The LIS3L02AQ is a low-cost, low-power, analog output three-axis linear accelerometer packaged in QFN package. The complete device includes a sensing element and an IC interface able to take the information from the sensing element and to provide an analog signal to the external world.

#### 3.1 Sensing element

The THELMA process is utilized to create a surface micro-machined accelerometer. The technology allows to (Sipolucile) carry out suspended silicon structures which are attached to the substrate in a few points called anchors and free to move on a plane parallel to the substrate itself. To be compatible with the traditional packaging techniques a cap is placed on top of the sensing element to avoid blocking the moving parts during the molding

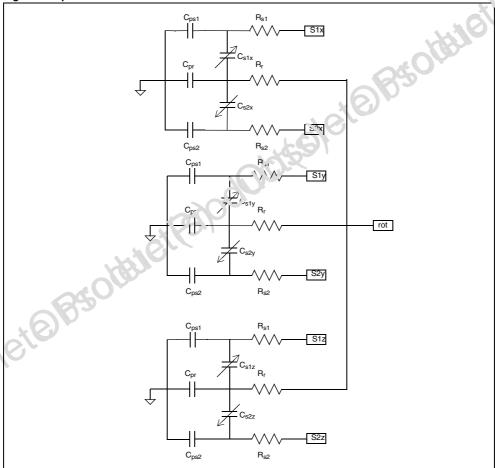

The equivalent circuit for the sensing element is shown in the figure below; when a linear acceleration is applied, the proof mass displaces from its nominal position, causing an imbalance in the capacitive half-bridge. This imbalance is measured using charge integration in response to a voltage pulse applied to the sense capacitor.

Figure 4. Equivalent electrical circuit

47/ 5/9

The nominal value of the capacitors, at steady state, is few pF and when an acceleration is applied the maximum variation of the capacitive load is few hundredths of pF.

#### 3.2 IC Interface

The complete signal processing uses a fully differential structure, while the final stage converts the differential signal into a single-ended one to be compatible with the external world.

The first stage is a low-noise capacitive amplifier that implements a Correlated Double Sampling (CDS) at its output to cancel the offset and the 1/f noise. The produced signal is then sent to three different S&Hs, one for each channel, and made available to the outside.

**EXPOUNCTION** The low noise input amplifier operates at 200 kHz while the three S&Hs operate at a sampling frequency of 66 kHz. This allows a large oversampling ratio, which leads to in-band noise reduction and to an accurate output waveform.

All the analog parameters (output offset voltage and sensitivity) are ratiometric to the voltage supply. Increasing or decreasing the voltage supply, the sensitivity and the offset will increase or decrease linearly. The feature provides the cancellation of the error related to the voltage supply along an analog to digital conversion chain.

#### 3.3 Factory calibration

The IC interface is factory calibrated to provide to the final user a device ready to operate.

The trimming values are stored inside the device by a non volatile structure. Any time the device is turned on, obsolete Brothitet Rapidolitical the trimming parameters are downloaded into the registers to be employed during the normal prelation thus

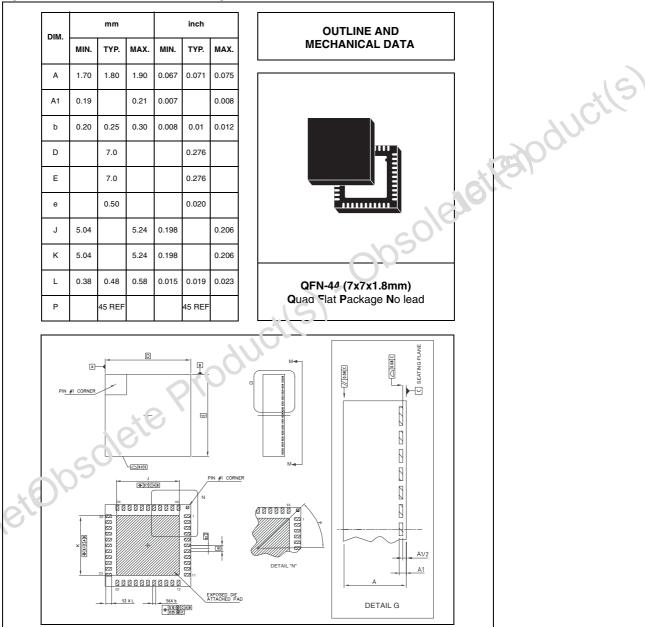

# **4 PACKAGE INFORMATION**

Figure 5. QFN-44 Mechanical Data & Package Dimensions

### **Table 5. Revision History**

| Date          | Revision | Description of Changes                                                          |

|---------------|----------|---------------------------------------------------------------------------------|

| January 2004  | 1        | First Issue                                                                     |

| February 2004 | 2        | Values of some parameters has been changed in Electrical characteristics table. |

| November 2004 | 3        | Modified/added some values in the table 2 Electrical characteristics.           |

| November 2004 | 4        | Corrected few typo errors.                                                      |

Obsoleta Protitiet Production of the contract of the contract

47/ 8/9

Information fit inclined is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in file support ofecies or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners

© 2004 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com